FD-SOI

全耗尽型绝缘体上硅

为混合信号应用而设的独特解决方案

意法半导体在硅工艺技术方面引入创新理念,以逐步利用现有的制造方法。全耗尽型绝缘体上硅 (FD-SOI) 是一种平面工艺技术,在实际简化制造工艺的同时,还可减少硅的几何形状。得益于晶体管的严格静电控制和极具创新性的电源管理技术,FD-SOI被公认为低功率、RF和毫米波应用的领先技术。与高密度PCM嵌入式非易失性存储器相结合,意法半导体为汽车应用提供了独特的解决方案。

FD-SOI创新

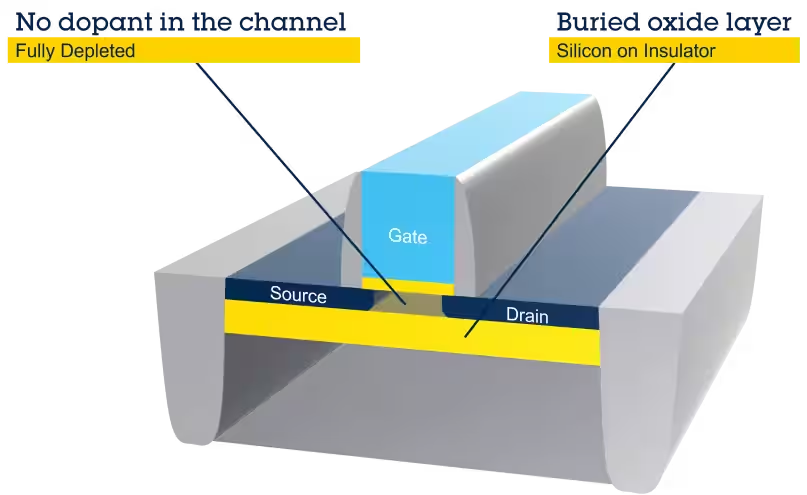

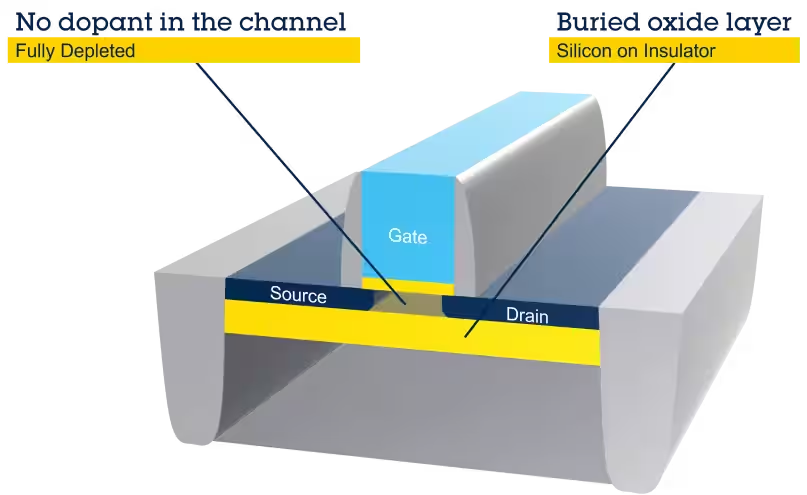

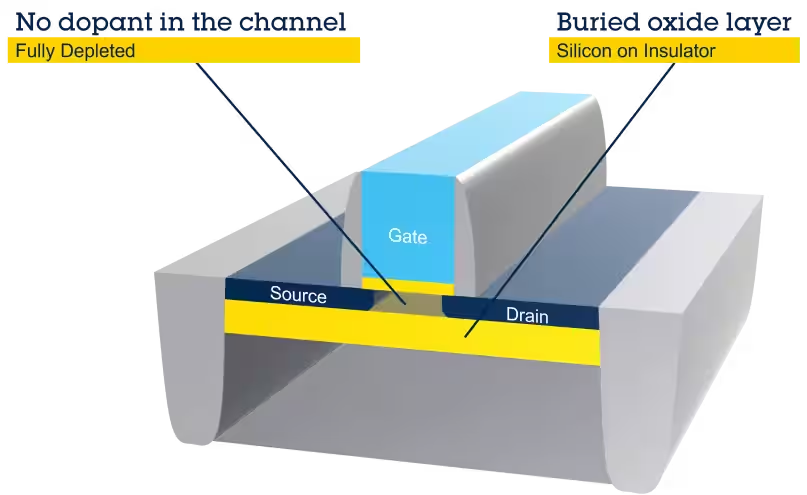

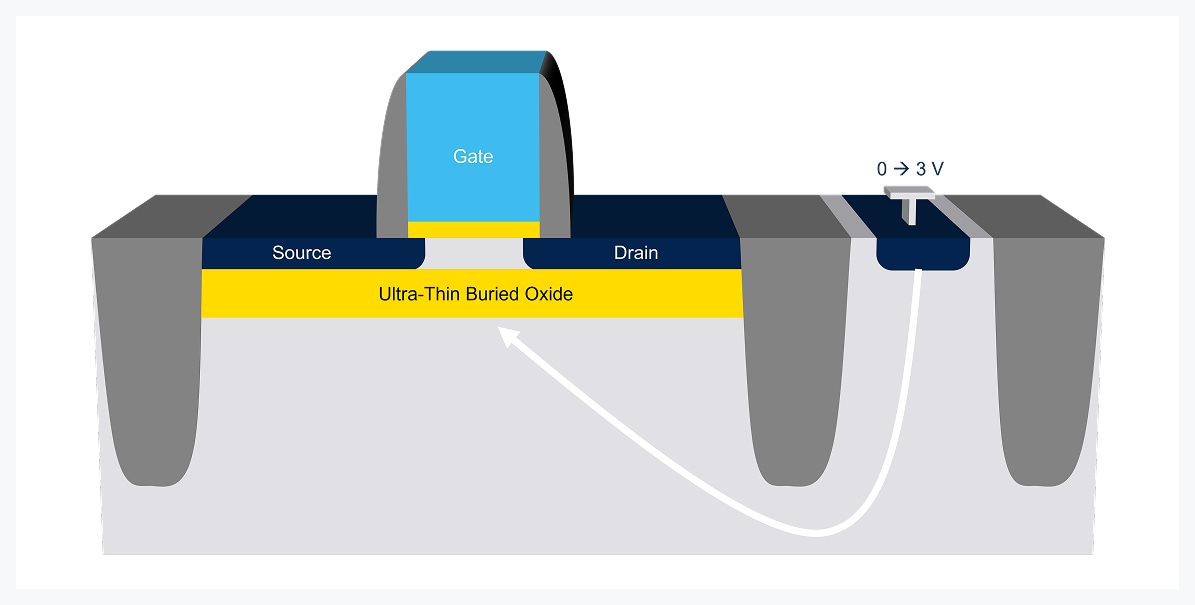

FD-SOI是一种平面工艺技术,依赖于两项主要技术创新。首先,在基底硅顶部放置一层超薄绝缘层,称为掩埋式氧化物。

接着,通过超薄的硅膜实现晶体管沟道。由于其厚度超薄,无需掺杂沟道,即可使晶体管完全耗尽。

这两项创新的结合被称为“超薄体和掩埋式氧化物全耗尽型SOI”或UTBB-FD-SOI。

Bulk与FD-SOI的对比

FD-SOI通过构造实现了比传统bulk技术更好的晶体管静电特性。

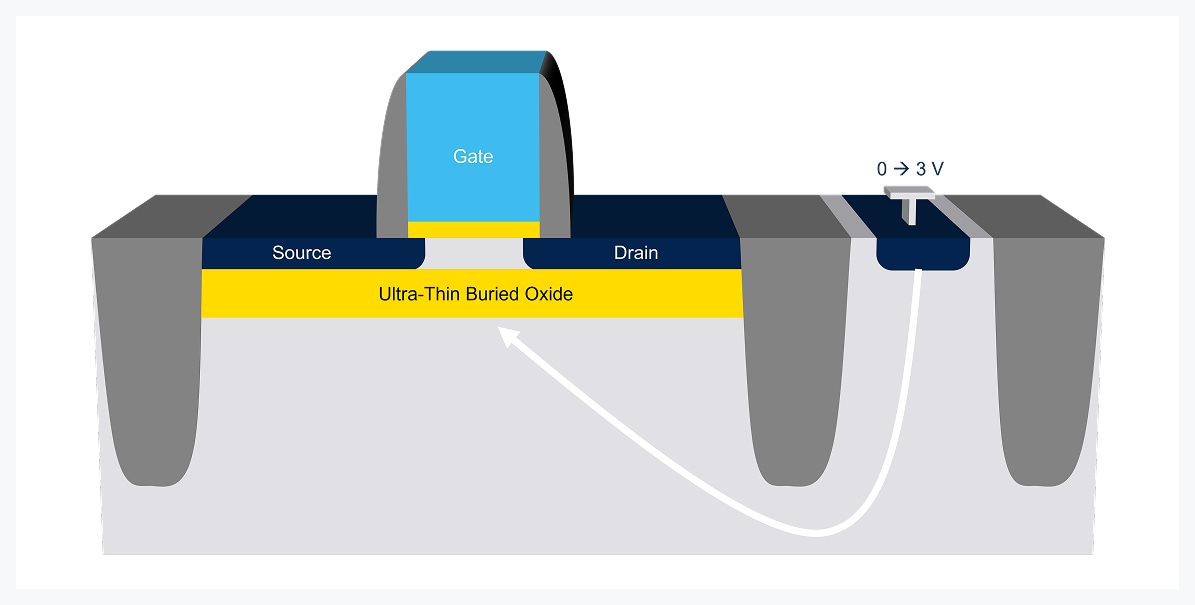

掩埋式氧化物层降低了源极和漏极之间的寄生电容,并且有效地限制了从源极流向漏极的电子,显著降低了性能下降的漏电流。

BULK

.png)

FD-SOI

.avif)

.avif)

.avif)

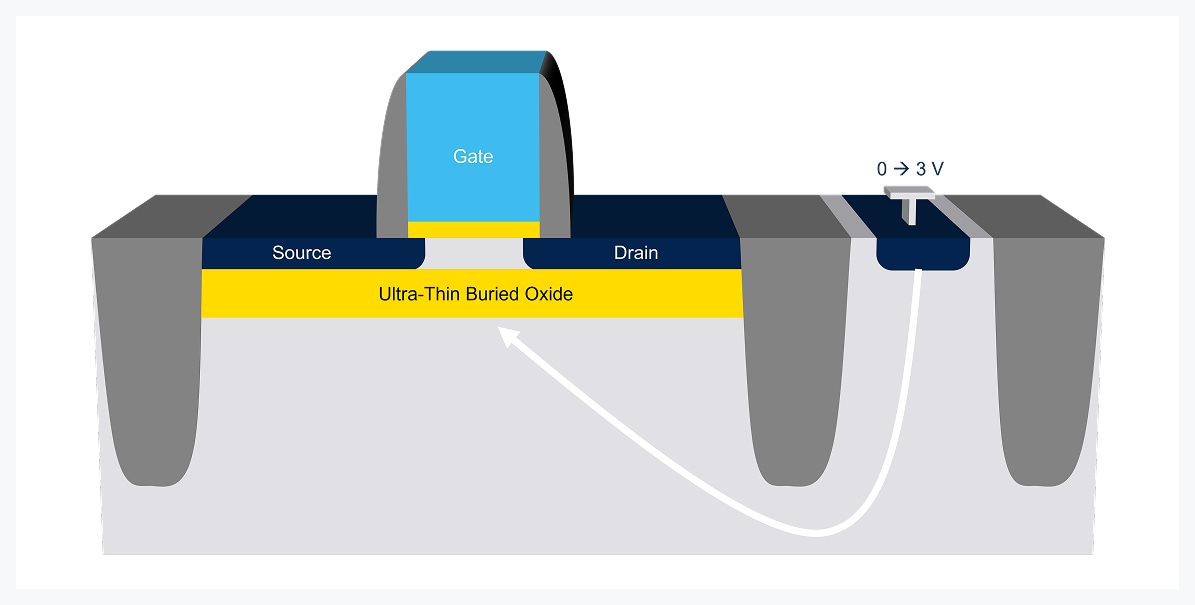

FD-SOI能实现有效的晶体管控制

在bulk技术中,由于寄生电流泄漏和晶体管几何尺寸缩减会降低效率,体偏置非常有限。全赖FD-SOI中的晶体管结构及其超薄绝缘体层,偏置效率得到了显著的提升。此外,掩埋式氧化物的存在使偏置电压得以进一步增强,从而形成了对晶体管的突破性动态控制。

当基板的极化为正时,即正向体偏置 (FBB),此时可以加快晶体管的切换速度。

由此提供了一种能够优化性能和功耗的强大技术。易于实现的FBB可在晶体管操作期间动态调制,为设计者带来极大的灵活性,从而能在需要时更快地设计电路,并在性能要求较低的场景中实现节能。

无论任何级别,均能高效表现

模拟和射频设计的优势

FD-SOI为模拟设计带来诸多优点。沟道的总介电隔离允许较低的栅极电容和漏电流,以及锁存抗扰性。此外,与bulk技术相比,全耗尽型晶体管中不存在沟道掺杂和口袋型离子注入,因此产生的噪声更低,且增益更高(高达+15dB)。

最终,这些特性都将转化为更小巧、更简单的模拟电路,在更低的工作功率下具有更高的性能。

卓越的功率效率

FD-SOI中改进的静电特性和介电隔离带来了两大主要优势。首先,可在低电压下维持具有竞争力的运行速度。其次能实现更有效的体偏置,提供对沟道的深度控制,并能优化被动和动态功耗。

存储器优势

FD-SOI与意法半导体获得专利的“单阱”位单元架构相结合,极大地提高了SRAM存储器性能,能够在低电压和极低泄漏下运行,同时保持与传统bulk SRAM相似的读/写速度。

FD-SOI技术平台

意法半导体为28 nm FD-SOI的设计提供了广泛的支持,使设计者得以使用各种关键设计模块。