Product overview

描述

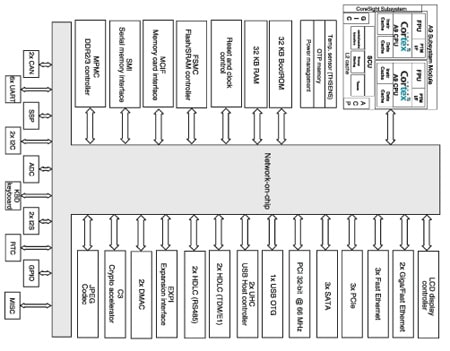

The SPEAr1310 is a member of the SPEAr family of embedded MPUs for network devices.

It offers an unprecedented combination of processing performance and aggressive power reduction control for next-generation communication appliances.

The SPEAr1310 is based on ARM's new multi-core technology (Cortex-A9 SMP/AMP) and it is manufactured with ST's 55nm HCMOS low power silicon process.

SPEAr1310 targets cost and power sensitive networking applications for the home and small business as well as telecom infrastructure equipment, with lowest overall leakage under real operating conditions. The device integrates ARM's latest generation ARMv7 CPU cores, ST's proven C3 security coprocessor, and advanced connectivity interfaces and controllers.

-

All features

- CPU subsystem:

- 2x ARM Cortex A9 cores, up to 600 MHz

- Supporting both symmetric (SMP) and asymmetric (AMP) multiprocessing

- 32+32 KB L1 Instructions/Data cache per core with parity check

- Shared 512 KB L2 cache (ECC protected) with parity check

- Accelerator coherence port (ACP)

- Bus: 64-bit multilayer network-on-chip

- Memories:

- 32 KB BootROM

- 32 KB internal SRAM

- Multi-port controller (MPMC) for external DDR2-800/DDR3-1066 with 16/32 bits datapath, up to 1GB addressable with ECC option for SEC/DED

- Controller (FSMC) for external NAND Flash, parallel NOR Flash and asynchronous SRAM

- Controller (SMI) for external serial NOR flash

- Connectivity:

- 2x Giga/Fast Ethernet ports (for external GMII/RGMII/MII PHY)

- 3x Fast Ethernet (for external SMII/RMII PHY)

- 3x PCIe 2.0 links (embedded PHY)

- 3x SATA gen-2 host port

- 1x 32-bit PCI expansion bus (up to 66 MHz)

- 2x USB 2.0 host ports with integrated PHYs

- 1x USB2.0 OTG port with integrated PHY

- 2x CAN 2.0 a/b interfaces

- 2x TDM/E1 HDLC controllers with 256/32 time slots per frame respectively

- 2x HDLC controllers for external RS485 PHYs

- 2x I2S ports for external audio/modem

- 6x UARTs (up to 5 Mbaud)

- 1x SSP port (SPI and other protocols), master/slave, up to 41 Mbps

- 2x I2C ports master/slave

- Integrated support for external peripherals:

- TFT LCD controller, up to 1920 x 1200 (60 Hz), 24 bpp

- Touchscreen I/F (4-wire resistive)

- 9 x 9 keyboard controller

- Memory card interface (MCIF) supporting SD/SDIO 2.0, SDHC, MMC 4.2/4.3, CF/CF+ Rev 4.1, XD

- Expansion interface (EXPI)

- Security: C3 cryptographic accelerator

- 13x timers and 1x real time clock

- Miscellaneous functions:

- 2x high-performance 8-channels DMA controllers

- JPEG HW codec

- 10 bit ADC, up to 1 Msps, 8 inputs with autoscan capability

- Programmable bidirectional GPIO signals with interrupt capability

- 510 + 209 one time programmable (OTP) bits

- Embedded sensor for junction temperature monitoring

- JTAG-PTM (debugging and test interface)

- Power saving features:

- Power islands for leakage reduction

- IP clock gating for dynamic power reduction

- Dynamic frequency scaling

- CPU subsystem: