## STM32MP13x 系列硬件开发入门

## 引言

本应用笔记展示了如何使用 STM32MP13x 微处理器（MPU）。其中介绍了基于这些产品开发应用程序所需的最少硬件资源。本应用笔记提供了开发板特性硬件实现概述。它着重介绍以下方面：电源，封装选择，时钟管理，复位控制，启动模式设置和调试管理。

本应用笔记还包括了参考设计原理图。它们包括对主要元件、接口和模式的描述。

表 1. 适用产品

| 类型   | 产品线                                |

|------|------------------------------------|

| 微控制器 | STM32MP131, STM32MP133, STM32MP135 |

# 1 概述

本文档适用于基于 STM32MP13x Arm® 的 MPU。

注意 **Arm** 是 **Arm Limited** (或其子公司) 在美国和/或其他地区的注册商标。

表 2. 参考文档

| -    | 参考     | 标题                                       |

|------|--------|------------------------------------------|

| [1]  | AN2867 | STM8AF/AL/S、STM32 MCU 和 MPU 的振荡器设计指南     |

| [2]  | AN1709 | STM8、STM32 和传统 MCU 的 EMC 设计指南            |

| [3]  | AN5105 | 基于 STM32 微控制器的触摸感应控制入门                   |

| [4]  | AN4316 | 在 MCU 上调谐触摸传感应用                          |

| [5]  | AN5275 | STM32MP1 系列自举程序中使用的 USB DFU/USART 协议     |

| [6]  | AN5168 | STM32MP1 系列 MPU 的 DDR 配置                 |

| [7]  | AN5587 | 在壁式适配器电源上集成 STM32MP13x 系列和 STPMIC1       |

| [8]  | AN5592 | STM32MP13x 系列 DDR 存储器布线指南                |

| [9]  | AN5585 | 在电池供电的应用中集成 STM32MP13x 系列和 STPMIC1       |

| [10] | AN5586 | STM32MP13x 系列分立电源硬件集成                    |

| [11] | AN4879 | USB 硬件和 PCB 指南 (使用 STM32 MCU)            |

| [12] | UM2993 | STM32MP135F-DK 探索板用户手册                   |

| [13] | RM0475 | 基于 Arm 的 STM32MP13x 高级 32 位 MPU          |

| [14] | DSXXXX | STM32MP13xA/Dxx 数据手册                     |

| [15] | DSXXXX | STM32MP13xC/Fxx 数据手册                     |

| [16] | ES0539 | STM32MP131x STM32MP133x STM32MP135x 勘误手册 |

表 3. 术语表

| 缩略语     | 说明                                         |

|---------|--------------------------------------------|

| ADC     | 模数转换器                                      |

| AHB     | 高级高性能总线                                    |

| AXI     | 高级可扩展接口 (通过扩展, 基于 AXI 的互连矩阵)               |

| AXIM    | AXI 矩阵 (基于 AXI 的互连)                        |

| AXIMC   | AXI 矩阵配置控制                                 |

| BKPSRAM | 备份 SRAM                                    |

| BSEC    | 启动和安全控制器 (OTP 接口)                          |

| CEC     | 消费电子控制 (HDMI 标准的一部分)                       |

| CNT     | 通用定时器 (位于 Cortex®-A7 内)                    |

| CRYP    | 加密外设, 支持 DES、三重 DES 和 AES                  |

| CSI     | 低功耗内部振荡器                                   |

| CTI     | 交叉触发接口                                     |

| DAP     | 调试访问端口                                     |

| DCMI    | 数字相机接口 (并行接口)                              |

| DDRCTRL | 双数据速率 SDRAM 控制器, 支持 LPDDR2 和 DDR3/DDR3L 协议 |

| 缩略语      | 说明                                           |

|----------|----------------------------------------------|

| DDRPERFM | DDR 性能监测器, 链接到 DDRCTRL                       |

| DDRPHYC  | DDR 物理接口控制                                   |

| DFSDM    | 数字滤波器, 用于 $\Sigma\Delta$ 调制器                 |

| DLYBQS   | 用于 QUASDPI 的延迟功能块, 补偿外部信号定时以达到最高数据速率         |

| DLYBSD   | 用于 SDMMC 的延迟功能块, 补偿外部信号定时以达到最高数据速率           |

| DMA      | 直接存储器访问: 总线主控能够在外设和存储器之间或存储器之间自主地传输数据        |

| DMAMUX   | DMA 请求复用器                                    |

| ETH      | 以太网控制器                                       |

| ETM      | 嵌入式跟踪宏单元™                                    |

| ETZPC    | 增强型 TrustZone® 保护控制器, 用于配置一些外设和 ROM/RAM 保护设置 |

| EXTI     | 扩展中断和事件控制器                                   |

| FDCAN    | 具有灵活数据速率的控制器局域网络 (也可以支持时间触发的 CAN (TT))       |

| FMC      | 灵活存储控制器                                      |

| GIC      | 通用中断控制器                                      |

| GMAC     | 千兆以太网媒体访问控制器                                 |

| GPIO     | 通用输入输出                                       |

| GPU      | 图形处理单元                                       |

| HASH     | 加密哈希外设, 支持安全哈希算法 (SHA)                       |

| HDMI     | 高清多媒体接口                                      |

| HDP      | 硬件调试端口                                       |

| HSE      | 高速外部石英振荡器                                    |

| HSEM     | 硬件信号量, 有助于多处理器资源共享                           |

| HSI      | 高速内部振荡器                                      |

| I2C      | 内部集成电路接口                                     |

| I2S      | 内部集成电路音频                                     |

| IPCC     | 处理机间通信控制器                                    |

| IWDG     | 独立看门狗                                        |

| JTAG     | 联合测试行动小组 (调试接口)                              |

| LCD      | 液晶显示器                                        |

| LPTIM    | 低功耗定时器                                       |

| LSE      | 低速外部石英振荡器                                    |

| LSI      | 低速内部振荡器                                      |

| LTDC     | LDC TFT 显示控制器                                |

| MDIOS    | 管理数据输入/输出从设备, 用于控制以太网物理接口                    |

| MDMA     | 主 DMA                                        |

| MLAHB    | 多层 AHB (基于 AHB 的互连)                          |

| OTG      | USB On-The-Go, 标准 USB 接口, 能够变成主机或设备          |

| OTP      | 一次性程序存储器                                     |

| PMB      | 进程监视功能块                                      |

| PMIC     | 通过信号和串行接口提供具有很大可控性的各种平台电源的外部电源管理电路           |

| PWR      | 电源控制                                         |

| 缩略语     | 说明                                     |

|---------|----------------------------------------|

| QUADSPI | 四路数据通道串行外设接口                           |

| RCC     | 复位和时钟控制                                |

| RNG     | 随机数发生器                                 |

| RMA     | 退料分析产品生命周期状态                           |

| ROM     | 只读存储器                                  |

| RTC     | 实时时钟                                   |

| SAI     | 串行音频接口                                 |

| SDMMC   | 安全数字和多媒体卡接口，支持 SD、MMC、e.MMC™ 和 SDIO 协议 |

| SMPS    | 开关模式电源                                 |

| SPDIF   | Sony/Philips 数字接口格式                    |

| SPI     | 串行外设接口                                 |

| SRAM    | 静态随机存取存储器                              |

| STGEN   | 系统定时生成器，用于 Cortex-A7 定时器               |

| STGENC  | STGEN 控制：STGEN 的安全部分                   |

| STGENR  | TGEN 读取：STGEN 的只读部分                    |

| STM     | 系统跟踪宏单元                                |

| SWD     | 串行线调试                                  |

| SWO     | 单线输出（跟踪端口）                             |

| SYSCFG  | 系统配置                                   |

| SYSRAM  | 系统 SRAM                                |

| TAMP    | 篡改检测外设                                 |

| TEMP    | 温度传感器                                  |

| TFT     | 薄膜晶体管：LCD 技术工艺                         |

| TIM     | 定时器                                    |

| TSGEN   | 调试时间戳生成器，用于确保多核跟踪同步                    |

| TZC     | TrustZone 地址空间控制器，用于保护对 SDRAM 的访问      |

| UART    | 通用异步收发器                                |

| USART   | 通用同步/异步收发器                             |

| USB     | 通用串行总线                                 |

| USBH    | USB 主机控制器                              |

| USBPHYC | USB 物理接口控制                             |

| VREFBUF | ADC 电压参考缓冲器                            |

| WWDG    | 窗口看门狗                                  |

## 2 电源

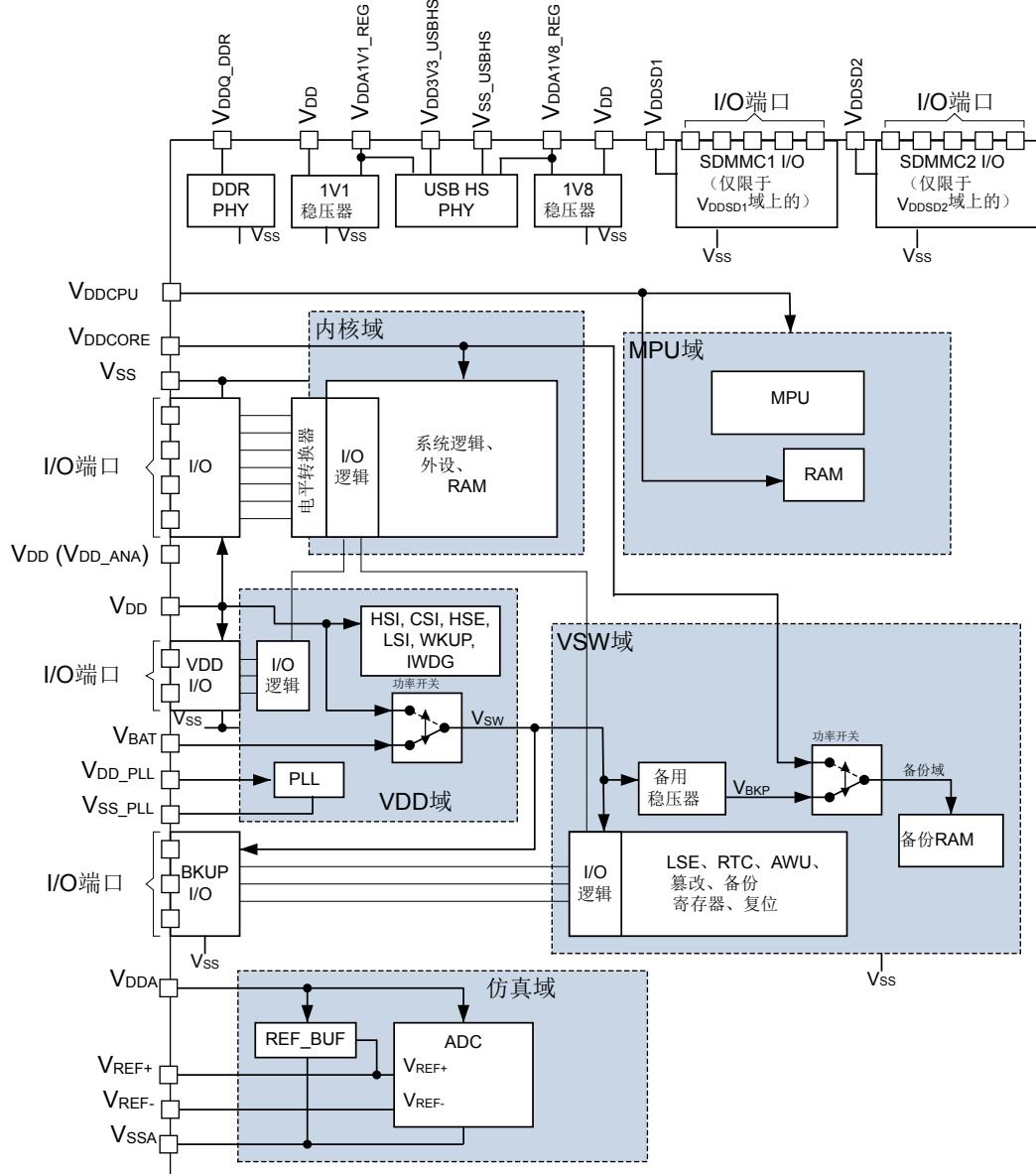

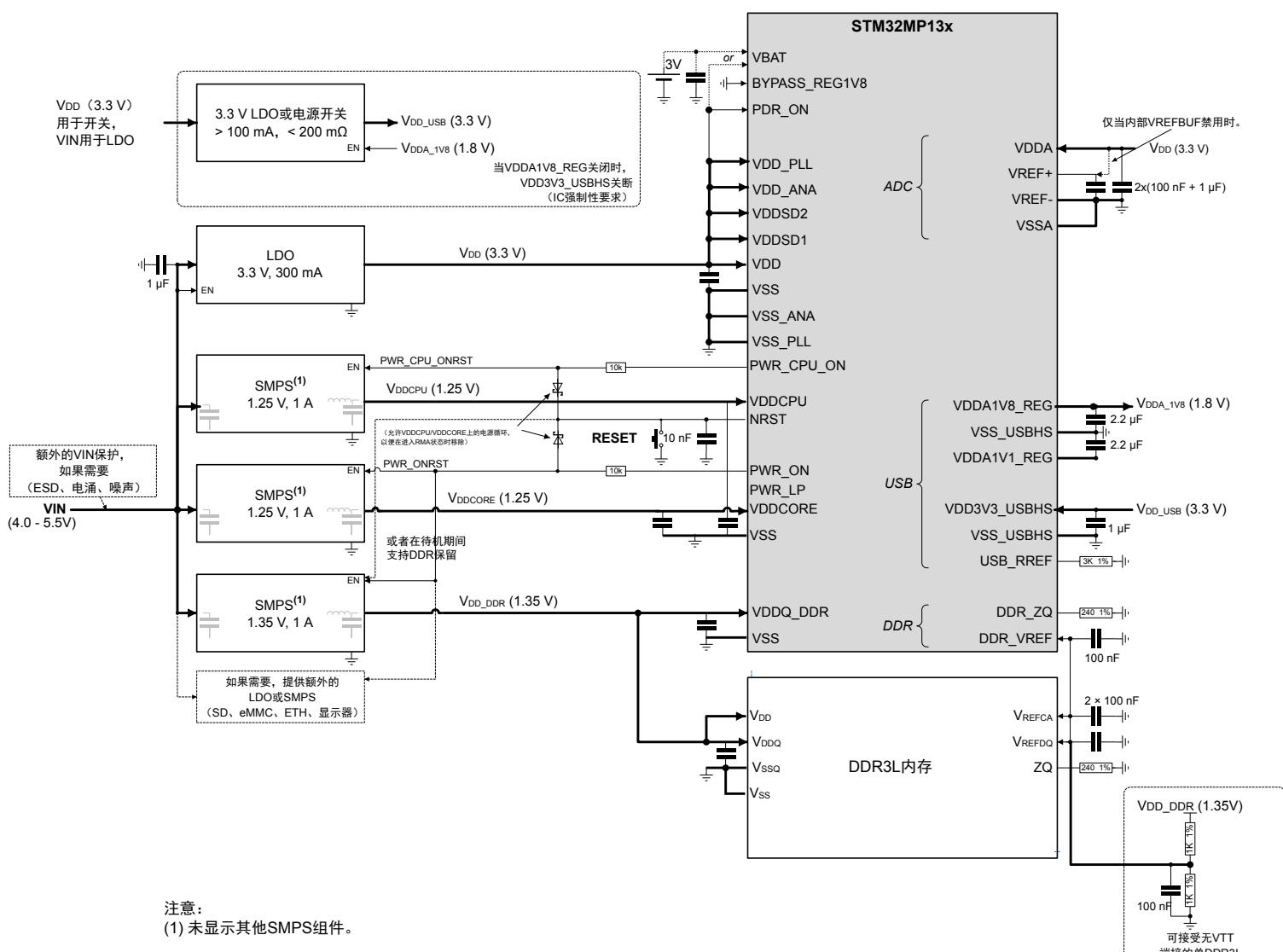

图 1. 供电方案

## 2.1 概述

STM32MP13x 电源的主要特性如下（详细信息和有保障的操作点在产品数据手册中）：

- 主 I/O 供电电压 ( $V_{DD}$ ) 范围为 1.71 V - 3.6 V。

- 核心逻辑工作电压 ( $V_{DDCORE}$ ) 范围为 1.21 V - 1.29 V。

- MPU 域工作电压 ( $V_{DDCPU}$ ) 范围：

- 1.21 V - 1.38 V (OPP 650 MHz)

- 1.32 V - 1.38 V (OPP 1000 MHz)

- USB 供电电压 ( $V_{DD3V3\_USBHS}$ ) 范围为 3.07 V - 3.6 V。

- 内置稳压器用于为一些内部模块供电：

- 面向 USB 的 1.8 V LDO 由  $VDDA1V8\_REG$  提供，用于为 USB 内部供电

当  $BYPASS\_REG1V8 = VDD$  时， $VDDA1V8\_REG$  必须从外部供电。在这种情况下，电压范围为 1.65 V 到 1.95 V。

- 面向 USB 的 1.1 V LDO 由  $VVDD1V1\_REG$  提供，用于外部解耦

注：不得使用内置稳压器为外部组件供电。

- 当主电源  $V_{DD}$  断电时，可通过  $V_{BAT}$  电压为实时时钟(RTC)和备份寄存器供电。这种可以在  $V_{BAT}$  和  $V_{DD}$  之间自动切换的内部电源被称为 VSW 域。VSW 域还用于为 PI3、PI2、PI1、PI0、PC13、PC14、PC15 引脚供电。

### 注意

由于模拟开关仅能传递有限的电流 (3 mA)，因此使用输出模式的 GPIO PI3、PI2、PI1、PI0、PC13、PC14、PC15 是受限的。频率必须限制在 2 MHz，最大负载为 30 pF，且这些 I/O 不能作为电流源使用（如，驱动 LED）。

$V_{BAT}$  的电压范围 1.20 V 到 3.6 V。

当  $V_{DD}$  高于  $V_{BAT}$  时，可在  $V_{BAT}$  引脚上为外部备用电压器件（如超级电容器）启用小充电电流。

### 2.1.1 独立 ADC 电源和参考电压

为了提高转换精度和动态范围，ADC 和参考均配有独立电源，可以单独滤波。该电源可以屏蔽 PCB 上的噪声。

模拟工作电压 ( $V_{DDA}$ ) 范围为 1.71 V - 3.6 V：

- ADC/VREFBUF 电源源从单独的  $VDDA$  引脚输入。

- $VSSA$  引脚提供了独立的电源接地连接。

在所有情况下， $VSSA$  引脚必须外部连接到相同的供电地，而不是  $VSS$ 。

### 外部 VREF

用户可以在  $VREF+$  引脚上连接一个单独的外部参考电压 ADC 输入。 $VREF+$  上的电压可能介于 1.62 V 和  $V_{DDA}$  之间。

### 内部 VREF

用户可在 VREFBUF 模块中使能  $VREF+$  上的内部参考电压。

$VREF+$  上的电压可在 1.5 V、1.8 V、2.048 V 和 2.5 V 之间选择。

有了  $VREF+$  引脚上可用的内部  $V_{REF}$ ，它可以在外部使用。如果负载保持在数据手册中的值以内，它可以用于模拟比较器参考。

VREFBUF 需要  $V_{DDA}$  等于或高于  $V_{REF+} + 0.3$  V。

### 小心

$VREF-$  引脚必须外部连接到  $VSSA$ 。

### 用于 ADC 仿真输入开关的升压器

当  $V_{DDA}$  电源低于 2.7 V 时, ADC 输入与模拟开关进行多路复用, 这样会降低性能。为最大限度地发挥 ADC 模拟性能, 可以为模拟开关提供以下电源:

- $V_{DD}$ , 如果高于 2.7 V

- 内嵌的 3.3 V 升压器 (来自  $V_{DDA}$ )。

控制是在 **SYSCFG\_PMCR** 寄存器中完成的, 如下表所示。

表 4. ANASWVDD 和 EN\_BOOSTER 的推荐设置

| $V_{DDA}$ (V) | $V_{DD}$ (V) | SYSCFG_PMCR.ANASWVDD | SYSCFG_PMCR.EN_BOOSTER | 开关电源                | ADC 仿真性能 |

|---------------|--------------|----------------------|------------------------|---------------------|----------|

| > 2.7         | 1.71 至 3.6   | 0                    | 0                      | $V_{DDA}$ (> 2.7 V) | 最大值      |

| < 2.7         | > 2.7        | 1                    | 0                      | $V_{DD}$ (> 2.7 V)  |          |

|               | < 2.7        | 0                    | 1 <sup>(1)</sup>       | 升压器 (~3.3 V)        |          |

|               |              |                      | 0 <sup>(2)</sup>       | $V_{DDA}$ (< 2.7 V) | 降低       |

1. 升压电压可能需要 50 毫秒才能稳定下来。

2. 如果可以接受 ADC 仿真性能降低, 禁用升压器最多可节省 250 mA 的电流。

### 电源解耦建议

建议采用带外部低噪声基准的  $V_{REF+}$ 。

如果通过内部 **VREFBUF** 为  $V_{REF+}$  供电, 建议使用以下解耦电容:

- 置于  $V_{REF+}$  和  $V_{REF-}/VSSA$  引脚之间: 1x 100 nF 尽可能接近, 1x 1  $\mu$ F 略微远离

- 置于  $VDDA$  和  $VSSA$  引脚之间: 1x 100 nF 尽可能接近, 1x 1  $\mu$ F 略微远离

当只能使用一个电容时, 建议保持 1  $\mu$ F, 并尽量靠近  $V_{REF+}$  和  $VDDA$  引脚。

如果  $VDDA$  用作参考电压  $V_{REF+}$ , 建议使用以下解耦电容:

- 置于  $V_{REF+}/VDDA$  和  $V_{REF-}/VSSA$  引脚之间: 1x 100 nF 尽可能接近, 1x 1  $\mu$ F 略微远离

- 当只能使用一个电容时, 建议保持 1  $\mu$ F, 并尽量靠近  $V_{REF+}$  和  $VDDA$  引脚。

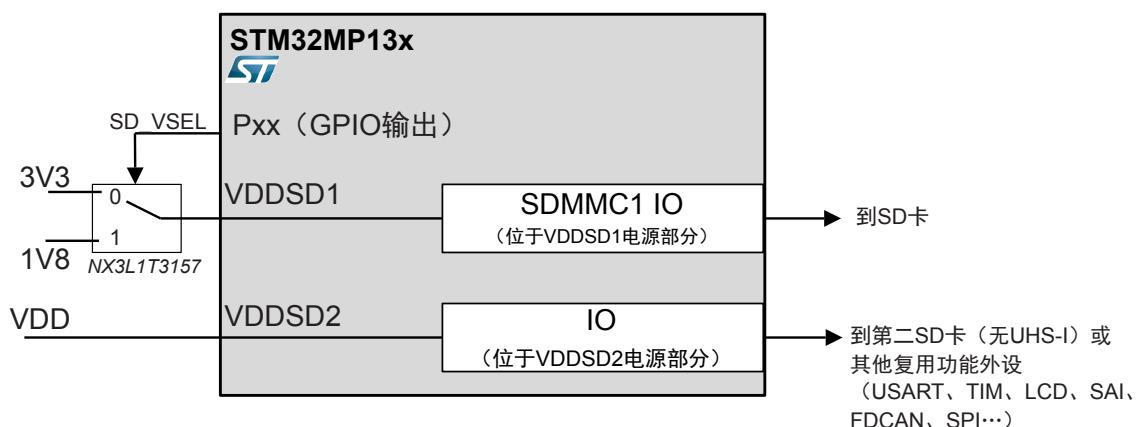

### 2.1.2 独立 I/O 电源轨

在 UHS-I 模式下使用 SD 卡时 (通过使用 I/O 的两个部分), 不需要外部分立电平转换器。IOs 由独立的  $V_{DDSD1}$  和  $V_{DDSD2}$  电源供电。

由独立  $V_{DDSD1}$  和  $V_{DDSD2}$  电源供电的 I/O 具有多个 SDMMC 信号。这些信号在相应产品的数据手册上以“VSD1”或“VSD2”后缀进行标识。VSD1 可见于 PC8、PC9、PC10、PC11、PC12 和 PD2。VSD2 可见于 PB3、PB4、PB14、PB15、PE3 和 PG6。

如果这些 I/O 上未使用 SD 卡, 或者使用了外部电平转换器, 则  $V_{DDSD1}$  和  $V_{DDSD2}$  电源可以连接到  $V_{DD}$  电源。更多详细信息, 请参见第 8.8 节: **SD-Card 无外部电平转换器**。

如果满足以下两个条件,  $V_{DDSD1}$  或  $V_{DDSD2}$  电源可以连接到  $V_{SS}$ :

- $V_{DDSD1}$  或  $V_{DDSD2}$  I/O 部分未使用 I/O

- 没有其他 GPIO > 3.6 V

通常情况下, 如果一个 5 V 容限 I/O 在 5 V 电压下有自己的输入, 则  $V_{DDSDx}$  不能被禁用或低于 1.4 V (5 V - 3.6 V)。

可以在运行期间关闭  $V_{DDSD1}$  或  $V_{DDSD2}$  电源, 而不依赖于  $V_{DD}$  的功率电平。为此, 其他 GPIO 不得 > 3.6。例如, SDMMC 上的断电重启将  $V_{DDSD1}$  设为 0, 条件如下:

- $V_{DDSD1}$  I/O 用于连接板载 SDMMC 存储器,

- 且  $V_{DDSD1}$  通过板载 SDMMC 存储器电源供电。

### 2.1.3 面向 GPIO 的 HSLV 模式和补偿单元

HSLV (高速低压) 模式可用于部分 GPIO; 当使用 1.8 V 时, 该模式可以增加 I/O 的驱动。

HSLV 模式仅可在 I/O 电源低于 2.7 V 时使用，否则会对器件造成永久损坏。

HSLVEN 位控制相关接口 I/O 的 HSLV 模式；这是独立于 I/O 电源之外完成的。SYSCFG\_HSLVEN4R 和 SYSCFG\_HSLVEN5R 分别控制 SDMMC1 和 SDMMC2 接口上所有 I/O 的 HSLV 模式。这包括由  $V_{DD}$ 、 $V_{DDSD1}$  或  $V_{DDSD2}$  供电的 IO。

对于由  $V_{DD}$  供电的 I/O，HSLV 模式由 OTP 位 (product\_below\_2V5) 进行保护。为了能够使用 HSLV 模式，OTP 位必须已经融合。由  $V_{DDSD1}$  和  $V_{DDSD2}$  供电的 I/O 不要指望那种类型的保护。

补偿单元用于控制 I/O 换向转换速率 (tfall/trise)。这样做是为了降低多个 I/O 引脚的电源的 I/O 噪音。由于补偿单元与电源相关，因此必须完成以下操作：

- 必须面向由  $V_{DD}$  供电的 I/O 对 SYSCFG\_CMPENSETR.EN 进行编程

- 必须面向由  $V_{DDSD1}$  供电的 I/O 对 SYSCFG\_CMPSD1ENSETR.EN 进行编程

- 必须面向由  $V_{DDSD2}$  供电的 I/O 对 SYSCFG\_CMPSD2ENSETR.EN 进行编程。

## 2.1.4

### 电池备份

为了在  $V_{DD}$  关闭后保留备份寄存器和 BKPSRAM 的内容，可以将 VBAT 引脚连接到电池或其它电源供电的可选备用电压。

VBAT 引脚还为 RTC 供电，因此即使当主数字供电 ( $V_{DD}$ ) 关闭时 RTC 也能工作。 $V_{BAT}$  电源的开关由复位模块中内置的下电复位 (PDR) 电路进行控制。

若应用中没有使用外部电池，则要求将 VBAT 外部连至 VDD。

## 2.1.5

### 稳压器

1.8 V LDO (用于 USB) 总是在上电复位后处于启用状态 (如果 BYPASS\_REG1V8 =  $V_{SS}$ )。进入待机状态后，它将被禁用，且 (LP/LPLV-) Stop 不会对其造成影响。

上电复位后始终使能 1.1 V LDO (用于 USB)。进入待机状态后，它将被禁用，且 (LP/LPLV-) Stop 不会对其造成影响。

(除非特别说明) 否则不得使用内置稳压器为外部组件供电。

## 2.2

### 电源方案

电路由以下电源供电：

- $V_{DD}$  是 I/O 的主电源。在待机模式期间，内部部件保持供电。有用电压范围为 1.71 V 到 3.6 V (1.8 V、2.5 V、3.0 V、或 3.3 V (典型值))。

- 这些电源必须连接到外部解耦电容 (参见表 5)。

- $V_{DD\_PLL}$  和  $V_{DD\_ANA}$  必须连接至  $V_{DD}$ 。

- $V_{DDSD1}$  和  $V_{DDSD2}$  是两个独立 I/O 部分的专用电源。电压范围与  $V_{DD}$  相同。

- 这些电源必须连接到外部解耦电容 (参见表 5)。

- $V_{DDCORE}$  是数字内核域电源。在待机模式期间，它可以从外部关断。运行模式期间的电压范围是 1.21 V-1.29 V (1.25 V 典型值)。

- 该电源必须连接到外部解耦电容 (参见表 5)。

- 可在特定停止模式 (LPLV\_Stop, LPLV\_Stop2) 下进一步减小  $V_{DDCORE}$ 。这涉及：

- PWR\_ON 信号：例如通过 STPMIC1、外部电源管理电路

- PWR\_LP 信号通过分立 SMPS 组件。

- $V_{DDCPU}$  是 MPU 域电源。在待机和 LPLV-Stop2 模式期间，它可以从外部关断。电压范围：

- 1.21 V-1.38 V (1.25 V 典型值) 最高 650 MHz

- 1.32 V-1.38 V (1.35 典型值) 高于 650 MHz。

- 该电源必须连接到外部解耦电容 (参见表 5)。

- 可在特定停止模式 (LPLV\_Stop) 下进一步减小  $V_{DDCPU}$ 。这涉及：

- PWR\_ON 信号通过 STPMIC1、外部电源管理 IC

- PWR\_CPU\_ON 和 PWR\_LP 信号通过分立 SMPS 组件

- **VBAT** 引脚可连至外部电池 ( $1.2 \text{ V} < V_{\text{BAT}} < 3.6 \text{ V}$ )。

- 如果应用不支持备用电池，则建议将该引脚连接到  $V_{\text{DD}}$ 。

- 如果应用支持备用电池，则建议在  $V_{\text{BAT}}$  和  $V_{\text{SS}}$  之间添加一个陶瓷电容。参见表 5。

- 如果应用在  $V_{\text{BAT}}$  上使用超级电容器，则不需要额外的解耦。

- **VDDA** 引脚是仿真 (ADC/VREFBUF) 电源，必须连接到外部解耦电容。请参见表 5。

- **VREF+**引脚可连至  $V_{\text{DDA}}$  外部供电电源。如果将独立的内部或外部参考电压施加到  $V_{\text{REF}+}$ 上，则必须在该引脚和  $V_{\text{REF}-}$ 之间连接解耦电容。请参见表 5 和第 2.1.1 节。

可采用更多措施过滤模拟噪声： $V_{\text{DDA}}$  可通过基于电感器的滤波器连至  $V_{\text{DD}}$ 。

- $V_{\text{DDQ\_DDR}}$  是 DDR I/O 电源，必须将其连接到外部解耦电容 (参见表 5)。

- 连接 DDR3 内存时的电压范围为  $1.425 \text{ V}$  到  $1.575 \text{ V}$  ( $1.5 \text{ V}$  典型值)。

- 连接 DDR3L 内存时的电压范围为  $1.283 \text{ V}$  到  $1.45 \text{ V}$  ( $1.35 \text{ V}$  典型值)。

- 连接 LPDDR2 或 LPDDR3 内存时的电压范围为  $1.14 \text{ V}$  到  $1.3 \text{ V}$  ( $1.2 \text{ V}$  典型值)。

- $V_{\text{DD3V3\_USBHS}}$  是 USB 高速 PHY 电源。电压范围为  $3.07 \text{ V}$ - $3.6 \text{ V}$ 。必须连接到外部解耦电容 (参见表 5)。

$V_{\text{DD3V3\_USBHS}}$  也用于为 OTG\_VBUS (PI7) 和 OTG\_ID (PA10) 引脚供电。

- $V_{\text{DDA1V8\_REG}}$  引脚是内部稳压器的输出引脚，必须将其连接到外部解耦电容 (参见)。请参见表 5。

- $V_{\text{DDA1V8\_REG}}$  从内部连接到 USB PHY 和 USB PLL。

- 默认情况下使能内部  $V_{\text{DDA1V8\_REG}}$  稳压器，可通过软件进行控制。它在待机期间始终关闭。

对于  $1.8 \text{ V}$  稳压器配置，有个特定的 BYPASS\_REG1V8 引脚必须连接到  $V_{\text{SS}}$  或  $V_{\text{DD}}$ ，以激活或禁用稳压器。当  $V_{\text{DD}}$  低于  $2.25 \text{ V}$  时，必须旁路  $1.8 \text{ V}$  稳压器：

- 如果  $\text{BYPASS\_REG1V8} = V_{\text{DD}}$ ， $V_{\text{DDA1V8\_REG}}$  引脚必须连接到  $V_{\text{DD}}$  (如果低于  $1.98 \text{ V}$ ) 或专用的  $1.65 \text{ V} - 1.98 \text{ V}$  电源 ( $1.8 \text{ V}$  典型值)。

- 如果  $\text{BYPASS\_REG1V8} = V_{\text{SS}}$ ， $V_{\text{DD}}$  必须高于  $2.25 \text{ V}$ ，以便让  $1.8 \text{ V}$  稳压器正常工作。

## 小心

除非  $V_{\text{DDA1V8\_REG}}$  存在，否则  $V_{\text{DD3V3\_USBHS}}$  不得存在，不然会使永久损坏。对于分立元件电源实现，必须通过 **STPMIC1** 排序或外部元件来确保。

所有电源接地 ( $V_{\text{SS}}$ 、 $V_{\text{SS\_ANA}}$ 、 $V_{\text{SS\_PLL}}$ 、 $V_{\text{SS\_USBHS}}$ 、 $V_{\text{SSA}}$ ，以及  $V_{\text{REF}-}$ ) 均应与电源层连接在一起。

下表可以作为指导原则。电容器的实际数量和值可根据不同的参数 (电容器的尺寸、电容器的介电质、PCB 技术) 和使用产品电源完整性模拟的结果进行调整。

表 5. 按封装分类的解耦建议

| 电源引脚                 | 解耦点 <sup>(1)</sup>   | 值 <sup>(2)</sup>      | TFBGA289<br>(9 x 9) | TFBGA320<br>(11 x 1) | LFBGA289<br>(14 x 14) | 注释                                  |

|----------------------|----------------------|-----------------------|---------------------|----------------------|-----------------------|-------------------------------------|

| VBAT                 | VSS                  | 100 nF <sup>(3)</sup> | 1                   | 1                    | 1                     | 如果 VBAT 连接至 VDD 或使用超级电容器替代电池，则可以忽略。 |

| VDDCORE              | VSS                  | 1 μF                  | 8                   | 8                    | 8                     | 不包括 PMIC/SMPS 上的电容                  |

| VDDCPU               | VSS                  | 1 μF                  | 7                   | 7                    | 7                     | 不包括 PMIC/SMPS 上的电容                  |

| VDDQ_DDR             | VSS                  | 1 nF                  | 7                   | 7                    | 6                     | 不包括 PMIC/SMPS 上的电容和 DDR 内存上的附加电容    |

|                      |                      | 1 μF                  | 3                   | 3                    | 3                     |                                     |

| VDD_ANA              | VSS_ANA              | 1 μF                  | 1                   | 1                    | 1                     | -                                   |

| VDD_PLL,<br>VDD_PLL2 | VSS_PLL,<br>VSS_PLL2 | 1 μF                  | 2                   | 2                    | 2                     | 不包括 PMIC/SMPS 上的电容                  |

| VDD                  | VSS                  | 1 μF                  | 4                   | 4                    | 4                     |                                     |

| VDDSD1/VDDSD2        | VSS                  | 1 μF                  | 1/1                 | 1/1                  | 1/1                   |                                     |

| VDDA1V8_REG          | VSS_USBHS            | 2.2 μF                | 1                   | 1                    | 1                     | -                                   |

| VDDA1V1_REG          |                      |                       |                     |                      |                       |                                     |

| VDD3V3_USBHS         |                      |                       |                     |                      |                       |                                     |

| VDD3V3_USB           | VSS                  | 1 μF                  |                     |                      |                       |                                     |

| VDDA                 | VSSA                 | 100 nF +<br>1 μF      | 1+1                 | 1+1                  | 1+1                   | VSSA 必须连接到 VSS 层。                   |

| VREF+                | VREF-和<br>VSSA       |                       |                     |                      |                       | VREF-必须先连接到 VSSA，然后连接到 VSS 平面。      |

1. 所有 VSS\_X 和 VSSA 均必须连接到公共 VSS 平面。

2. 所有 μF 电容器均为 MLCC (多层陶瓷)。

3. 上升时间应该小于 33 us/V。

表 6. 提供未使用功能的用法

| 电源           | 通常的连接                        | 可能的连接        | 引脚或功能 <sup>(1)</sup> | 相关功能块      |

|--------------|------------------------------|--------------|----------------------|------------|

| VDD3V3_USBHS | 专用的 3.3 V 供电                 | 开路或 VSS      | USB_DP1/DM1 引脚       | USBH       |

|              |                              |              | USB_DP2/DM2 引脚       | OTG 或 USBH |

| VDD3V3_USB   | 专用的 3.3 V 供电                 | 开路或 VSS      | USB_DP1/DM1 引脚       | USBH       |

|              |                              |              | USB_DP1/DM1 引脚       | OTG 或 USBH |

| VDDA1V1_REG  | (解耦电容)                       | 开路           | PA10 引脚作为 OTG_HS_ID  | OTG        |

|              |                              |              | USB_DP1/DM1 引脚       | USBH       |

| VDDA1V8_REG  | 解耦电容或专用的 1.8 V 电源或 VDD 1.8 V | 开路           | USB_DP2/DM2 引脚       | OTG 或 USBH |

|              |                              |              | USB_DP1/DM1 引脚       | USBH       |

| VDDA         | 专用电源或 VDD                    | 开路、VSS 或 VDD | ADC 内部通道             | ADC1/ADC2  |

|              |                              |              | ADCx_INxx 引脚         | ADC1/ADC2  |

|              |                              |              | VREFBUF 的用法          | VREFBUF    |

|              |                              |              | VREF+ 引脚             | ADC        |

| 电源     | 通常的连接                                           | 可能的连接 | 引脚或功能 <sup>(1)</sup>                       | 相关功能块               |

|--------|-------------------------------------------------|-------|--------------------------------------------|---------------------|

| VDDSD1 | VDD 或专用动态电源 (3.3 V - 1.8 V) 面向 SD-Card UHS-I 模式 | VDD   | PC[12:8], PD[2]引脚 <sup>(2)</sup>           | SDMMC1 和其他 AFmux 函数 |

| VDDSD2 | VDD 或专用动态电源 (3.3 V - 1.8 V) 面向 SD-Card UHS-I 模式 | VDD   | PB[15, 14, 4, 3]、PE3、PG6 引脚 <sup>(3)</sup> | SDMMC2 和其他 AFmu 函数  |

1. 只有在不使用所有相关引脚/功能时才可能的连接。

2. 如果这些引脚不使用, VDDSD1 必须连接到 VDD。

3. 如果这些引脚不使用, VDDSD2 必须连接到 VDD。

## 2.3 复位和电源监控

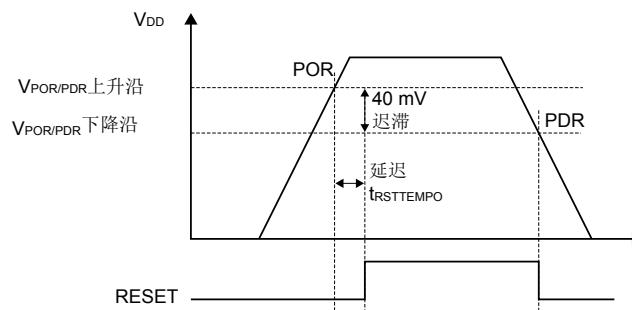

### 2.3.1 上电复位 (POR)/下电复位 (PDR)

本器件内部集成有 POR/PDR 电路, 可以从 1.71 V 开始正常工作。

当  $V_{DD}$  低于指定阈值  $V_{POR/PDR}$  时, 器件无需外部复位电路便会保持复位状态。

有关上电/下电复位阈值的相关详细信息, 请参见产品数据手册的电气特性部分。

图 2. 上电复位/下电复位波形

注意:  $t_{RSTTEMPO}$  大约2.6毫秒,  $V_{POR/PDR}$  的上升沿为1.67 V (典型值),  $V_{POR/PDR}$  下降沿为1.63 V (典型值)。

请参考产品数据手册以获取确切值。

内部 POR/PDR 电路可以通过 PDR\_ON 引脚禁用。在这种情况下, 外部供电监控器必须监控  $V_{DD}$ , 必须一直将器件保持在复位模式, 直到  $V_{DD}$  高于指定门限。

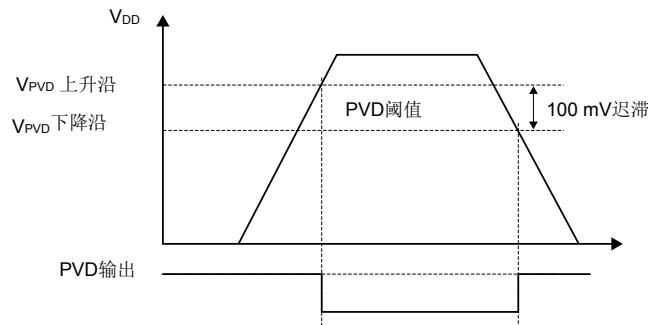

### 2.3.2 可编程电压检测器 (PVD)

用户可以使用 PVD 监视  $V_{DD}$  电源, 将其与阈值进行比较。阈值可以由电源控制寄存器 (PWR\_CR) 中 PLS[2:0] 位选择。

通过设置 PVDE 位来使能 PVD。

电源控制/状态寄存器 (PWR\_CR) 中提供了 PVDO 标志, 用于指示  $V_{DD}$  是大于还是小于 PVD 阈值。该事件内部连接到 EXTI 线 16, 如果通过 EXTI 寄存器使能, 则可以产生中断。根据 EXTI 线 16 上升沿/下降沿的配置, 可以产生 PVD 输出中断:

- $V_{DD}$  降至 PVD 阈值以下时

- $V_{DD}$  升至 PVD 阈值以上时

- 当两种情况均出现时

该功能的用处之一就是在中断服务程序中执行紧急关闭系统的任务。

图 3. PVD 阈值

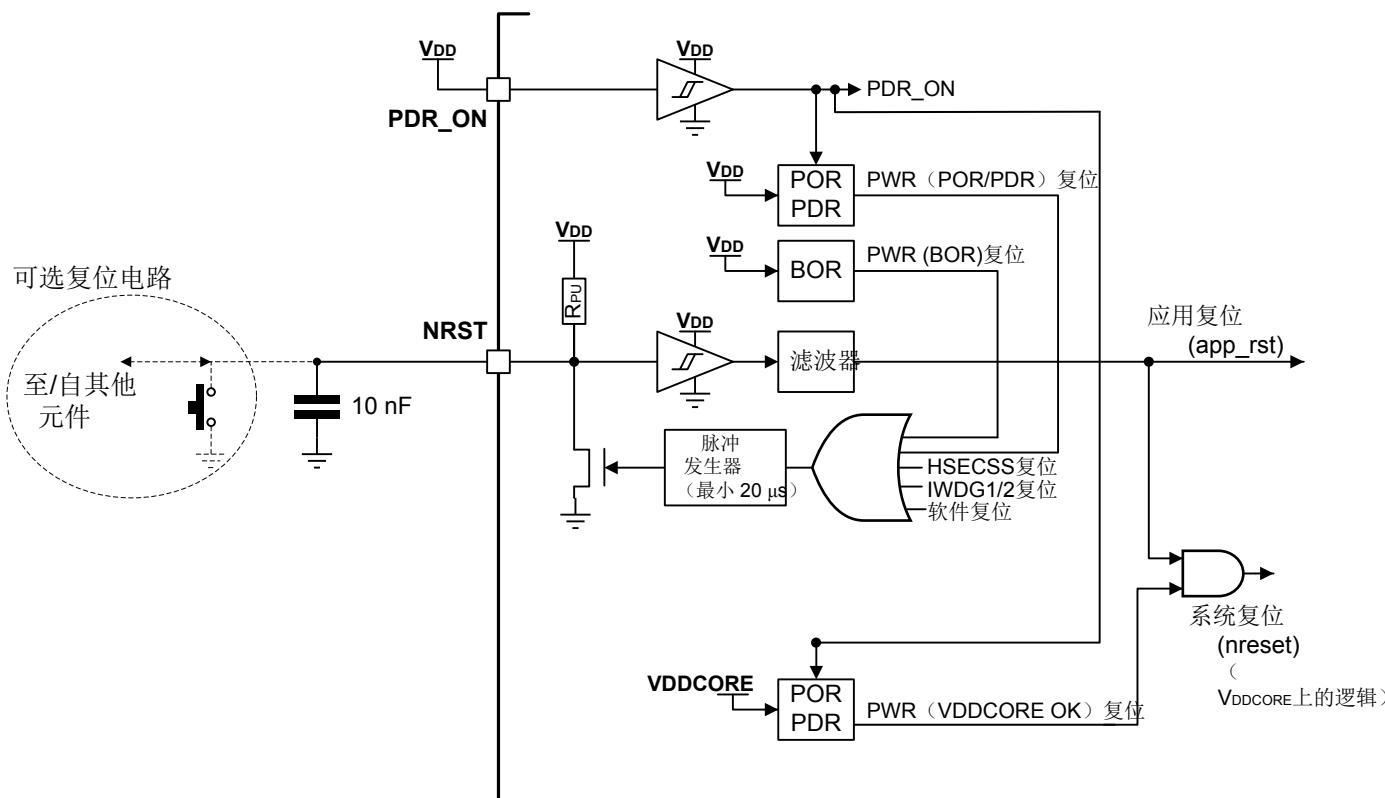

### 2.3.3 应用和系统复位

通过以下源之一产生应用复位 (app\_rst) :

- 通过 NRST 焊盘复位

- 通过 por\_rst 信号复位 (通常被称为上电复位)

- 通过 bor\_rst 信号复位 (通常被称为欠压复位)

- 通过独立看门狗 1 复位 (iwdg1\_rst)

- 通过独立看门狗 2 复位 (iwdg2\_rst)

- 当 Cortex-A7 (MPU) 将 RCC 中的 MPSYSRST 位设为“1”时，由 RCC 进行软件复位

- HSE 故障，时钟安全系统功能被激活 (hcss\_rst)

通过以下源之一产生系统复位 (nreset) :

- 通过 app\_rst 信号复位 (应用复位)

- 通过 vcore\_rst 信号复位

注意

当系统处于待机状态时， $V_{DDCORE}$  关闭，但  $V_{DD}$  仍存在。因此，当系统退出待机模式时， $vcore_rst$  信号被激活，从而产生  $nreset$  复位。

图 4. 复位引脚电路简图

## 3 封装

### 3.1 封装选择

封装选择必须考虑一些主要取决于应用的限制。

On STM32MP13x 设备：

- 所有封装都提供相同的引脚和功能（TFBGA320 11 x 11 除外，它不提供 DDR.DTO0 引脚用于 DDR DLL 测试目的）。

- 所有封装拥有 135 个 GPIO（包括在 GPIO 上复用的 3 个 BOOT 信号和 4 个 JTAG 信号）。

下面汇总了常见的一些限制：

- PCB 技术限制**

窄间距和高焊球密度可能要求更多的 PCB 层数和更高级的 PCB，这需要使用微过孔（激光过孔）技术进行层叠。

- 封装高度**

- 可用的 PCB 面积**

- 散热限制**（较大的封装具有更好的散热能力）

下表中列出的封装可用于所有 STM32MP13x 器件。

表 7. STM32MP13x 封装总览

| 封装       | 尺寸 <sup>(1)</sup> (mm x mm) | 最小间距 (mm) | 高度(mm) | 焊球数 |

|----------|-----------------------------|-----------|--------|-----|

| TFBGA289 | 9 x 9                       | 0.5       | 1.2    | 289 |

| TFBGA320 | 11 x 11                     | 0.5       | 1.2    | 320 |

| LFBGA289 | 14 x 14                     | 0.8       | 1.4    | 289 |

1. 典型主体尺寸。

## 3.2 引脚复用映射

为了更容易地探索外设复用映射，建议使用 STM32CubeMX 工具。

图 5. STM32CubeMX 示例截图

## 4 时钟

可以使用不同的时钟源驱动子系统时钟：

- HSI 振荡器时钟（高速内部时钟信号）

- CSI 振荡器时钟（低功耗内部时钟信号）

- HSE 振荡器时钟（高速外部时钟信号）

- PLL1/2/3/4 时钟

- PLL\_USB 用于产生 USB 时钟（480 MHz）

STM32MP13x 器件具有两个次级时钟源：

- 32 kHz 低速内部 RC（LSI RC）。它驱动独立看门狗，也可选择驱动 RTC（用于停止/待机模式下的自动唤醒）

- 32.768 kHz 低速外部晶振（LSE 晶振），用于驱动实时时钟(RTCCLK)

每个时钟源都可以单独打开或者在未使用时关闭。若需时钟树的说明，请参考产品参考手册。

### 4.1 HSE OSC 时钟

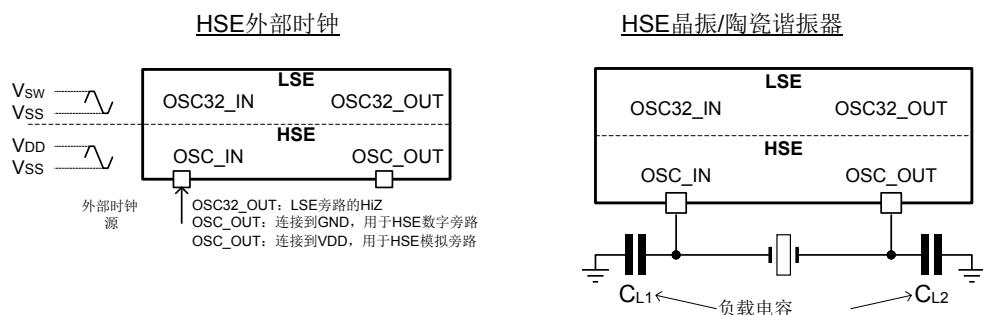

可以从 2 个可能的时钟源生成 HSE（参见下图）：

- HSE 用户外部时钟

- HSE 外部晶振/陶瓷谐振器

图 6. HSE 时钟源

下一个公式定义负载电容  $C_L$ ：

$$C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$$

其中  $C_{stray}$  为引脚电容以及与电路板或 PCB 走线相关的电容（位于 2 和 4 pF 之间（典型值），参见第 7 节：建议了解如何降低该值）。

如需更详细信息，请参考[1]。

#### 4.1.1 外部时钟源 (HSE 旁路)

在此模式下，必须提供外部时钟源。该时钟源的频率范围 8 - 50 MHz。请参考产品数据手册以获取确切的最大值。必须通过占空比约为 50% 的外部数字或模拟时钟信号来驱动 OSC\_IN 引脚。外部数字信号为  $V_{IL}/V_{IH}$ ，而模拟信号的振幅拥有 200 mV 最小峰-峰值。

注意

如要允许 USB 启动，启动 ROM 自动选择 HSE 模式。它在启动阶段检查 OSC\_OUT 连接（在 NRST 上升沿）：

- 当 OSC\_OUT 连接到 GND 时，HSE 数字旁路（ $1 k\Omega$ ，最大值）

- 当 OSC\_OUT 连接到  $V_{DD}$  时，HSE 模拟旁路（ $1 k\Omega$ ，最大值）

- OSC\_OUT 为高阻抗或连接到晶振/陶瓷谐振器：HSE 晶振/陶瓷谐振器模式

使用 HSE 旁路时，可通过 PWR\_ON 使能外部时钟发生器，以节省功耗（在待机时禁用）。在这种情况下，OSC\_IN 时钟输入必须在 PWR\_ON 上升沿产生后的 10 毫秒内保持稳定。

#### 4.1.2

#### 外部晶振/陶瓷谐振器 (HSE 晶振)

外部振荡器频率范围为 8 至 48 MHz。外部振荡器在主时钟上产生非常精确的速率。相关的硬件配置如图 6 所示。使用一个 24 MHz 的晶振频率对于得到精确的 USB 高速时钟是一个好的选择。

晶振/陶瓷谐振器和负载电容必须尽可能地靠近振荡器的引脚，以尽量减小输出失真和起振稳定时间。负载电容值必须根据所选晶振/陶瓷谐振器的不同做适当调整。

对于  $C_{L1}$  和  $C_{L2}$ ，建议使用可满足晶振/陶瓷谐振器的要求且大小介于 5 pF 到 25 pF（典型值）之间的 NP0/C0G 电容。 $C_{L1}$  和  $C_{L2}$  的大小通常相同。晶振制造商指定的负载电容通常是  $C_{L1}$  和  $C_{L2}$  的串联组合。确定  $C_{L1}$  和  $C_{L2}$  的规格时，必须将 PCB 和引脚的电容考虑在内（引脚与电路板的电容可粗略地估算为 10 pF）。

参照产品数据手册中的[1]和电气特性部分以获取更多详情。

#### 4.2

#### LSE OSC 时钟

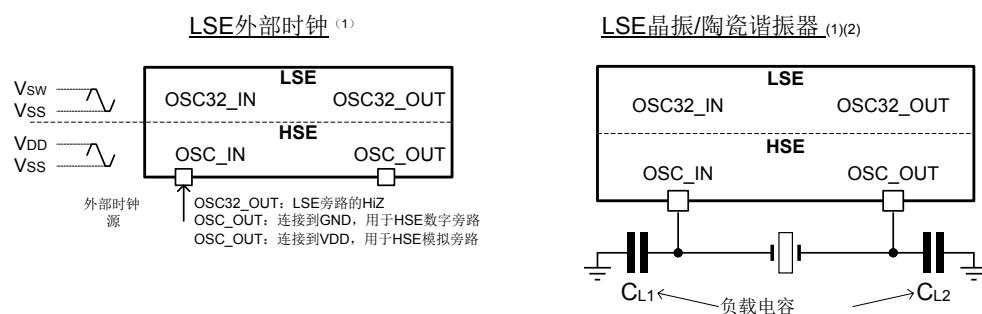

可以从 2 个可能的时钟源生成 LSE（参见下图）：

- LSE 用户外部时钟

- LSE 外部晶振/陶瓷谐振器

图 7. LSE 时钟源

(1) OSC32\_IN 和 OSC32\_OUT 引脚也可用作 GPIO，但建议在同一应用中不要既用作 RTC 又用作 GPIO 引脚。

(2) 强烈建议使用负载电容  $C_L \leq 12.5 \text{ pF}$  的谐振器。

#### 4.2.1

#### 外部时钟源 (LSE 旁路)

在此模式下，必须提供频率高达 1 MHz 的外部时钟源。必须使用占空比约为 50% 的外部数字或模拟时钟信号来驱动 OSC32\_IN 引脚，同时 OSC32\_OUT 引脚必须保持为高阻抗。外部数字信号为  $V_{IL}/V_{IH}$ ，而模拟时钟信号的振幅拥有 200 mV 最小峰-峰值。请参见图 7。旁路模式的配置以及数字和仿真之间的选择在 RCC 寄存器内完成。

#### 4.2.2

#### 外部晶振/陶瓷谐振器 (LSE 晶振)

LSE 晶振是 32.768 kHz 低速外部晶振或陶瓷谐振器。它为实时时钟外设 (RTC) 提供低功耗且精度高的时钟源，用于时钟/日历或其他定时功能。

谐振器和负载电容必须尽可能地靠近振荡器的引脚，以尽量减小输出失真和起振稳定时间。负载电容值  $C_{L1}$  和  $C_{L2}$  必须根据所选振荡器的不同做适当调整。

参照产品数据手册中的文档[1]和电气特性部分以获取更多详情。

## 4.3 时钟安全系统 (CSS) 和时钟监控

详细信息请参见产品参考手册。

### 4.3.1 HSE

可以使用 CSS 硬件检测 HSE 时钟损耗（时钟未切换）。如果 HSE 振荡器已启用，该功能在运行模式和停止模式下可用。如果在 HSE 振荡器时钟上检测到故障，则可能产生系统复位，并向 TAMP 发出信号，以进行安全保护。CSS 可以由软件激活。激活后，时钟监测器将在 HSE 振荡器启动延迟后被启用。在此振荡器停止后，时钟监测器被关闭。

HSE 过频保护是通过在超时模式下配置的安全低功耗定时器 (LPTIM3) 实现的。在 HSE 过频保护模式下，LPTIM3 将 HSE 频率与 HSI 频率进行比较。然后，如果相对频率超过编程后的限制值，LPTIM3 自动触发篡改。通过该解决方案，软件可以对相对于 HSE 标称频率的限制值进行编程，该限制值可以是范围内的任意值。

在输入相应的内部篡改输入之前，HSE 时钟损耗和 HSE 过频保护输出均为“ORed”（输入篡改输入 #4）。

### 4.3.2 LSE

使用 LSE 硬件可以检测到 LSE 时钟丢失（时钟在 200  $\mu$ s 内未切换）以及频率过高（高于 2 MHz），并生成篡改事件。这适用于所有系统模式，包括 VBAT 模式。如果在 LSE 振荡器时钟上检测到故障，则 RTC/TAMP 时钟源将停止，并向 TAMP 模块发出信号，以进行安全保护（输入篡改输入 #3）。

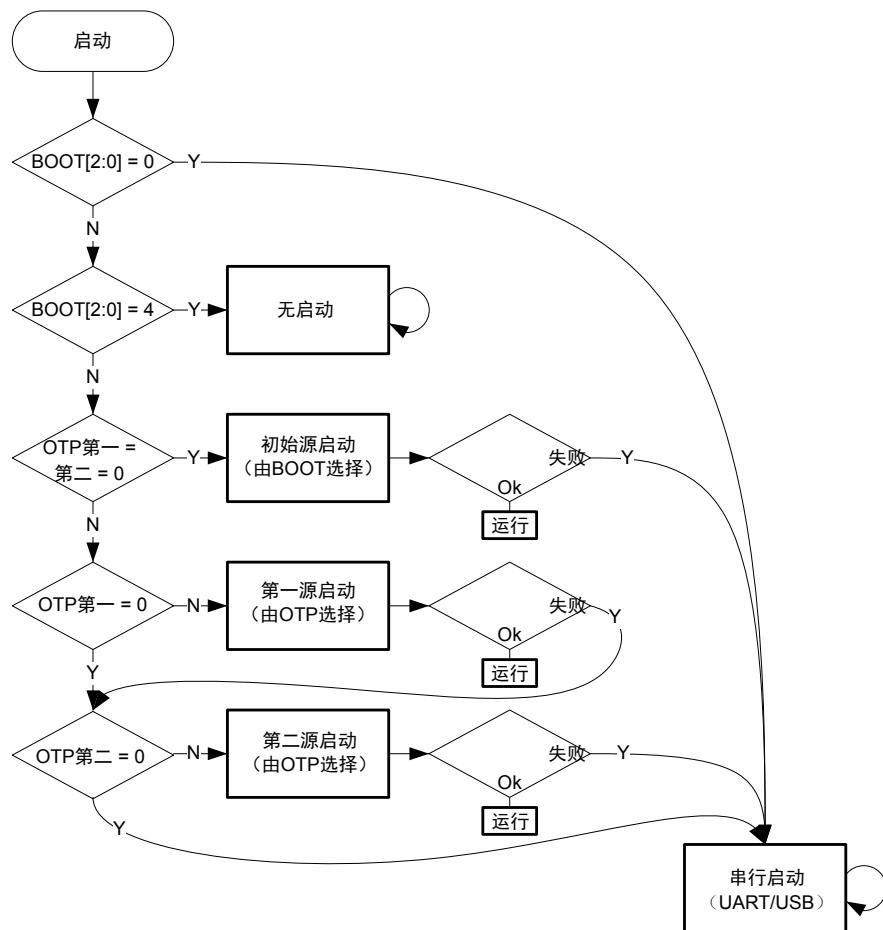

## 5 启动配置

### 5.1 启动模式选择

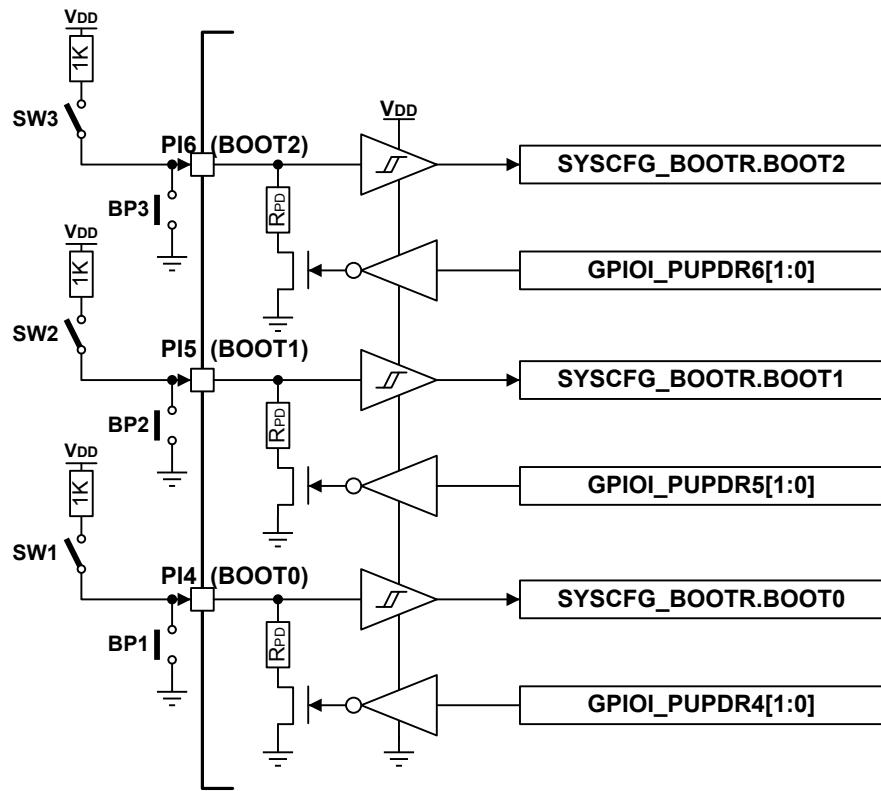

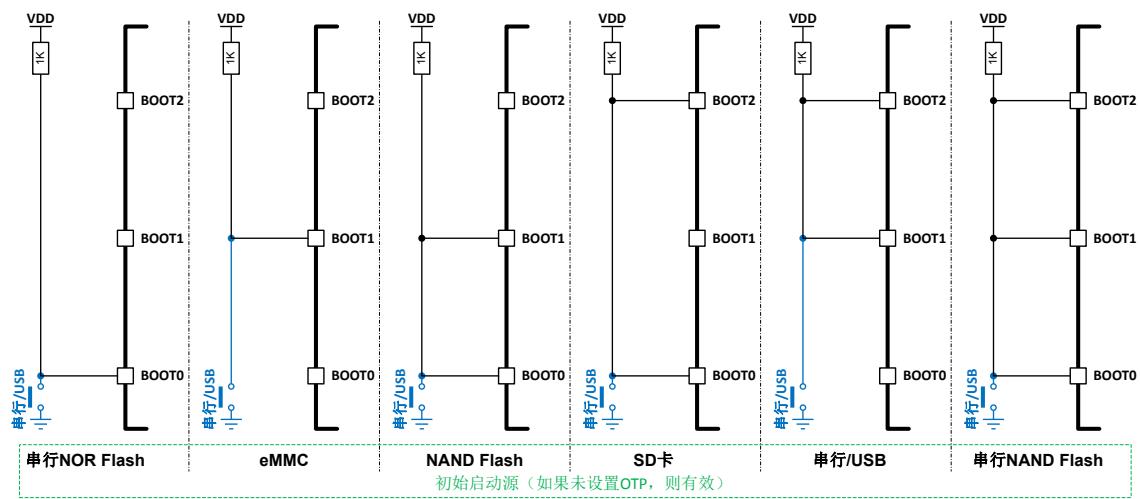

在 STM32MP13x 器件中，可通过 PI[6:4] GPIO 上的 BOOT[2:0]引脚选择不同的启动模式。

表 8. 启动模式

| BOOT2 | BOOT1 | BOOT0 | 初始启动模式                       | 注释                                                                                                                                        |

|-------|-------|-------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0     | 0     | UART 和 USB <sup>(1)</sup>    | 等待以下传入连接: <ul style="list-style-type: none"><li>默认引脚上的 USART3/6 和 UART4/5/7/8</li><li>OTG_HS_DP/DM 引脚上的 USB HS 器件<sup>(2)</sup></li></ul> |

| 0     | 0     | 1     | 串行 NOR-Flash <sup>(3)</sup>  | Quad-SPI 上的串行 NOR-Flash <sup>(4)</sup>                                                                                                    |

| 0     | 1     | 0     | eMMC <sup>(3)</sup>          | SDMMC2 上的 eMMC（默认） <sup>(4)(5)</sup>                                                                                                      |

| 0     | 1     | 1     | NAND-Flash <sup>(3)</sup>    | FMC 上的 SLC NAND-Flash                                                                                                                     |

| 1     | 0     | 0     | 工程启动（无 Flash 启动）             | 用于在不从 Flash 启动的情况下获得调试访问权限 <sup>(6)</sup>                                                                                                 |

| 1     | 0     | 1     | SD 卡 <sup>(3)</sup>          | SDMMC1（默认）上的 SD 卡 <sup>(4)(5)</sup>                                                                                                       |

|       |       |       |                              | 等待以下传入连接: <ul style="list-style-type: none"><li>默认引脚上的 USART3/6 和 UART4/5/7/8</li><li>OTG_HS_DP/DM 引脚上的 USB HS 设备<sup>(2)</sup></li></ul> |

| 1     | 1     | 1     | 串行 NAND-Flash <sup>(3)</sup> | quad SPI 上的串行 NAND-Flash <sup>(4)</sup>                                                                                                   |

- OTP 设置可对其进行禁用。请注意，即使是 UART 启动也始终需要 HSE 时钟/晶振，除非在 OTP 中禁用了 USB 和 HSE 频率自动检测。

- 如果 OTP 未针对不同频率进行编程，则 USB 需要 HSE 时钟/晶振（参见第 5.3 节：嵌入式自举模式）。

- OTP 设置可以更改启动源（例如：通过 OTP 设置，按照先 SD-Card，然后 eMMC 的启动顺序）。

- OTP 可以更改默认引脚。

- 或者，可通过 OTP 选择该默认接口以外的另一个 SDMMC 接口。

- 处于无限循环中的 Cortex-A7 Core0 切换 PA13。

系统复位（包括从待机状态退出）后，默认情况下选择 BOOT 引脚（PI[6:4]）的备用功能 AF0。可以在 SYSCFG\_BOOTR 寄存器中对 BOOT 引脚进行采样。然后，通过对相应的 GPIOx\_MODER 和 GPIOx\_PUPDR 寄存器进行编程，引脚可以用作 GPIO。

#### 重要事项

在复位期间，必须用正确的逻辑电平驱动启动引脚，以选择所需的启动源。

如果是 UART 启动，则使用可能的 U(S)ARTx\_RX 引脚之一为了避免在启动 ROM 接收并解码初始化字符之前向主机发送浮动信号，需要在相应的 U(S)ARTx\_TX 引脚上设一个 10 kΩ VDD 上拉电阻。

用于启动或系统控制台的 UART\_RX 引脚不应保持浮动，以免解码虚拟串行字符。为此，可在 uBoot/Linux 设备树中定义一个内部上拉，或者在板件上使用 10 kΩ VDD 上拉电阻。

表 9. UART 可能的启动引脚

| 外设                   | 信号 | 引脚   |

|----------------------|----|------|

| USART3               | RX | PB12 |

|                      | TX | PB10 |

| UART4 <sup>(1)</sup> | RX | PD8  |

|                      | TX | PD6  |

| UART5                | RX | PB5  |

|                      | TX | PB13 |

| USART6               | RX | PC7  |

|                      | TX | PC6  |

| UART7                | RX | PF6  |

|                      | TX | PF7  |

| UART8                | RX | PE0  |

|                      | TX | PE1  |

1. 推荐默认 UART 给 Linux 控制台 (即作为 STLINK STDC14 连接器上的 VCP)。

## 5.2 启动引脚连接

下图显示了选择 STM32MP13x 器件的启动存储器所需的外部连接示例。

PI[6:4] GPIO 上的 BOOT[2:0] 引脚在 AFmux 上复位后默认选择。

图 8. 启动模式选择

尽管具有各种软件恢复方案，但也存在 Flash 存储器内容错误或损坏，系统可能无法启动的风险。这种情况也称为‘变砖’。Flash 存储器内容错误或损坏可能是用户错误、编入坏 Flash 内容、断电等导致的。

### 注意

在空 Flash 上，启动代码会自动切换到 UART/USB 连接。

可能需要强制使用 UART/USB 连接，以对电路板 Flash 存储器进行重新编程。例如，在售后服务、固件更新后等情况下。

在一些情况下，初始启动在与常规启动不同的 Flash 上完成。可以从 SD 卡进行初始启动，这种情况下在诸如串行 NOR、串行 NAND、eMMC 或 SLC NAND 的另一个 Flash 存储器中复制二进制数据。由于初始启动代码可通过设置相关的 OTP 位来强制将来通过编程的 Flash 进行启动，因此可以实现这一功能（参见图 10）。这样就可以实现简单灵活的大规模量产，而无需干预启动引脚。

最终电路板的典型连接示例如下图中所述。

图 9. BOOT 引脚的典型连接示意图

可通过多种方式实现“开关”：按钮、焊接桥、连接器触点、测试点等。但在正常产品启动期间默认为“开路”，以避免电流流入外部电阻器。

## 5.3 嵌入式自举模式

该嵌入式自举程序位于启动 ROM 存储器中（请参见[5]获取详细信息）。

在启动期间，QUADSPI、FMC、SDMMC 和 USART 外设通过内部 64 MHz 振荡器（HSI）工作。

但是，USB OTG HS 器件只有在存在外部时钟（HSE）的情况下才能工作，默认时钟频率为 8、10、12、14、16、20、24、28、32、36、40 或 48 MHz（自动检测）。另外，固定的 24、25 或 26 MHz 频率可以与 OTP 设置一起使用。

图 10. 启动流程简图

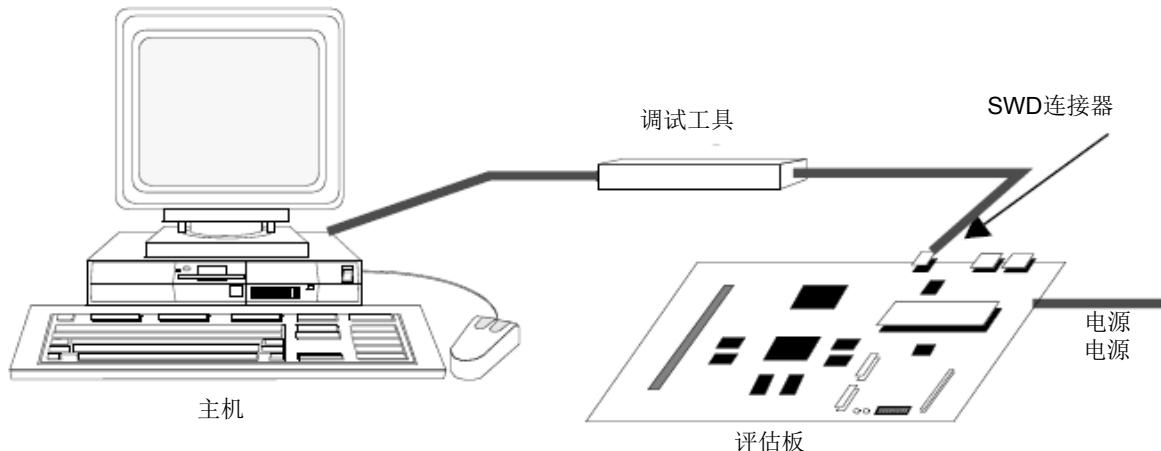

## 6 调试管理

主机/目标接口为连接主机与应用板的硬件设备。此接口由三部分组成：硬件调试工具、JTAG 或 SWD 连接器，以及连接主机与调试工具的电缆。

下图显示了主机到评估板的连接。

图 11. 主机到板的连接

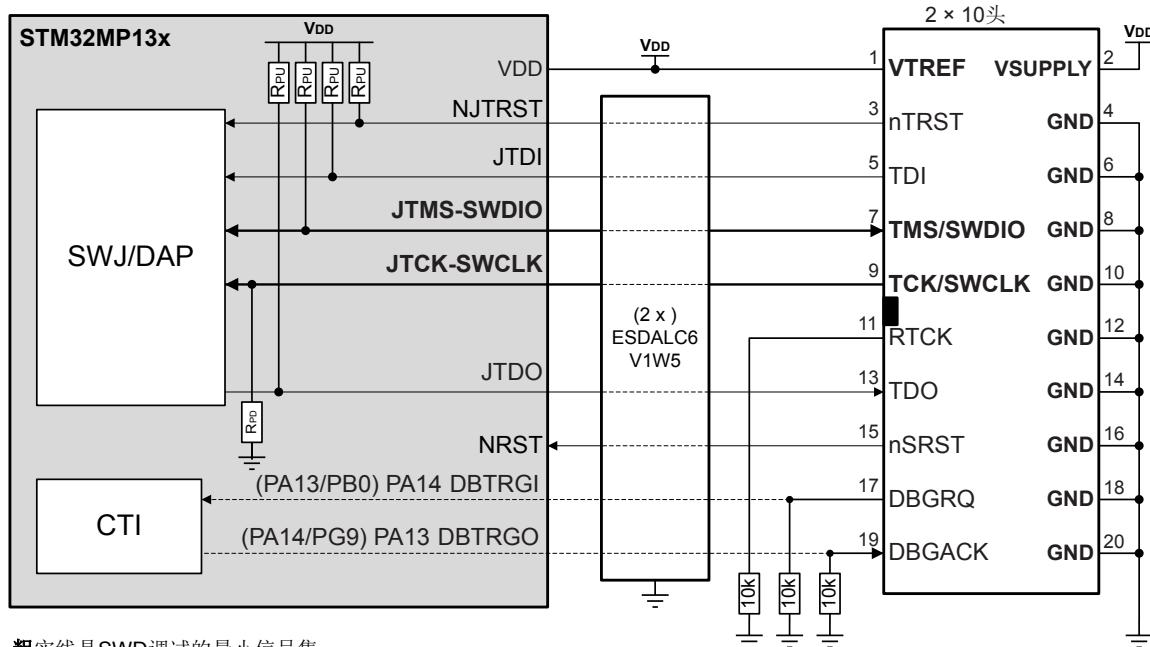

### 6.1 SWJ 调试端口（串行接口和 JTAG）

STM32MP13x 内核集成了串行/JTAG 调试端口 (SWJ-DP)。这是一个 Arm 标准 CoreSight™ 调试端口，其中组合了：

- JTAG 调试端口(JTAG-DP)提供用于连接到 AHP-AP 端口的 5 引脚标准 JTAG 接口

- 串行线调试端口(SW-DP)提供用于连接到 AHB-AP 端口的 2 引脚（时钟+数据）接口

- SW-DP 的 2 个引脚与 JTAG-DP 的 5 个 JTAG 引脚中的 2 个引脚复用。

在 STM32MP13x 器件上，在 GPIO 和 AFMux\_00 上复用的四路 JTAG 信号如下所列：

- PF14 JTCK-SWCLK

- PF15 JTMS-SWDIO

- PH4 JTDI

- PH5 JTDO

NJTRST 在专用引脚上可用。

为了使用 RMA (退料审查)，JTAG 引脚 (JTDI、JTCK、JTMS) 必须处于可访问的状态。根据用于将 JTAG 序列输入 STM32MP13x 的工具，可能需要 JTDO 引脚 (有些工具需要使用 JTDO 输出检查 JTAG ID)。

### 6.2 引脚排列和调试端口引脚

#### 6.2.1 JTAG 引脚上的内部上拉/下拉电阻

为避免 I/O 电平浮空，器件在 JTAG 引脚上内置有内部上拉和下拉电阻：

- NJTRST: 内部上拉

- JTDI: 内部上拉

- JTDO-TRACESWO: 内部上拉

- JTMS-SWDIO: 内部上拉

- JTCK-SWCLK: 内部下拉

注意

JTAG IEEE 标准建议在 TDI、TMS、nTRST 上增加上拉电阻，但对 TCK 没有特殊建议。然而，对于 STM32MP13x 器件，有一个集成的下拉电阻用于 JTCK。

由于带有上拉和下拉电阻，因此无需添加外部电阻。

## 6.2.2

## 使用标准 JTAG 连接器的调试端口连接

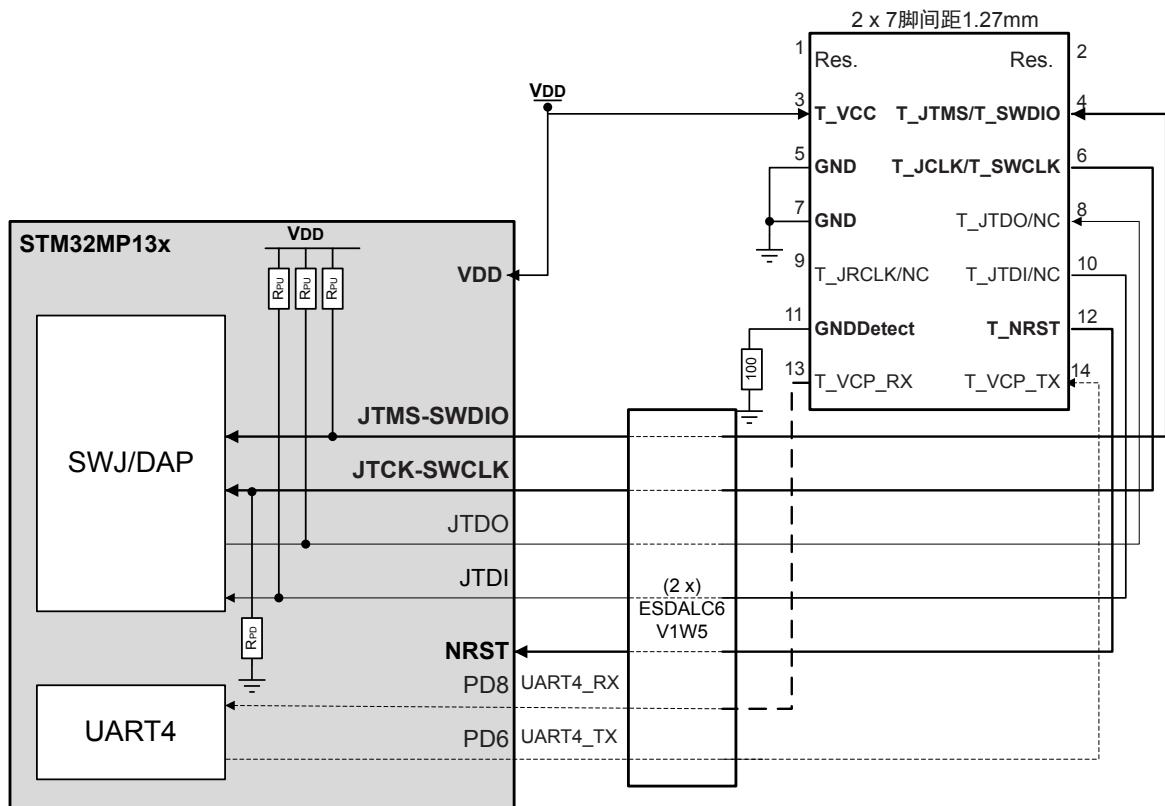

下图显示了 STM32MP13x 器件和标准 JTAG/SWD 连接器之间的连接。

图 12. JTAG/SWD MIPI10 连接器实现示例

### 6.2.3

## 使用 STDC14 连接器的调试端口和 UART 连接

下图显示了 STM32MP13x 器件与 STDC14 连接器之间的连接，包括 UART 虚拟 COM 端口连接。STDC14 头的参考示例为 FTSH-107-01-L-DV-K-A。

图 13. JTAG/SWD/UART VCP STDC14 连接器实现示例

粗实线：SWD调试的最小信号集。

## 注意

STDC14 连接器采用 (从引脚 3 到引脚 12) Arm10 引脚排列 (Arm Cortex 调试连接器)。

6.2.4

## 并行跟踪和 HDP

#### 6.2.4.1

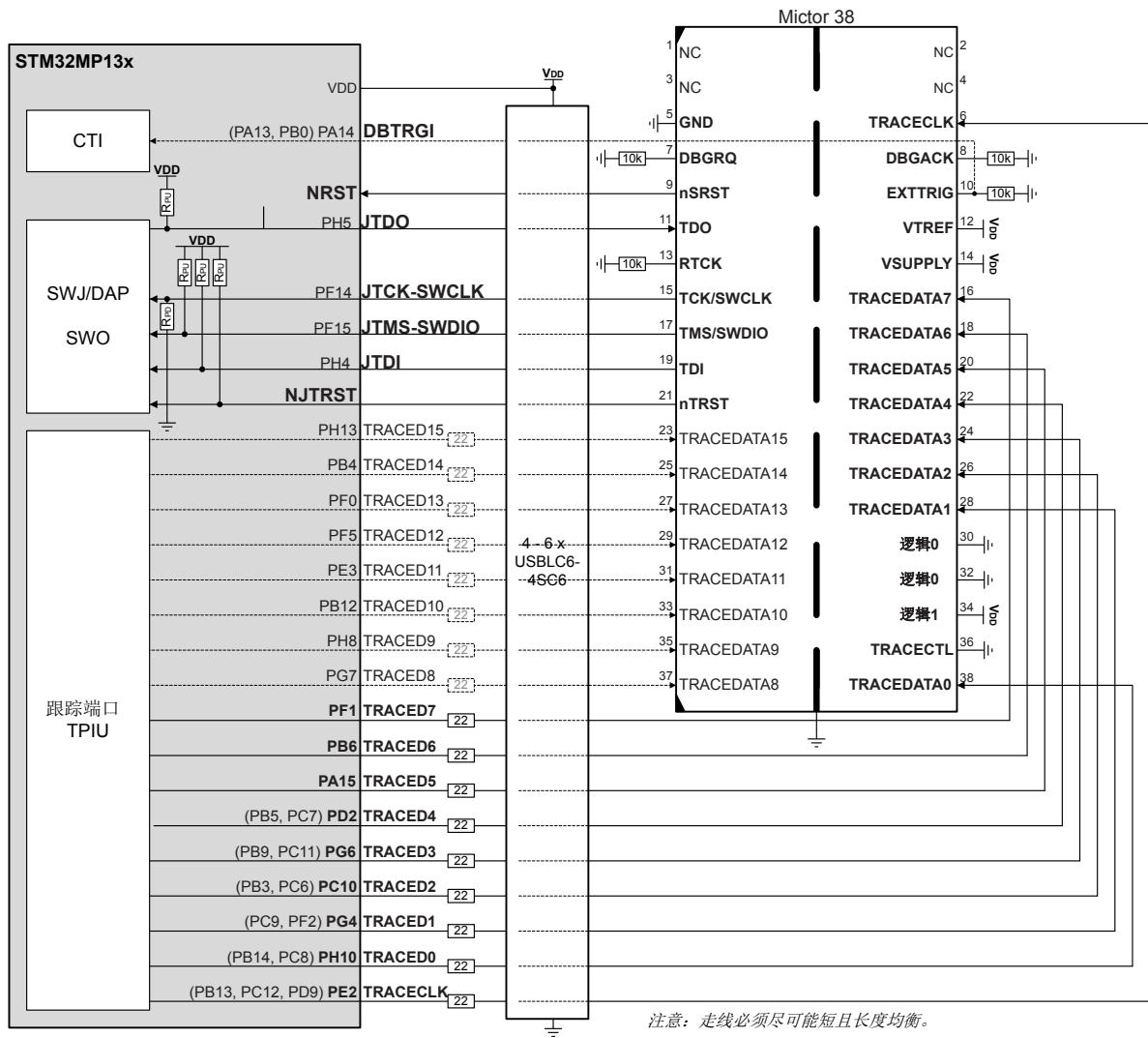

## 并行跟踪

**TRACED[15:0]** 和 **TRACECLK** 信号作为 I/O 引脚上的复用功能提供。用户可以选择跟踪数据数量  $N = 1, 2, 4, 8$  或 16 个引脚。跟踪数据越少，可用跟踪带宽越低，在不出现跟踪溢出的前提下，可跟踪的信息越少。

STM32MP13x 器件中有一个 4-Kbyte 的缓冲区。要跟踪的信息可以是跟踪源、代码和/或数据跟踪等的数量。对于每种产品，对可用功能和跟踪总线进行权衡可能会导致在产品开发过程中使用跟踪时功能变少。

此跟踪符合 Arm CoreSight 跟踪要求。此跟踪需要专用跟踪工具，以便解释和关联通过 SWD 或 JTAG 完成的调试。

有关 TPI (跟踪端口接口) CoreSight 组件的更多信息, 请参见产品参考手册和《CoreSight SoC-400 技术参考手册》。

### 注意

为了有效跟踪带宽, **TRACECLK** 必须尽可能快地运行, 同时在所有并行跟踪信号上保持良好的信号完整性。这取决于电路板和连接器选择、**GPIO** 强度设置 (**GPIO OSPEEDR** 寄存器) 和 **V<sub>DD</sub>** 电压。

使用  $V_{DD} = 1.8$  V 时, 可能需要对 OTP 位 `product_below_2v5` 和寄存器 `SYSCFG_HSLVEN0R` (`HSLVEN_TRACE` 位) 进行设置。该设置确保在用于跟踪信号的焊盘上获得最佳速度。

### 警告

当  $V_{DD}$  高于 2.7 V 时, 不得置位 UHSLVEN, 否则可能造成器件永久损坏。

图 14. Mictor-38 上带 JTAG/SWD 的并行跟踪端口实现示例

#### 6.2.4.2

## 硬件调试端口

一些内部信号可用于深度调试。需要内部知识以及示波器或逻辑分析仪。有关更多信息，请参阅产品参考手册和数据手册。

## 6.2.5

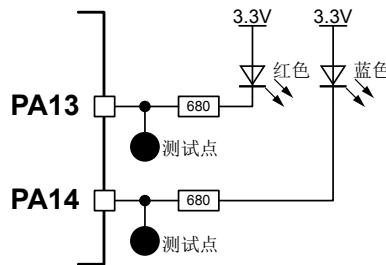

## 调试触发器和 LED

CoreSight CTI (交叉触发接口) 可在引脚上作为 DBTRGI 和 DBTRGO 使用:

- DBTRGI 引脚可以由外部用户信号生成。可以在 CoreSight 组件内编程，以便在调试模式（中断）下启动/停止跟踪或进入特定内核。DBTRGI 可在 PA13、PA14 或 PB0 上获得。

- DBTRGO 可由 CTI 生成，以便从外部查看其中一个 CoreSight 组件已达到的触发条件（内核中断、跟踪启动等）。DBTRGO 可在 PA13、PA14 或 PG9 上获得。

PA13 引脚有以下特定行为（详情请参见启动文档）：

- 在启动阶段, 如果启动失败, 则将 PA13 引脚设置为低漏极开路。此时, 即错误 LED 点亮。

- 在 UART/USB 启动期间, PA13 引脚以大约 5 Hz 的频率切换开漏, 直到连接开始。此时, 错误 LED 快速闪烁。

- 当  $\text{BOOT}[2:0] = 0b100$  (未启动, 用于特定调试), PA13 以大约 5 kHz 的频率切换漏极开路。此时, 错误 LED 发出弱光。

- 在所有其他情况下, PA13 保持其复位值 (高阻抗, 直至进行软件设置)。

如下图所示，在 PA13 上设置一个红色 LED 是个好主意。

图 15. LED 连接示例

LED 对于快速发出系统活动的视觉信号很有用。因此，使用 PA13 和 PA14 是一个不错的选择。这无法避免在 PA13 或 PA14 上使用 DBTRGI 和 DBTRGO 进行调试（假设软件在该特定调试期间停止控制 LED）。

## 7 建议

### 7.1 PCB (印刷电路板)

出于技术原因，必须使用多层印刷电路板 (PCB)，这样才能实现不错的解耦和屏蔽效果：

- 一层是对地的隔离层 (VSS)

- 另一层用于为  $V_{DD}$ 、 $V_{DDCPU}$ ，以及  $V_{DDCORE}$  等电源供电。

### 7.2 元件位置

为了减少 PCB 上的交叉耦合，PCB 的初始布局必须对不同的电路的 EMI 贡献进行区分，不同的电路包括噪声、大电流电路、低电压电路和数字部分。

### 7.3 接地和供电 ( $V_{SSx}$ 、 $V_{DDx}$ )

由于 STM32MP13x 器件中涉及大功率和高频率，必须使用具有以下特征的 PCB：

- 至少有四层

- 为  $V_{SSx}$  和  $V_{DDx}$  提供专用的电源平面。

### 7.4 I/O 速度设置

在 I/O 上设置正确的输出驱动非常重要。这样可确保足够的上升和下降时间，也可避免额外的振铃和噪声。

当对 I/O 速度没有特定要求时，必须将 OSPEEDR 设为 0。

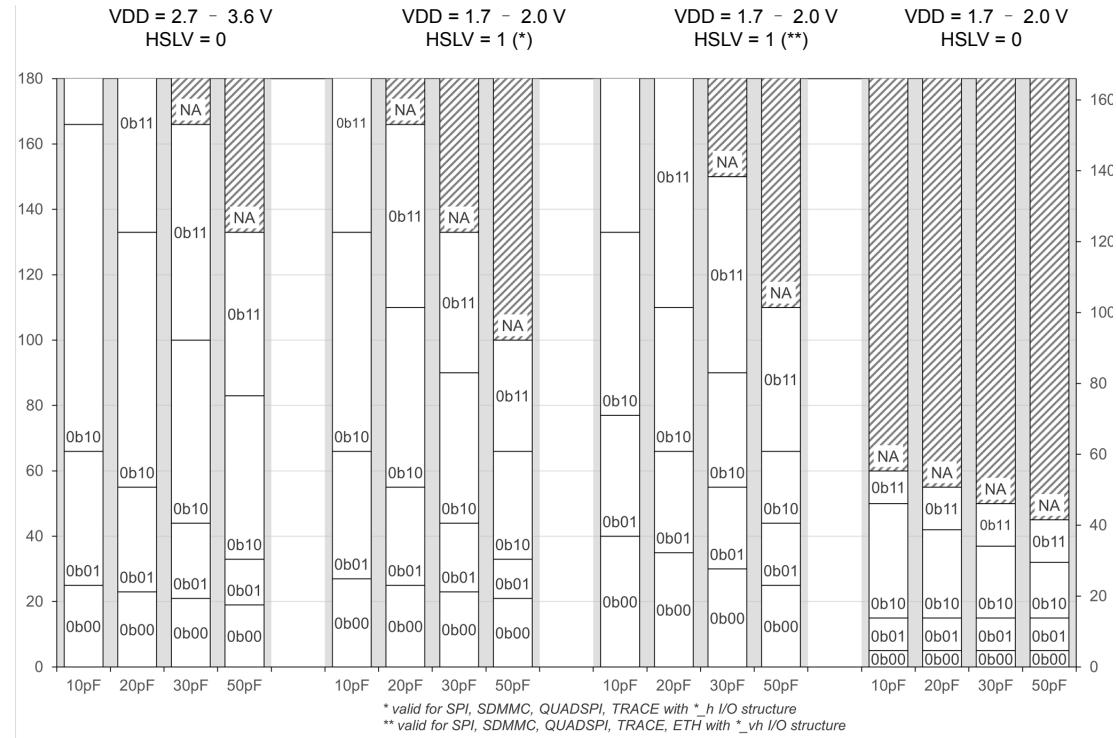

作为第一近似值，以下表格可用于根据信号频率和容性负载快速选择正确设置。如果出现信号完整性问题，该设置可能需要量身定制。

在大多数情况下，需要在 SYSCFG 中使能 I/O 补偿（有关更多详细信息，请参见产品数据手册）。

在异步或单边沿时钟数据通道（如 SDR）的情况下，最大有效数据切换频率实际上仅为数据率的一半。例如，以 10 Mbits/s 运行的 SPI 的数据信号具有 5 Mhz 的最大频率（例如，输出串行数据 01010101...），但时钟信号的最大频率为 10 MHz。在双边沿时钟数据通道（如 DDR）中，时钟和数据具有相同的最大切换频率。

对于高速接口（SDMMC、QSPI、ETH、SPI、LTDC、TRACE），必须在 I/O 电源小于 2.7 V 时启用高速低电压 (HSLV) 模式，以确保足够的转换速率。通过在对应的 SYSCFG\_HSLVENxR 寄存器中写入一个特殊的值，可以为每个接口独立启用 HSLV 模式。

#### 警告

在 I/O 电压高于 2.7 V 时启用 HSLV 模式，可能会损坏设备。

图 16. 各种负载和电压下的 I/O 速度总结

对于除 SDMMC 之外的所有接口，必须在启用 HSLV 之前对 OTP 位 `product_below_2v5` 进行编程。

表 10.  $V_{DD} = 3.3$  V 典型值时的 OSPEEDR 设置示例

| 外设                         | 信号    | 切换速率 (MHz) | OSPEEDR              |                   |                      |    |

|----------------------------|-------|------------|----------------------|-------------------|----------------------|----|

|                            |       |            | 当 $C_L = 30$ pF 时的速度 |                   | 当 $C_L = 10$ pF 时的速度 |    |

| FMC 异步                     | 数据/控制 | 50         | 2                    | 高速                | 1                    | 中速 |

| FMC 同步                     | CLK   | 100        | 2                    | 高速                | 2                    | 高速 |

|                            | 数据/控制 | 50         | 2                    | 高速                | 1                    | 中速 |

| QUADSPI (SDR)              | CLK   | 133        | 2                    | 高速 <sup>(1)</sup> | 2                    | 高速 |

|                            | 数据/控制 | 66.5       | 2                    | 高速                | 2                    | 高速 |

| QUADSPI (DDR)              | 全部    | 66.5       | 2                    | 高速                | 2                    | 高速 |

| LTDC (HDMI) <sup>(2)</sup> | CLK   | 74.25      | 2                    | 高速                | 2                    | 高速 |

|                            | 数据/控制 | 37.125     | 1                    | 中速                | 1                    | 中速 |

| LTDC <sup>(2)</sup>        | CLK   | 90         | 2                    | 高速                | 2                    | 高速 |

|                            | 数据/控制 | 45         | 2                    | 高速                | 1                    | 中速 |

| LTDC                       | CLK   | 48         | 2                    | 高速                | 1                    | 中速 |

|                            | 数据/控制 | 24         | 1                    | 中速                | 0                    | 低速 |

| TIM/LPTIM                  | 全部    | 5          | 0                    | 低速                | 0                    | 低速 |

| I2C                        | 全部    | 1          | 0                    | 低速                | 0                    | 低速 |

| USART                      | 全部    | 5          | 0                    | 低速                | 0                    | 低速 |

| SPI                        | CLK   | 50         | 2                    | 高速                | 1                    | 中速 |

| 外设          | 信号    | 切换速率 (MHz) | OSPEEDR                      |                              |   |    |

|-------------|-------|------------|------------------------------|------------------------------|---|----|

|             |       |            | 当 $C_L = 30 \text{ pF}$ 时的速度 | 当 $C_L = 10 \text{ pF}$ 时的速度 |   |    |

| SPI         | 数据/控制 | 25         | 1                            | 中速                           | 0 | 低速 |

| SAI         | MCLK  | 15         | 0                            | 低速                           | 0 | 低速 |

|             | CLK   | 1          | 0                            | 低速                           | 0 | 低速 |

|             | 数据/控制 | 0.5        | 0                            | 低速                           | 0 | 低速 |

| SDMMC (SDR) | CLK   | 130        | 2                            | 高速 (1)                       | 2 | 高速 |

|             | 数据/控制 | 65         | 2                            | 高速 (1)                       | 1 | 中速 |

| SDMMC (DDR) | 全部    | 52         | 2                            | 高速                           | 1 | 中速 |

| FDCAN       | 全部    | 5          | 0                            | 低速                           | 0 | 低速 |

| ETH (MII)   | CLK   | 50         | 2                            | 高速                           | 1 | 中速 |

|             | 数据/控制 | 25         | 1                            | 中速                           | 0 | 低速 |

| ETH (RMII)  | 全部    | 50         | 2                            | 高速                           | 1 | 中速 |

| ETH (RGMII) | 全部    | 125        | 3                            | 超高速                          | 2 | 高速 |

| ETH (MDIO)  | MDIO  | 2.5        | 0                            | 低速                           | 0 | 低速 |

| TRACE       | 全部    | 133        | 3                            | 超高速                          | 2 | 高速 |

|             |       | 100        | 2                            | 高速                           | 2 | 高速 |

1. 当  $CL = 20 \text{ pF}$  时的值。

2. 封装, 需要 HSE 外部振荡器。

表 11.  $V_{DD} = 1.8 \text{ V}$  典型值时的 OSPEEDR 设置示例

| 外设                | 信号    | 切换速率 (MHz) | OSPEEDR $C_L=30 \text{ pF}$  |                              | OSPEEDR $C_L=10 \text{ pF}$  |                              |

|-------------------|-------|------------|------------------------------|------------------------------|------------------------------|------------------------------|

|                   |       |            | 当 $C_L = 30 \text{ pF}$ 时的速度 | 当 $C_L = 10 \text{ pF}$ 时的速度 | 当 $C_L = 30 \text{ pF}$ 时的速度 | 当 $C_L = 10 \text{ pF}$ 时的速度 |

| FMC 异步            | 数据/控制 | 50         | 3                            | 超高速                          | 2                            | 高速                           |

| FMC 同步            | CLK   | 45         | 3                            | 超高速                          | 2                            | 高速                           |

|                   | 数据/控制 | 22.5       | 2                            | 高速                           | 2                            | 高速                           |

| QUADSPI (SDR) (1) | CLK   | 133        | 3                            | 超高速 (2)                      | 2                            | 高速                           |

|                   | 数据/控制 | 66.5       | 2                            | 高速                           | 2                            | 高速                           |

| QUADSPI (DDR) (1) | 全部    | 66.5       | 2                            | 高速                           | 2                            | 高速                           |

| LTDC (HDMI) (3)   | CLK   | 74.25      | 2                            | 高速 (2)                       | 2                            | 高速                           |

|                   | 数据/控制 | 37.125     | 1                            | 中速                           | 1                            | 中速                           |

| LTDC (3)          | CLK   | 69         | 2                            | 高速                           | 2                            | 高速                           |

|                   | 数据/控制 | 34.5       | 1                            | 中速                           | 1                            | 中速                           |

| TIM/LPTIM         | 全部    | 5          | 0                            | 低速                           | 0                            | 低速                           |

| I2C               | 全部    | 1          | 0                            | 低速                           | 0                            | 低速                           |

| USART             | 全部    | 5          | 0                            | 低速                           | 0                            | 低速                           |

| SPI (4)           | CLK   | 50         | 2                            | 高速                           | 1                            | 中速                           |

|                   | 数据/控制 | 25         | 1                            | 中速                           | 0                            | 低速                           |

| SAI               | MCLK  | 15         | 1                            | 中速                           | 1                            | 中速                           |

|                   | CLK   | 1          | 0                            | 低速                           | 0                            | 低速                           |

|                   | 数据/控制 | 0.5        | 0                            | 低速                           | 0                            | 低速                           |

| SDMMC (SDR) (5)   | CLK   | 130        | 3                            | 超高速 (2)                      | 2                            | 高速                           |

|                   | 数据/控制 | 65         | 2                            | 高速                           | 1                            | 中速                           |

| 外设                         | 信号    | 切换速率 (MHz) | OSPEEDR $C_L=30\text{ pF}$ |                    | OSPEEDR $C_L=10\text{ pF}$ |    |

|----------------------------|-------|------------|----------------------------|--------------------|----------------------------|----|

| SDMMC (DDR) <sup>(5)</sup> | 全部    | 52         | 2                          | 高速                 | 1                          | 中速 |

| FDCAN                      | 全部    | 5          | 0                          | 低速                 | 0                          | 低速 |

| ETH (MII)                  | CLK   | 50         | 1                          | 中速                 | 1                          | 中速 |

|                            | 数据/控制 | 25         | 0                          | 低速                 | 0                          | 低速 |

| ETH (RMII)                 | 全部    | 50         | 1                          | 中速                 | 1                          | 中速 |

| ETH (RGMII) <sup>(6)</sup> | 全部    | 125        | 3                          | 超高速 <sup>(2)</sup> | 2                          | 高速 |

| ETH (MDIO)                 | MDIO  | 2.5        | 0                          | 低速                 | 0                          | 低速 |

| TRACE <sup>(7)</sup>       | 全部    | 133        | 3                          | 超高速 <sup>(2)</sup> | 2                          | 高速 |

|                            |       | 100        | 3                          | 超高速                | 2                          | 高速 |

1. *HSLVENxR* 为了 *QUADSPI* 而启用。

2. 当  $CL=20\text{ pF}$  时的值。

3. *HSLVENxR* 为了 *LTDC* 而启用。

4. *HSLVENxR* 为了 *SPI* 而启用。

5. *HSLVENxR* 为了 *SDMMC* 而启用。

6. *HSLVENxR* 为了 *ETH* 而启用。

7. *HSLVENxR* 为了 *TRACE* 而启用。

## 7.5

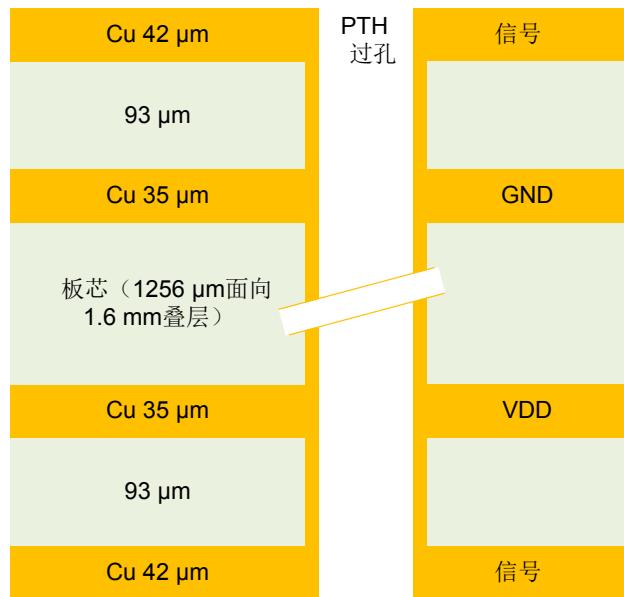

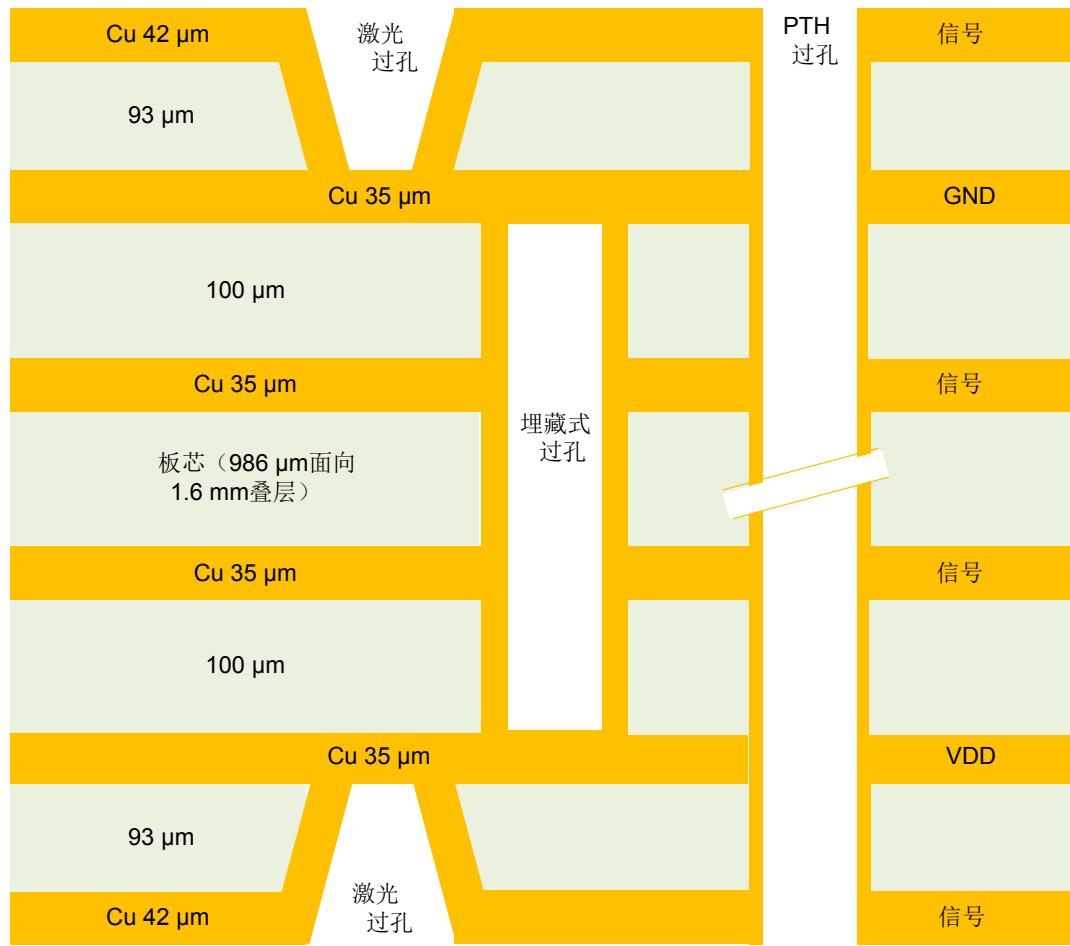

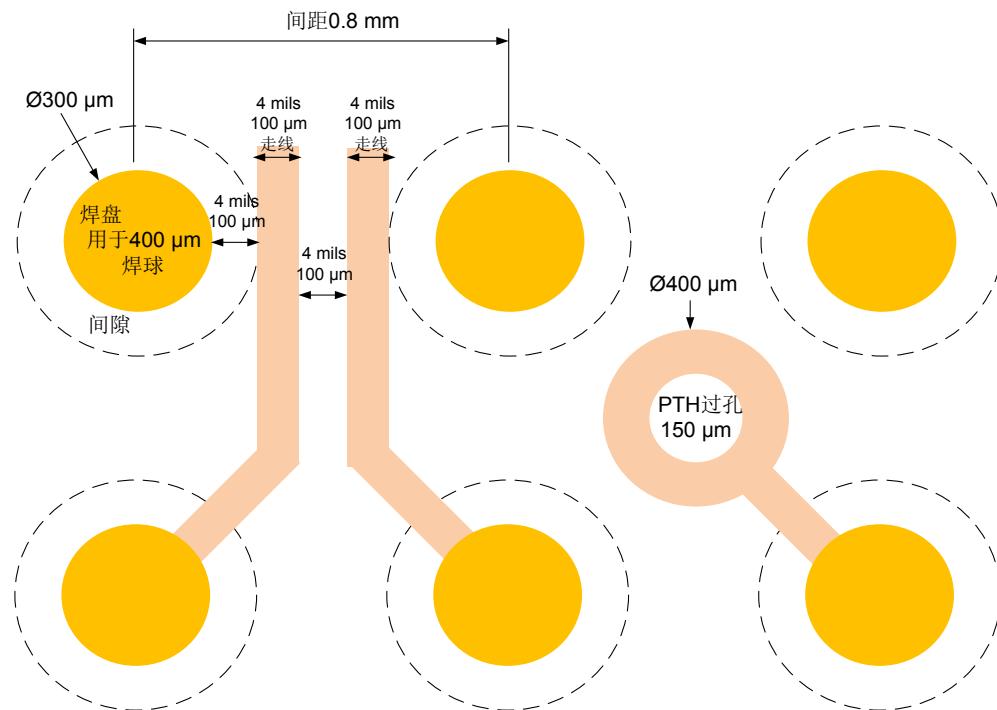

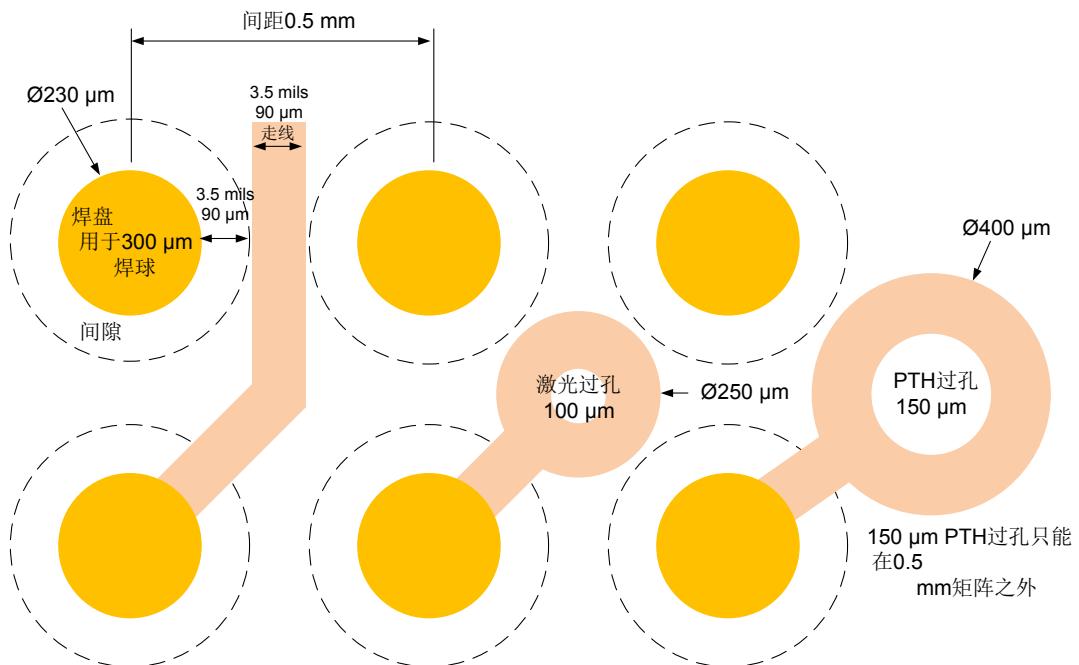

## PCB 层叠和技术

必须在 PCB 成本与电气连接容易性之间进行权衡。6 层和 4 层 PCB 示例的详细信息请参见下图。

对于 14x14 0.8 mm 间距封装和 11x11 0.5 mm 间距封装，可以仅使用 PTH。对于 9x9 0.5 mm 间距封装，需要使用 PTH、埋藏式孔，以及激光钻孔。

图 17. 4 层 PCB 层叠示例（仅采用 PTH 过孔）

图 18. 6 层 PCB 层叠示例 (采用 PTH 过孔、埋藏式过孔, 以及激光钻孔)

图 19. 0.8mm 间距封装的 PCB 规则示例 (采用 PTH 过孔)

图 20. 0.5mm 间距封装的 PCB 规则示例（采用激光过孔和 PTH 过孔）

## 7.6

### 解耦和封装扇出布线

所有供电和接地引脚都必须适当连至供电电源。这些连接，包括焊盘、线、过孔，都必须有尽可能低的阻抗。典型情况下，这可通过使用粗的线宽做到，最好在多层 PCB 中使用专用供电层。

此外，每个供电对都应使用陶瓷电容（参见表 5 获得详细信息）解耦。这些电容需要尽量靠近适当的引脚，或在这些引脚 PCB 的下面。确切值取决于应用。

推荐的 PCB 布局和扇出布线，以及各种封装类型的解耦电容的位置，可以在 *STM32MP13x 系列 DDR 存储器路由指南 (AN5692)* 附带的参考设计中找到。

## 7.7

### ESD/EMI 保护

从产品开发开始就应该考虑静电放电 (ESD) 与电磁干扰 (EMI)，因为在后期处理这些问题时可能非常复杂和代价昂贵。

ESD 和 EMI 由全球标准推动（如 IEC 61000 或 JESD 22），大多数国家/地区均要求在认证后才能在产品上附加强制标志（如 CE 或 FCC）。ESD 和 EMI 也由标准化接口认证或要求（如 USB）推动。

最终产品保护应通过外部组件完成，尤其是最终产品中供外部用户访问的接口（例如，以太网、USB、SD 卡）。

某些组件提供 ESD 保护以及 EMI 共模滤波（如用于 USB 的 ECMF02-2AMX6）。第 8 节：参考设计示例中详细说明了一些 ESD/EMI 保护示例。

更多详细信息，请参见文档[2]。

## 7.8

### 敏感信号

当设计应用时，研究以下几点可以提高电磁兼容性 (EMC) 性能：

- 暂时性干扰会永久影响运行过程的信号。例如，中断和握手选通信号。这种情况不适用于 LED 指令。

以下操作可以提高这些信号的 EMC 性能：

- 周围接地走线

- 缩短长度

- 附近无噪声或敏感走线（串扰效应）

对于数字信号，两个逻辑状态必须达到可能的最佳电气边界。建议使用慢速施密特触发器消除寄生状态。

- 噪声信号（如时钟）

- 敏感信号（如高阻抗）

更多详细信息，请参见文档[2]。

## 7.9

### 不使用的 I/O 和特性

STM32MP13x 器件面向多种应用，通常一个特定应用不会使用 100% 的 MCU 资源。

为了提高 EMC 性能，不使用的时钟、计数器、I/O 都不应浮空，例如，I/O 应该设置为 0 或者 1（上拉或者下拉至不用的 I/O 引脚），并且不使用的功能应被“冻结”或禁用。

请参见表 6. 提供未使用功能的用法。

## 8 参考设计示例

本节提供了一些示例，以帮助用户将主要和关键接口连接到 STM32MP13x 器件。

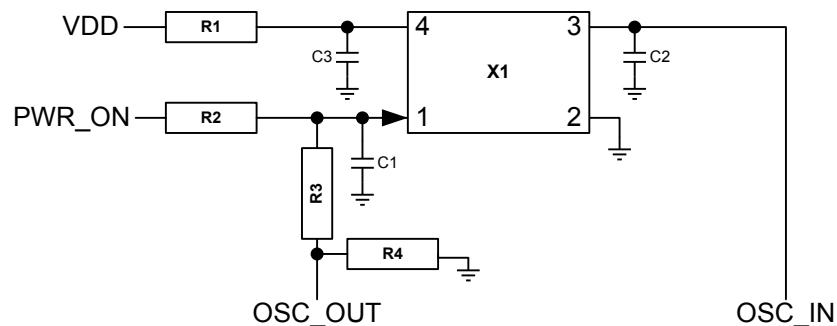

### 8.1 时钟

以下两个时钟源用于 STM32MP13x 器件（参见第 4 节获取详细信息）：

- LSE: 32.768 kHz 晶振用于嵌入式 RTC

- HSE: 24 MHz 晶振或外部振荡器作为 MCU 主时钟

图 21. HSE 推荐的振荡器/晶振选项的原理图

DT61427V1

表 12. 振荡器或晶振的 HSE BOM

| -  | 振荡器             | 晶振选项            |

|----|-----------------|-----------------|

| X1 | NZ2016SH 24 MHz | NX2016SA 24 MHz |

| R1 | 10 Ω            | -               |

| R2 | 10 kΩ           | -               |

| R3 | -               | 0 Ω             |

| R4 | 1 kΩ            | -               |

| C1 | -               | 6.8 pF          |

| C2 | -               | 6.8 pF          |

| C3 | 10 nF           | -               |

### 8.2 复位

NRST 复位信号为低电平有效（参见图 3. PVD 阈值）。复位源包括“复位”按钮和通过 JTAG 连接器的调试工具（参见第 2.3 节：复位和电源监控）。

## 8.3 启动模式

通过设置永久导线或开关 SW3 (位于 PI6 引脚上的 BOOT2)、SW2 (位于 PI5 引脚上的 BOOT1) 和 SW1 (位于 PI4 引脚上的 BOOT0) 以及内部 OTP 来配置启动选项。参见第 5 节: 启动配置。

当 U(S)ART 使用该引脚启动时, U(S)ARTx\_TX 引脚上必须设置  $10\text{ k}\Omega$  VDD 上拉电阻。由此可避免向主机发送一个浮动信号, 直到启动 ROM 接收并解码初始化字符。

表 13. U(S)ART 可能的启动引脚

| 外设                   | 信号 | 引脚   |

|----------------------|----|------|

| USART3               | Rx | PB12 |

|                      | Tx | PB10 |

| UART4 <sup>(1)</sup> | Rx | PD8  |

|                      | Tx | PD6  |

| UART5                | Rx | PB5  |

|                      | Tx | PB13 |

| USART6               | Rx | PC7  |

|                      | Tx | PC6  |

| UART7                | Rx | PF6  |

|                      | Tx | PF7  |

| UART8                | Rx | PE0  |

|                      | Tx | PE1  |

- 推荐默认 UART 给 Linux<sup>®</sup> 控制台 (作为 STLINK STDC14 连接器上的 VCP)。

如果是 QUADSPI 启动, 则 QUADSPI 可从以下之一启动:

- 专用的默认 QUADSPI 启动 GPIO (用于连接板件上的 QUADSPI 单存储区)

- 使用一些 FMC Nand8 启动 GPIO (PD1、PD4、PD5、PD11、PD15、PE9), 用于连接板件上的 FMC Nand8, 其中:

- PD1: QUADSPI\_BK1\_NCS

- PD4: QUADSPI\_CLK

- PD5: QUADSPI\_BK1\_IO0

- PD11: QUADSPI\_BK1\_IO2

- PD15: QUADSPI\_BK1\_IO3

- PE9: QUADSPI\_BK1\_IO1

## 8.4 SWD/JTAG 接口

参考设计显示了 STM32MP25x 器件和某些标准连接器之间的连接 (参见调试管理)。

注意

如果可用, 则建议将调试器探针系统的复位引脚连接到 NRST, 以便能够通过调试器复位应用。

表 14. SWD/JTAG 接口

| 接口    | 信号        | 引脚   | I/O 电源域 |

|-------|-----------|------|---------|

| UART6 | USART6 Rx | PF4  | VDD     |

|       | USART6 Tx | PF5  |         |

| UART8 | UART8 Rx  | PF3  | VDD     |

|       | UART8 Tx  | PG3  |         |

| UART9 | UART9 Rx  | PB14 | VDD     |

|       | UART9 Tx  | PD13 |         |

## 8.5 电源

请参见第 2 节: 电源。

### 8.5.1 采用 DDR3L 的 3.3 V I/O 分立电源示例

该参考设计示例针对不强调降低功耗的低成本 DDR3L 简单 3.3 V IO 平台。支持睡眠、停止和待机模式。

支持 LP-Stop 和低功耗待机模式（具有 DDR3L 保持功能）。但由于使用 DDR3L 时没有进行自刷新的低功耗目标，所以此功能意义不大。更多详细信息，请参见参考文档[10]。

当 nRST 被激活或 STM32MP13x 从待机模式退出时，应该在 VDDCPU 和 VDDCORE 上进行一次电源循环。因此，SMPS 的使能信号连接到 PWR\_ONRST 和 PWR\_CPU\_ONRST。如果返回设备进入 RMA 状态以便进行故障分析，不应进行电源循环。因此，连接到 PWR\_ONRST 和 PWR\_CPU\_ONRST 的两个二极管必须移除。

图 22. 采用 3.3 V I/O 和 DDR3L 的分立电源示例

## 8.5.2

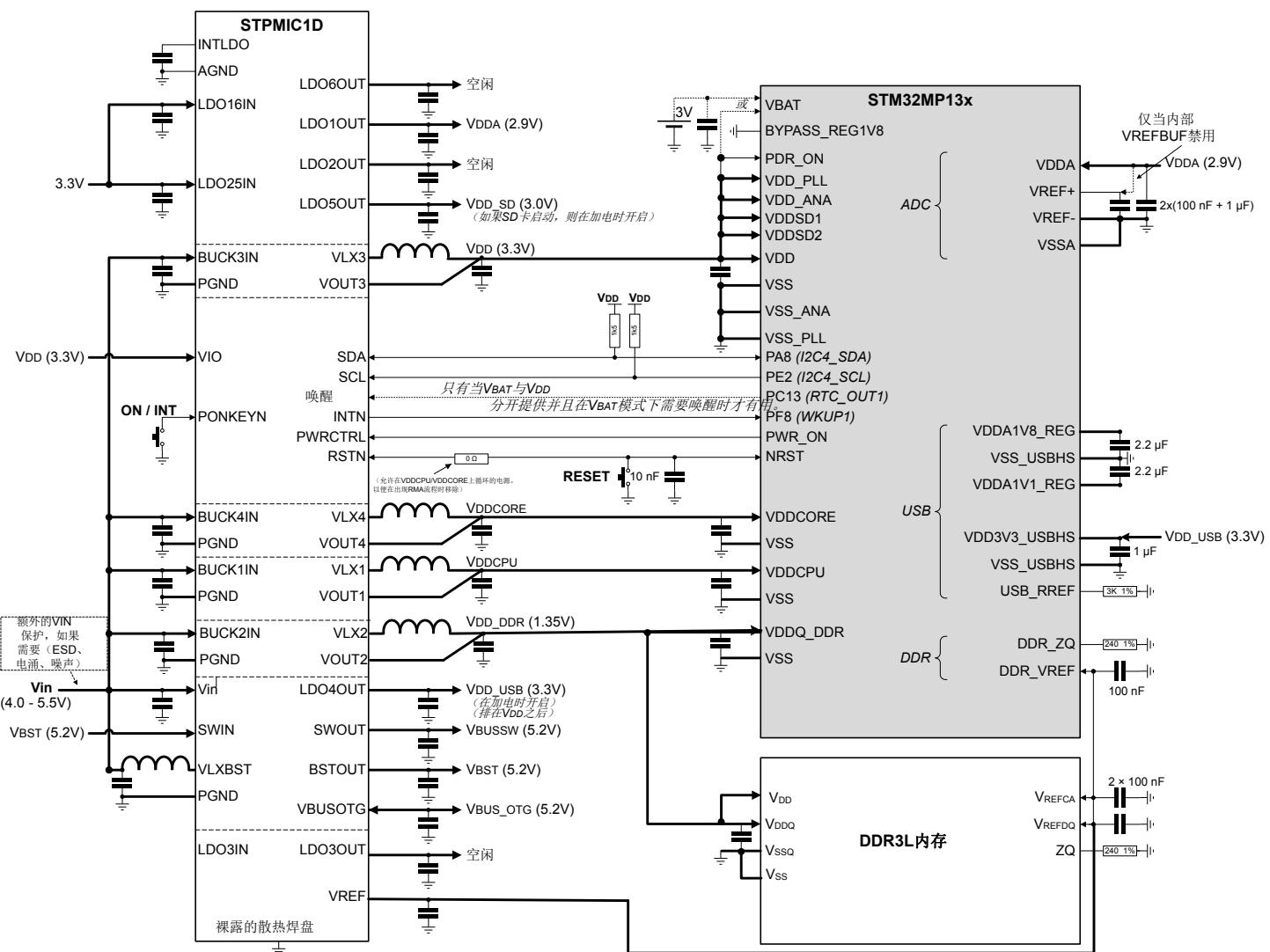

## STPMIC1 电源示例 (3.3 V I/O, 采用 DDR3L)

该参考设计示例针对采用低成本 DDR3L 和高集成度 STPMIC1 的复杂 3.3V I/O 平台。通常，所有平台组件均可以由 STPMIC1 供电。得益于 STPMIC1 I2C 和旁带信号，支持全电源控制。支持睡眠模式、停止模式，以及待机模式（详细信息请参见 STPMIC1 数据手册）。

如果 nRST 已激活，则 STPMIC1 自动对 VDDCORE 和 VDDCPU 进行断电重启（nRST 按钮，退出待机模式，系统复位）。如果进入 RMA 状态，则不得断电重启。STM32MP13x nRST 与 STPMIC1 之间的  $0\ \Omega$  电阻可以在进入 RMA 状态后进行设置和移除。

在同一条 I<sup>2</sup>C 总线上，无法共享由安全和非安全软件控制的 I<sup>2</sup>C 器件。例如，在我们的标准交付中，安全软件控制 STPMIC1，并使用独特且安全的 I<sup>2</sup>C 主设备（STM32MP13x 上的 I<sup>2</sup>C3、I<sup>2</sup>C4 或 I<sup>2</sup>C5）。

图 23. STPMIC1 电源示例 (3.3 V I/O, 采用 DDR3L)

## 注意

**BUCK1** 和 **BUCK4** 默认值为 1.2 V。该值允许产品以低频率启动。然后，软件应该将 **BUCK** 值设为预期的运行时间值（**VDDCORE** 和 **VDDCPU** 上的典型值为 1.25 V）。

## 8.5.3

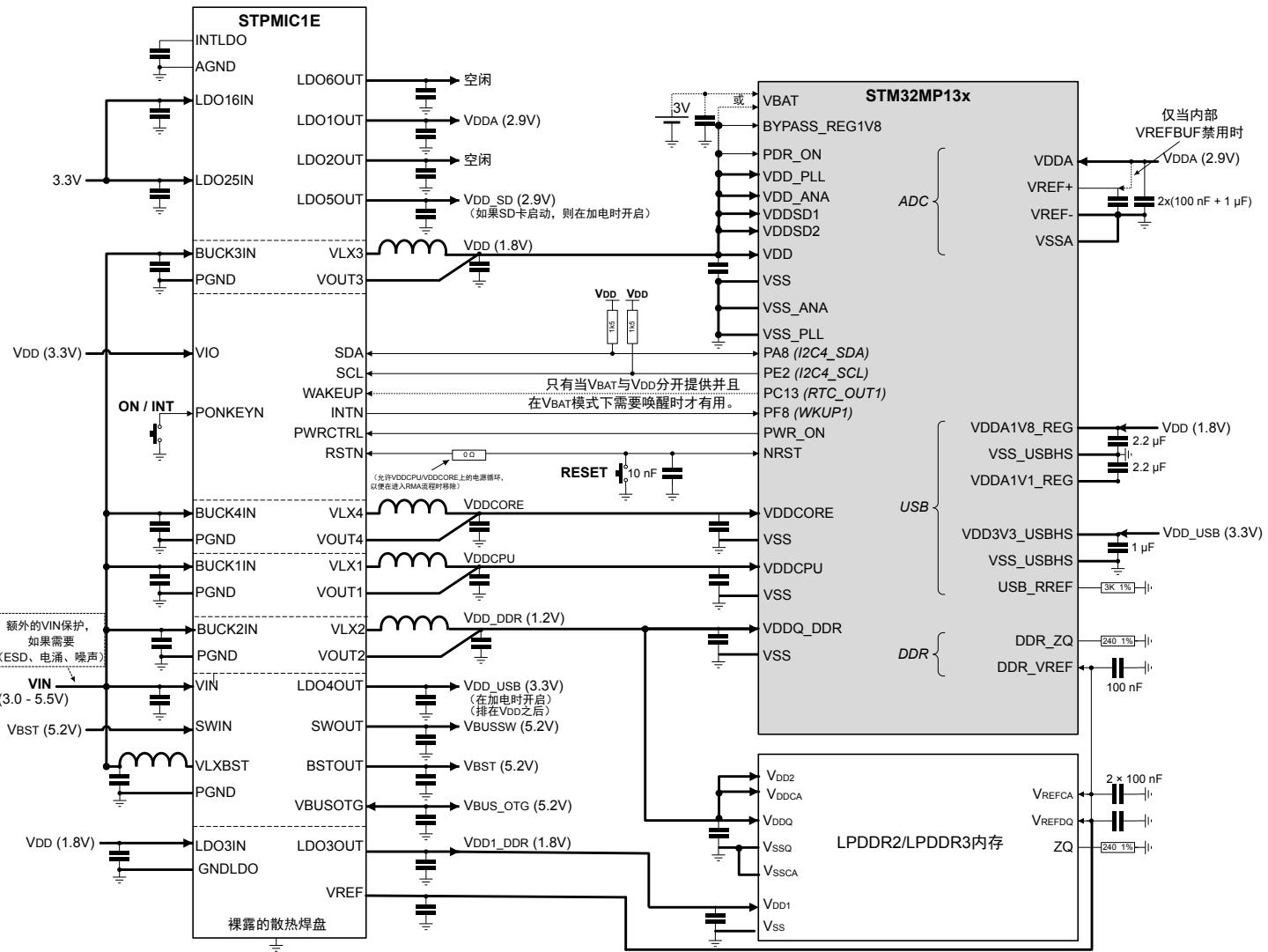

## 采用 LPDDR2/LPDDR3 的 1.8 V I/O STPMIC1 电源示例

该参考设计示例针对采用低功耗 LPDDR2/LPDDR3 和高集成度 PMIC 的复杂 1.8 V I/O 平台。通常，所有平台组件均可以由 STPMIC1 供电。得益于 STPMIC1 I2C 和旁带信号，支持全电源控制。支持睡眠/停止/待机模式以及具有 LPDDR2/LPDDR3 保持功能的极低功耗待机模式（参见 STPMIC1 数据手册获取详细信息）。

图 24. 采用 LPDDR2/LPDDR3 的 1.8V I/O STPMIC1 电源示例

## 注意

BUCK1 和 BUCK4 默认值为 1.2 V。该值允许产品以低频率启动。然后，软件应该将 BUCK 值设为预期的运行时间值 (VDDCORE 和 VDDCPU 上的典型值为 1.25 V)。

## 8.6

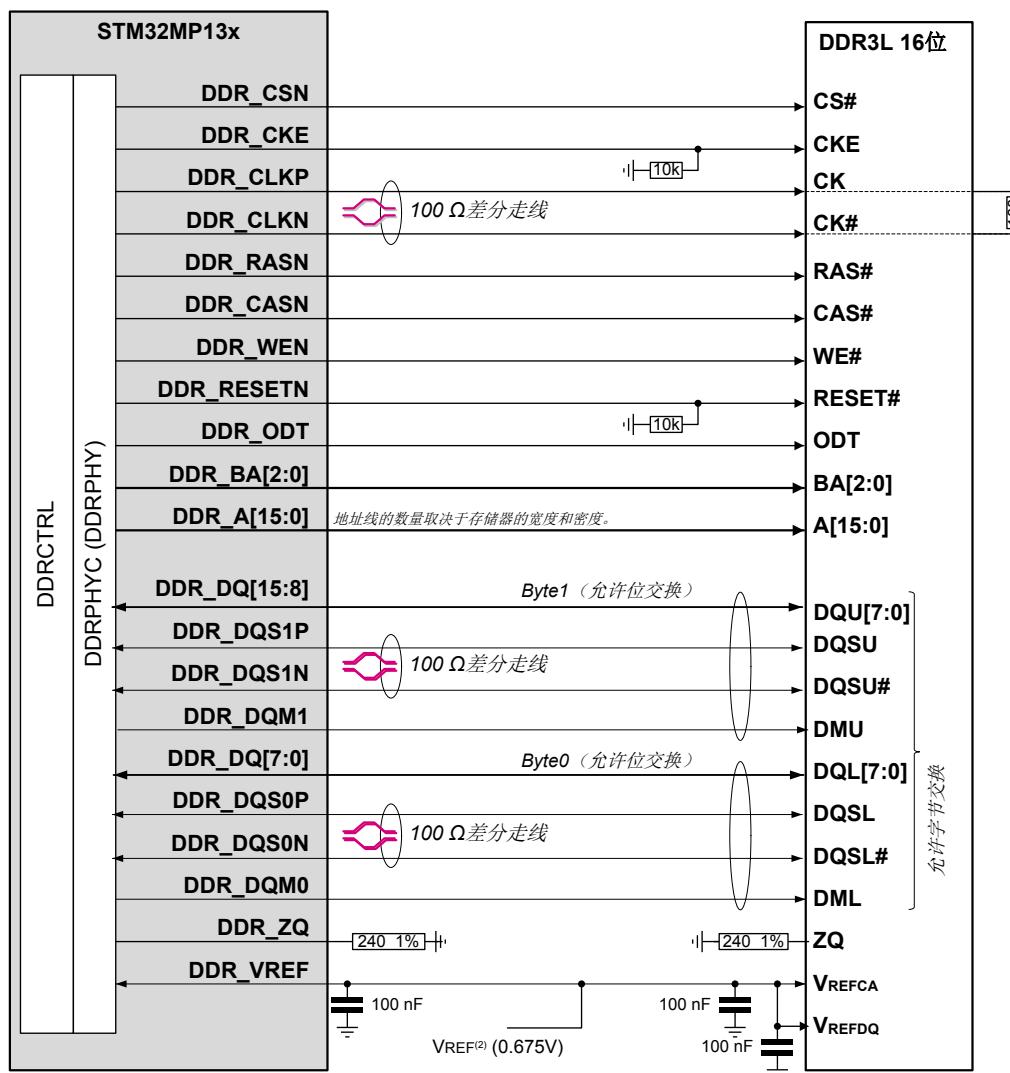

## DDR3/DDR3L SDRAM

DDR3 与 DDR3L 的区别仅在于电源电压 (1.5 V vs 1.35 V) 和 VREF 电平 (0.75 V vs 0.675 V)。DDR3L 已取代大多数 DDR3 设计。

必须在 DDR\_ZQ 之间连接一个  $240 \Omega$ , 1% 的电阻。下图中的值应适用于大多数情况，但可以根据每侧 I/O 驱动强度和 PCB 阻抗进行调整。关于路由示例，请参见文档[8]。

图 25. DDR3L 16 位连接示例

注意：

(1) 未显示电源和解耦电容。

(2) 或者，为了简化路由和避免长 VREF 线路，可通过靠近每个 VREF 引脚的 VDDQ 上的  $1 \text{ k}\Omega$  /  $1\text{k}\Omega$ , 1% 电阻分压器在本地生成 VREF。

[8] 中对详细路由示例进行了说明。

## 8.7

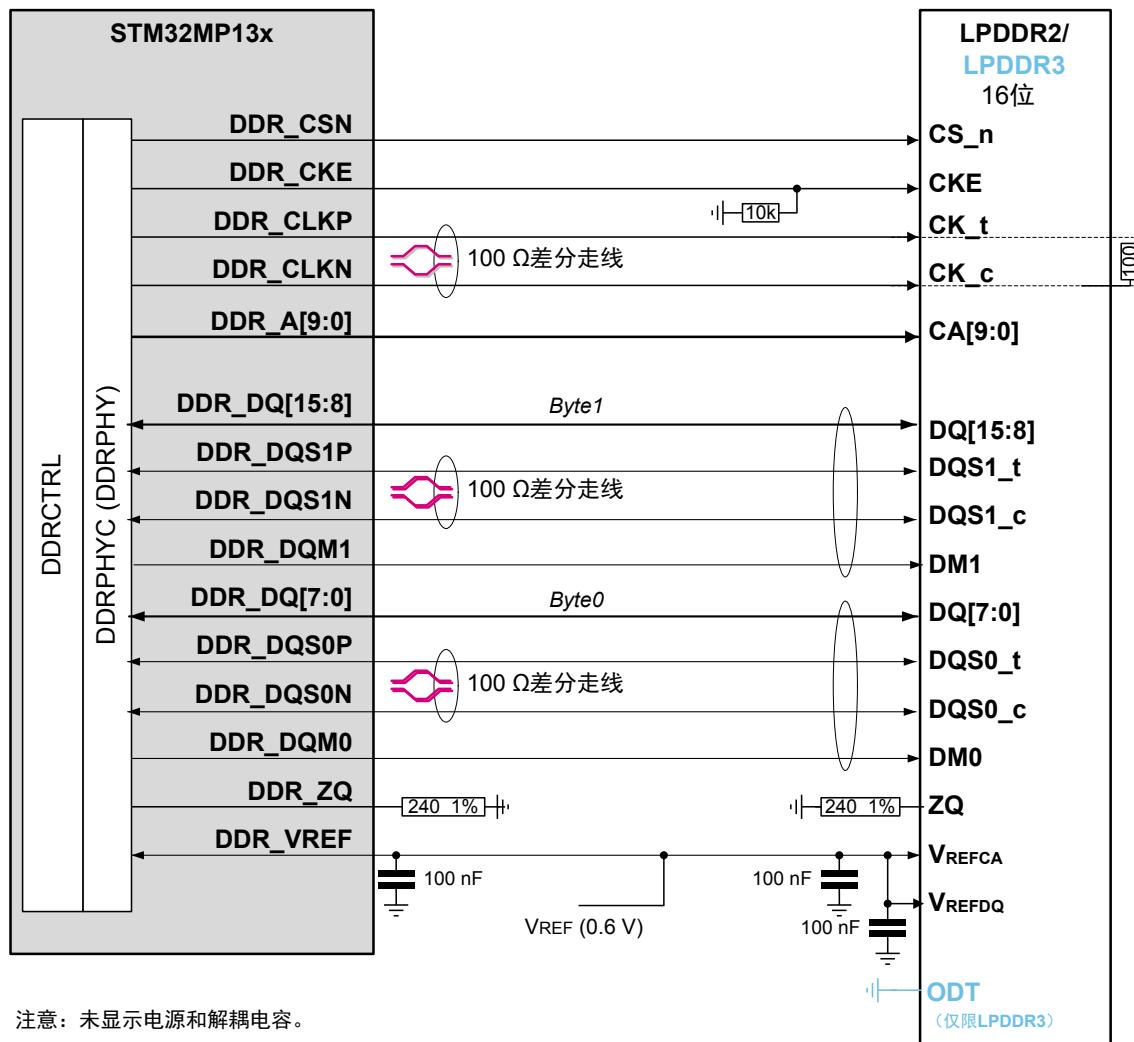

## LPDDR2/3 SDRAM

必须在 DDR\_ZQ 和 VSS 之间连接一个电阻器 ( $240 \Omega$ , 1%)。该电阻不得与 LPDDR2/LPDDR3 组件所需的一个或多个 ZQ 电阻共用。关于路由示例，请参见文档[8]。

图 26. LPDDR2/LPDDR3 16 位连接示例

[8]中对详细路由示例进行了说明。

## 8.8

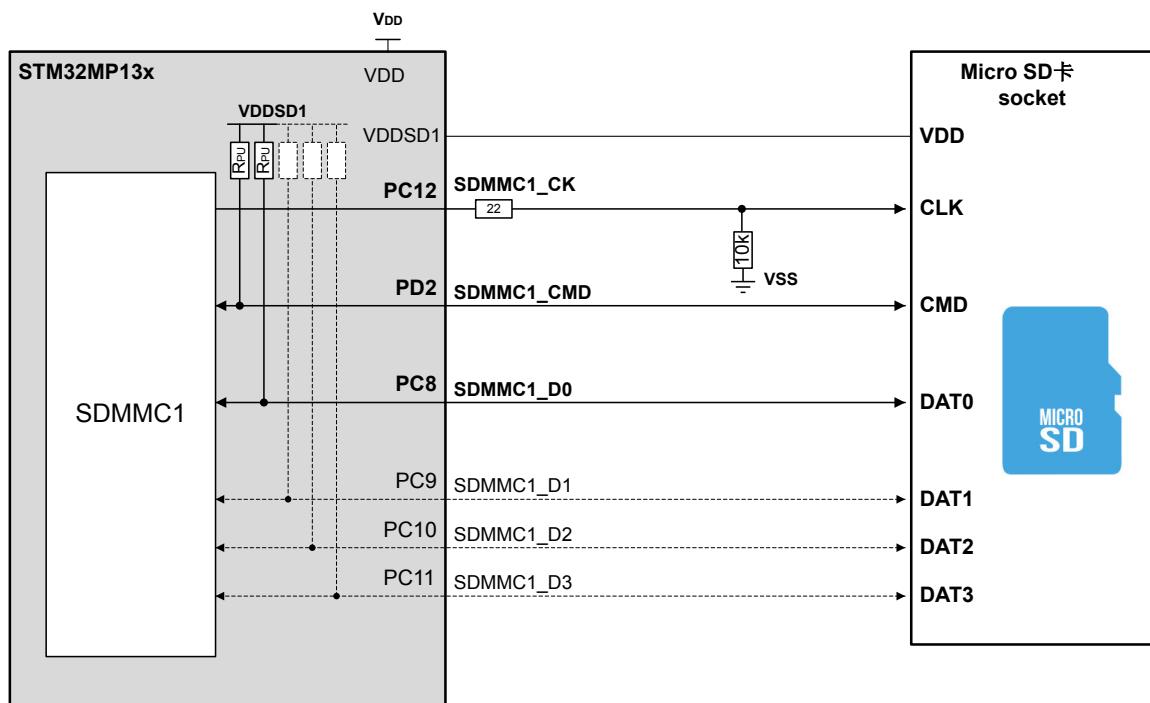

## SD-Card 无外部电平转换器

由于  $V_{DDSDx}$  专用电源，可以在不需要外部电平转换器的情况下使用更快速的 UHS-I 模式。更快速的 UHS-I 模式可达 SDR50 和 DDR50、50 Mbytes/s 总线速度。对于这些模式，用户必须将  $V_{DDSDx}$  I/O 电压切换到 1.8 V (SD 卡通过 3 V card I/O 启动)。

## 注意

启动总是在“标准”模式 (3 V I/O) 下完成。如果 UHS-I 中的应用使用了此卡，则在复位或退出待机状态后需要重启电源。

该示例独立于 MPU I/O 电压  $V_{DD}$ ，可以位于 1.71 V 和 3.6 V 之间。当  $V_{DD}$  为 1.8 V (典型值) 时， $V_{DDSDx}$  应在启动阶段由与“标准”模式下 SD-Card 启动事务兼容的电压供电 (2.7 V-3.6 V)。

## 注意

良好的信号完整性取决于电路板、GPIO 强度设置 (GPIO\_OSPEEDR 寄存器) 和  $V_{DD}$  电压。

如果使用  $V_{DD} = 1.8$  V，可能需要以下设置，以确保在用于 SDMMC 输出的焊盘上获得最佳速度：

- OTP 位 product\_below\_2v5 中的设置

- 寄存器 SYSCFG\_HSLVEN4R 中的设置 (HSLVEN\_SDMMC1 位) 或寄存器 SYSCFG\_HSLVEN5R 中的设置 (HSLVEN\_SDMMC2 位)

- 或者同时需要上述两个寄存器中的设置

## 警告

当  $V_{DD}$  高于 2.7 V 时，不得置位 UHSLVEN，否则可能造成器件永久损坏。

如果需要，阻抗匹配电阻应尽可能靠近输出驱动器引脚布置。以下示例中的值应适用于大多数情况，但可以根据 I/O 驱动强度和 PCB 阻抗进行调整。

在  $V_{DD\_SD}$  关闭前 (如待机前)，必须通过 SDMMC1 驱动器将进入卡的所有信号设为 0 或高阻态。

下图显示了一个不使用 UHS-I SD 卡模式的连接示例。

图 27. 无外部电平转换器的 SD 卡示例 (非 UHS-I 模式连接)

注意：- 平直的粗线条：默认的引脚和 SD 卡启动期间低级启动 ROM 要求的最小信号集。

- 走线必须尽可能短且长度均衡。

如果  $V_{DD} = 3.3$  V，则  $V_{DD\_SD}$  可连接到  $V_{DD}$ ，以节约电源。

如果  $V_{DD} = 1.8$  V，则  $V_{DD\_SD}$  应该由外部电源供电 (电压符合 SD-card 标准) (2.7 V - 3.6 V)。

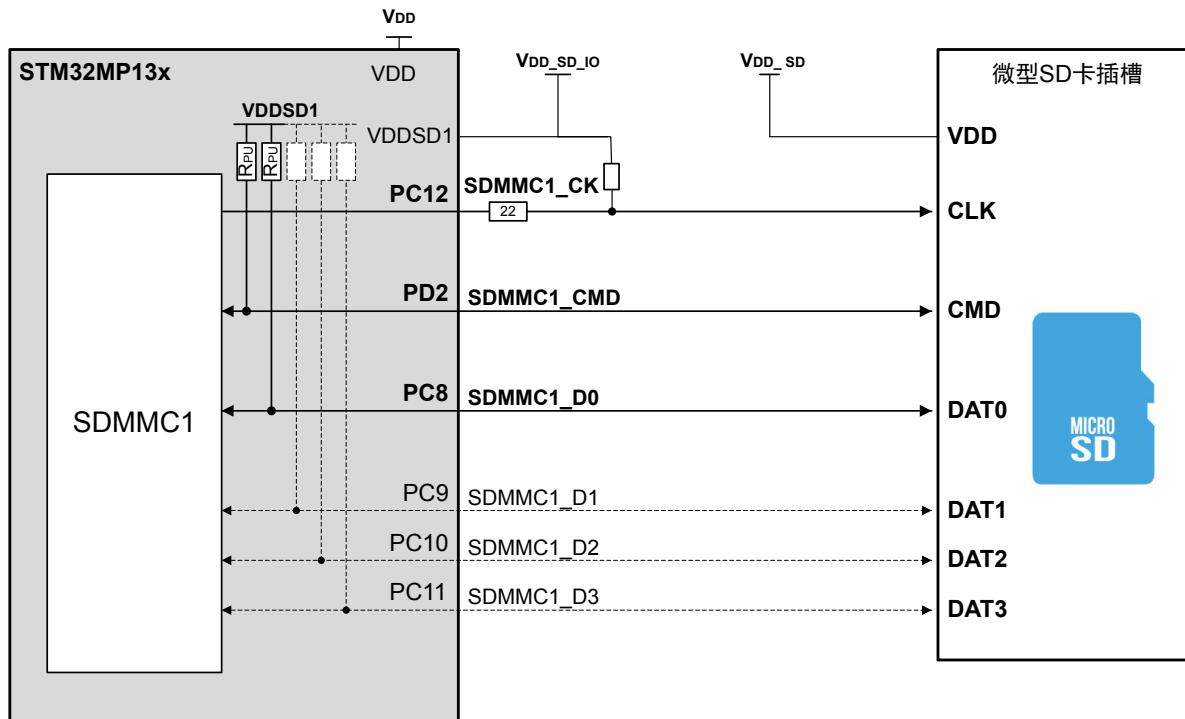

如果使用 UHS-I SD-Card 模式，则 SDMMC1（或 SDMMC2）焊盘环部分必须由专用电源（ $V_{DD\_SD\_IO}$ ）供电。处于 UHS-I 模式时，软件必须能够将电源从  $V_{DD\_SD}$  改为 1.8 V。与 SDMMC1 对应的电压源为  $V_{DDSD1}$ （或者  $V_{DDSD2}$  对应于 SDMMC2）。可能的连接如下图所示。

图 28. 无外部电平转换器的 SD 卡示例（UHS-I 模式连接）

注意：- 平直的粗线条：默认的引脚和 SD 卡启动期间低级启动 ROM 要求的最小信号集。

- 走线必须尽可能短且长度均衡。

DT66031V1

示例同样适用于 SDMMC2 接口（使用 PB3、PB4、PB14、PB15、PE3，以及 PG6 GPIO）。

#### 注意

当产品需要使用 UHS-I 方式从 SD-Card 启动时，必须在生产过程中更新 STPMIC1 默认配置。必须对该配置进行设置，以允许两个调节器在 3.3 V 时可用。

可用使用可通过 GPIO 进行编程的外部开关（1.8 V、3.3 V）为  $V_{DDSDx}$  电源引脚供电。节省一个可编程调节器（参见下图）。

图 29. 使用外部电源开关为  $V_{DDSDx}$  供电

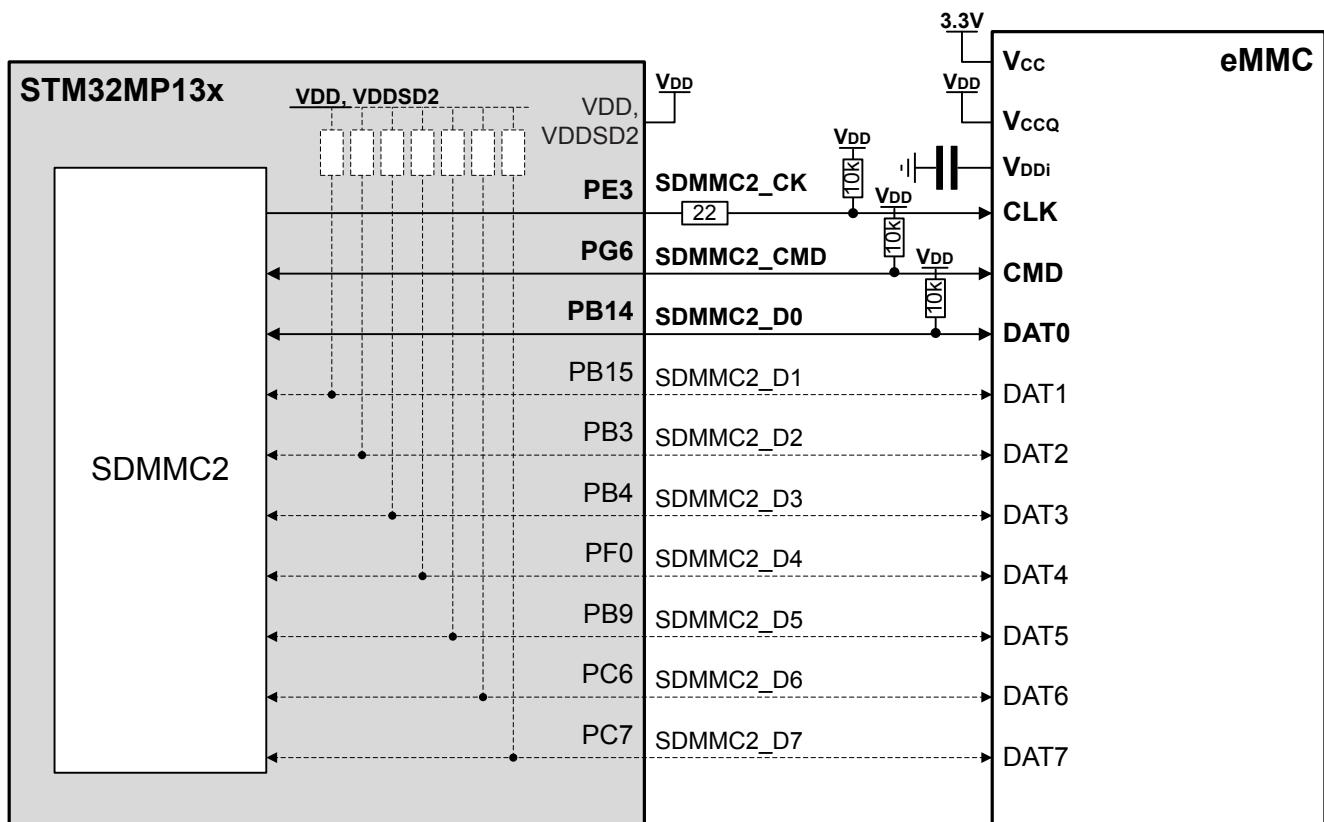

## 8.9 eMMC Flash

### 注意

良好的信号完整性取决于电路板、GPIO 强度设置（GPIO\_OSPEEDR 寄存器）和  $V_{DD}$  电压。

如果使用  $V_{DD} = 1.8$  V，可能需要以下设置，以确保在用于 SDMMC 输出的焊盘上获得最佳速度：

- OTP 位 product\_below\_2v5 中的设置

- 寄存器 SYSCFG\_HSLVEN4R 中的设置（HSLVEN\_SDMMC1 位）或寄存器 SYSCFG\_HSLVEN5R 中的设置（HSLVEN\_SDMMC2 位）

- 上述两个寄存器中的设置。

图 30. eMMC 连接示例

注意：- 平直的粗线条：默认的引脚和eMMC启动期间低级启动ROM要求的最小信号集。

- 走线必须尽可能短且长度均衡。未显示解耦电容。

- 在该模式下，VDD和VDDSD2将被绑在一起。

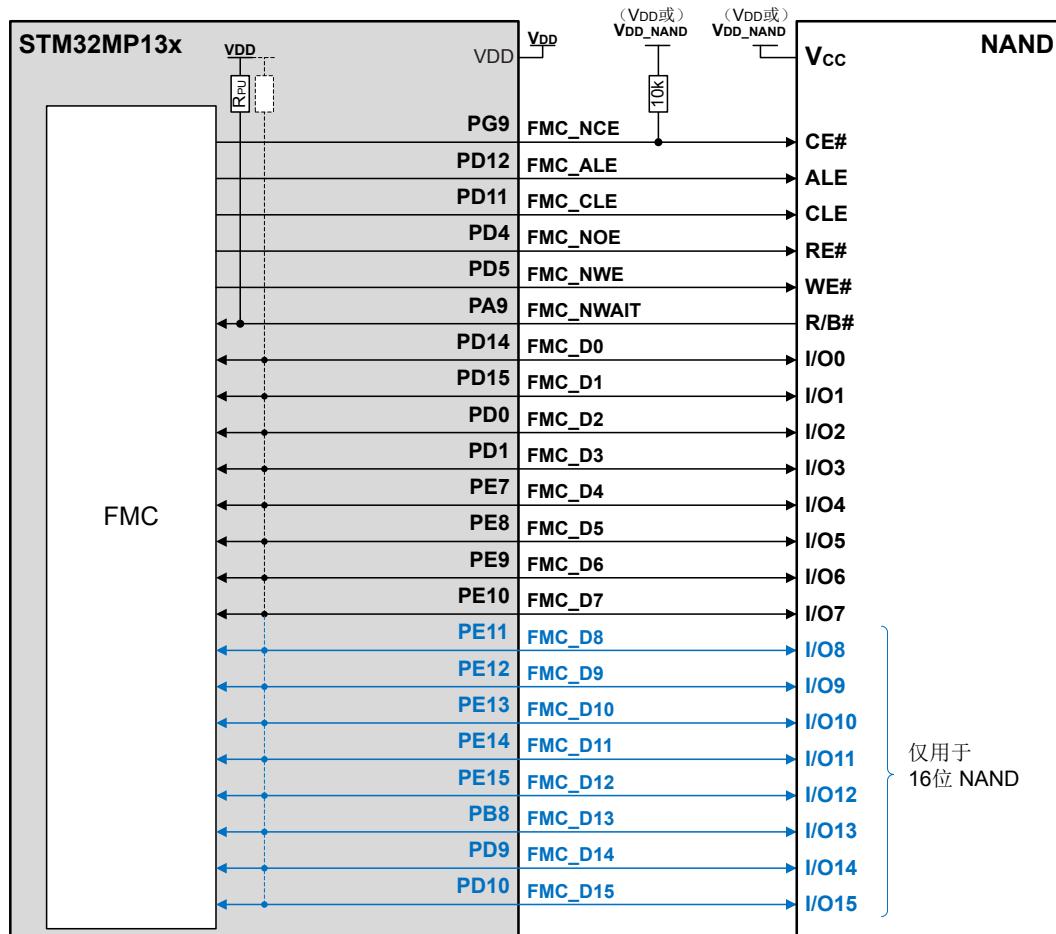

## 8.10 SLC NAND Flash

支持单个 8 位或 16 位 SLC NAND 存储器设备以及两个独立的 8 位 SLC NAND 存储器设备：

- 单个 8 位或 16 位 SLC NAND 存储器设备 = CE# = FMC\_NCE

- 独立的 8 位 SLC NAND 存储器设备 = device1 CE# = FMC\_NCE 且 device2 CE# = FMC\_NCE2。

注意

仅在连接到 FMC\_NCE 的 SLC NAND 存储器设备上执行启动。

图 31. SLC NAND-Flash 连接示例

注意：- 平直的粗线条：默认的引脚和NAND启动期间低级启动ROM要求的最小信号集。

- 走线必须尽可能短且长度均衡。未显示解耦电容。

- V<sub>DD\_NAND</sub> 必须切断1毫秒 以上才能重启(复位或待机退出时)。

—— 原理图仅适用于16位NAND。

注意

仅支持单层单元(SLC) NAND-Flash。支持采用汉明、BCH4 或 BCH8 纠错算法。

## 8.11

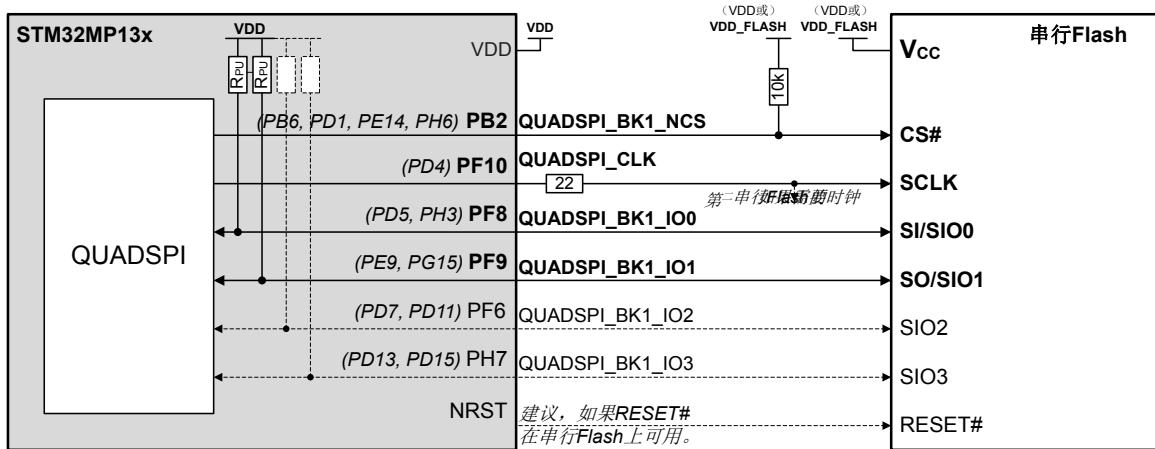

## 串行 NOR/NAND-Flash

启动总是在 SPI 模式下完成。如果出现以下情况，在复位或退出待机状态后，需要在串行 Flash 电源上进行电源循环：

- 应用程序在多个数据线中设置串行 Flash 存储器

- 或者扇区地址发生改变。

## 注意

良好的信号完整性取决于电路板、GPIO 强度设置 (GPIO\_OSPEEDR 寄存器) 和  $V_{DD}$  电压。

当使用  $V_{DD} = 1.8 \text{ V}$  时，可能需要以下设置，以确保在 QUADSPI 输出上使用的焊盘上获得最佳速度：

- OTP 位 product\_below\_2v5 中的设置和

- 寄存器 SYSCFG\_HSLVEN1R 的设置 (HSLVEN\_QUADSPI 位)。

## 警告

当  $V_{DD}$  高于  $2.7 \text{ V}$  时，不得置位 UHSLVEN，否则可能造成器件永久损坏。

如果需要，阻抗匹配电阻应尽可能靠近输出驱动器引脚布置。以下示例中的值应适用于大多数情况，但可以根据 I/O 驱动强度和 PCB 阻抗进行调整。

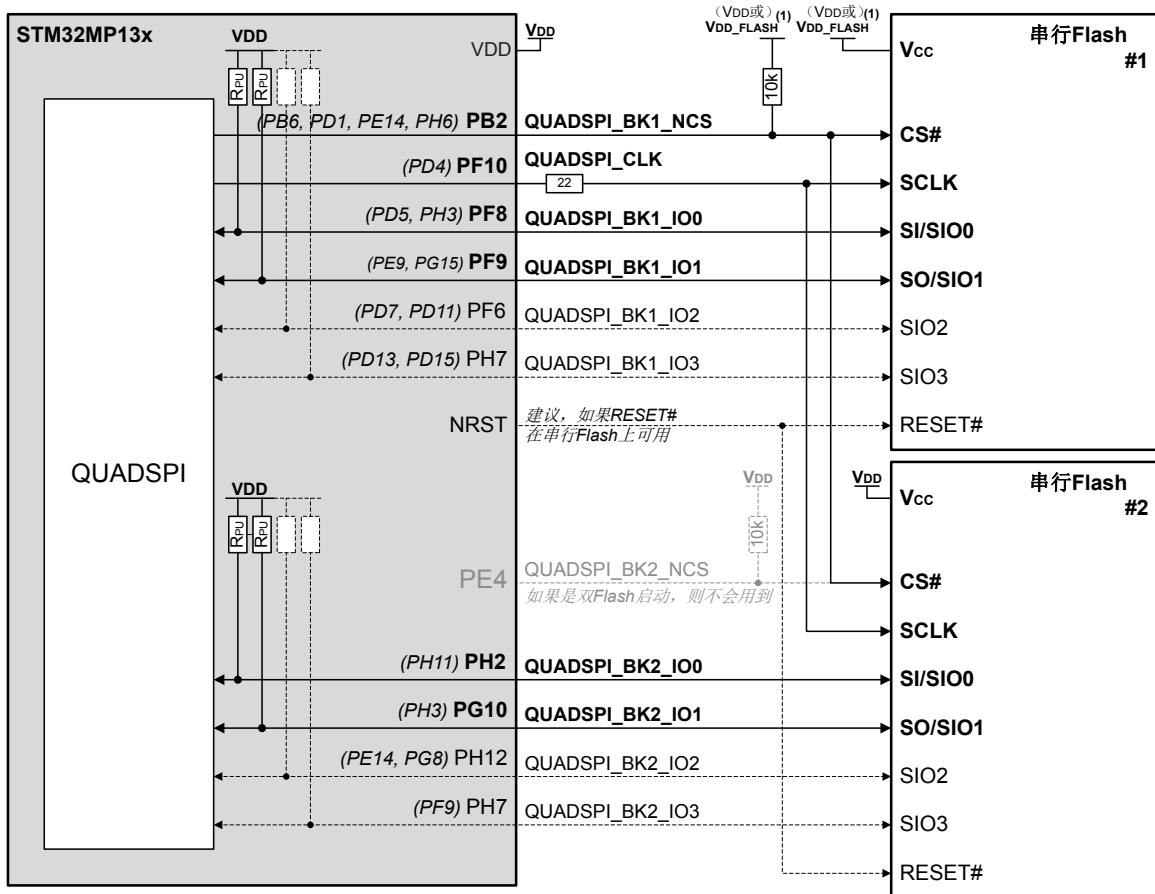

图 32. 串行 Flash 连接示例

注意：

- 平直的粗线条：默认的引脚和串行 Flash 启动期间低级启动 ROM 要求的最小信号集。

- 未显示解耦电容。

- $V_{DD\_FLASH}$  必须切断 1 毫秒以上才能重启（复位或待机退出时）。

- 在使用 SI/SO 的 SPI 模式启动期间，一些串行存储器可以使用 IO2 和 IO3 引脚作为附加功能（如 HOLD）。为了使这类设备能够启动，可能需要通过添加外部上拉或在使用 OTP 启动期间定义内部上拉的方式将这些引脚设置为非活动级别。

如果串行 Flash 存储器发生空白或损坏情况，启动 ROM 尝试从单一串行 Flash 存储器引导。在此之后，启动 ROM 尝试双串行 Flash 模式，这意味着 PH2 和 PG10 可能与板件上使用的信号冲突。如果需要，可以通过对 OTP 进行编程（3、5、6 和 7）来避免 PH2 和 PG10 出现上述冲突。这种编程强制启动 ROM 只使用单个串行 Flash 配置中所需的四个引脚。

QUADSPI 串行 Flash 存储器可以从专用 GPIO 启动，也可以使用一些 FMC\_Nand8 启动 GPIO (PD4、PD1、PD5、PE9、PD11、PD15)，以便允许两种类型的 Flash 存储器在板件上的占用空间相同。在这种情况下，应该在生产阶段对 STM32MP13x 默认启动引脚 NVM 重新编程。

此外，可以使用 OTP (word 9) 设置面向器件页面和功能块大小对 NAND 配置进行设置。

图 33. 双串行 Flash 连接示例

注意：

- 平直的粗线条：默认的引脚和双串行Flash启动期间低级启动ROM要求的最小信号集。

- 未显示解耦电容。

- VDD\_FLASH 必须切断1毫秒以上才能重启（复位或待机退出时）。

- 在使用SI/SO的SPI模式启动期间，一些串行存储器可以使用IO2和IO3引脚作为附加功能（如HOLD）。为了使这类设备能够启动，可能需要通过添加外部上拉或在使用OTP启动期间定义内部上拉的方式将这些引脚设置为非活动级别

如果存储器 I/O 电源可以独立于  $V_{DD}$  被关断，则严禁 NRST 直接连接到存储器复位引脚。此外，可以使用以下选项：

- 如果存储器支持内部 POR（上电复位），则存储器复位引脚可保持开路

- 存储器复位引脚通过肖特基二极管与 NRST 侧的阴极连接

否则，当其 I/O 电源不存在时，NRST 可能会被存储器内部保护功能下拉为低电平。这可能导致平台意外复位。

关于存储器复位引脚要求的详细信息，请参考存储器文档（尤其是在复位引脚上存在内部上电复位和/或内部上拉时）。

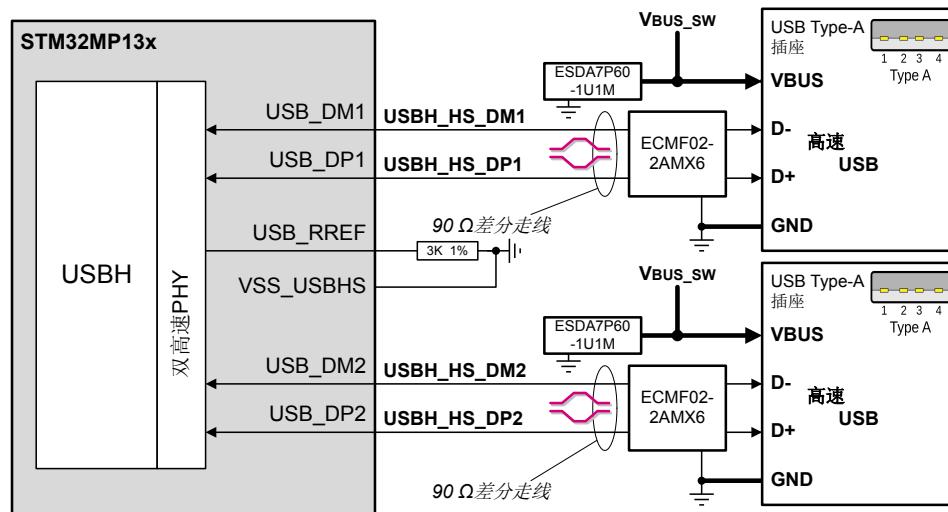

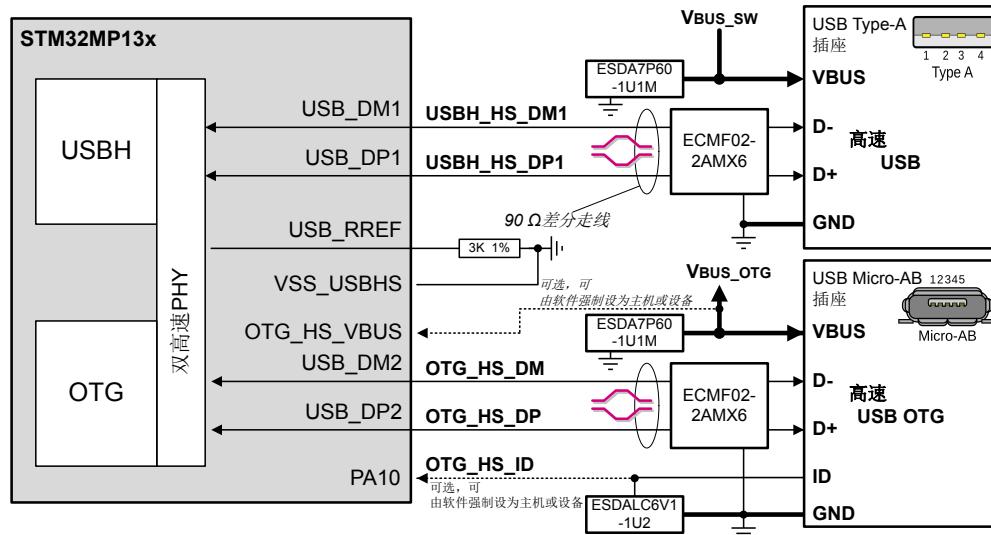

## 8.12 USB

## 注意

通过一些外部组件支持 USB Type-C™。

电阻器 (3 k, 1%) 必须连接在 USB\_RREF 和 VSS\_USBHS (或者 VSS, 前提是 VSS\_USBHS 在所选的封装上不可用) 之间。

图 34. USB 两端口主机高速

图 35. USB 主机高速 + OTG 高速连接示例

## 注意

在 OTG 外设上, 通过使用 Micro-B 插座 (而不是 Micro-AB) 并让 OTG\_ID 引脚保持未连接状态来支持 USB 高速。

## 注意

使用 OTG\_HS\_VBUS 信号可防止在某些情况下可能需要 USB 认证。这是由于 USB\_DPx 引脚上拉在 OTG\_HS\_VBUS 信号可用之前被激活。此外, OTG\_HS\_VBUS GPIO 电气特性要求在 OTG\_HS\_VBUS 之前有  $V_{DD}$ , 情况并不总是如此, 例如在设备连接到主机期间。请参见文档[11]。

因此, 建议使用带有一些电阻桥的 GPIO, 该 GPIO 上有一个 EXTI 中断连接到外部 USB VBUS 信号。此外, 还建议对 OTG\_HS\_ID 信号进行相同处理 (使用连接到外部 USB ID 号的 GPIO+EXTI)。关于实现细节, 请参见参考文档[11]。有了该解决方案, 由于 VBUS 和 ID USB 信号上的 EXTI, 可以从低功耗模式功能中额外唤醒。

OTG\_HS\_VBUS 和 OTG\_HS\_ID 信号在一些 GPIO 上已经可用。然后, 可以将这些 GPIO 与其关联的 EXTI 组合使用, 或者使用任意其他 GPIO。OTG\_HS\_VBUS 位于 P17 (EXTI17) 上, 而 OTG\_HS\_ID 位于 PA10 (EXTI10) 上。

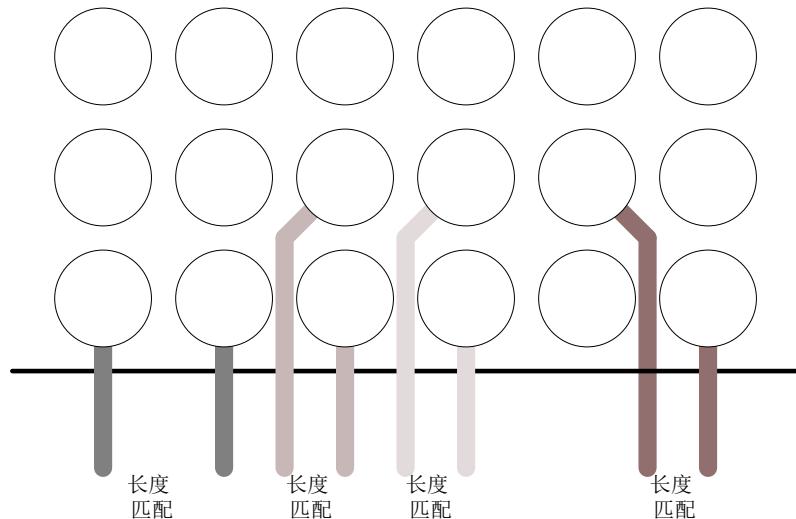

### USB 高速 PCB 走线长度匹配

USB (以及 DDR) 差分对长度匹配考虑了封装和电路板布局。内部焊球连接长度在封装中较小。因此, 更长的板级连接是首选, 并且已经在封装中进行了考虑。

下图显示了四个差分对, 导线长度已经在封装内匹配。这意味着无需在板件上补偿由于内排焊球和外排焊球位置造成长度差异。

图 36. USB 高速 PCB 走线示例

表 15. USB 高速 PCB 路由建议

| 建议                               | 最小值   | 典型值      | 最大值   | 单位             |

|----------------------------------|-------|----------|-------|----------------|

| 差分阻抗                             | 76.5  | 90       | 103.5 | $\Omega$       |

| 单端阻抗                             | 38.25 | 45       | 51.75 | $\Omega$       |

| 一对 (包括封装) 内部的长度匹配                | -50   | -        | +50   | mils           |

|                                  | -1.27 | -        | +1.27 | mm             |

| 最大走线长度 (直到连接器或第一个活动组件)           | -     | -        | 8     | 英寸             |

|                                  | -     | -        | 203   | mm             |

| 最大通孔数量 (建议的值)                    | -     | -        | 2     | -              |

| 任意差分走线和其他信号之间的距离                 | S-2S  | S-3S 或其他 | -     | <sup>(1)</sup> |

| 不要在电源平面拆分点上方走线。无次级走线 (仅点对点)。无直角。 |       |          |       |                |

1. 在应用笔记“DDR 存储器路由指南(AN5692) ”可以找到定义。

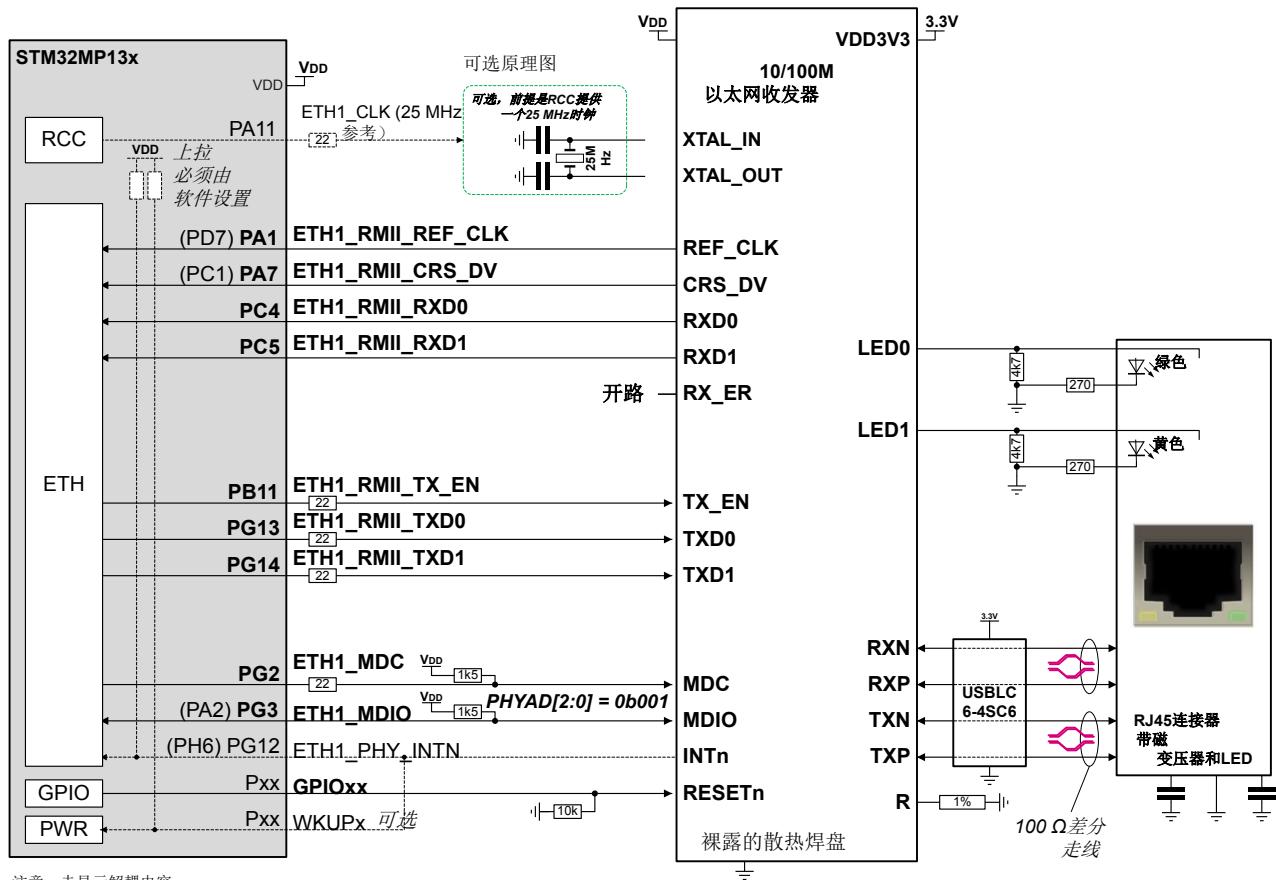

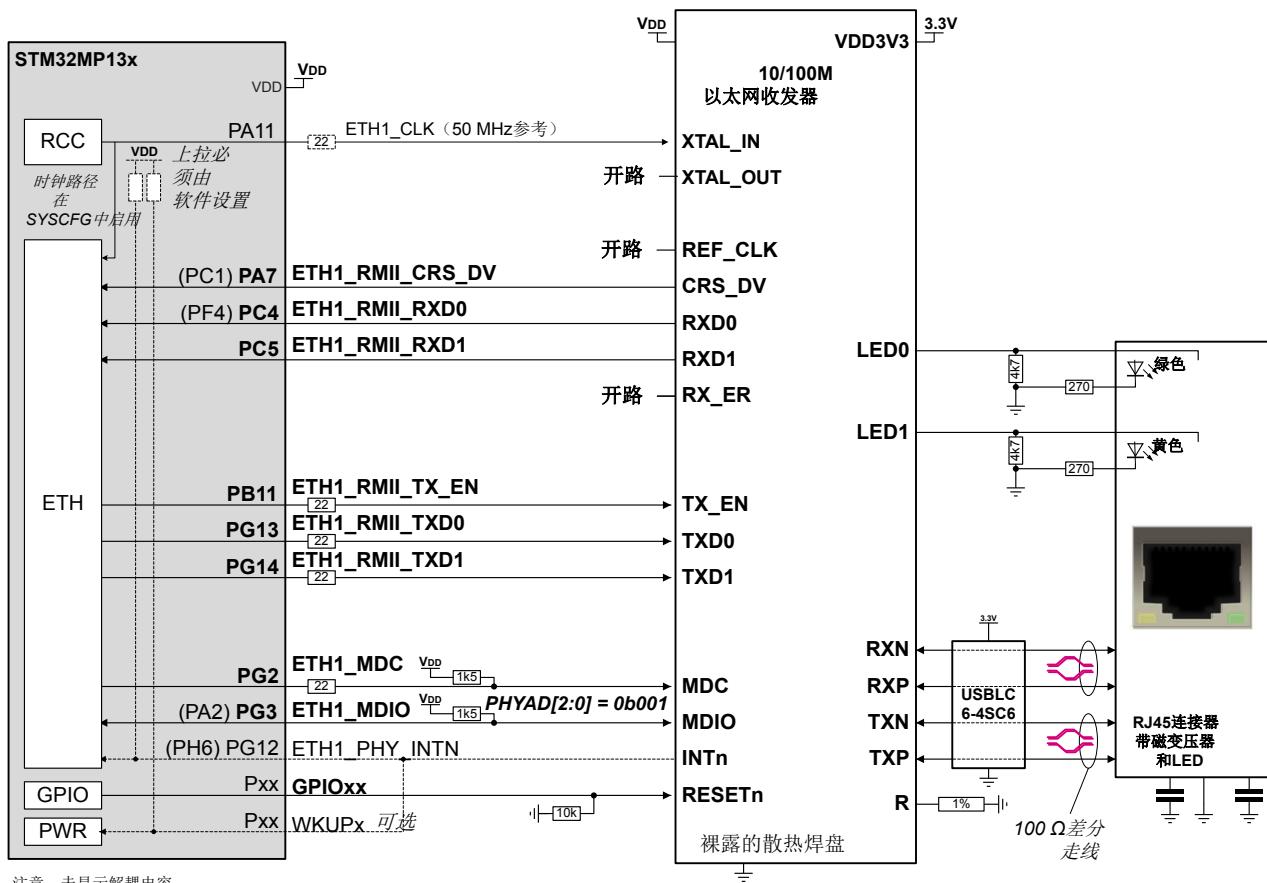

## 8.13 以太网

### 8.13.1 10/100 M 以太网

注意

良好的信号完整性取决于电路板、GPIO 强度设置 (GPIO\_OSPEEDR 寄存器) 和  $V_{DD}$  电压。

如果需要，阻抗匹配电阻必须尽可能靠近输出驱动器引脚布置。以下示例中的值应适用于大多数情况，但可以根据每侧 I/O 驱动强度和 PCB 阻抗进行调整。

图 37. 10/100 M 以太网 PHY 连接示例

在低功耗模式下，RCC 不能为 PHY 提供 25 MHz 参考时钟。因此在平台需要 LAN 唤醒 (WOL) 时，PHY 上需要专用的 25 MHz 晶振。设置 RCC PLL 以便让 PHY 获得 25 MHz 时钟，可以约束其他 RCC 频率。在这种情况下，可以更加灵活地在 PHY 上安排一个专用 25 MHz 晶振。

注意

或者, 如果 PHY 允许并且 RCC 可提供精确的 50 MHz 时钟, 可由 STM32MP13x 器件向 PHY 提供 50 MHz 的 ETH\_CLK, 且 REF\_CLK 在两侧均未连接。这可以在某些 PHY 上节省 BOM、面积以及一些功率。

如要检查 RCC 是否能够提供精确的 50 MHz 时钟 (如果 PHY 允许), 必须根据 HSE 石英频率和 RCC 其他外设核心时钟频率设置进行检查。

图 38. 10/100M 以太网 PHY 连接 (具有来自 RCC 的 REFCLK) 示例

注意: 未显示解耦电容。

由于 RCC 无法在低功耗模式下为 PHY 提供 50 MHz 参考时钟, 因此在平台需要 LAN 唤醒 (WOL) 时, 不能使用该选项。设置 RCC PLL 以便让 PHY 获得 50 MHz 时钟, 可以约束其他 RCC 频率。在这种情况下, 不能使用该选项。

如果具有双以太网接口 (ETH1, ETH2), 每个以太网收发器的 XTAL\_IN 时钟可以连接到 ETH1\_CLK 或 ETH2\_CLK。

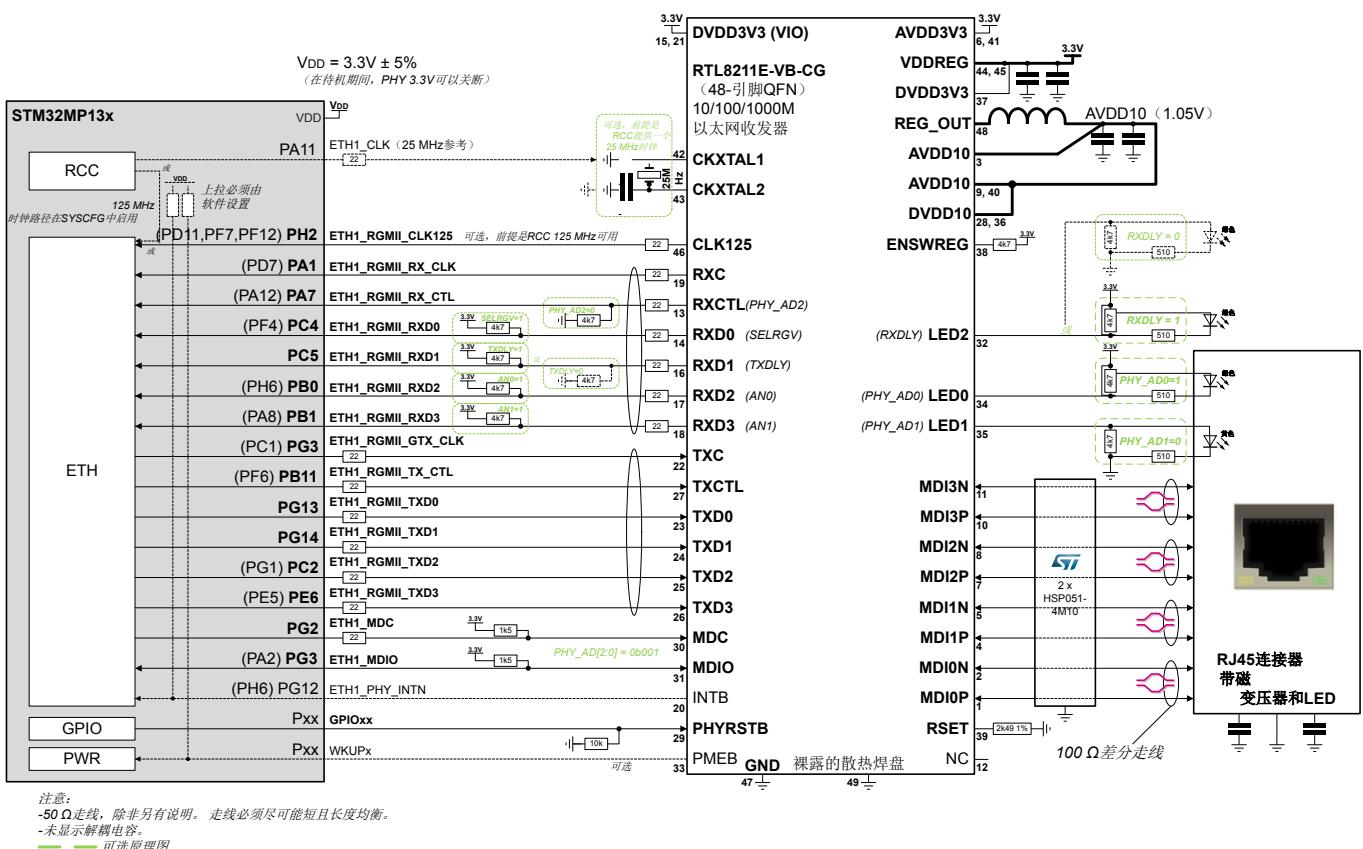

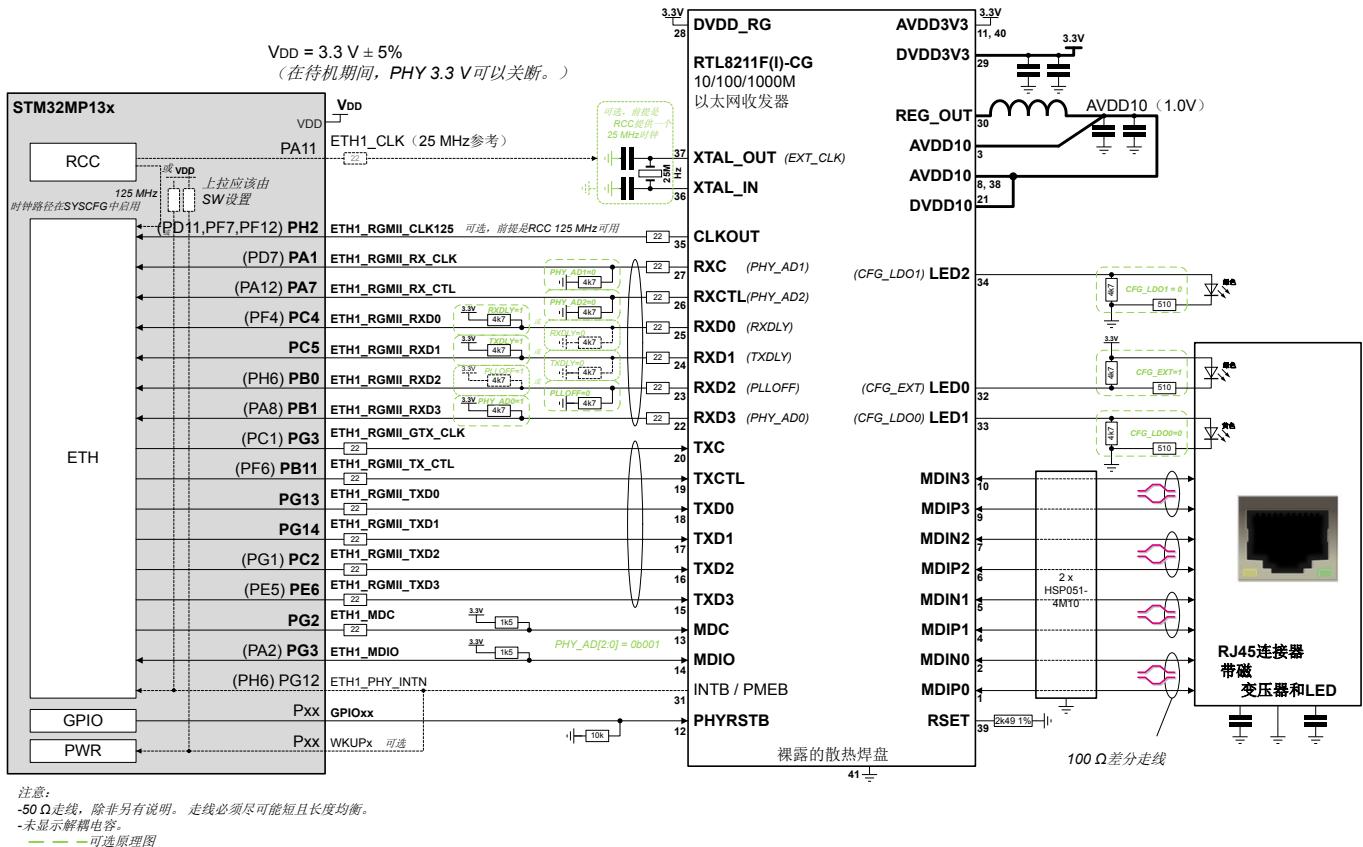

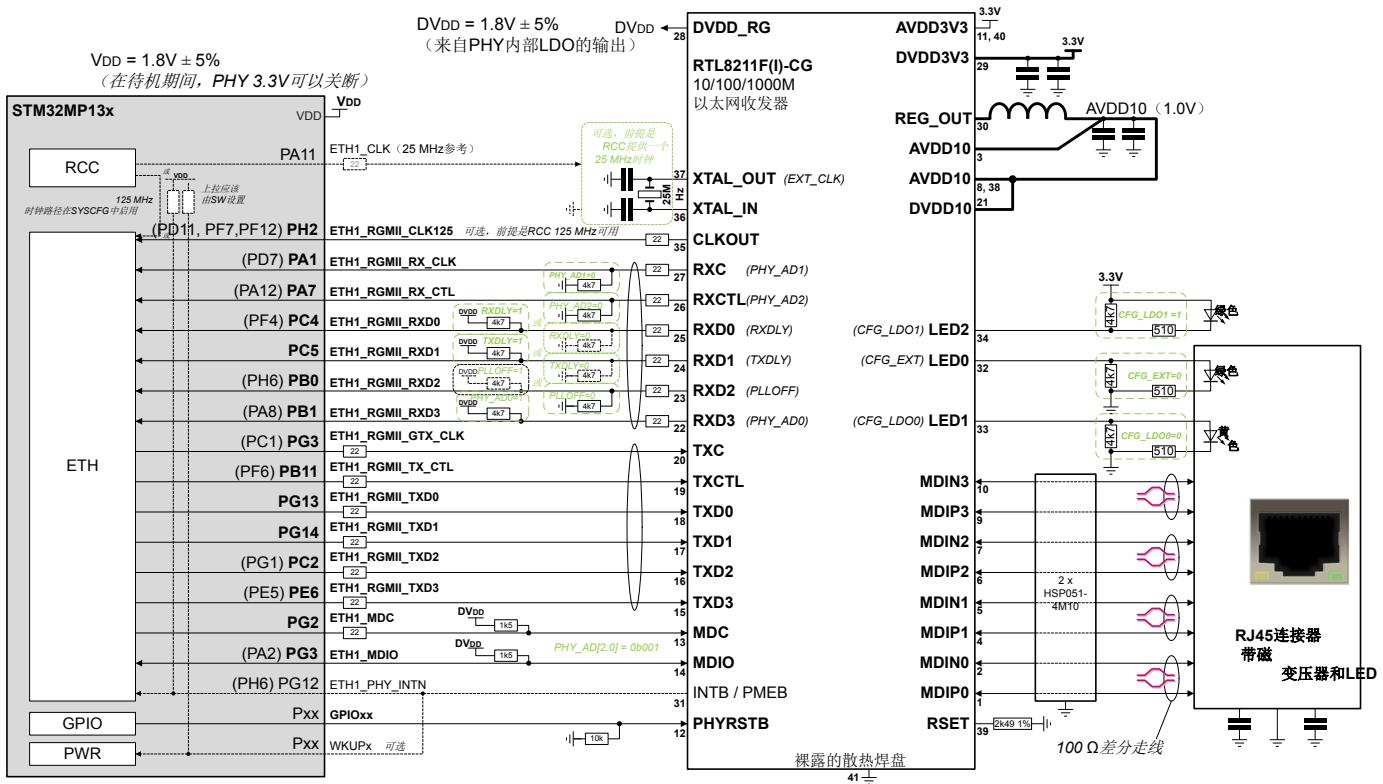

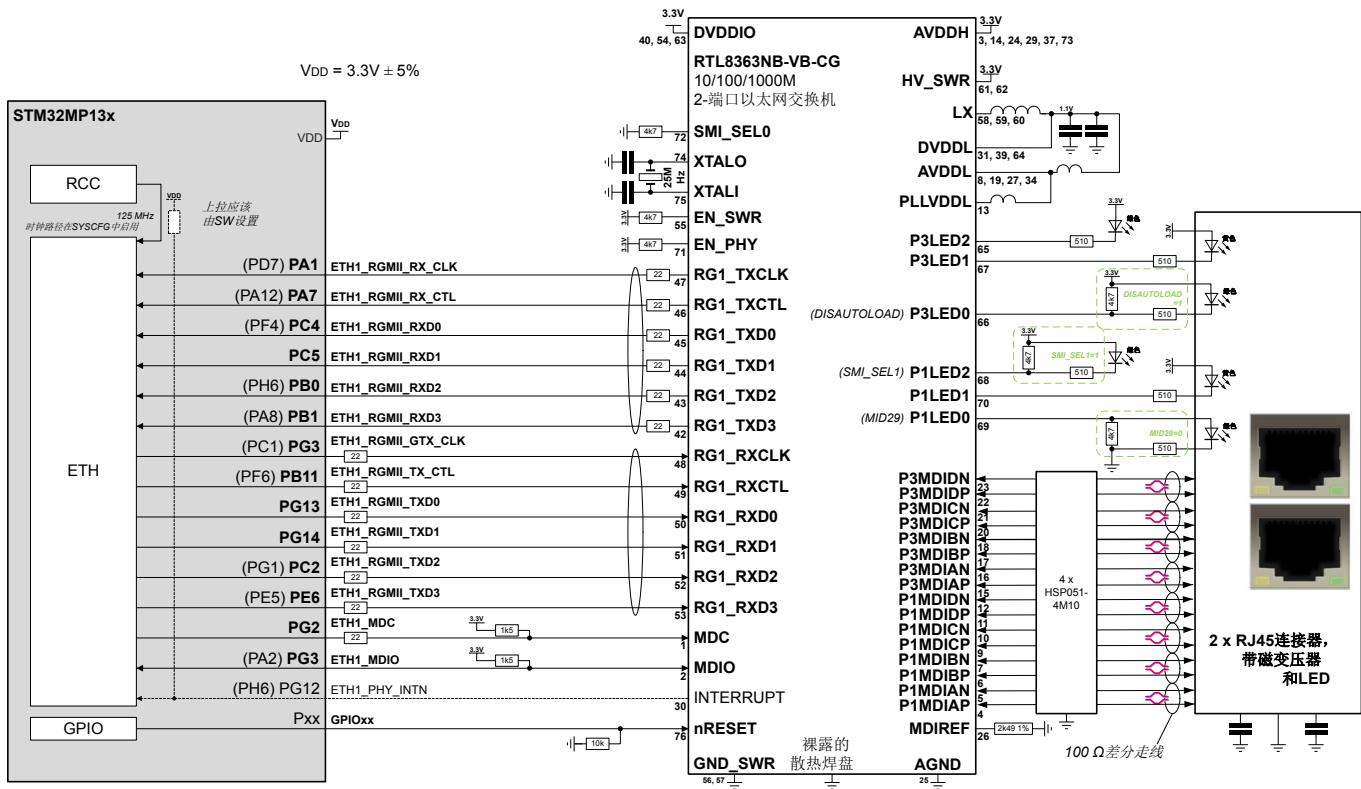

### 8.13.2 千兆以太网

## 注意

良好的信号完整性取决于电路板、GPIO 强度设置 (GPIO OSPEEDR 寄存器) 和  $V_{DD}$  电压。

使用  $V_{DD} = 1.8$  V 时, 需要对 2v5 以下产品的 OTP 位和寄存器 SYSCFG\_HSLVEN2R (HSLVEN\_ETH1 位) 和/或 SYSCFG\_HSLVEN3R (HSLVEN\_ETH2 位) 进行置位, 以确保在用于以太网输出的焊盘上获得最佳速度。

## 警告

当  $V_{DD}$  高于 2.7 V 时, 不得置位 UHSLVEN, 否则可能造成器件永久损坏。

如果需要，阻抗匹配电阻必须尽可能靠近输出驱动器引脚布置。以下示例中的值应适用于大多数情况，但可以根据每侧 I/O 驱动强度和 PCB 阻抗进行调整。

由于 RCC 无法在低功耗模式下为 PHY 提供 25 MHz 参考时钟，因此在平台需要 LAN 唤醒 (WOL) 时，PHY 上需要专用的 25 MHz 晶振。

设置 RCC PLL 以便让 PHY 获得 25 MHz 输出，可以约束其他 RCC 频率。在这种情况下，可以更加灵活地在 PHY 上安排一个专用 25 MHz 振荡器。

图 39. ( $V_{DD}=3.3\text{ V}$ , RTL8211E) 的千兆以太网 PHY 连接示例

图 40. ( $V_{DD}=3.3\text{ V}$ , RTL8211F) 的千兆以太网 PHY 连接示例

图 41.  $V_{DD}=1.8 \text{ V}$  (RTL8211F) 的千兆以太网 PHY 连接示例

图 42.  $V_{DD} = 3.3\text{ V}$  (RTL8363NB-VG) 的千兆以太网 2 端口交换机示例

## 版本历史

表 16. 文档版本历史

| 日期              | 版本 | 变更                                             |

|-----------------|----|------------------------------------------------|

| 2023 年 2 月 13 日 | 1  | 初始版本                                           |

| 2023 年 6 月 23 日 | 2  | 更新了：<br>• 第 8.1 节: 时钟<br>• 图 28<br>• 表 2. 参考文档 |

| 2023 年 9 月 25 日 | 3  | 更新了：<br>• 图 39<br>• 图 40<br>• 图 41<br>• 图 42   |

## 目录

|              |                              |           |

|--------------|------------------------------|-----------|

| <b>1</b>     | <b>概述</b>                    | <b>2</b>  |

| <b>2</b>     | <b>电源</b>                    | <b>5</b>  |

| <b>2.1</b>   | <b>概述</b>                    | <b>6</b>  |

| <b>2.1.1</b> | 独立 ADC 电源和参考电压               | 6         |

| <b>2.1.2</b> | 独立 I/O 电源轨                   | 7         |

| <b>2.1.3</b> | 面向 GPIO 的 HSLV 模式和补偿单元       | 7         |

| <b>2.1.4</b> | 电池备份                         | 8         |

| <b>2.1.5</b> | 稳压器                          | 8         |

| <b>2.2</b>   | <b>电源方案</b>                  | <b>8</b>  |

| <b>2.3</b>   | <b>复位和电源监控</b>               | <b>11</b> |

| <b>2.3.1</b> | 上电复位 (POR)/下电复位 (PDR)        | 11        |

| <b>2.3.2</b> | 可编程电压检测器 (PVD)               | 11        |

| <b>2.3.3</b> | 应用和系统复位                      | 12        |

| <b>3</b>     | <b>封装</b>                    | <b>14</b> |

| <b>3.1</b>   | <b>封装选择</b>                  | <b>14</b> |

| <b>3.2</b>   | <b>引脚复用映射</b>                | <b>15</b> |

| <b>4</b>     | <b>时钟</b>                    | <b>16</b> |

| <b>4.1</b>   | <b>HSE OSC 时钟</b>            | <b>16</b> |

| <b>4.1.1</b> | 外部时钟源 (HSE 旁路)               | 16        |

| <b>4.1.2</b> | 外部晶振/陶瓷谐振器 (HSE 晶振)          | 17        |

| <b>4.2</b>   | <b>LSE OSC 时钟</b>            | <b>17</b> |

| <b>4.2.1</b> | 外部时钟源 (LSE 旁路)               | 17        |

| <b>4.2.2</b> | 外部晶振/陶瓷谐振器 (LSE 晶振)          | 17        |

| <b>4.3</b>   | <b>时钟安全系统 (CSS) 和时钟监控</b>    | <b>18</b> |

| <b>4.3.1</b> | HSE                          | 18        |

| <b>4.3.2</b> | LSE                          | 18        |

| <b>5</b>     | <b>启动配置</b>                  | <b>19</b> |

| <b>5.1</b>   | <b>启动模式选择</b>                | <b>19</b> |

| <b>5.2</b>   | <b>启动引脚连接</b>                | <b>21</b> |

| <b>5.3</b>   | <b>嵌入式自举模式</b>               | <b>23</b> |

| <b>6</b>     | <b>调试管理</b>                  | <b>24</b> |

| <b>6.1</b>   | <b>SWJ 调试端口 (串行接口和 JTAG)</b> | <b>24</b> |

| <b>6.2</b>   | <b>引脚排列和调试端口引脚</b>           | <b>24</b> |

| <b>6.2.1</b> | JTAG 引脚上的内部上拉/下拉电阻           | 24        |

| <b>6.2.2</b> | 使用标准 JTAG 连接器的调试端口连接         | 25        |

|                       |                                                     |           |

|-----------------------|-----------------------------------------------------|-----------|

| 6.2.3                 | 使用 STDC14 连接器的调试端口和 UART 连接 . . . . .               | 26        |

| 6.2.4                 | 并行跟踪和 HDP . . . . .                                 | 26        |

| 6.2.5                 | 调试触发器和 LED . . . . .                                | 27        |

| <b>7</b>              | <b>建议 . . . . .</b>                                 | <b>29</b> |

| 7.1                   | PCB (印刷电路板) . . . . .                               | 29        |

| 7.2                   | 元件位置 . . . . .                                      | 29        |

| 7.3                   | 接地和供电 ( $V_{SSx}$ 、 $V_{DDx}$ ) . . . . .           | 29        |

| 7.4                   | I/O 速度设置 . . . . .                                  | 29        |

| 7.5                   | PCB 层叠和技术 . . . . .                                 | 33        |

| 7.6                   | 解耦和封装扇出布线 . . . . .                                 | 36        |

| 7.7                   | ESD/EMI 保护 . . . . .                                | 36        |

| 7.8                   | 敏感信号 . . . . .                                      | 36        |

| 7.9                   | 不使用的 I/O 和特性 . . . . .                              | 36        |

| <b>8</b>              | <b>参考设计示例 . . . . .</b>                             | <b>37</b> |

| 8.1                   | 时钟 . . . . .                                        | 37        |

| 8.2                   | 复位 . . . . .                                        | 37        |

| 8.3                   | 启动模式 . . . . .                                      | 38        |

| 8.4                   | SWD/JTAG 接口 . . . . .                               | 38        |

| 8.5                   | 电源 . . . . .                                        | 39        |

| 8.5.1                 | 采用 DDR3L 的 3.3 V I/O 分立电源示例 . . . . .               | 39        |

| 8.5.2                 | STPMIC1 电源示例 (3.3 V I/O, 采用 DDR3L) . . . . .        | 40        |

| 8.5.3                 | 采用 LPDDR2/LPDDR3 的 1.8 V I/O STPMIC1 电源示例 . . . . . | 41        |

| 8.6                   | DDR3/DDR3L SDRAM . . . . .                          | 42        |

| 8.7                   | LPDDR2/3 SDRAM . . . . .                            | 43        |

| 8.8                   | SD-Card 无外部电平转换器 . . . . .                          | 44        |

| 8.9                   | eMMC Flash . . . . .                                | 46        |

| 8.10                  | SLC NAND Flash . . . . .                            | 47        |

| 8.11                  | 串行 NOR/NAND-Flash . . . . .                         | 48        |

| 8.12                  | USB . . . . .                                       | 50        |

| 8.13                  | 以太网 . . . . .                                       | 52        |

| 8.13.1                | 10/100 M 以太网 . . . . .                              | 52        |

| 8.13.2                | 千兆以太网 . . . . .                                     | 54        |

| <b>版本历史 . . . . .</b> | <b>58</b>                                           |           |

| <b>表一览 . . . . .</b>  | <b>61</b>                                           |           |

| <b>图一览 . . . . .</b>  | <b>62</b>                                           |           |

## 表一覽

|              |                                                      |    |

|--------------|------------------------------------------------------|----|

| <b>表 1.</b>  | 适用产品 . . . . .                                       | 1  |

| <b>表 2.</b>  | 参考文档 . . . . .                                       | 2  |

| <b>表 3.</b>  | 术语表 . . . . .                                        | 2  |

| <b>表 4.</b>  | ANASWVDD 和 EN_BOOSTER 的推荐设置 . . . . .                | 7  |

| <b>表 5.</b>  | 按封装分类的解耦建议 . . . . .                                 | 10 |

| <b>表 6.</b>  | 提供未使用功能的用法 . . . . .                                 | 10 |

| <b>表 7.</b>  | STM32MP13x 封装总览 . . . . .                            | 14 |

| <b>表 8.</b>  | 启动模式 . . . . .                                       | 19 |

| <b>表 9.</b>  | UART 可能的启动引脚 . . . . .                               | 20 |

| <b>表 10.</b> | $V_{DD} = 3.3\text{ V}$ 典型值时的 OSPEEDR 设置示例 . . . . . | 30 |

| <b>表 11.</b> | $V_{DD} = 1.8\text{ V}$ 典型值时的 OSPEEDR 设置示例 . . . . . | 31 |

| <b>表 12.</b> | 振荡器或晶振的 HSE BOM . . . . .                            | 37 |

| <b>表 13.</b> | U(S)ART 可能的启动引脚 . . . . .                            | 38 |

| <b>表 14.</b> | SWD/JTAG 接口 . . . . .                                | 38 |

| <b>表 15.</b> | USB 高速 PCB 路由建议 . . . . .                            | 51 |

| <b>表 16.</b> | 文档版本历史 . . . . .                                     | 58 |

## 图一覽

|       |                                                  |    |

|-------|--------------------------------------------------|----|

| 图 1.  | 供电方案                                             | 5  |

| 图 2.  | 上电复位/下电复位波形                                      | 11 |

| 图 3.  | PVD 阈值                                           | 12 |

| 图 4.  | 复位引脚电路简图                                         | 13 |

| 图 5.  | STM32CubeMX 示例截图                                 | 15 |

| 图 6.  | HSE 时钟源                                          | 16 |

| 图 7.  | LSE 时钟源                                          | 17 |

| 图 8.  | 启动模式选择                                           | 21 |

| 图 9.  | BOOT 引脚的典型连接示意图                                  | 22 |

| 图 10. | 启动流程简图                                           | 23 |

| 图 11. | 主机到板的连接                                          | 24 |

| 图 12. | JTAG/SWD MIPI10 连接器实现示例                          | 25 |

| 图 13. | JTAG/SWD/UART VCP STDC14 连接器实现示例                 | 26 |

| 图 14. | Mictor-38 上带 JTAG/SWD 的并行跟踪端口实现示例                | 27 |

| 图 15. | LED 连接示例                                         | 28 |

| 图 16. | 各种负载和电压下的 I/O 速度总结                               | 30 |

| 图 17. | 4 层 PCB 层叠示例 (仅采用 PTH 过孔)                        | 33 |

| 图 18. | 6 层 PCB 层叠示例 (采用 PTH 过孔、埋藏式过孔, 以及激光钻孔)           | 34 |

| 图 19. | 0.8mm 间距封装的 PCB 规则示例 (采用 PTH 过孔)                 | 34 |

| 图 20. | 0.5mm 间距封装的 PCB 规则示例 (采用激光过孔和 PTH 过孔)            | 35 |

| 图 21. | HSE 推荐的振荡器/晶振选项的原理图                              | 37 |

| 图 22. | 采用 3.3 V I/O 和 DDR3L 的分立电源示例                     | 39 |

| 图 23. | STPMIC1 电源示例 (3.3 V I/O, 采用 DDR3L)               | 40 |

| 图 24. | 采用 LPDDR2/LPDDR3 的 1.8 V I/O STPMIC1 电源示例        | 41 |

| 图 25. | DDR3L 16 位连接示例                                   | 42 |

| 图 26. | LPDDR2/LPDDR3 16 位连接示例                           | 43 |

| 图 27. | 无外部电平转换器的 SD 卡示例 (非 UHS-I 模式连接)                  | 44 |

| 图 28. | 无外部电平转换器的 SD 卡示例 (UHS-I 模式连接)                    | 45 |

| 图 29. | 使用外部电源开关为 VDDSDx 供电                              | 45 |

| 图 30. | eMMC 连接示例                                        | 46 |

| 图 31. | SLC NAND-Flash 连接示例                              | 47 |

| 图 32. | 串行 Flash 连接示例                                    | 48 |

| 图 33. | 双串行 Flash 连接示例                                   | 49 |

| 图 34. | USB 两端口主机高速                                      | 50 |

| 图 35. | USB 主机高速 + OTG 高速连接示例                            | 50 |

| 图 36. | USB 高速 PCB 走线示例                                  | 51 |

| 图 37. | 10/100 M 以太网 PHY 连接示例                            | 52 |

| 图 38. | 10/100M 以太网 PHY 连接 (具有来自 RCC 的 REFCLK) 示例        | 53 |

| 图 39. | ( $V_{DD}=3.3$ V, RTL8211E) 的千兆以太网 PHY 连接示例      | 54 |

| 图 40. | ( $V_{DD}=3.3$ V, RTL8211F) 的千兆以太网 PHY 连接示例      | 55 |

| 图 41. | $V_{DD}=1.8$ V (RTL8211F) 的千兆以太网 PHY 连接示例        | 56 |

| 图 42. | $V_{DD} = 3.3$ V (RTL8363NB-VG) 的千兆以太网 2 端口交换机示例 | 57 |

**重要通知 - 仔细阅读**

意法半导体公司及其子公司（“ST”）保留随时对 ST 产品和/或本文档进行变更、更正、增强、修改和改进的权利，恕不另行通知。买方在订货之前应获取关于意法半导体产品的最新信息。ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对意法半导体产品的选择和使用，意法半导体概不承担与应用协助或买方产品设计相关的任何责任。

意法半导体不对任何知识产权进行任何明示或默示的授权或许可。

转售的意法半导体产品如有不同于此处提供的信息的规定，将导致意法半导体针对该产品授予的任何保证失效。

ST 和 ST 徽标均为意法半导体的商标。关于意法半导体商标的其他信息，请访问 [www.st.com/trademarks](http://www.st.com/trademarks)。其他所有产品或服务名称是其各自所有者的财产。

本文档中的信息取代本文档所有早期版本中提供的信息。

© 2023 STMicroelectronics - 保留所有权利