## STPMIC1 PCB 布局指南

## 简介

本应用笔记旨在提供一些关于如何在 4 层 PCB 上放置 STPMIC1 的信息，主要关注走线布线和具有大电流路径的开关部分。

因此，正确的 PCB 布线以及元件放置是实现高度集成电源管理的关键因素，必须考虑以下话题：

- 基于电感的 DC/DC 转换的内在行为导致的高频开关电流

- 数字接口的信号完整性

- 耗散功率的热管理

此外还提供了完整的 PCB 设计示例，可作为 STPMIC1 在最终应用中的自定义使用参考。

## 1 电源部分布局注意事项

由于开关电源周围的开关电流大，还有敏感的控制信号，因此合适的 PCB 布局对开关电源的设计极其重要。DC/DC 转换器电源部分布局不当会直接导致功率损耗、输出纹波、EMI 干扰的增加以及调节不准。不常见的影响有：数字线路上的感应噪声，回路不稳定，来自被动元件的可听噪声。个别情况下，较长走线的杂散电感可能导致异常的电压尖峰，进而可能使 STPMIC1 高于其最大额定电压（AMR）。在接下来的章节中，阐述了关键电流路径的根本原因，并提出一些关于如何限制它们对 STPMIC1 性能的影响的建议。

### 1.1 一般建议

- 始终考虑并确定返回电流的流动方向和方式

- 在所有开关 DC/DC 转换器配置中，关键走线的最小长度以及接地和电源平面的使用是一个关键因素

- 在关键电流路径沿线减少过孔使用

- 仅在板件的模拟部分路由模拟信号

- 不跨接地平面间隙路由模拟信号（电压反馈信号）

- 如果接地或电源平面必须分割（即机械和/或电气），则不要在相邻层上铺设任何走线穿过间隙。

- 不要低估解耦电容的重要性。解耦是将电容器尽可能靠近 STPMIC1 以提供瞬态开关电流的过程。在 DC/DC 转换器中，在 STPMIC1 附近放置 L-C 网络可以将引起过压峰值的走线电感降至最低。如果它们超过 AMR 的值，器件可能损坏

- 解耦电容的高电容值对低频解耦效果很重要，但对高频解耦效果则不太重要，此时最重要的原则是降低与解耦电容串联的杂散电感

- 所有无源元件应尽可能地靠近 STPMIC1 引脚，但是如果设备在一个较小区域内放置许多稳压器，要做到这一点比较困难。无源元件的放置标准是通过以下优先级来管理它们与 STPMIC1 的距离，最高优先级对应最短距离：

1. 每个降压转换器的输入电容和升压转换器的输出电容

2. 每个 LDO 和设备电源的输入电容器（VIN、INTLDO...）

3. 每个 DC/DC 转换器的电感

4. 每个降压转换器的输出电容和升压转换器的输入电容

5. 每个 LDO 稳压器的输出电容

- 应对电容器进行分组和定向，使每个 DC/DC 的输入电容和输出电容的接地侧彼此非常靠近，立即返回到接平面，并且相对远离另一个 DC/DC 和 LDO 电容器的接地回路

- 输出电容的正极必须尽可能靠近电感，从它的连接点开始，电压反馈走线应该朝向 VOUT 引脚

## 1.2 降压转换器关键电流路径

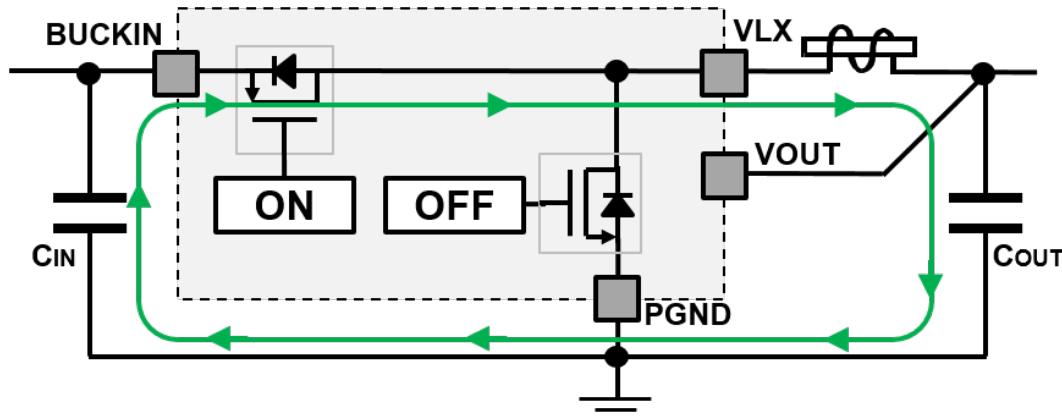

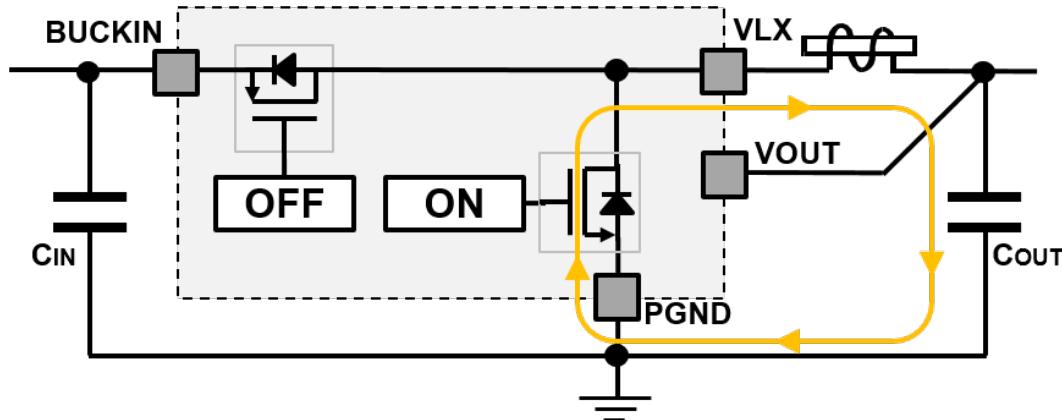

图 1. 降压转换器原理图（充电阶段）和图 2. 降压转换器原理图（放电阶段）显示了降压转换器的简化原理图，其中绿色/橙色表示电感充/放电阶段开关电流的关键路径。

图 1. 降压转换器原理图（充电阶段）

图 2. 降压转换器原理图（放电阶段）

电容器和电感应尽可能靠近 STPMIC1，并采用又宽又短的走线方式布线。输入电容是 PCB 布局中最关键的元件。它必须尽可能地靠近 BUCKIN 引脚和相关 PGND 引脚，将接地回路最小化。如果路由正确，输入电容会削去由器件的开关活动引起的高压尖峰。

将输出电容置于电感器附近。建议在单个公共点进行连接或使用适当数量的通孔立即连接到接地平面：

- 输出电容的接地侧

- 输入电容的接地侧

- 设备的 PGND 引脚

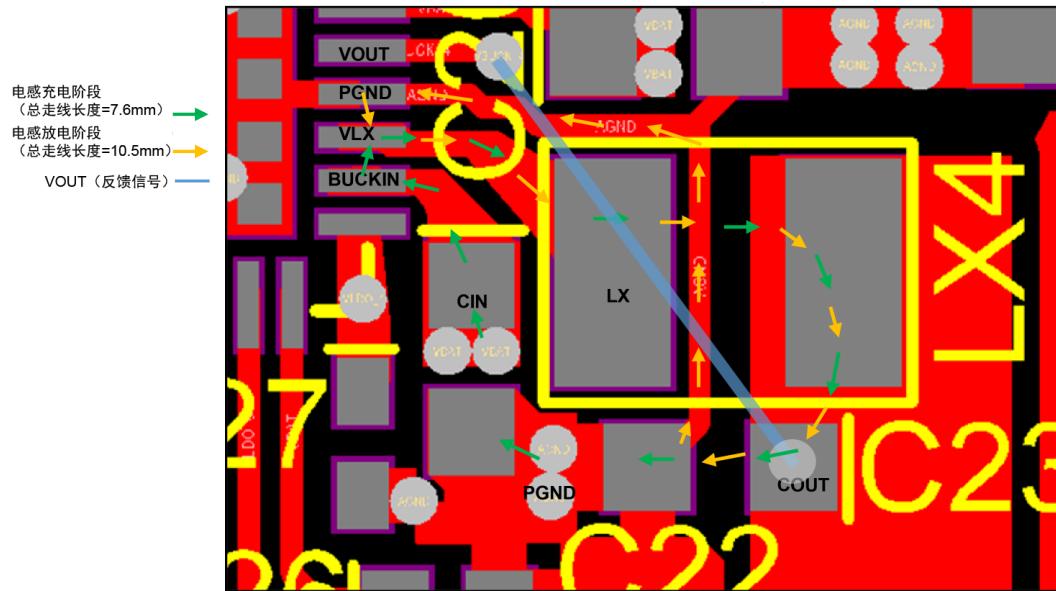

输出电压反馈信号应准确地在输出电容上拾取，并路由到 V<sub>OUT</sub> 引脚（反馈信号），以避免网络嘈杂。为充分减少噪声拾取，其走线应尽可能地小，且远离任何开关走线，建议在单独的层中布线，通过接地平面屏蔽开关线路（如图 3. 降压参考路由带关键路径中所示，反馈信号的轨迹在底层，浅蓝色走线）。

图 3. 降压参考路由带关键路径

## 1.3 升压转换器关键电流路径

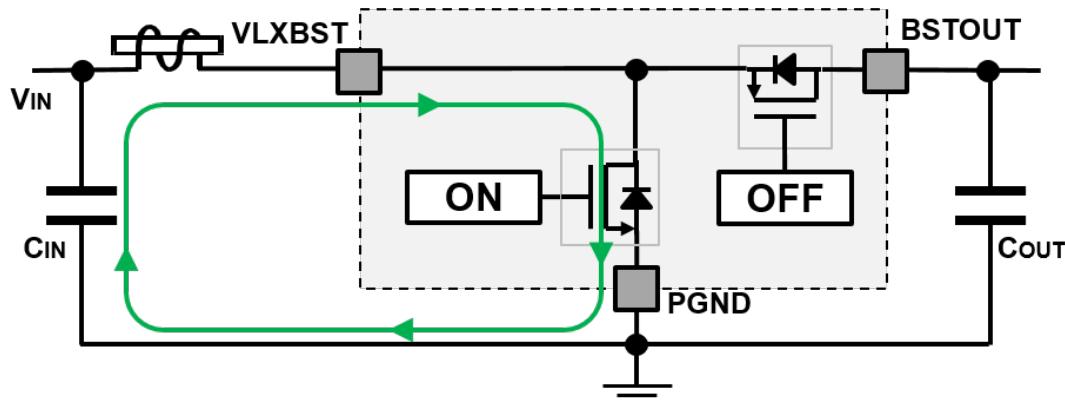

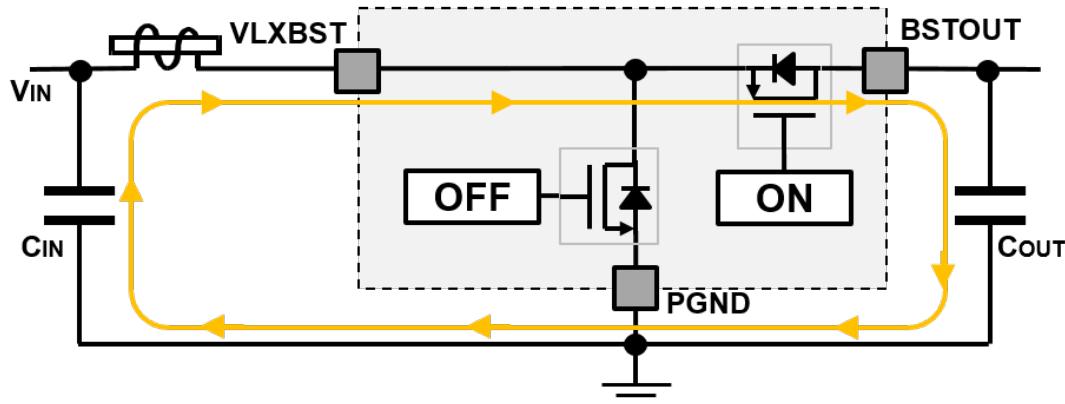

图 4. 升压转换器原理图（充电阶段）和图 5. 升压转换器原理图（放电阶段）显示了升压转换器的简化原理图，其中绿色/橙色表示电感充/放电阶段开关电流的关键路径。

图 4. 升压转换器原理图（充电阶段）

图 5. 升压转换器原理图（放电阶段）

$VLXBST$  节点的轨迹应进行优化（保持最小面积）以便能够处理大电流，因为这是升压转换器中噪音最大的节点。注意附近敏感节点的任何走线，例如降压转换器的反馈信号应该与  $VLXBST$  节点保持距离。

输出电容的位置非常重要，因为  $BSTOUT$  引脚也是升压调节回路的反馈点，因此应让其靠近器件，并采用既短且宽的走线进行布线，尽量减少寄生电感。

输入电容的接地侧应通过较短的走线路由到 STPMIC1 电源接地引脚（ $PGND$ ）和接地平面。在输入电容的  $V_{IN}$  侧与电感之间保持较短的距离，以保证  $V_{IN}$  沿线的电压稳定而干净，尽管开关活动会引起大的电流纹波。

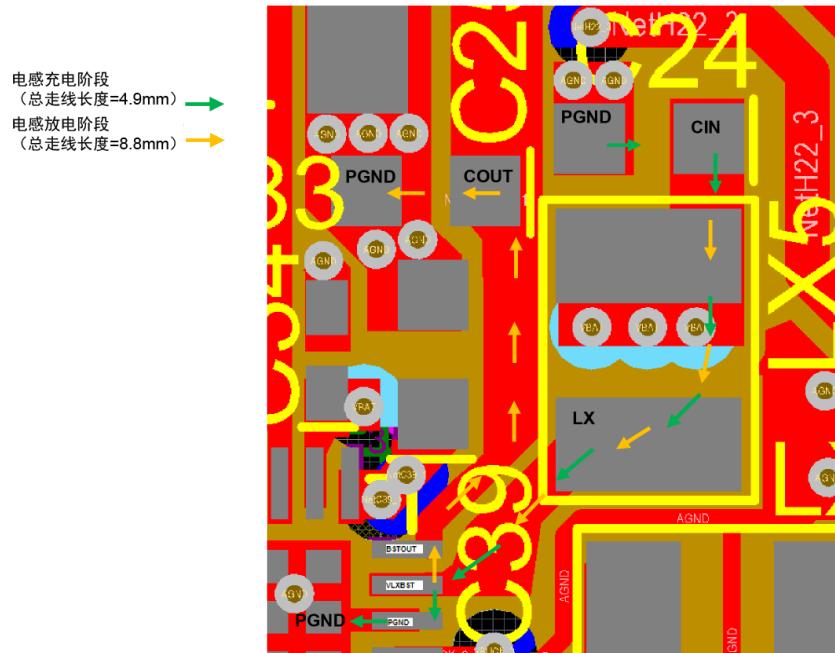

图 6. 升压参考路由带关键路径 显示 STEVAL-PMIC1x 的升压转换器部分的 PCB 布局

图 6. 升压参考路由带关键路径

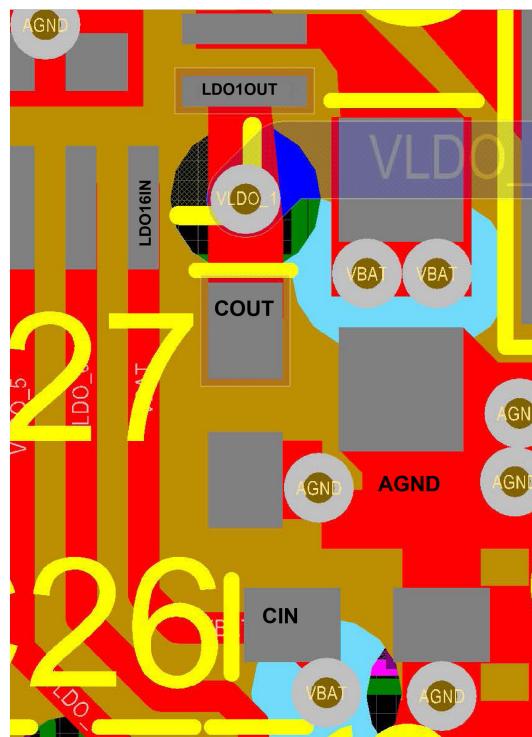

## 1.4 LDO

LDO 本身不受开关活动噪声的影响，但由于它们在物理上非常接近有源降压和升压转换器，注入的噪声是一个问题。为此，每个 LDO 电源都应该通过一个解耦电容进行滤波，该解耦电容放在尽可能靠近相关 LDO 的输入引脚的位置。此外，为了确保获得最佳性能，输出电容应靠近 LDO 输出，其接地侧尽可能远离任何开关接地回路，以避免噪声注入。

图 7. LDO 参考路由

## 2 热方面的考虑

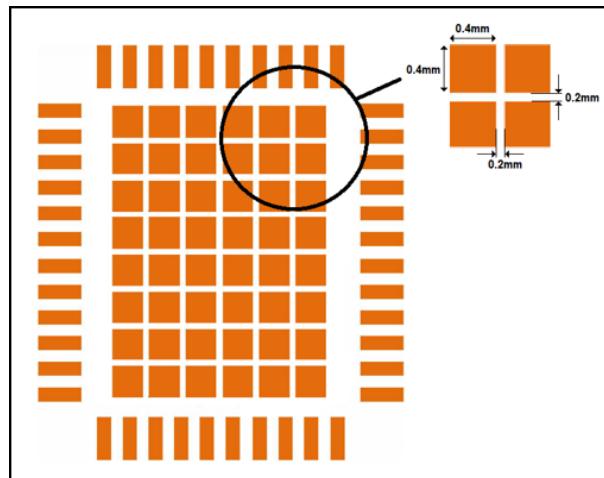

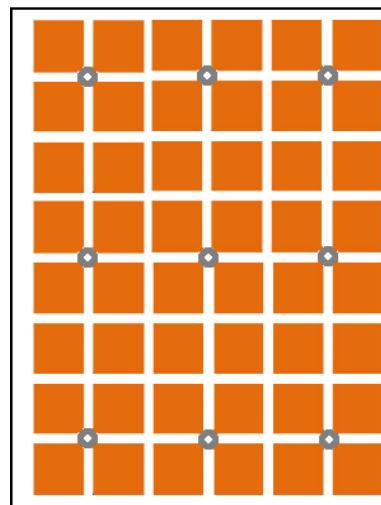

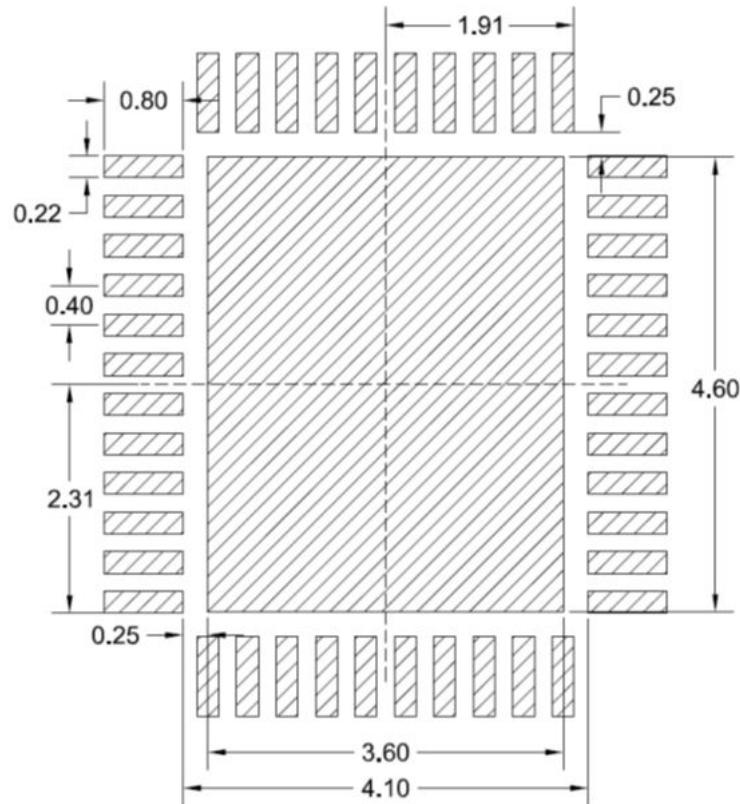

STPMIC1 的封装为 WFQFN 5x6x0.8 mm，采用裸露焊盘（ePad），这有助于器件的热功率耗散。在 PCB 中，热通孔将热量从 IC 带走，这些通孔通常有十二个左右，排成阵列。强烈建议在器件的 ePad 下方放置至少 9 个通孔（ground-fill），因为 PCB 主要通过使用接地面来改善热功率耗散性能，从而起到散热效果。

如图 8. 裸露焊盘焊接模板和图 9. 通孔放置建议中所示，裸露焊盘焊接区域可以被分割成对称的焊盘阵列，将锡膏涂敷于裸露焊盘面积的约 50% 至 75%。

图 8. 裸露焊盘焊接模板

图 9. 通孔放置建议

图 10. 建议的外形轮廓

### 3 数字接口布局注意事项

为了避免 DC/DC 转换器的开关活动对数字信号形成噪声注入，在相邻层上放置接地平面以屏蔽数字走线是一种效果不错的做法。其他建议：

- 将混合信号 PCB 的模拟和数字部分单独分区

- 仅在板件的数字部分中进行数字信号布线 ( $\text{I}^2\text{C BUS}$ )

- 如果接地或电源平面由于特定原因（即机械和/或电气）而被分割，则不要在相邻层上铺设任何走线穿过间隙。

- 如果 VIO 的电源远离 STPMIC1，VIO 引脚的数字解耦电容应直接连接到数字接地

## 4 PCB示例：STPMIC1评估板

表 1.4 层层叠 PCB

| 层     | 层叠       |

|-------|----------|

| 顶部    | 元件/电源/信号 |

| 中信号 1 | GND      |

| 中信号 2 | 电源/接地    |

| 底部    | 小信号/接地   |

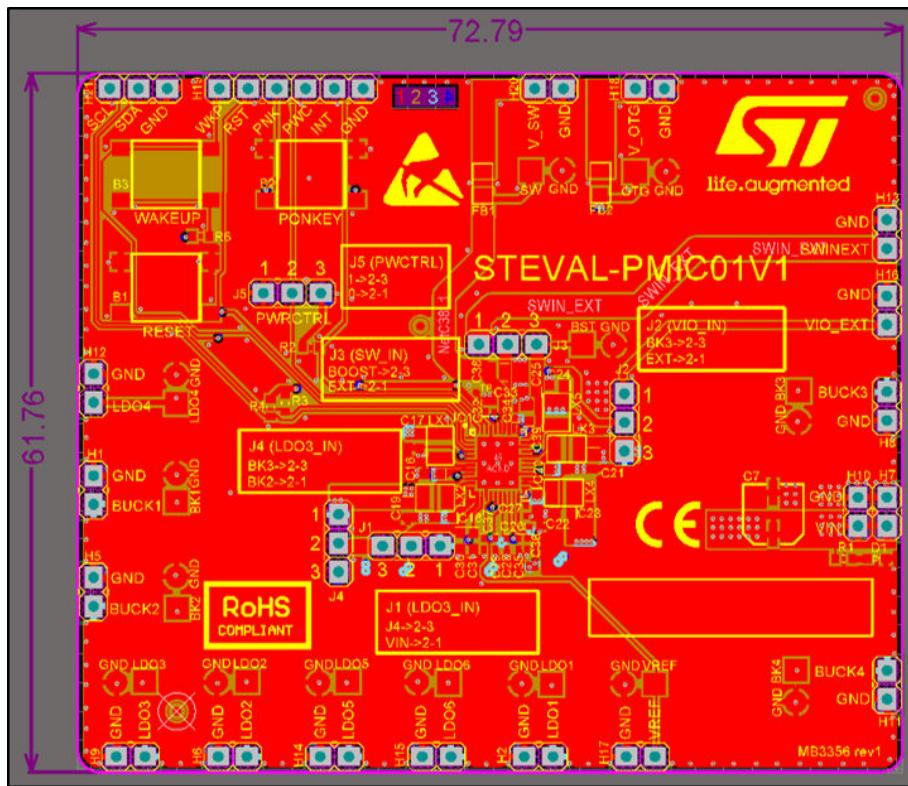

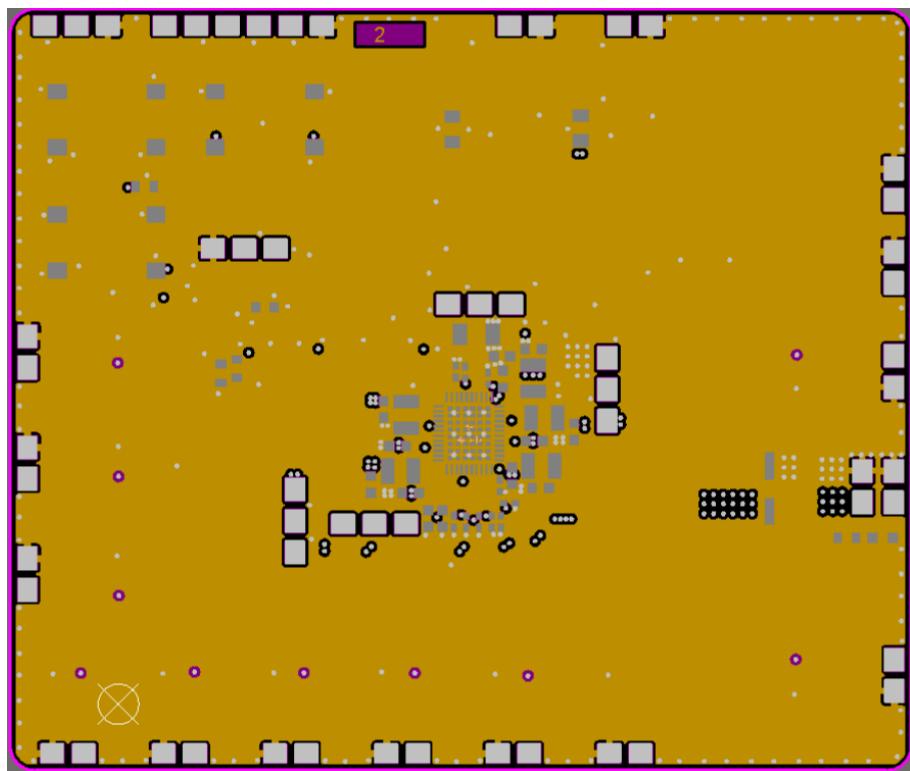

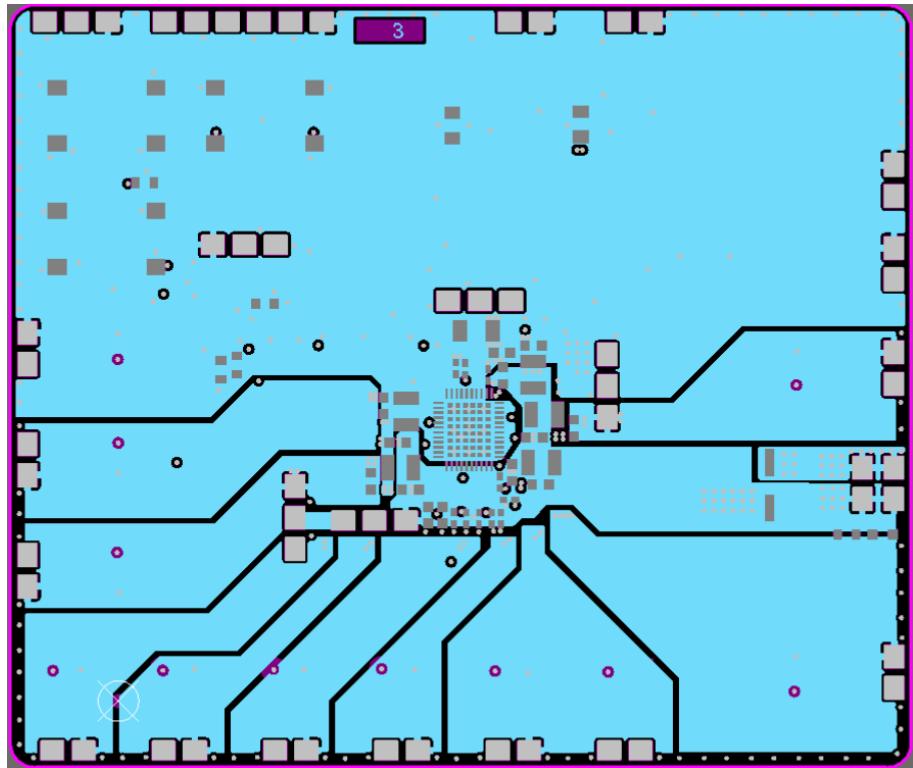

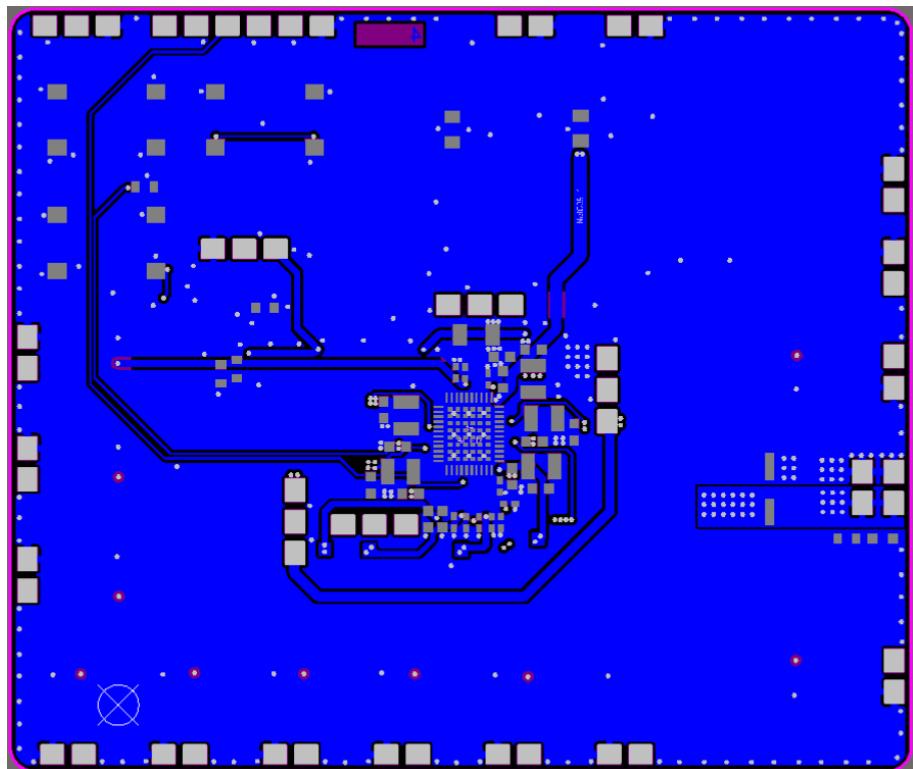

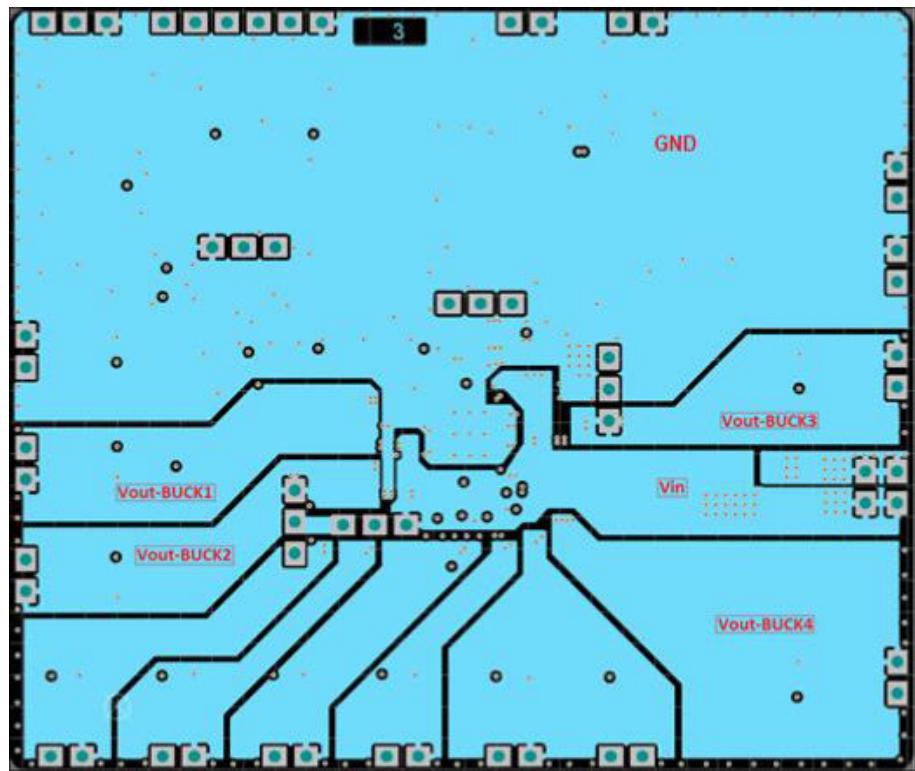

下图显示了 STEVAL-PMIC1x 评估板的板件布局。所有指南都适用于板件草图绘制，以便 STPMIC1 获得最佳性能。

图 11. 配备 STPMIC1 器件的评估板

图 12. 顶层（元件/电源/信号）

图 13. 中间层 1 (接地)

图 14. 中间层 2（电源/接地）

图 15. 底层（小信号/接地）

## 4.1 电源和接地平面

由于电源和接地都以平面的方式存在，感应效应被最小化，为 STPMIC1 提供一个非常低的阻抗路径。使用具有多个通孔的连续接地层能够有效实现低阻抗接地回路，但为了使 PCB 所有区域保持低阻抗，请勿缩小或分割接地层。

下面是中间层 1 的接地平面视图，GND 过孔围绕 PCB 边缘放置，间距仅有 2 mm（参见图 16. 中间层 1（接地平面）获取详细信息）

图 16. 中间层 1（接地平面）

在可能的情况下，建议所有大电流电源（如  $V_{IN}$ 、 $V_{OUT}$  和  $V_{BUS}$ ）使用扁平且较大的形状。这样可以减少功率损耗。检查接地平面和电源平面时，要确保平面的连续性不受过孔数量过多的影响。

中间层 2 的电源平面、过孔放置和平面形状的示例如下，用于将稳压器的  $V_{IN}$  和所有  $V_{OUT}$  路由到连接器头。

图 17. 中间层 2 电源/GND

## 4.2 通孔

虽然接地平面是一个很好的接地参考，但沿接地回路的通孔会在高频时会引入一些杂散电感。考虑到杂散电感是并行的，在平面上放置多个通孔可以减少这种影响。这些通孔必须以这样一种方式间隔开来，即电源平面不会被过度切割。

表 2. 通孔孔径

| 通孔类型 | 孔径     | 焊盘尺寸    |

|------|--------|---------|

| 通孔   | 0.2 mm | 0.45 mm |

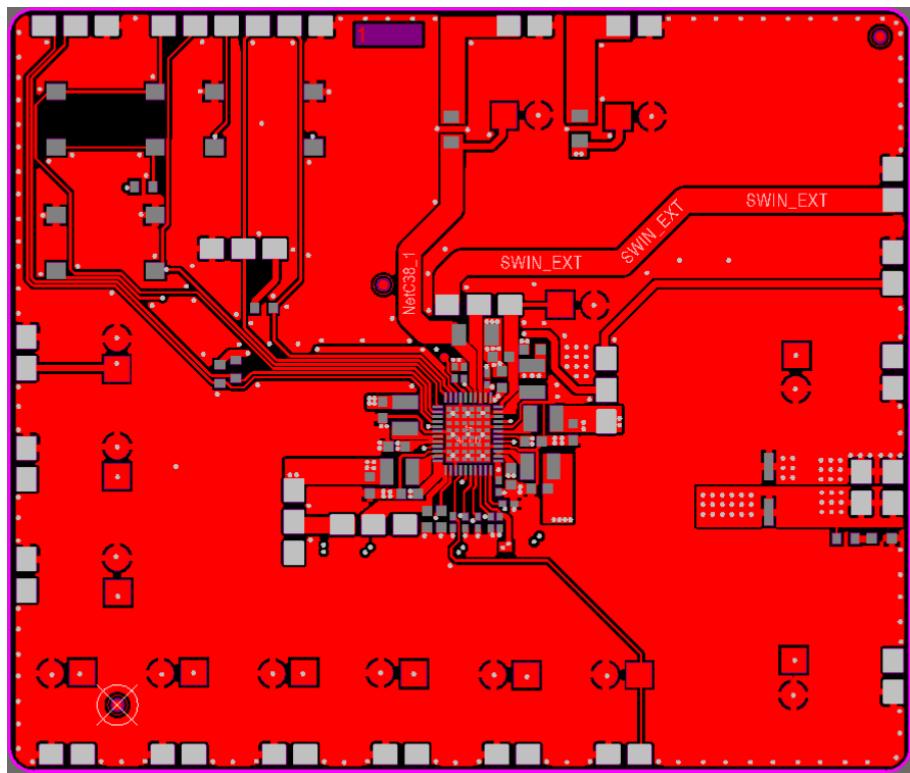

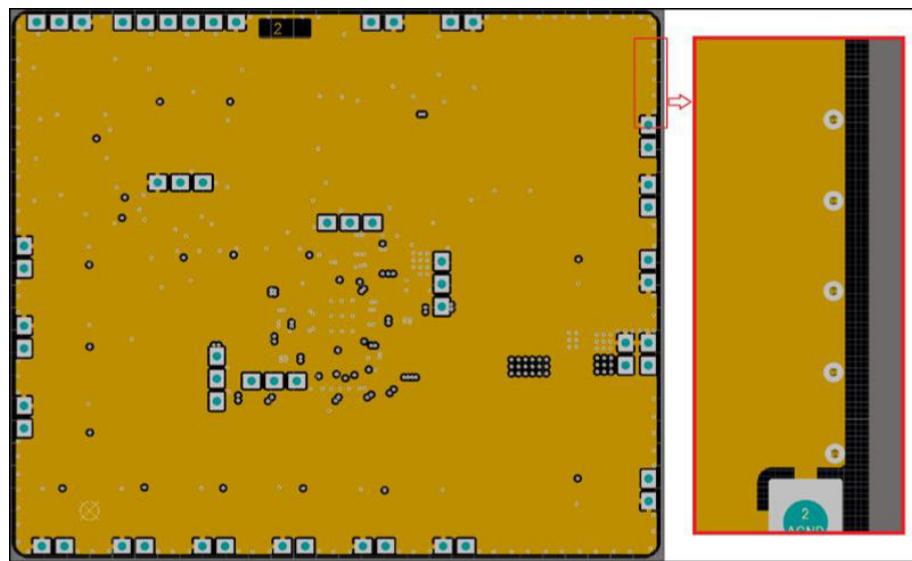

## 4.3 元件放置示例

图 18. 元件放置示例显示的放置方法具有较高的元件密度。本应用笔记中的所有建议在该板件上都已得到满足。将所有元件放在布局的顶部，并且仅在应用/板件尺寸真正需要时才使用底部，这是一个很好的做法。

图 18. 元件放置示例

## 修订历史

表 3. 文档修订历史

| 日期              | 版本 | 变更    |

|-----------------|----|-------|

| 2019 年 12 月 6 日 | 1  | 初始版本。 |

## 目录

|            |                                  |           |

|------------|----------------------------------|-----------|

| <b>1</b>   | <b>电源部分布局注意事项 .....</b>          | <b>2</b>  |

| <b>1.1</b> | <b>一般建议 .....</b>                | <b>2</b>  |

| <b>1.2</b> | <b>降压转换器关键电流路径 .....</b>         | <b>3</b>  |

| <b>1.3</b> | <b>升压转换器关键电流路径 .....</b>         | <b>5</b>  |

| <b>1.4</b> | <b>LDO .....</b>                 | <b>7</b>  |

| <b>2</b>   | <b>热方面的考虑 .....</b>              | <b>8</b>  |

| <b>3</b>   | <b>数字接口布局注意事项 .....</b>          | <b>10</b> |

| <b>4</b>   | <b>PCB 示例: STPMIC1 评估板 .....</b> | <b>11</b> |

| <b>4.1</b> | <b>电源和接地平面 .....</b>             | <b>14</b> |

| <b>4.2</b> | <b>通孔 .....</b>                  | <b>16</b> |

| <b>4.3</b> | <b>元件放置示例 .....</b>              | <b>17</b> |

|            | <b>修订历史 .....</b>                | <b>18</b> |

## 图一覽

|       |                   |    |

|-------|-------------------|----|

| 图 1.  | 降压转换器原理图（充电阶段）    | 3  |

| 图 2.  | 降压转换器原理图（放电阶段）    | 3  |

| 图 3.  | 降压参考路由带关键路径       | 4  |

| 图 4.  | 升压转换器原理图（充电阶段）    | 5  |

| 图 5.  | 升压转换器原理图（放电阶段）    | 5  |

| 图 6.  | 升压参考路由带关键路径       | 6  |

| 图 7.  | LDO 参考路由          | 7  |

| 图 8.  | 裸露焊盘焊接模板          | 8  |

| 图 9.  | 通孔放置建议            | 8  |

| 图 10. | 建议的外形轮廓           | 9  |

| 图 11. | 配备 STPMIC1 器件的评估板 | 11 |

| 图 12. | 顶层（元件/电源/信号）      | 12 |

| 图 13. | 中间层 1（接地）         | 12 |

| 图 14. | 中间层 2（电源/接地）      | 13 |

| 图 15. | 底层（小信号/接地）        | 13 |

| 图 16. | 中间层 1（接地平面）       | 14 |

| 图 17. | 中间层 2 电源/GND      | 15 |

| 图 18. | 元件放置示例            | 17 |

**重要通知 - 仔细阅读**

意法半导体公司及其子公司（“ST”）保留随时对 ST 产品和/或本文档进行变更、更正、增强、修改和改进的权利，恕不另行通知。买方在订货之前应获取关于意法半导体产品的最新信息。ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对意法半导体产品的选择和使用，意法半导体概不承担与应用协助或买方产品设计相关的任何责任。

意法半导体不对任何知识产权进行任何明示或默示的授权或许可。

转售的意法半导体产品如有不同于此处提供的信息的规定，将导致意法半导体针对该产品授予的任何保证失效。

ST 和 ST 标志是意法半导体的商标。关于意法半导体商标的其他信息，访问 [www.st.com/trademarks](http://www.st.com/trademarks)。其他所有产品或服务名称是其各自所有者的财产。

本文档中的信息取代本文档所有早期版本中提供的信息。

© 2023 STMicroelectronics - 保留所有权利