## 引言

STM32MP151、STM32MP153和STM32MP157产品线（在本文档中称为STM32MP15x）基于配备单核或双核且结合Arm® Cortex®-M4的Arm® Cortex®-A7。它们通常由STPMIC1电源管理IC辅助芯片供电，该芯片功能齐全，可提供完整的应用。

该应用笔记描述了一个为带分立调节器的STM32MP15xMPU供电的替代解决方案。仅涵盖支持核心芯片组的应用程序（STM32MP15x + DDR + 闪存）。

本应用笔记适用于需要以下详细信息的硬件产品设计师和架构师：

- 详细原理框图

- 低功耗模式和复位管理（故障恢复）

- 用于为STM32MP15x电源轨供电的稳压器模块（VRM）电气规范。

# 目录

|          |                                              |           |

|----------|----------------------------------------------|-----------|

| <b>1</b> | <b>概述</b>                                    | <b>6</b>  |

| 1.1      | 参考文档                                         | 7         |

| <b>2</b> | <b>词汇表</b>                                   | <b>8</b>  |

| <b>3</b> | <b>分立电源拓扑</b>                                | <b>9</b>  |

| 3.1      | STM32MP15x带有DDR3L和3.3 V I/O电压接口              | 9         |

| 3.1.1    | 输入电压                                         | 11        |

| 3.1.2    | LDO或SMPS的调节器拓扑建议                             | 11        |

| 3.2      | STM32MP15x带有DDR3L和1.8 V I/O电压接口              | 16        |

| 3.2.1    | 输入电压                                         | 17        |

| 3.2.2    | LDO或SMPS的调节器拓扑建议                             | 17        |

| 3.3      | 低功耗模式和故障恢复管理                                 | 19        |

| 3.3.1    | 故障恢复管理电路（可选）                                 | 20        |

| <b>4</b> | <b>上电时序管理</b>                                | <b>21</b> |

| 4.1      | 上电 / 下电时序和复位管理                               | 21        |

| 4.2      | 低功耗模式管理                                      | 24        |

| 4.2.1    | LP-Stop模式                                    | 24        |

| 4.2.2    | 待机模式                                         | 26        |

| 4.3      | 故障恢复管理                                       | 29        |

| <b>5</b> | <b>STM32MP15xD和STM32MP15xF增强型CPU频率供应管理</b>   | <b>31</b> |

| 5.1      | 故障恢复管理和特定系统工作模式                              | 33        |

| 5.2      | 上电 / 下电时序和复位管理                               | 34        |

| 5.3      | 低功耗模式管理                                      | 34        |

| 5.3.1    | LP-Stop模式                                    | 34        |

| 5.3.2    | 待机模式                                         | 35        |

| <b>6</b> | <b>稳压器模块（VRM）规范</b>                          | <b>36</b> |

| 6.1      | VDD（VDD_ANA、VDD_PLL、VDD_DSI）的VRM规范电源域        | 36        |

| 6.2      | VDDCORE电源域的VRM规范                             | 37        |

| 6.2.1    | 面向STM32MP15xD和STM32MP15xF器件的VDDCORE电源域的VRM规范 | 37        |

---

|          |                                              |           |

|----------|----------------------------------------------|-----------|

| 6.3      | VDDQ_DDR电源域VRM规范                             | 38        |

| <b>7</b> | <b>稳压器模块示例</b>                               | <b>40</b> |

| 7.1      | 5 V DC~3.3 V DC - 300 mA应用的VRM示例             | 40        |

| 7.2      | 5 V DC~1.215 V DC - 1500 mA应用的VRM示例          | 40        |

| 7.3      | 5V DC~可扩展1.34 V / 1.2 V DC - 1500 mA应用的VRM示例 | 41        |

| 7.3.1    | Vout (R1、R2、R3、R4) 计算实例                      | 42        |

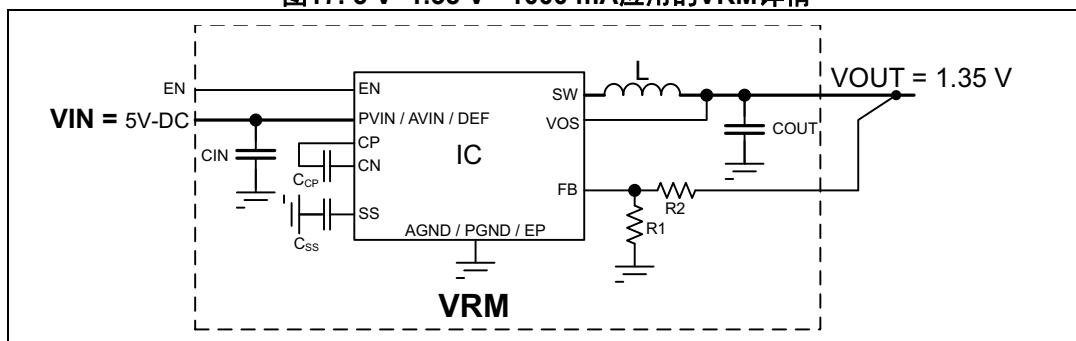

| 7.4      | 5V DC~1.35 V DC - 1000 mA应用的VRM示例            | 42        |

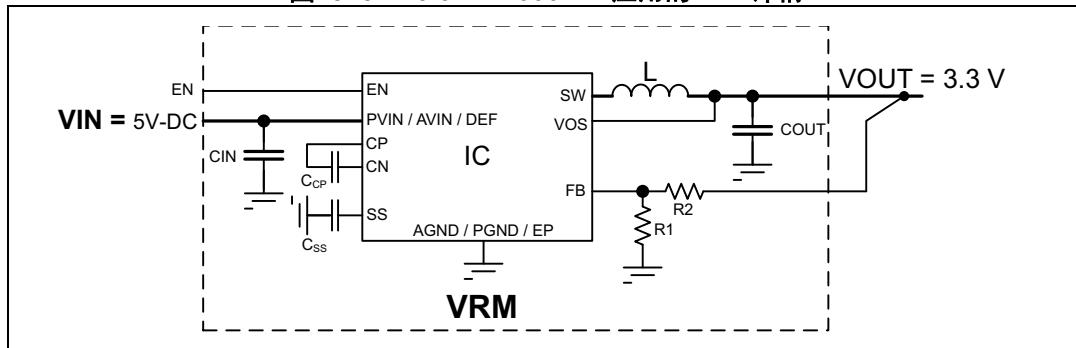

| 7.5      | 5V DC~3.3 V DC - 2000 mA应用的VRM示例             | 44        |

| <b>8</b> | <b>版本历史</b>                                  | <b>45</b> |

## 表格索引

|      |                                          |    |

|------|------------------------------------------|----|

| 表1.  | 参考文档 .....                               | 7  |

| 表2.  | 词汇表 .....                                | 8  |

| 表3.  | 系统工作模式 .....                             | 19 |

| 表4.  | 系统工作模式 .....                             | 33 |

| 表5.  | VDD电源域的VRM规范 .....                       | 36 |

| 表6.  | VDDCORE电源域的VRM规范 .....                   | 37 |

| 表7.  | 通过电压缩放实现800 MHz支持的VDDCORE电源域的VRM规范 ..... | 38 |

| 表8.  | VDDQ_DDR和DDR3L IC电源域的VRM规范 .....         | 38 |

| 表9.  | 5 V~3.3 V - 300 mA应用的VRM示例 .....         | 40 |

| 表10. | 5 V~1.215 V - 1500 mA应用的VRM示例 .....      | 40 |

| 表11. | 1.34V / 1.2 V的VRM真值表 .....               | 42 |

| 表12. | 5 V~1.35 V - 1000 mA应用的VRM示例 .....       | 43 |

| 表13. | 5 V~3.3V - 2000 mA应用的VRM示例 .....         | 44 |

| 表14. | 文档版本历史 .....                             | 45 |

| 表15. | 中文文档版本历史 .....                           | 45 |

## 图片目录

|      |                                                   |    |

|------|---------------------------------------------------|----|

| 图1.  | 分立电源拓扑示例, IO位于3.3 V和DDR3L处 . . . . .              | 10 |

| 图2.  | VDD3V3_USBHS/FS电源配集成电源开关 . . . . .                | 14 |

| 图3.  | VDD3V3_USBHS/FS电源配分立电源开关 . . . . .                | 14 |

| 图4.  | 分立电源拓扑示例, IO位于1.8 V和DDR3L处 . . . . .              | 16 |

| 图5.  | 来自VDD_PERIPH的VDD3V3_USBHS/FS电源 . . . . .          | 18 |

| 图6.  | PWR_ONRST故障恢复管理信号 . . . . .                       | 20 |

| 图7.  | 上电 / 下电时序和复位管理图 . . . . .                         | 21 |

| 图8.  | LP-Stop模式顺序 . . . . .                             | 24 |

| 图9.  | 待机模式顺序 . . . . .                                  | 26 |

| 图10. | 故障恢复顺序 . . . . .                                  | 29 |

| 图11. | 分立电源拓扑示例, IO位于3.3 V, DDR3L和VDDCORE电压缩放 . . . . .  | 32 |

| 图12. | LP-Stop模式顺序 . . . . .                             | 35 |

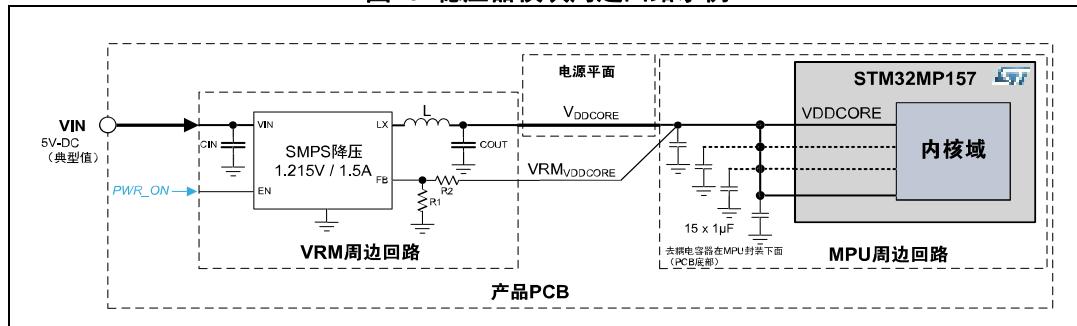

| 图13. | 稳压器模块周边回路示例 . . . . .                             | 36 |

| 图14. | 5 V~3.3 V - 300 mA应用的VRM详情 . . . . .              | 40 |

| 图15. | 5 V~1.215 V/1500 mA应用的VRM详情 . . . . .             | 40 |

| 图16. | 5 V~可扩展1.34 V / 1.2 V - 1500 mA应用的VRM详情 . . . . . | 41 |

| 图17. | 5 V~1.35 V - 1000 mA应用的VRM详情 . . . . .            | 42 |

| 图18. | 5 V~3.3 V - 2000 mA应用的VRM详情 . . . . .             | 44 |

## 1 概述

本应用笔记适用于所有具有较大功能集和严格电源要求的STM32MP15x器件。

本文档主要讲述核心芯片组的供电（STM32MP15x + DDR +闪存），并作如下假设：

- 5 V DC输入电源应用

- DDR3L x32位总线宽度+总线终端电阻

- 通用闪存由3.3 V电源供电。

本文档中提供的稳压器电气规范仅适用于严格遵循STM32MP15x去耦方案（参见AN5031[\[1\]](#)）和布局建议的情况。

本应用笔记中提供的功耗数值只是举例说明，不应用作参考。如需了解关于功耗的信息，请参阅AN5284 [\[7\]](#)和相关产品数据手册。

本应用笔记中提供的STM32MP15x电气和定时数据只是举例说明，不应用作参考。请参阅相关STM32MP15x产品数据手册。

lpDDR2和lpDDR3内存不在该应用笔记的范围内。据推测，它们不由功率分离调节器供电，原因如下：

- lpDDR2/3内存有严格的上电和掉电时序约束（参考JEDEC规范），因为太过复杂，难以通过分立调节器电路实现

- 与使用电源管理IC（如STPMIC1）相比，使用分立调节器进行低功耗管理更复杂（参见DS12505 [\[5\]](#)）。

STM32MP15x产品是基于Arm<sup>®</sup>(a) Cortex<sup>®</sup>的器件。

**arm**

---

a. Arm是Arm Limited（或其子公司）在美国和/或其他地区的注册商标。

## 1.1 参考文档

表1. 参考文档<sup>(1)</sup>

| 参考  | 文档ID    | 标题                             |

|-----|---------|--------------------------------|

| [1] | AN5031  | STM32MP1系列硬件开发入门               |

| [2] | AN5109  | STM32MP1系列使用低功耗模式              |

| [3] | AN5089  | STM32MP1系列和STPMIC1硬件和软件集成      |

| [4] | RM0436  | STM32MP157参考手册 <sup>(2)</sup>  |

| [5] | DS12505 | STM32MP157C数据手册 <sup>(3)</sup> |

| [6] | AN5122  | STM32MP1系列DDR存储器路由指南           |

| [7] | AN5284  | STM32MP1系列系统功耗                 |

| [8] | AN5438  | STM32MP1系列寿命估计                 |

1. 这些文档可从 [www.st.com](http://www.st.com) 获得。

2. 本参考手册仅供参考，但本应用笔记适用于所有STM32MP15x器件。

3. 本数据手册仅供参考，但本应用笔记适用于所有STM32MP15x器件。

## 2 词汇表

表2. 词汇表

| 术语   | 意义                          |

|------|-----------------------------|

| FSBL | 第一阶段启动程序                    |

| HSI  | 高速内部振荡器                     |

| LDO  | 低压降。本文档中的线性稳压器。             |

| MPU  | 微处理器单元。指本文档中的STM32MP15x器件   |

| POR  | 上电复位                        |

| RC   | 离散阻容网络                      |

| RCC  | STM32MP15x复位和时钟控制           |

| RMS  | 均方根                         |

| SMPS | 开关模式电源                      |

| VRM  | 稳压器模块。在本文档中，VRM是降压SMPS或LDO。 |

### 3 分立电源拓扑

#### 3.1 STM32MP15x带有DDR3L和3.3 V I/O电压接口

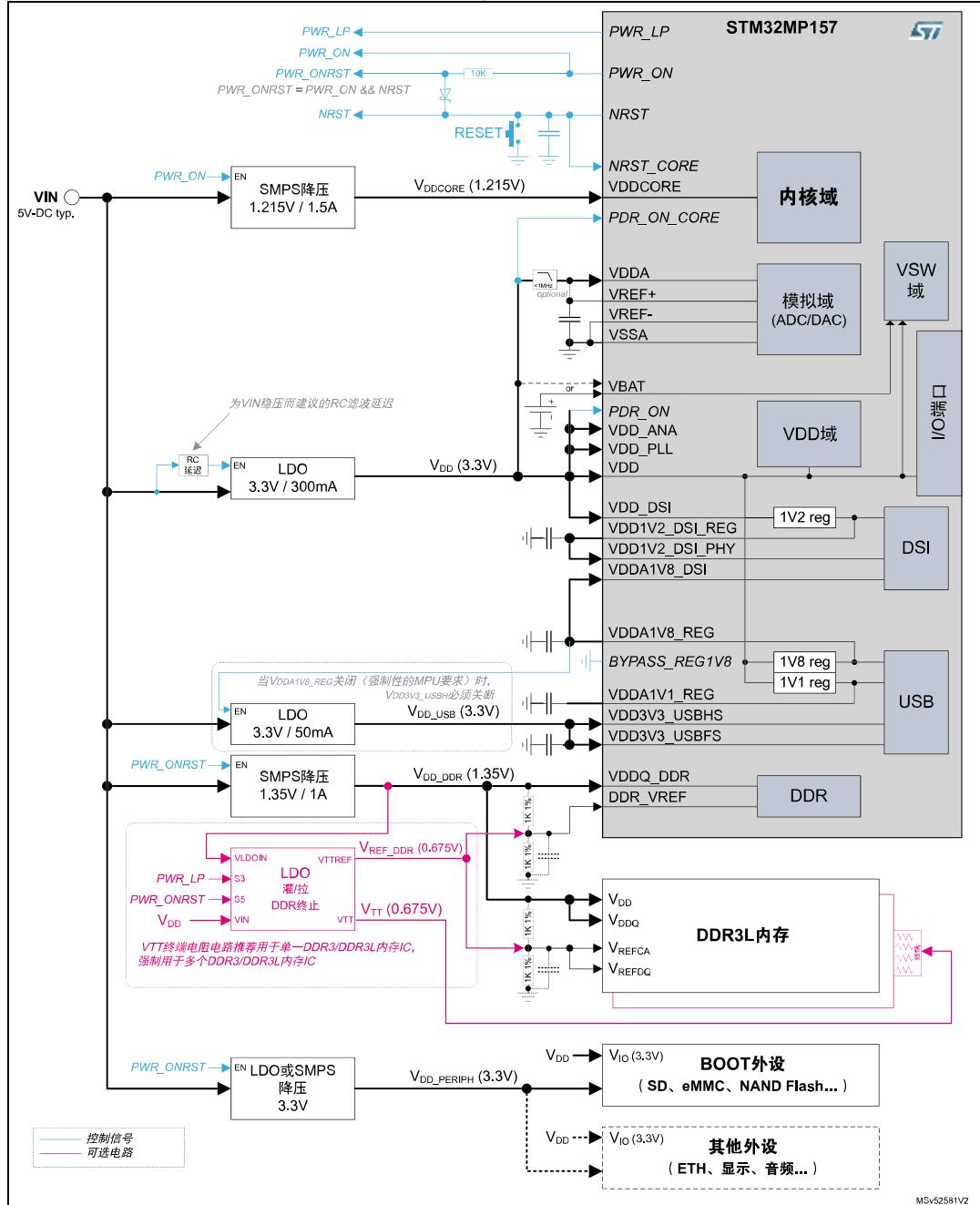

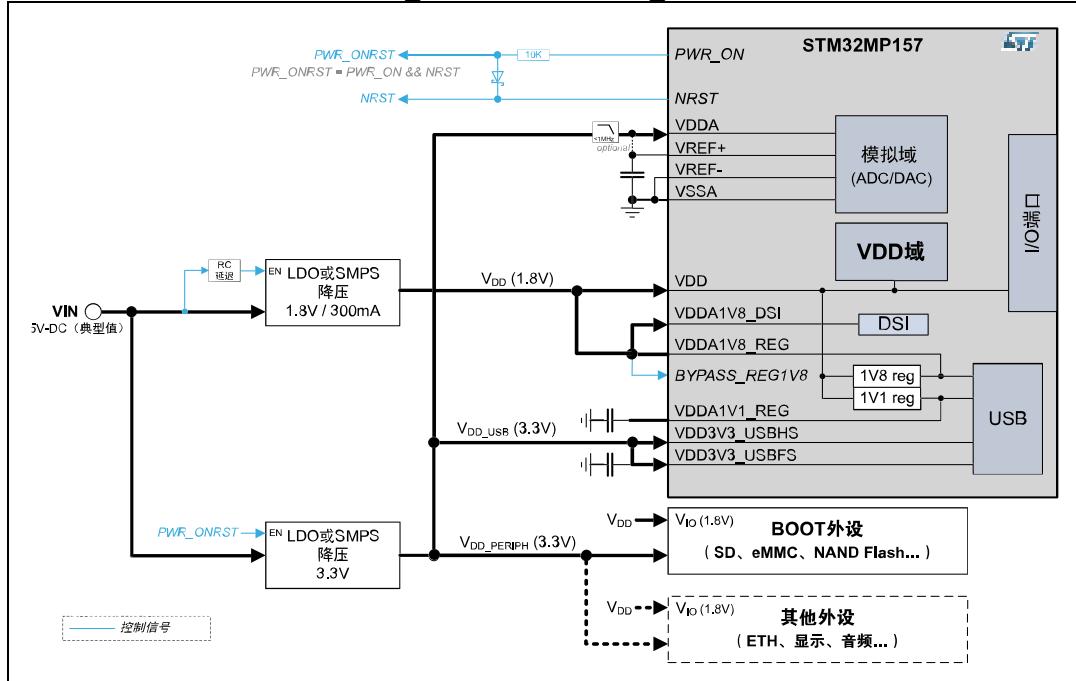

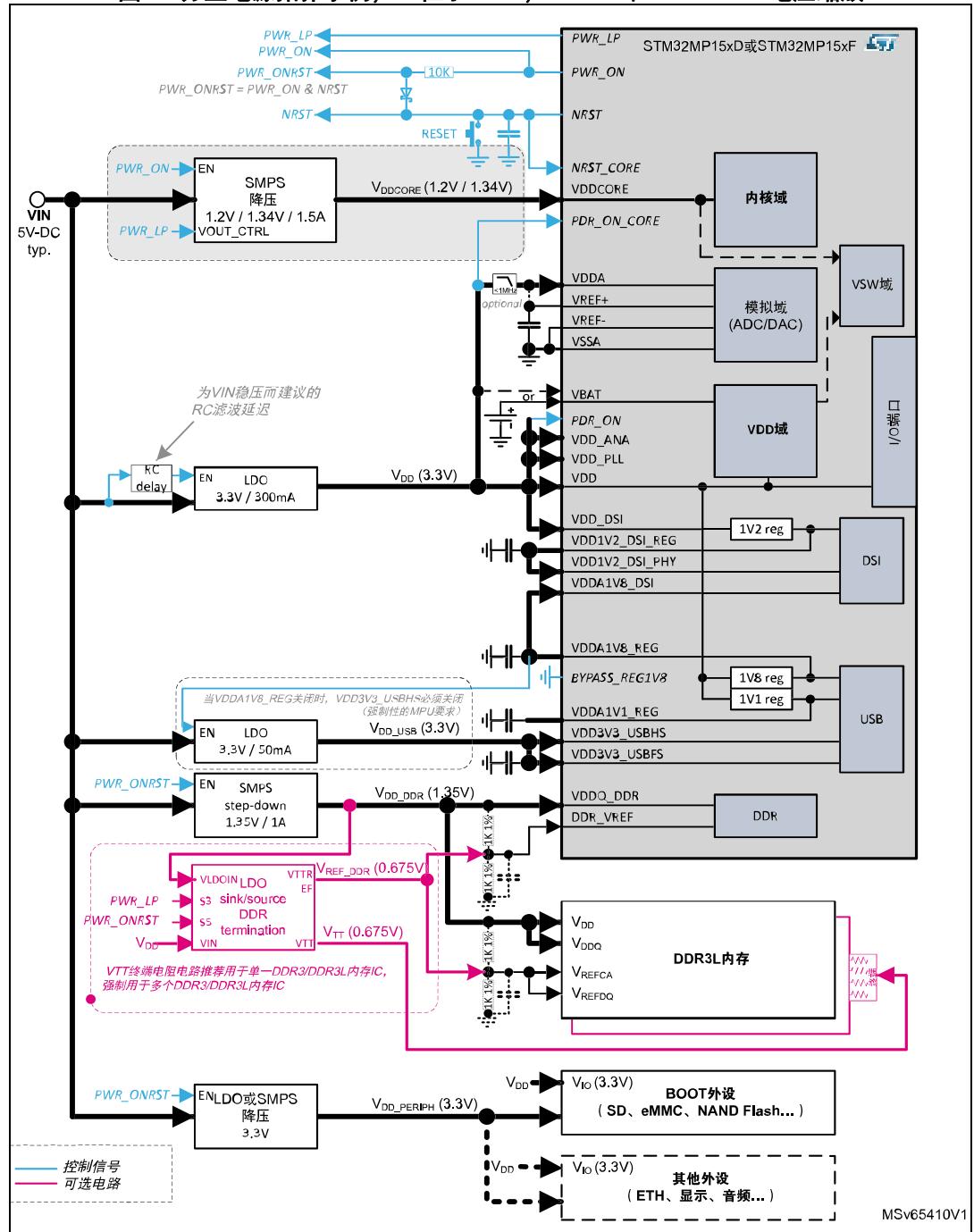

[图 1](#)展示了由STM32MP15x、DDR3L易失性内存和通用闪存（启动外设）组成的基本应用。在该应用中，子系统外设（以太网Phy、RGB LCD、音频等）没有显示，但可以假设其I/O接口工作电压为3.3V（VDD）。该应用由线性和开关电源降压转换器供电。

下面给出了STM32MP157器件的示例。适用于所有STM32MP15x器件。

图1. 分立电源拓扑示例，IO位于3.3 V和DDR3L处

注：

MPU去耦方案没有显示 (参见AN5031 [1])

没有显示SMPS和LDO稳压器产品部件号、以及分立元件，但第 3.1.2 节：LDO或SMPS的调节器拓扑建议详细介绍了其电气规范。

没有显示VIN上的附加保护，如ESD、EMI滤波和过电压。

### 3.1.1 输入电压

该应用示例是由一个5 V（典型）直流电压源（VIN）供电，电压范围为4.0到5.5 V。它只使用以下DC-DC降压转换器：

- 线性稳压器（LDO）

- 非隔离降压SMPS

或者，该应用可以由更高的输入电压（比如12V）供电。在这种情况下，使用与正确输入电压匹配且额定值适当的分立稳压器。对于高于12V的输入电压（典型的工业应用），推荐使用预调节拓扑。例如，使用24 V-5 VDC-DC降压SMPS进行预调节以生成VIN，然后使用该示例中定义的拓扑。建议进行预调节，避免降压SMPS在占空比极低（出现相关问题）的情况下工作。

最小VIN电压应高于应用中使用的最高电压。在该应用中，该应用所需的最高电压是3.3 V（供应 $V_{DD}$ 和 $V_{DD\_PERIPH}$ ）。如果考虑的是理想调节器（无压降）和理想电源，最小VIN可以是3.3 V。在实际情况中，3.3 V稳压器的合理压降为400 mV（在满载情况下工作），再加上VIN路径上的300 mV压降（包括直流和交流压降+裕量），需要的最低VIN电压大约为4 V。

由具有最低最大额定输入电压的VIN供电的调节器限制最高VIN电压。在该应用中，该电压假设为5.5 V。

### 3.1.2 LDO或SMPS的调节器拓扑建议

选择LDO或SMPS调节器拓扑是在简单集成与高效性能之间进行权衡的结果：

- LDO：易于集成、噪音低，但功率效率（热熔性）低

- SMPS：功率效率高（热熔性比LDO低）；集成难度高，噪声比LDO（开关动作）高。

对于由直流电源供电的应用（通常是由AC-DC墙上适配器供电），功率效率没有电池应用那么重要。然而，热熔性仍然是一个重要标准，应尽可能减少。尤其当应用程序运行最耗电的用例时，或者当其使用12V（而不是5V）VIN电源时。

相反，处于待机模式的应用程序应具备低静止电流，以使稳压器保持‘打开’，还应具备低泄漏电流，以使稳压器‘关闭’。

应相应地选择稳压器拓扑。

### VDD电源域

对于VDD电源域，LDO拓扑是在权衡功率损失、电压噪声、以及成本之后的最佳选择：

- VDD / VIN电压比是0.66（3.3 V / 5 V）。LDO功率效率约为66%，准常数。

- 平均电流消耗很低，即使复杂的用例也是如此。它通常低于最坏情况下的平均电流100 mA（假定50mA），从来没有超过200mA（假设在非常坏的情况下峰值为300mA，留有一些余量）。

- 停止和待机模式下的电流消耗非常低，分别约为1 mA和10  $\mu$ A（参见DS12505 [5]了解有关详情及条件）

在LDO拓扑中，功率效率为：大约66%（约等于VDD / VIN比率）；使用SMPS降压转换器时，约为90%。采用LDO时的功率损耗为85 mW，采用SMPS转换器时的功率损耗为18 mW（假设电流消耗为50mA）。对于这两种情况，相比其他应用电源域，热熔性可以忽略不计。

在停止模式下，LDO和降压SMPS的功率损耗是相等的，因为在轻负载情况下，普通降压转换器的功率效率会降低。

在待机模式下，SMPS的功率损耗要比LDO高。SMPS的静态电流通常比LDO高，而且LDO没有开关损耗。

### VDDA和VREF电源域

VDDA引脚为ADQDAC和参考电压缓冲器（VREFBUF）供电，以便为ADQDAC生成 $V_{REF+}$ 参考电压。

ADC和DAC的性能不仅受 $V_{REF+}$ 电源噪声电平的直接影响，还受到VDDA电源噪声电平的影响（由于VDDA电源抑制比）。

如果VDDA由VDD电源供电，根据需要的ADC/DAC性能，可以在VDD电源和VDDA之间插入一个带低直流阻抗的低通滤波器。

如果期望有限的ADC / DAC性能， $V_{REF+}$ 应仅连接到VDD电源。

### VDDCORE电源域

对于VDDCORE电源域，为了功率效率，建议使用降压SMPS拓扑，因为这是应用中电流消耗最高的域之一。

对于VDDCORE，由于VDDCORE和VIN之间的比率约为0.24(1.215V/5V)，所以不建议使用LDO拓扑。对于LDO，功率效率可以低至24%，这意味着LDO转换器消耗的能量远远大于MPU本身消耗的能量。

### **VDD\_DDR和VTT电源域**

对于V<sub>DD\_DDR</sub>电源域，建议使用降压SMPS拓扑，原因与VDDCORE相同。

如果应用需要终端电阻在DDR3 / DDR3L地址/命令总线上，应有一个专用的灌/拉 LDO为VTT供电，电压为V<sub>DD\_DDR</sub>/2。这样的稳压器通常集成一个VREF\_DDR转换器，允许从设计中删除电阻分压器（1 kΩ / 1 kΩ）。

### **VDD\_USB电源域**

VDD3V3\_USBHS和VDD3V3\_USBFS是MPU的USB PHY电源引脚。它们应由3.07 V-3.6 V的电压供电。VDD3V3\_USBHS和VDD3V3\_USBFS的电流消耗都小于30 mA（为了允许一定余量，假设为50 mA）。

当VDDA1V8\_REG不存在时，VDD3V3\_USBHS不得存在，不然会使MPU永久损坏（参见DS12505[5]获取详细信息）。VDD3V3\_USBHS不能直接连接到VDD，因为VDD总是出现在VDDA1V8\_REG之前。

为了适应该约束，应由VDDA1V8\_REG启用VDD3V3\_USBHS。VDD\_USB是在启用VDDA1V8\_REG时启用的，因此默认情况下，其在上电时、以及使用DSI或USB时启用。可以有不同的电源选项：

- 专用LDO（推荐），参见图 1

- 集成式电源开关 / 负载开关，参见图 2

- 分立电源开关，参见图 3。

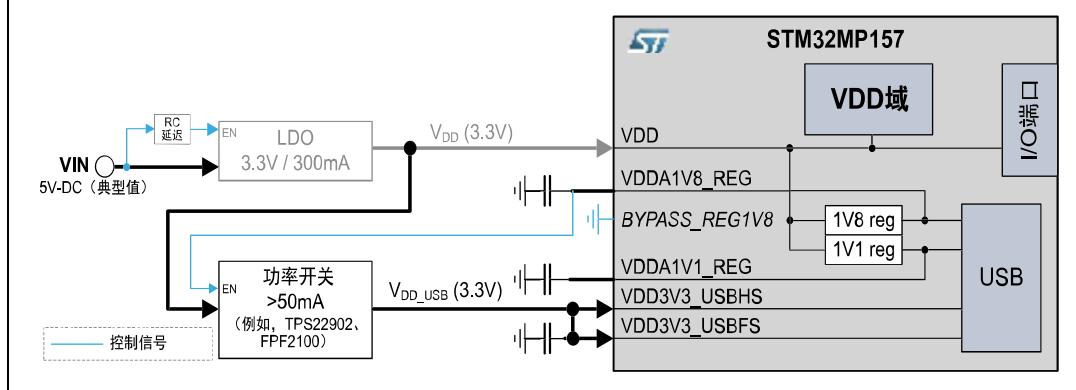

下面给出了STM32MP157器件的示例。适用于所有STM32MP15x器件。

图2. VDD3V3\_USBHS/FS电源配集成电源开关

电源开关（负载开关）的主要电气标准有：

- 导通电阻应足够低，以确保VDD\_USB永远不会低于3.07V。如果VDD有+/-5%的容差，通常低于700 mΩ：

$$R_{on} < ((3.3 \text{ V} - 5\%) - 3.07 \text{ V}) / 50 \text{ mA} = 0.7 \text{ Ω}.$$

- EN\_VIH最小阈值（高电平激活）应低于1.7V（最小VDDA1V8\_REG），以确保电源开关在任何情况下都能接通。

- 当电源开关被禁用时，建议使用集成输出放电电阻器为VDD\_USB去耦电容器放电。

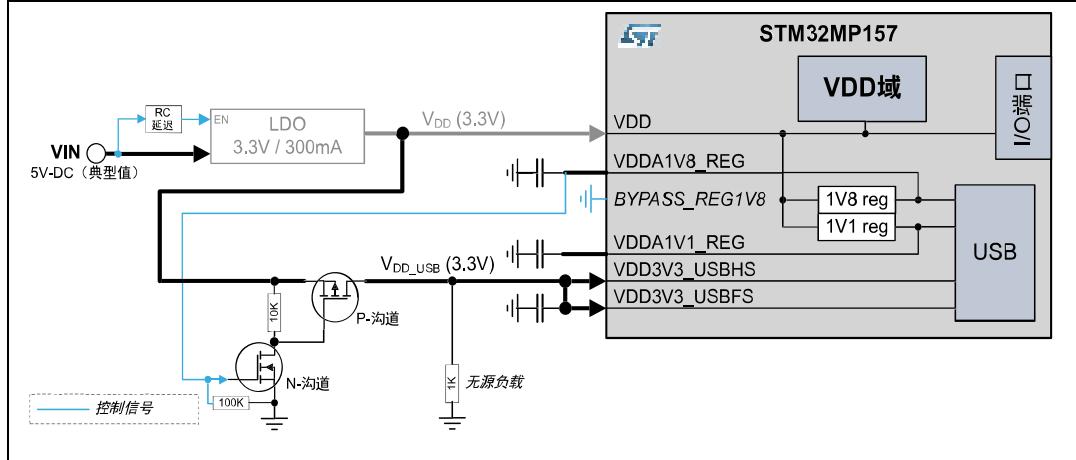

下面给出了STM32MP157器件的示例。适用于所有STM32MP15x器件。

图3. VDD3V3\_USBHS/FS电源配分立电源开关

该分立电源开关由一个P-沟道功率MOSFET和一个N-沟道MOSFET组成。P-沟道MOSFET作为电源开关，将电流从VDD吸取到VDD\_USB，提供给VDD3V3\_USBHS/FS。P-沟道栅极由N-沟道MOSFET驱动，它作为漏极开路用于反转P-沟道的极性。N-沟道栅极由VDDA1V8\_REG电压驱动。增加了1 kΩ无源负载为VDD3V3\_USBHS/FS上的去耦电容器放电，在启用VDD\_USB后，持续消耗3.3 mA电流。

分立电源开关主要电气特性：

- P沟道MOSFET：

- $V_{DSS}$ 和 $V_{GSS} > -3.3$  V

- $I_D$ 最小: -50 mA

- $I_D$ 峰值  $>> -50$  mA (为VDD3V3\_USBHS/FS去耦电容器充电时的峰值电流)

- $V_{GS} = -3.3$  V时,  $R_{DS}$  (导通)  $< 0.7$   $\Omega$

- N沟道MOSFET：

- $V_{DSS} > 3.3$  V

- $V_{GSS} > 1.8$  V

- $I_D$ 最小: 10 mA

- $V_{GS} = 1.8$  V时,  $R_{DS}$  (导通)  $< 100$   $\Omega$

#### **VDD\_PERIPH电源域**

对于VDD\_PERIPH功率域, 电压和稳压器拓扑取决于最终应用。在图 1中所示的应用中, 假设所有外设都可以由3.3 V电压源供电。

### 3.2 STM32MP15x带有DDR3L和1.8 V I/O电压接口

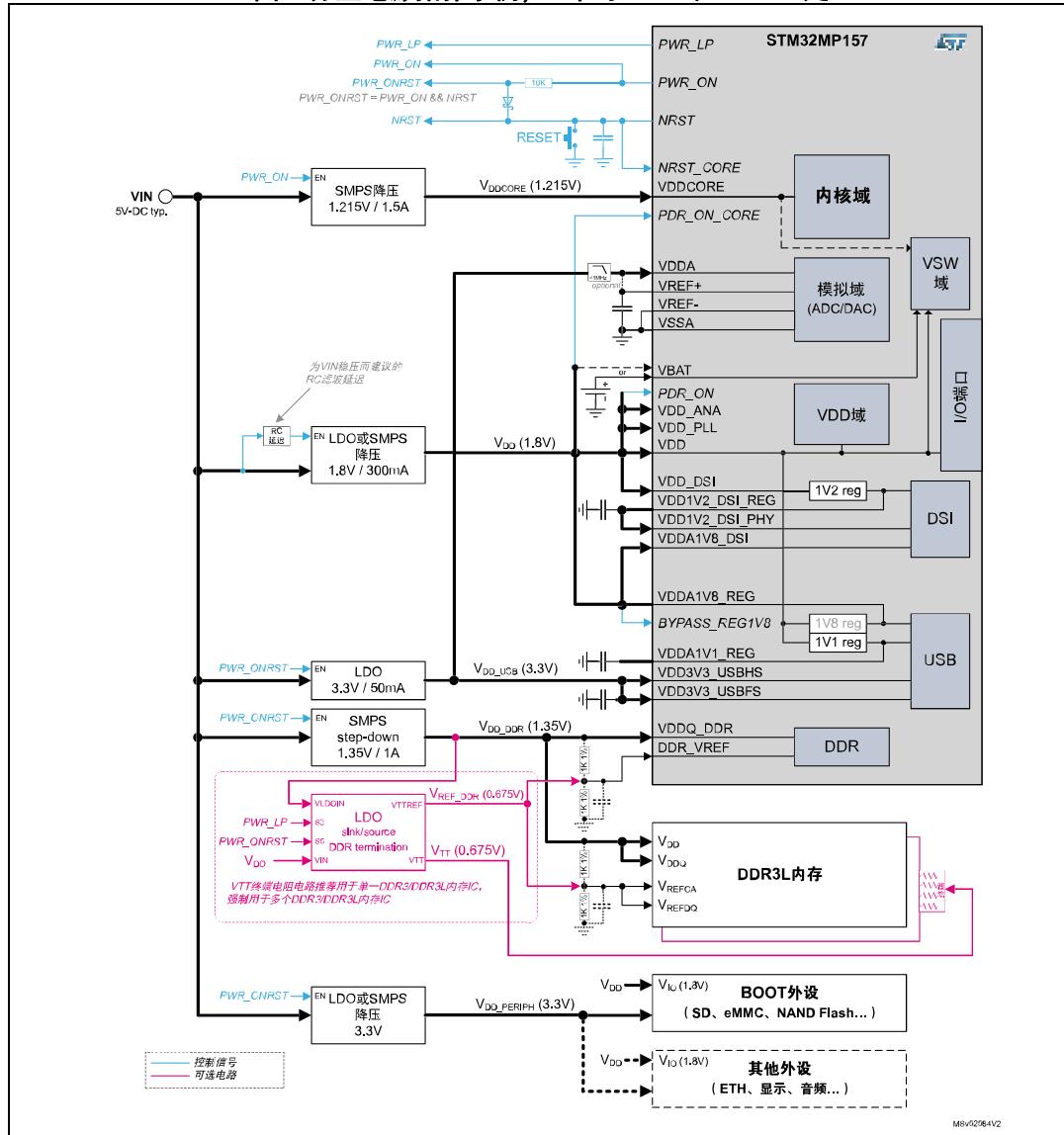

图4显示的应用与图1相同，除了I/O接口电压从3.3 V变为1.8 V。没有显示子系统外设（以太网、LCD、音频等），但可假设其I/O接口的工作电压为1.8 V ( $V_{DD}$ )，或使用电平转换器。该应用由线性和开关电源降压转换器供电。

下面给出了STM32MP157器件的示例。适用于所有STM32MP15x器件。

图4. 分立电源拓扑示例，IO位于1.8 V和DDR3L处

注:

MPU去耦方案没有显示 (参见AN5031 [1])

没有显示SMPS和LDO稳压器产品部件号、以及分立元件，但第 3.2.2 节：LDO或SMPS的调节器拓扑建议详细介绍了其电气规范。

没有显示VIN上的附加保护，如ESD、EMI滤波和过电压。

### 3.2.1 输入电压

请参见[第 3.1.1 节：输入电压](#)。

### 3.2.2 LDO或SMPS的调节器拓扑建议

本节类似于[第 3.1.2 节：LDO或SMPS的调节器拓扑建议](#)，不同之处在于：

#### VDD电源域

对于VDD电源域，为了功率效率，建议使用降压SMPS拓扑。然而，因为该电源域上的低电流消耗，LDO拓扑也可以接受。

- VDD / VIN电压比是0.36（1.8 V / 5 V）。LDO功率效率约为36%，准常数。

- 平均电流消耗很低，即使复杂的用例也是如此。最坏情况下，平均电流通常低于100 mA（假定50 mA），从来没有超过200 mA（非常坏的情况下峰值为300 mA，留有一些余量）。

- 停止和待机模式下的电流消耗非常低，分别约为1mA和10 $\mu$ A（参见DS12505了解有关详情及条件）

采用LDO拓扑时，功率效率约为36%（约等于VDD / VIN比率）；使用SMPS降压转换器时，约为90%。采用LDO时的功率损耗为160 mW，采用SMPS转换器时的功率损耗为18 mW（假设电流消耗为50 mA）。如果60mw的损耗可以接受，那么就可以使用LDO，具体取决于应用的散热能力。

#### VDD\_USB电源域

VDD3V3\_USBHS和VDD3V3\_USBFS是MPU的USB PHY电源引脚。它们应由3.07 V-3.6 V的电压供电。VDD3V3\_USBHS和VDD3V3\_USBFS的电流消耗都小于30 mA（为了允许一定余量，假定为50 mA）。

当VDDA1V8\_REG不存在时，VDD3V3\_USBHS不得存在，不然会使MPU永久损坏（参见DS12505 [\[5\]](#)）。

为了适应这些约束，VDD3V3\_USBHS应与PWR\_ON或PWR\_ONRST信号同步，因为VDD连接到VDDA1V8\_REG，并在应用中首先上升（参见[图 4](#)）。有两个电源选项：

- 专用LDO（推荐），参见[图 4](#)

- 重用为外设供电（V<sub>DD\_PERIPH</sub>）的稳压器，参见[图 5](#)。

下面给出了STM32MP157器件的示例。适用于所有STM32MP15x器件。

图5. 来自VDD\_PERIPH的VDD3V3\_USBHS/FS电源

$V_{DD\_PERIPH}$ 电源可用于为VDD3V3\_USBHS和VDD3V3\_USBLS供电，但需满足以下条件：

- $V_{DD\_PERIPH}$  电压应在 VDD3V3\_USBHS/LS 电压公差 (3.07 V 至 3.6 V) 范围内

- 除非 VDD (VDDA1V8\_REG) 存在, 否则  $V_{DD\_PERIPH}$  (VDD3V3\_USBHS) 不得存在。

如果  $V_{DD\_PERIPH}$  稳压器具有相同的电压并且通过 PWR\_ONRST 进行控制（如图 5 中所示），则满足两个约束条件。

### VDDA和VREF电源域

VDDA引脚为ADC / DAC和参考电压缓冲器（VREFBUF）供电，以生成ADC/DAC  $V_{REF+}$  参考电压。

ADC和DAC的性能不仅受V<sub>REF+</sub>电源噪声电平的直接影响，还受到VDDA电源噪声电平的影响（由于VDDA电源抑制比）。

如果应用中使用的ADC/DAC的参考电压 $V_{REF+}$ 高于 2 V，则可以使用 $V_{DD\_PERIPH}$ 电源为VDDA供电。根据需要的ADC/DAC性能，可以在VDD电源和VDDA之间插入一个带低直流阻抗的低通滤波器。

如果能够接受有限的ADC / DAC性能, VREF+可以连接到V<sub>DD\_P</sub>ERIPH电源。

### 3.3 低功耗模式和故障恢复管理

STM32MP15x器件支持多种工作模式以降低功耗（参见AN5109：“STM32MP1系列使用低功耗模式”获取详细信息）。

两个MPU输出引脚PWR\_ON和PWR\_LP可根据工作模式自动控制。它们用于控制应用稳压器：

- **PWR\_ON**: 电源请求信号（高电平激活）。启用VDDCORE和应用外设电源。它在运行、停止、以及Low-Power-Stop模式下是活跃的。它在待机模式下不活跃（当VDD不存在时，在VBAT和关机模式下为隐式）。

- **PWR\_LP**: 低功耗模式请求信号（低电平激活）。用于请求稳压器或外设进入低功耗状态。在LP\_Stop和待机模式下，它是活跃的。它在运行和停止模式下不活跃。

**注：**有了分立稳压器应用，LPCFG（PWR\_CR1寄存器中的PWR\_ON引脚配置）应始终设置为0。

[表 3](#)总结了[图 1](#)中阐述的应用工作模式的供电状态。

**表3. 系统工作模式**

| 电源模式               | NRST / NRST_CORE | VDD      | PWR_ON / VDDCORE | PWR_ONRST / VDD_DDR VDD_PERIPH | PWR_LP / VTT |

|--------------------|------------------|----------|------------------|--------------------------------|--------------|

| 运行                 | 1                | 启动       | 1 / 启动           | 1 / 启动                         | 1 / 启动       |

| 停止                 | 1                | 启动       | 1 / 启动           | 1 / 启动                         | 1 / 启动       |

| LP-Stop            | 1                | 启动       | 1 / 启动           | 1 / 启动                         | 0 / 关闭       |

| 待机                 | 1                | 启动       | 0 / 关闭           | 0 / 关闭                         | 0 / 关闭       |

| VBAT或断电            | -                | 关闭（无VIN） | 关闭（无VIN）         | 关闭（无VIN）                       | 关闭（无VIN）     |

| 崩溃<br>(watchdog超时) | 0<br>(脉冲)        | 启动       | 1 / 启动           | 0 / 关闭                         | 1 / VTT关闭    |

### 3.3.1 故障恢复管理电路（可选）

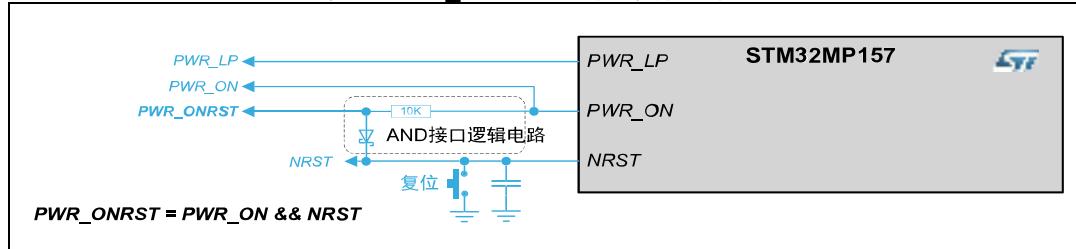

PWR\_ONRST是专门用于管理应用级崩溃恢复的附加信号。如图6中所示，PWR\_ONRST信号由PWR\_ON和NRST通过离散逻辑AND电路生成。

下面给出了STM32MP157器件的示例。适用于所有STM32MP15x器件。

图6. PWR\_ONRST故障恢复管理信号

AND逻辑电路由一个10 kΩ电阻和一个二极管组成。建议使用肖特基二极管，如BAT54或BAT60。10 kΩ电阻的阻值可以根据稳压器使能（EN）引脚的综合阻抗进行调整；如在部分或所有稳压器使能（EN）引脚内置有下拉电阻器的情况下，尤其如此。

PWR\_ONRST信号相当于PWR\_ON信号。然而，如果发生复位（NRST信号低脉冲），PWR\_ONRST信号变成低电平，这意味着由该信号控制的稳压器在NRST低脉冲持续时间内关闭，然后复位释放到高电平状态后再打开。

这使得电源循环可以在外设上进行。建议在应用复位（NRST）发生后确保外设的正确重启和复位，特别是对于没有复位输入信号的外设。对于eMMC、NAND、NOR和SD-Card等外设启动器件/闪存，特别建议进行电源循环。

STM32MP15x器件具有双向焊盘复位（NRST），允许复位外部器件。如果发生崩溃（iwdg1\_out\_rst或iwdg2\_out\_rst watchdog超时），NRST信号上会产生一个复位脉冲。PWR\_ONRST信号上会产生一个相同的脉冲来控制外设电源的电源循环。[第4节：上电时序管理](#)中提供了一个时序图示例。

**注：**MPU的RPCTL（复位脉冲控制）允许控制NRST引脚的最小脉冲持续时间。启动时应由软件启用，并设置适当的持续时间；例如，通过在RCC\_RDLSICR寄存器中设置位字段MRD[4:0]=0x1F，将脉冲持续时间设为31 ms。

这就确保分立稳压器输出电压有足够的时间在脉冲结束（过渡到‘1’）之前下降，并重新启用稳压器。

## 4 上电时序管理

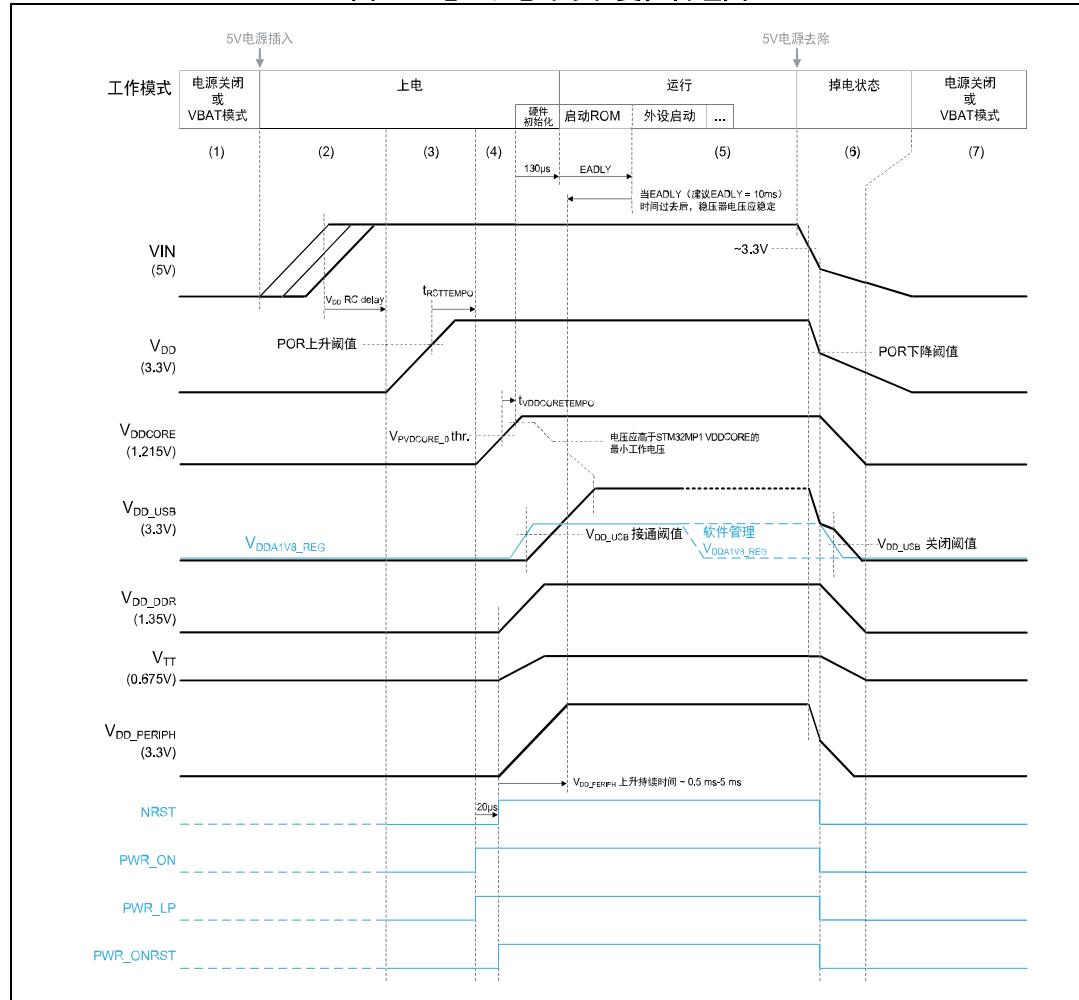

在图 7 到图 10 中, 与管理有关的  $V_{DDA1V8\_REG}$  电平和信号波形以浅蓝色显示, 从而提高清晰度。

### 4.1 上电 / 下电时序和复位管理

图 7 中显示应用上电和下电时序, 详情请参见图 1: 分立电源拓扑示例, IO 位于 3.3 V 和 DDR3L 处中所示的实现步骤。

图7. 上电 / 下电时序和复位管理图

1. 应用没有上电, 或者MPU处于VBAT模式 (由VBAT向VSW电源域供电)。

2. 一个有效的电源连接到该应用。VIN电压上升。经历一段时延 (由无源R-C网络定义), 以允许VIN电压稳定, VDD稳压器已启用。

3.  $V_{DD}$ 电压开始上升:

- a) MPU将NRST、PWR\_ON、PWR\_LP信号设为低电平, 使PWR\_ONRST信号变为低电平。

- b) 一旦 $V_{DD}$ 电源电压高于POR上升阈值水平<sup>(a)</sup>, 将开始 $t_{RSTTEMPO}$ <sup>(b)</sup>时延。

4.  $t_{RSTTEMPO}$ 时延过后, MPU将PWR\_ON和PWR\_LP信号设为高电平:

- a)  $t_{RSTTEMPO}$ 时延过后, MPU先等待20  $\mu$ s<sup>(c)</sup>, 然后释放NRST信号, 使PWR\_ONRST变为高电平。 $V_{DD\_PERIPH}$ 、 $V_{DD\_DDR}$ 和 $V_{TT}$ 由PWR\_ONRST信号启用,  $V_{DD\_PERIPH}$ 、 $V_{DD\_DDR}$ 和 $V_{TT}$ 电压开始上升。

- b)  $V_{DDCORE}$ 稳压器由PWR\_ON信号启用,  $V_{DDCORE}$ 电压开始上升。

- c) 一旦 $V_{DDCORE}$ 电压高于 $V_{PVDCORE\_0}$ <sup>(d)</sup>上升阈值水平, 将开始 $t_{VDDCORETEMPO}$ <sup>(e)</sup>时延。只要时延 $t_{VDDCORETEMPO}$ 没有过去, MPU保持内部复位状态。

5. 时延 $t_{VDDCORETEMPO}$ 过后, MPU退出内部复位状态 ( $V_{DDCORE\_OK}$ ):

- a)  $V_{DDCORE}$ 电压应高于 $V_{DDCORE}$ <sup>(f)</sup>最小工作电压。这应由 $V_{DDCORE}$ 稳压器电压转换率来保证。

- b)  $V_{DDA1V8\_REG}$ 内部稳压器已启用。如果 $V_{DDA1V8\_REG}$ 电压达到 $V_{DD\_USB}$ 稳压器启用阈值,  $V_{DD\_USB}$ 稳压器将启用。

- c) MPU执行内部硬件初始化 (允许在约130  $\mu$ s的时间内加载HSI和选项字节)。然后进入运行模式。EADLY<sup>(g)</sup>延时定时器 (10 ms) 将启动。

-

- a. POR上升阈值 =  $V_{BOR0}$ 上升沿 = 1.67 V (典型值)

- b.  $t_{RSTTEMPO}$  = 377  $\mu$ s (典型值)

- c. MPU的内部RCC时延。

- d.  $V_{PVDCORE\_0}$ 上升沿 = 最低0.95 V

- e.  $t_{VDDCORETEMPO}$  = 最低200  $\mu$ s

- f.  $V_{DDCORE}$ 工作电压 = 最低1.18 V

- g. 当从待机模式恢复时, EADLY定时器防止Boot ROM在准备就绪之前对启动外设执行任何访问。通常, 它等待闪存上的稳定电压 (由Boot ROM读取) 来获取启动软件。在该应用中, 保持默认值 (10 ms), 以等待 $V_{DD\_PERIPH}$ 和 $V_{DD\_USB}$ 电压稳定下来 (参见RM0436 [\[4\]](#) 获取更多详细信息)。

- d) 当EADLY时间过后, Boot ROM开始访问外部外设, 以加载和执行启动软件。默认情况下, 当EADLY时间过后, 所有稳压器电压都应稳定; 特别是 $V_{DD\_PERIPH}$ 和 $V_{DD\_USB}$ , 它们分别是为闪存和USB接口供电的电源域。

- e) 在应用初始化之后, 如果没有附加USB外设, 软件将禁用 $V_{DDA1V8\_REG}$  ( $V_{DD\_USB}$ )。

6. 从应用移除电源:

- a) VIN电压下降

- b) 当VIN电压接近 $V_{DD}$ 、 $V_{DD\_USB}$ 和 $V_{DD\_PERIPH}$  (3.3 V) 时, 它们开始和VIN并行下降。

- c) 一旦 $V_{DD}$ 电源电压低于POR下降阈值<sup>(a)</sup>, MPU内部复位并禁用 $V_{DDA1V8\_REG}$ 。MPU将NRST、PWR\_ON和PWR\_LP信号设为低电平。PWR\_ONRST信号被NRST和PWR\_ON信号强制变为低电平。 $V_{DDCORE}$ 、 $V_{DD\_DDR}$ 、 $V_{TT}$ 、 $V_{DD\_PERIPH}$ 稳压器被禁用。VIN上的电流消耗降低, 使VIN缓慢下降。如果 $V_{DDA1V8\_REG}$ 达到 $V_{DD\_USB}$ 稳压器禁用阈值,  $V_{DD\_USB}$ 稳压器将禁用。

7. 应用没有上电, 或者MPU处于VBAT模式 (由VBAT向 $V_{SW}$ 电源域供电)。

---

a. POR下降阈值 =  $V_{BOR0}$ 下降沿 = 1.63 V典型值 (或 =  $V_{BOR3}$ 下降沿 = 2.6 V最大, 如果选项字节SELINBORH[0:1] = 11 (BOR = 2.7 V) )。

## 4.2 低功耗模式管理

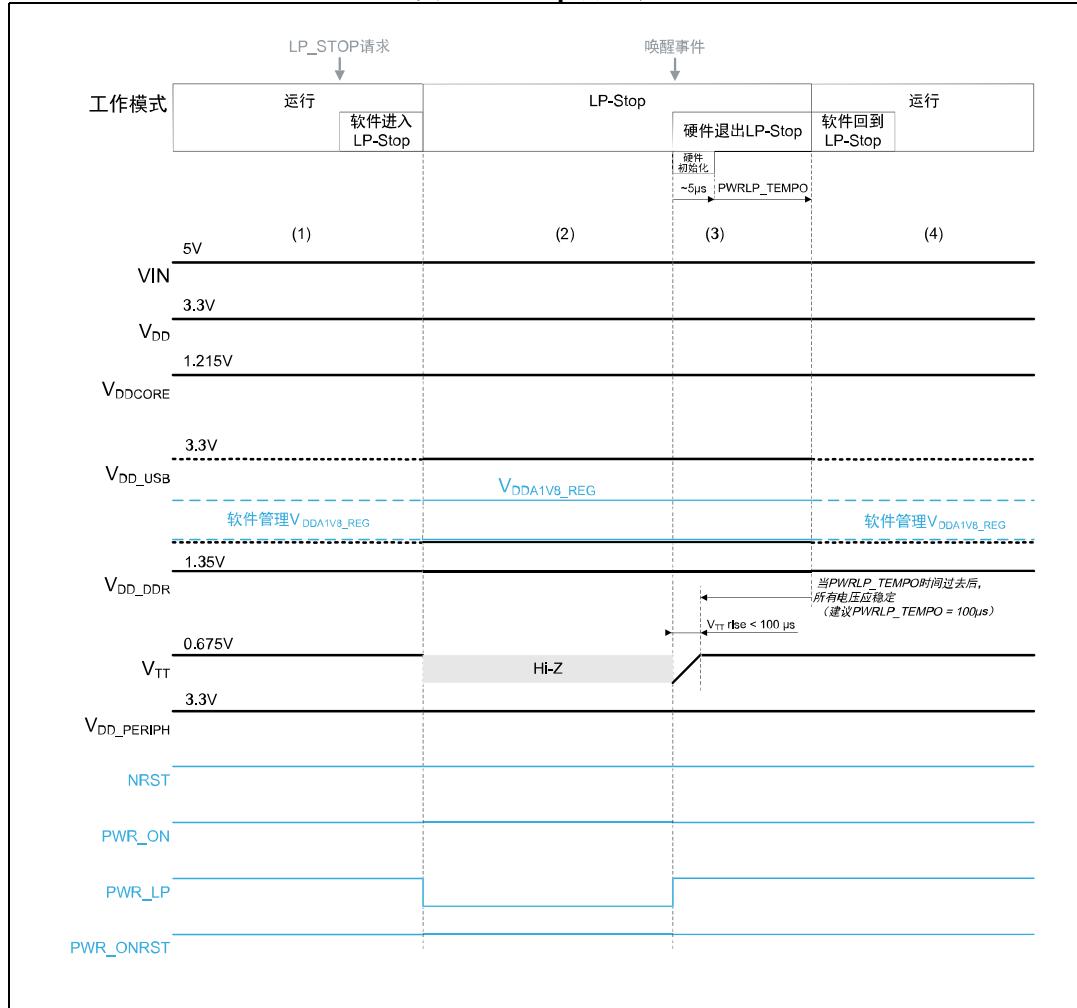

### 4.2.1 LP-Stop模式

图 8: LP-Stop模式顺序中显示应用LP-Stop模式顺序, 详情请参见图 1: 分立电源拓扑示例, IO位于3.3 V和DDR3L处中的实现步骤。在该应用中,  $V_{TT}$ 是支持低功耗模式的唯一稳压器。

图8. LP-Stop模式顺序

1. 应用已上电并运行。当请求LP\_Stop模式时，软件准备进入LP\_Stop模式（停止一些时钟，将DDR设为自刷新，设置PWRLP\_TEMPO）。然后设置LPDS寄存器以进入LP-Stop模式：使PWR\_LP信号有效。

2.  $V_{TT}$ 进入低功耗模式（高阻抗）。

3. 遇到唤醒事件时，MPU退出LP-Stop模式，并使PWR\_LP信号无效：

- a)  $V_{TT}$ 退出低功耗模式

- b) 执行时钟恢复过程

- c) HSI时钟振荡器稳定（大约需要5  $\mu$ s）之后，PWRLP\_TEMPO<sup>(a)</sup>定时器超时，等待 $V_{TT}$ 稳压器电压稳定。在本应用中， $V_{TT}$ 稳压器恢复时间小于100  $\mu$ s。因此，PWRLP\_TEMPO持续时间至少应为100  $\mu$ s。

4. 当PWRLP\_TEMPO延时过后，应用进入运行模式。软件从LP-Stop模式恢复（恢复时钟，从自刷新恢复DDR）。根据USB动作，软件可以打开或关闭VDDA1V8\_REG（MPU的内部稳压器），这将自动打开或关闭 $V_{DD\_USB}$ 稳压器。

---

a. PWRLP\_TEMPO是专用定时器，设计目的是在应用从LP-Stop模式变为运行模式时，等待稳压器恢复。PWRLP\_TEMPO延时值必须在RCC\_PWR LPDLYCR寄存器的PWRLP\_DLY[21:16]位字段中设置。

## 4.2.2 待机模式

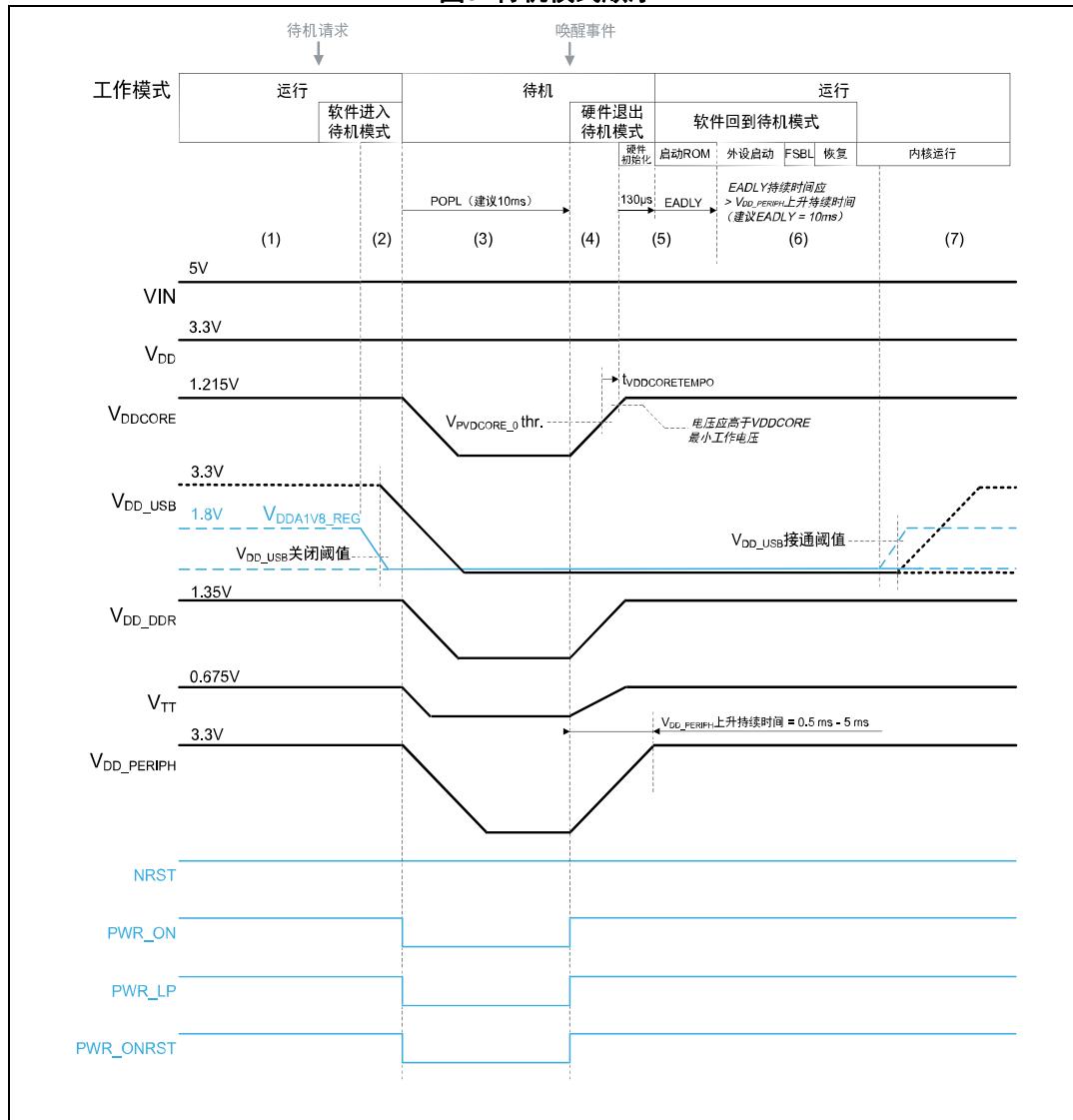

图 9 中显示应用待机模式顺序，详情请参见图 1：分立电源拓扑示例，IO 位于 3.3 V 和 DDR3L 处中的实现步骤。

在该应用中，被 Boot ROM 用于读取启动软件（例如，FSBL）的闪存由  $V_{DD\_PERIPH}$  电源域供电，而 DDR 内存在待机模式下被关闭。

图9. 待机模式顺序

1. 应用已上电并运行。当请求待机模式时，软件准备进入待机模式（停止一些时钟，设置POPL<sup>(a)</sup>和EADLY<sup>(b)</sup>定时器等）。

2. 该软件可能关闭USB电源域，方法是关闭V<sub>DDA1V8\_REG</sub>，使V<sub>DD\_USB</sub>稳压器关闭<sup>(c)</sup>。软件就绪后，MPU进入待机模式，POPL定时器自动启动。

3. PWR\_ON信号被判为无效，而PWR\_LP信号被判为有效：

- a) 当PWR\_ON信号被判为有效时，PWR\_ONRST信号被强制变为低电平

- b) V<sub>DDCORE</sub>稳压器被PWR\_ON信号关闭

- c) V<sub>DD\_DDR</sub>、V<sub>REF\_DDR</sub>、V<sub>TT</sub>和V<sub>DD\_PERIPH</sub>被PWR\_ONRST信号关闭。

4. 遇到唤醒事件时，MPU退出待机模式<sup>(d)</sup>，并使PWR\_ON信号有效，使PWR\_LP信号无效：

- a) 当PWR\_ON和NRST信号均为高电平时，PWR\_ONRST信号上升。V<sub>DD\_DDR</sub>、V<sub>REF\_DDR</sub>、V<sub>TT</sub>和V<sub>DD\_PERIPH</sub>被PWR\_ONRST信号启用，V<sub>DD\_DDR</sub>、V<sub>REF\_DDR</sub>、V<sub>TT</sub>和V<sub>DD\_PERIPH</sub>电压开始上升。

- b) V<sub>DDCORE</sub>稳压器由PWR\_ON信号启用，V<sub>DDCORE</sub>电压开始上升。

- c) 一旦V<sub>DDCORE</sub>电压高于V<sub>PVDCORE\_0</sub>上升最小阈值，将开始t<sub>VDDCORETEMPO</sub>时延。只要t<sub>VDDCORETEMPO</sub>时延没有过去，MPU保持内部复位状态。

5. t<sub>VDDCORETEMPO</sub>时延过后，MPU退出内部复位状态（V<sub>DDCORE\_OK</sub>）：

- a) V<sub>DDCORE</sub>电压应高于V<sub>DDCORE</sub>最小工作电压。这应该由V<sub>DDCORE</sub>稳压器电压转换率来保证。

- b) MPU执行内部硬件初始化（允许在约130 μs的时间内加载HSI和选项字节），然后进入运行模式。

- c) EADLY延时定时器将启动。

-

- a. POPL定时器允许设置最短待机时间（最短PWR\_ON脉冲低电平时间）。应设置POPL定时器，以保证外设稳压器的最短关闭时间。这是为了确保外设在低电压下正确重启。POPL定时器应根据具有最慢下降电压的稳压器进行设置（在此应用中，建议设为10 ms）。

- b. 当从待机模式恢复时，EADLY定时器防止Boot ROM在准备就绪之前对启动外设执行任何访问。通常，其目的是等待闪存（由Boot ROM读取）获得稳定的电压，从而获取启动软件。在该应用中，建议采用默认值（10 ms），以等待V<sub>DD\_PERIPH</sub>和V<sub>DD\_USB</sub>电压稳定下来（参见RM0436 [\[1\]](#) 获取更多详细信息）。

- c. 或者，如果软件在进入待机模式之前未关闭V<sub>DDA1V8\_REG</sub>，此时会被硬件自动禁用，关闭V<sub>DD\_USB</sub>。在本例中，V<sub>DDA1V8\_REG</sub>由硬件在退出待机模式时自动打开，打开V<sub>DD\_USB</sub>。

- d. STM32MP15x在退出待机模式之前需等待POPL定时器时间过去；即使之前发生了唤醒事件。

6. 当EADLY延时过后，Boot ROM开始访问外部外设（闪存），以加载和执行启动软件。默认情况下，当EADLY延时过后，所有稳压器电压都应稳定；特别是 $V_{DD\_PERIPH}$ ，它是为闪存供电的电源域。

- a) 读取Boot ROM（外设启动），并验证和执行FSBL。

- b) 该软件检测到“退出待机模式”，并相应地恢复内核软件。

7. 软件恢复运行之后，它可能接通USB电源域，方法是接通 $V_{DDA1V8\_REG}$ ，使 $V_{DD\_USB}$ 稳压器开启，具体取决于USB器件是否存在。

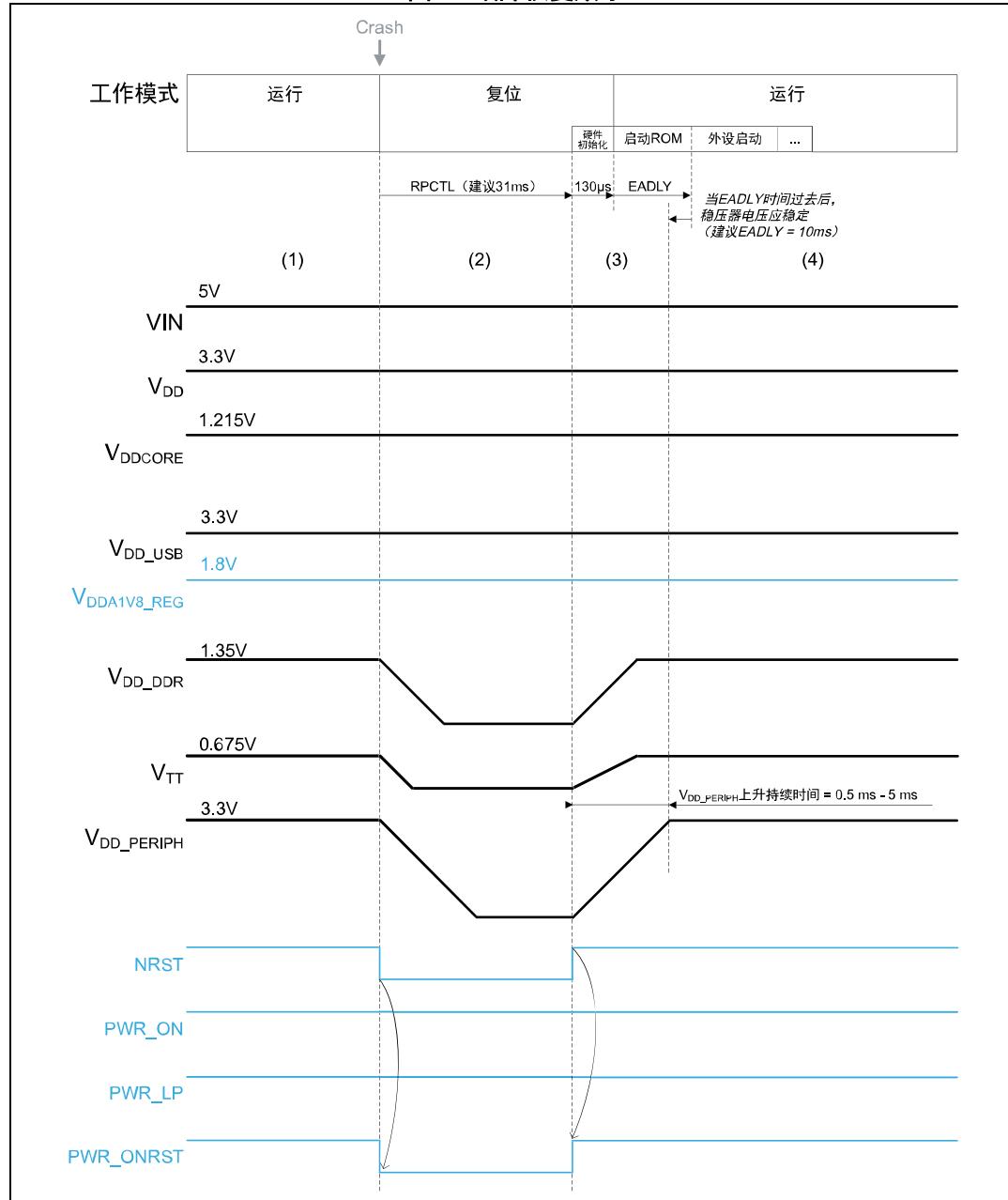

## 4.3 故障恢复管理

如第 3.3.1节：故障恢复管理电路（可选）中所示，可以在设计中添加一个可选的外部分立电路（参见图 6：PWR\_ONRST故障恢复管理信号），用于执行外设电源循环。这允许外设在崩溃后正确地重启。这特别适合闪存，它在崩溃之后没有复位输入以正确重启。

图 10中显示的顺序说明了故障恢复顺序，详情请见图 1：分立电源拓扑示例，IO位于3.3 V 和DDR3L处中的实现步骤。

图10. 故障恢复顺序

1. 应用已上电并运行。在应用初始化过程中，RPCTL定时器（参见[第 3.3.1节](#)）设为31 ms，EADLY设为10 ms。发生崩溃（iwdg1\_out\_rst或iwdg2\_out\_rst watchdog超时），或者从用户复位按钮执行NRST脉冲。

2. MPU确认NRST信号有效，RPCTL定时器启动：

- a) NRST\_CORE和PWR\_ONRST信号被NRST信号强制变为低电平。

- b)  $V_{DD\_DDR}$ 、 $V_{REF\_DDR}$ 、 $V_{TT}$ 和 $V_{DD\_PERIPH}$ 稳压器被PWR\_ONRST信号关闭。

- c)  $V_{DD\_DDR}$ 、 $V_{REF\_DDR}$ 、 $V_{TT}$ 和 $V_{DD\_PERIPH}$ 电压下降

3. RPCTL定时器时间间隔过后（31 ms后）：

- a) MPU释放NRST信号。

- b) NRST\_CORE信号随NRST信号升高，PWR\_ONRST信号升高，因为PWR\_ON和NRST信号都为高电平。

- c)  $V_{DD\_DDR}$ 、 $V_{REF\_DDR}$ 、 $V_{TT}$ 和 $V_{DD\_PERIPH}$ 稳压器由PWR\_ONRST信号开启， $V_{DD\_DDR}$ 、 $V_{REF\_DDR}$ 、 $V_{TT}$ 和 $V_{DD\_PERIPH}$ 电压开始升高。

- d) MPU执行内部硬件初始化（允许在约130  $\mu$ s的时间内加载HSI和选项字节），然后进入运行模式。

- e) EADLY延时定时器将启动。

4. 当EADLY延时过后，Boot ROM开始访问外部外设（例如，闪存），以加载和执行启动软件（外设启动）。默认情况下，当EADLY延时过后，所有稳压器电压都应稳定；特别是 $V_{DD\_PERIPH}$ ，它是为闪存供电的电源域。

## 5 STM32MP15xD和STM32MP15xF增强型CPU频率供应管理

STM32MP15xD和STM32MP15xF器件具有增强的用户任务配置文件（参见AN5438 [\[8\]](#)）。该配置文件允许ARM®双Cortex®-A7 CPU在更高的时钟频率下运行（参见DS12505 [\[5\]](#)了解详细信息和限制）。

相应地，当CPU的工作频率（Fmpuss\_ck）为650 MHz以上时，V<sub>DDCORE</sub>电压必须提高。当其不在650 MHz以上的运行模式下运行时，V<sub>DDCORE</sub>电压必须设置回其标称电压（1.2 V典型值）。这意味着稳压器模块必须支持两个输出电压。在该应用笔记中，我们选择使用LP-Stop模式。因此，这两个输出电压由MPU的PWR\_LP信号驱动。参见[第 6.2.1 节：面向STM32MP15xD和STM32MP15xF器件的VDDCORE电源域的VRM规范](#)了解关于VRM的详细信息。

[图 11](#)显示的应用与[STM32MP15x带有DDR3L和3.3 V I/O电压接口](#)中的应用相同，除了V<sub>DDCORE</sub>电源。

图11. 分立电源拓扑示例, IO位于3.3 V, DDR3L和VDDCORE电压缩放

1. MPU去耦方案没有显示（参见AN5031）。

2. 没有显示SMPS和LDO稳压器产品部件号、以及分立元件，但[第6节：稳压器模块（VRM）规范](#)详细介绍了其电气规范。

3. 没有显示VIN上的附加保护，如ESD、EMI滤波和过电压。

## 5.1 故障恢复管理和特定系统工作模式

[第 3.3 节：低功耗模式和故障恢复管理](#)中给出的信息同样适用于STM32MP15xD 和 STM32MP15xF器件，除了[表 3：系统工作模式](#)（被[表 4：系统工作模式](#)替换）。

此表总结了[图 11：分立电源拓扑示例，IO位于3.3 V，DDR3L 和VDDCORE电压缩放](#)中所示的应用工作模式的电源状态。

表4. 系统工作模式

| 电源模式               | NRST<br>NRST_CORE | VDD      | PWR_ON /<br>VDDCORE       | PWR_ON /<br>VDDCORE | PWR_LP /<br>VTT |

|--------------------|-------------------|----------|---------------------------|---------------------|-----------------|

| 运行                 | 1                 | 启动       | 1 / On_hv <sup>(1)</sup>  | 1 / 启动              | 1 / 启动          |

| 停止                 | 1                 | 启动       | 1 / On_hv <sup>(2)</sup>  | 1 / 启动              | 1 / 启动          |

| LP-Stop            | 1                 | 启动       | 1 / On_nom <sup>(3)</sup> | 1 / 启动              | 0 / 关闭          |

| 待机                 | 1                 | 启动       | 0 / 关闭                    | 0 / 关闭              | 0 / 关闭          |

| VBAT或断电            | -                 | 关闭（无VIN） | 关闭（无VIN）                  | 关闭（无VIN）            | 关闭（无VIN）        |

| 崩溃<br>(watchdog超时) | 0 (脉冲)            | 启动       | 1 / On_hv                 | 0 / 关闭              | 1 / VTT关闭       |

1. 高电压启动: VDDCORE = 1.34 V增强CPU频率电压。

2. 至于增强CPU频率任务配置文件的可靠性，使用“高电压”的Stop（停止）模式被认为是RUN（运行）模式。有了本应用笔记中描述的VRM，建议使用LP-Stop而不是Stop模式。

3. 标称电压启动: VDDCORE = 1.2 V标称电压。

## 5.2 上电 / 下电时序和复位管理

[第 4.1 节：上电 / 下电时序和复位管理](#)中给出的数据同样适用于STM32MP15xD 和 STM32MP15xF器件，除了VDDCORE电压值：1.34 V而不是1.215 V。

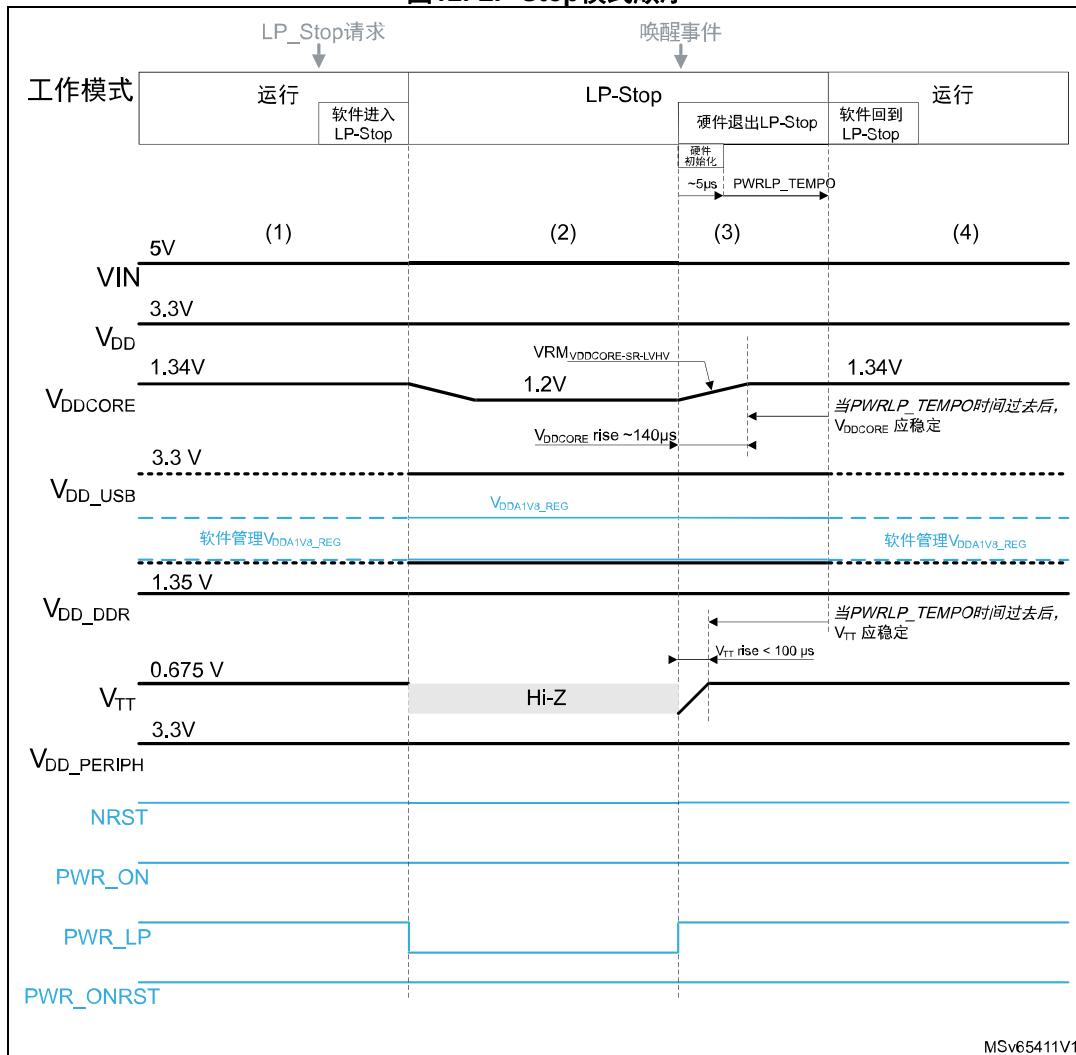

## 5.3 低功耗模式管理

### 5.3.1 LP-Stop模式

[图 12：LP-Stop模式顺序](#)中显示应用LP-Stop模式顺序，详情请参见[图 11：分立电源拓扑示例，IO位于3.3 V, DDR3L 和VDDCORE电压缩放](#)中的实现步骤。

在本应用中，VDDCORE由两路电压驱动：

- 在运行模式下是1.34 V，用于支持增强CPU频率

- 在低功耗停止模式下是1.2 V

在低功耗模式下， $V_{TT}$  稳压器设为高阻抗。

图12. LP-Stop模式顺序

- 应用已上电并运行。当请求LP\_Stop模式时，软件准备进入LP\_Stop模式（停止一些时钟，将DDR设为自刷新，设置PWRLP\_TEMPO等）。然后设置LPDS寄存器以进入LP-Stop模式：使PWR\_LP信号有效：

- $V_{TT}$ 进入低功耗模式（高阻抗）。

- $V_{DDCORE}$ 电压下降到VRM<sub>VDDCORE-LPSTOP</sub>电压（1.2V）并且保持稳定

- 遇到唤醒事件时，MPU退出LP-Stop模式，并使PWR\_LP信号无效：

- $V_{TT}$ 退出低功耗模式

- $V_{DDCORE}$ 电压通过VRM<sub>VDDCORE-SR-LVHV</sub>电压转换速率升高到VRM<sub>VDDCORE-RUN</sub>电压（1.34V），并且保持稳定。

- 执行时钟恢复过程。

- HSI时钟振荡器稳定（大约需要5μs）之后，PWRLP\_TEMPO定时器超时，等待 $V_{TT}$ 稳压器和 $V_{DDCORE}$ 电压趋于稳定。在应用中， $V_{TT}$ 稳压器恢复时间小于100 μs，VDDCORE稳压器恢复时间约为140 μs。因此，PWRLP\_TEMPO持续时间最少应有140 μs（ $V_{TT}$ 和 $V_{DDCORE}$ 之间的最大上升持续时间值）。

- 当PWRLP\_TEMPO延时过后，应用进入运行模式。该软件从LP-Stop模式恢复（恢复时钟，从自刷新恢复DDR等）。根据USB动作，软件可以打开或关闭VDDA1V8\_REG（MPU的内部稳压器），这将自动打开或关闭VDD\_USB稳压器。

### 5.3.2 待机模式

第 4.2.2 节：待机模式中给出的数据同样适用于 STM32MP15xD 和 STM32MP15xF 器件，除了 VDDCORE 电压值：1.34 V 而不是 1.215 V。

## 6 稳压器模块 (VRM) 规范

本节提供为MPU电源域供电的稳压器模块 (VRM) 的电气规范。

产品设计者在设计VRM (参见图 13) 时, 必须根据这些电气规范选择稳压器IC和相关的分立元件。

本节仅适用于严格遵循MPU去耦方案 (参见AN5031[1]) 和布局建议, 以最小化电力传输网络阻抗的应用场景。

图13. 稳压器模块周边回路示例

### 6.1 VDD ( $V_{DD\_ANA}$ 、 $V_{DD\_PLL}$ 、 $V_{DD\_DSI}$ ) 的VRM规范电源域

$V_{DD}$  是IO电压接口的主电源, 在待机模式期间, 内部部件保持供电。 $V_{DD\_ANA}$ 、 $V_{DD\_PLL}$ 和 $V_{DD\_DSI}$ 必须连接到 $V_{DD}$ 。 $V_{DD}$ 通常为1.8 V或3.3 V, 可以设为1.71 V-2 V或2.7 V-3.6 V范围内的值。

只要VIN电压存在, 此电源总是启用。不需要选择带EN引脚的稳压器。然而, 为了稳定输入电压, 一个EN引脚可能需要添加一个分立RC滤波器来延迟稳压器启动。

表5. VDD电源域的VRM规范

| 符号                | 参数                    | 工作条件                                               | 最小          | 典型值             | 最大值        | 单位         |

|-------------------|-----------------------|----------------------------------------------------|-------------|-----------------|------------|------------|

| $VRM_{VDD}$       | 输出电压范围                | 包括 $VRM_{VDD-N}$                                   | 1.71<br>2.7 | 1.8<br>3.0或 3.3 | 2.0<br>3.6 | V          |

| $VRM_{VDD-ACC}$   | 输出电压精度                | 包括线性调节、负载调节和温度变化                                   | -5          | -               | +5         | %          |

| $VRM_{VDD-N}$     | 输出噪声电压<br>(SMPS的波纹电压) | $I_{OUT} = 10 \mu A-300 mA$<br>$f = 10 Hz$ 至 5 MHz | -           | -               | 30         | $mV_{p-p}$ |

| $VRM_{IDD}$       | 连续输出电流                |                                                    | 300         | -               | -          | $uA$       |

| $VRM_{VDD-TRANS}$ | 负载瞬态调节                | $I_{OUT} = 1 mA-100 mA$ 或 $100 mA - 1 mA/1 \mu s$  | -           | -               | +/-30      | $mV$       |

## 6.2 VDDCORE电源域的VRM规范

$V_{DDCORE}$ 是为所有MPU核心部件（包括双核Arm®Cortex®-A7CPU和3DVivante®GPU）供电的主数字电压。因此， $V_{DDCORE}$ 电源会出现明显的电流负载瞬态。因此，应特别注意MPU去耦电容器的放置位置和布局，以便最小化电力传输网络阻抗。

由于 $V_{DDCORE}$ 在待机模式下是关闭的，需要一个带EN引脚的稳压器来支持待机模式。除了选择带有输出放电电阻的稳压器外，建议在稳压器被禁用时允许电压快速下降。这是为了在应用进入待机模式时最小化POPL定时器MPU寄存器的设置)。

表6. VDDCORE电源域的VRM规范

| 符号                            | 参数           | 工作条件                                                                                          | 最小    | 典型值   | 最大值            | 单位                       |

|-------------------------------|--------------|-----------------------------------------------------------------------------------------------|-------|-------|----------------|--------------------------|

| VRM <sub>VDDCORE</sub>        | 输出电压         |                                                                                               | -     | 1.215 | -              | V                        |

| VRM <sub>VDDCORE-ACC</sub>    | 输出电压精度       | 包括线性调节、负载调节和温度变化                                                                              | -2.88 | -     | +2.88          | %                        |

| VRM <sub>VDDCORE-RIPPLE</sub> | 输出噪声/波纹电压    | $I_{OUT} = 1 \text{ mA}$ 至 $1500 \text{ mA}$<br>$f = 10 \text{ Hz}$ 至 $5 \text{ MHz}$         | -     | -     | 30             | $\text{mV}_{\text{p-p}}$ |

| VRM <sub>ICORE</sub>          | 连续输出电流       |                                                                                               | 1500  | -     | -              | $\mu\text{A}$            |

| VRM <sub>VDDCORE-TRANS</sub>  | 负载瞬态调节       | $I_{OUT} = 1 \text{ mA} - 450 \text{ mA}$ 或 $450 \text{ mA} - 1 \text{ mA}$ / $1 \mu\text{s}$ | -     | -     | $\pm 30^{(1)}$ | $\text{mV}$              |

| VRM <sub>VDDCORE-SR</sub>     | 启动时的输出电压转换速率 | VRM <sub>VDDCORE</sub> 从 $V_{PVDCORE\_0}$ 转为 $V_{DDCORE-\text{Min}}$                          | 1.15  | -     | -              | $\text{mV}/\mu\text{s}$  |

- 当瞬态电流为负时，由负载瞬态引起的电压过冲/下冲不得高于 $VRM_{VDDCORE} + VRM_{VDDCORE-TRANS}$ ；当瞬态电流为正时，不得低于 $VRM_{VDDCORE} - VRM_{VDDCORE-TRANS}$ 。输出电压噪声/纹波（VRM<sub>VDDCORE-RIPPLE</sub>）默认包含在VRM<sub>VDDCORE-TRANS</sub>预算中。

### 6.2.1 面向STM32MP15xD和STM32MP15xF器件的VDDCORE电源域的VRM规范

当Arm®双Cortex®-A7在增强模式下以800-MHz时钟频率工作时，VRM必须向MPU的 $V_{DDCORE}$ 提供VRM<sub>VDDCORE-RUN</sub>电压。当应用在LP-Stop模式下工作时，VRM必须向MPU的 $V_{DDCORE}$ 提供VRM<sub>VDDCORE-LPSTOP</sub>电压。因此，VRM必须支持两路由MPU的PWR\_LP信号驱动的可控输出电压（参见表 11 获取详细信息）。

表 7 中提供VRM电气规范。

第 7.3 节 提供VRM电路示例。

表7. 通过电压缩放实现800 MHz支持的VDDCORE电源域的VRM规范

| 符号                             | 参数                                  | 工作条件                                                                                       | 最小          | 典型值  | 最大值   | 单位    |

|--------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------|-------------|------|-------|-------|

| VRM <sub>VDDCORE-RUN</sub>     | 输出电压<br>(在运行模式下)                    | STM32MP15xF在运行模式下的频率高于650 MHz                                                              | -           | 1.34 | -     | V     |

| VRM <sub>VDDCORE-LPSTOP</sub>  | 输出电压<br>在LP-Stop模式下                 | STM32MP15xF在LP-Stop模式下                                                                     |             | 1.2  |       | V     |

| VRM <sub>VDDCORE-ACC</sub>     | 输出电压精度<br>在运行模式或LP-Stop模式下          | 包括线性调节、负载调节和温度变化                                                                           | -2.98       | -    | +2.98 | %     |

| VRM <sub>VDDCORE-SR-LVHV</sub> | 从'LP-Stop'转为<br>'RUN'工作模式时的输出电压转换速率 | VRM <sub>VDDCORE</sub> 从VRM <sub>VDDCORE-LPSTOP-Min</sub> 转为VRM <sub>VDDCORE-RUN-Min</sub> | (参见<br>(1)) | -    | -     | mV/μs |

1. VRM<sub>VDDCORE-SR-LVHV</sub>值没有技术约束。然而, 如第 5.3.1节: LP-Stop模式中所述, 应根据VRM<sub>VDDCORE-SR-LVHV</sub>值设置MPU的PWRLP TEMPO定时器。例如, 如果VRM的电压转换速率为1 mV/μs, 则从VRM<sub>VDDCORE-LPSTOP</sub>转为VRM<sub>VDDCORE-RUN</sub>的恢复电压持续时间为 $140 \mu s = (1340 \text{ mV} - 1200 \text{ mV}) \times 1 \text{ mV/}\mu\text{s}$ 。在本例中, MPU的PWRLP TEMPO定时器应设为最小值 $140 \mu s$ 。建议添加10-20%的余量, 以说明最坏的情况(温度、公差等)。建议的电压转换速率为1-10 mV/μs。较低的电压转换速率会增加瞬态电流, 但会减少从'LP-Stop'向'Run'模式转变期间的输出电压恢复时间, 而较高的电压转换速率会带来相反的结果。

其他VRM电气规范(VRM<sub>VDDCORE-RIPPLE</sub>、VRM<sub>ICORE</sub>、VRM<sub>VDDCORE-TRANS</sub>和VRM<sub>VDDCORE-SR</sub>)在表 6: VDDCORE电源域的VRM规范中定义。

### 6.3 VDDQ\_DDR电源域VRM规范

V<sub>DDQ\_DDR</sub>为MPDDR电压接口供电。除了V<sub>DDQ\_DDR</sub>, VRM也应为DDR供电。本节仅涵盖双DDR3L的VRM规范(参见图 1: 分立电源拓扑示例, IO位于3.3 V和DDR3L处获取详细信息)。应特别注意去耦电容器的放置位置和布局, 以便最小化MPU<sub>VDDQ\_DDR</sub>电源和DDR3L的电力传输网络阻抗。更多详细信息, 请参见AN5122 [6]。

由于DDR内存在待机模式下是关闭的, 需要一个带EN引脚的稳压器来支持待机模式。此外, 建议选择带有输出放电电阻的稳压器, 以便在稳压器被禁用(应用进入待机模式)时允许电压快速下降。

假设:

- DDR3L电压范围为1.283 V到1.45 V(1.35 V典型值)。(来自JEDEC JESD79-3-1A)

- 1.425 V最大DC值(来自JEDEC JESD79-3-1A) = 1.35 V + 5.5%

- VDDR最大AC值 = 25 mV(1.45 V - 1.425 V)

- 相同的值用于VDDR最小AC

- 1.308 V最小DC值(1.283 V + 0.025) = 1.35 V - 3.1%

表8. VDDQ\_DDR和DDR3L IC电源域的VRM规范

| ??                      | ??      | ????                  | ??                          | ???  | ???                         | ?? |

|-------------------------|---------|-----------------------|-----------------------------|------|-----------------------------|----|

| VRM <sub>VDDR</sub>     | ?????   |                       | -                           | 1.35 | -                           | V  |

| VRM <sub>VDDR-ACC</sub> | ??????? | ????????????????????? | -3<br>(-3.1) <sup>(1)</sup> | -    | +3<br>(+5.5) <sup>(1)</sup> | %  |

表8. VDDQ\_DDR和DDR3L IC电源域的VRM规范

| ??                         | ??        | ????                                                                                          | ??   | ??? | ???            | ??                |

|----------------------------|-----------|-----------------------------------------------------------------------------------------------|------|-----|----------------|-------------------|

| VRM <sub>VDDR-RIPPLE</sub> | ????/???? | $I_{OUT} = 1 \text{ mA} \dots 1 \text{ A}$<br>$f = 10 \text{ Hz} \dots 5 \text{ MHz}$         | -    | -   | 25             | mV <sub>p-p</sub> |

| VRM <sub>IDDR</sub>        | ???????   |                                                                                               | 1000 | -   | -              | uA                |

| VRM <sub>VDDR-TRANS</sub>  | ???????   | $I_{OUT} = 1 \text{ mA} - 450 \text{ mA}$ ? $450 \text{ mA} - 1 \text{ mA}$ / $1 \mu\text{s}$ | -    | -   | $\pm 25^{(2)}$ | mV                |

| VRM <sub>VDDR-SS</sub>     | ???????   | ?EN?????VRM <sub>VDDR</sub> ~ 0??95%<br>?VRM <sub>VDDR</sub> ?????                            | -    | -   | $10^{(3)}$     | us                |

- ????????????? +/-3%

- ????????????????????/?????VRM<sub>VDDR</sub> + VRM<sub>VDDR-TRANS</sub>????????????VRM<sub>VDDR</sub> - VRM<sub>VDDR-TRANS</sub>?????/???VRM<sub>VDDR-RIPPLE</sub>?????VRM<sub>VDDR-TRANS</sub>????

- 10 ms?MPU?EADLY?????EADLY??MPU????????????????????????????????? 4?????????

## 7 稳压器模块示例

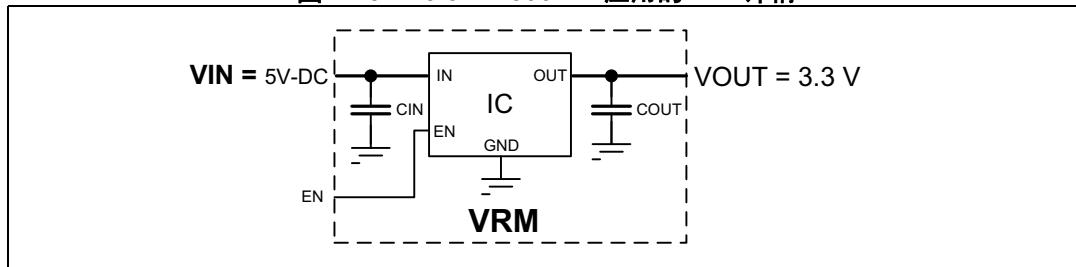

### 7.1 5 V DC~3.3 V DC - 300 mA应用的VRM示例

图14. 5 V~3.3 V - 300 mA应用的VRM详情

表9. 5 V~3.3 V - 300 mA应用的VRM示例

| ??         | ??                                                         |

|------------|------------------------------------------------------------|

| IC         | ??3.3 V LDO DFN4-1x1 mm - ???NCP161AMX330TBG?              |

| CIN / COUT | MLCC - 1 $\mu$ F - 6.3 V - 0402 - Murata GRM155R60J105KE19 |

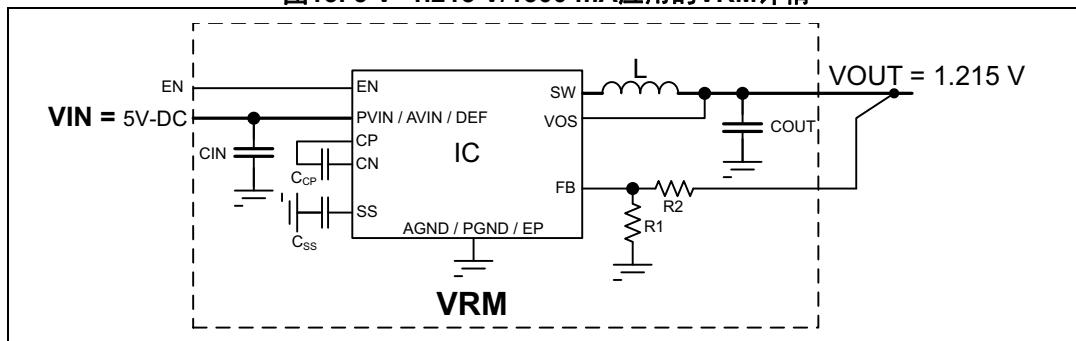

### 7.2 5 V DC~1.215 V DC - 1500 mA应用的VRM示例

图15. 5 V~1.215 V/1500 mA应用的VRM详情

表10. 5 V~1.215 V - 1500 mA应用的VRM示例

| ??                                | ??                                                               |

|-----------------------------------|------------------------------------------------------------------|

| IC                                | ??3A??SMPS - VQFN-3x3 mm – Ti TLV62090RGT                        |

| L                                 | ?? – 1 $\mu$ H – 3.22 A – 14 m $\Omega$ – Wurth 74404043010A     |

| CIN                               | MLCC - 10 $\mu$ F - 10 V - 0603 - Murata GRM188R61A106KE69D      |

| COUT                              | 2 x MLCC – 22 $\mu$ F – 6.3 V – 0603 – Murata GRM188R60J226MEA0J |

| C <sub>CP</sub> / C <sub>SS</sub> | MLCC – 10 nF - 16 V - 0402 – Yageo CC0402KRX7R7BB103             |

| R1                                | 160 k $\Omega$ - 1%                                              |

| R2                                | 82.5 k $\Omega$ - 1%                                             |

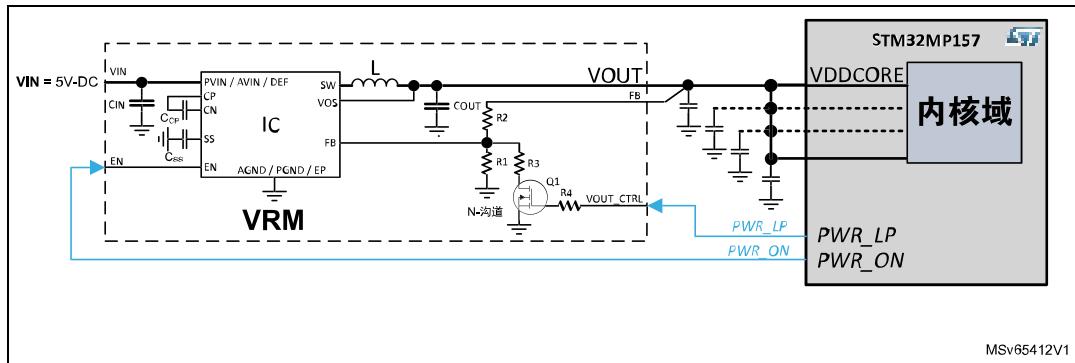

## 7.3 5V DC~可扩展1.34 V / 1.2 V DC - 1500 mA应用的VRM示例

图16. 5 V~可扩展1.34 V / 1.2 V - 1500 mA应用的VRM详情

图 16 中的 VRM 有一个附加电路插入到反馈回路中，允许控制两个输出电压（参见第 7.3.1 节：[Vout \(R1, R2, R3, R4\) 计算实例](#) 获取详细信息）。

| 元件                                | 说明                                                                                                    |

|-----------------------------------|-------------------------------------------------------------------------------------------------------|

| IC                                | 可调节3 A降压SMPS - VQFN-3x3 mm – Ti TLV62090RGT                                                           |

| L                                 | 电感器 – 1 $\mu$ H – 3.22 A – 14 m $\Omega$ – Wurth 74404043010A                                         |

| CIN                               | 2 x MLCC – 10 $\mu$ F – 10 V – 0603 – Murata GRM188R61A106KE69D                                       |

| COUT                              | 2 x MLCC – 22 $\mu$ F – 6.3 V – 0603 – Murata GRM188R60J226MEA0J                                      |

| C <sub>CP</sub> / C <sub>SS</sub> | MLCC – 10 nF – 16 V – 0402 – Yageo CC0402KRX7R7BB103                                                  |

| R1                                | 150 k $\Omega$ - 1%                                                                                   |

| R2                                | 75 k $\Omega$ - 1%                                                                                    |

| R3                                | 430 k $\Omega$ - 1%                                                                                   |

| R4                                | 150 k $\Omega$ - 5%                                                                                   |

| Q1 <sup>(1)</sup>                 | N-沟道MOSFET, V <sub>gs(th)</sub> : 1V, V <sub>ds</sub> : 20 V, I <sub>d</sub> : 0.5 A - Vishay Si1062x |

1. Q1 MOSFET选择的关键参数：

- N-沟道

- I<sub>DSS</sub> << 2  $\mu$ A (条件: V<sub>ds</sub> = 0.8V, V<sub>gs</sub> = 0 V)

- V<sub>GS(th)</sub> < 1.8 V (应低于PWR\_LP IO 电压；所以低于MPU的VDD电压)

- I<sub>D min</sub> > 2  $\mu$ A

- V<sub>DS</sub> > 0.8 V

- 建议C<sub>rss</sub>小于20pF (这是为了避免在PWR\_LP信号跃迁过程中能量从PWR\_LP信号传输到Q1栅极-漏极 (通过C<sub>rss</sub>)，然后再传输到IC的反馈节点。在PWR\_LP信号跃迁过程中，这种能量传输会对IC的反馈节点产生干扰，造成小的过冲和下冲现象，持续时间几  $\mu$ s)。

表11. 1.34V / 1.2 V的VRM真值表

| EN | VOUT_CTRL | VOUT     |

|----|-----------|----------|

| 0  | -         | 0 V (关闭) |

| 1  | 0         | 1.2 V    |

| 1  | 1         | 1.34 V   |

### 7.3.1 Vout (R1、R2、R3、R4) 计算实例

图 16 中使用的 IC (降压SMPS) 有一个反馈电压等于  $V_{FB} = 0.8 \text{ V}$ 。

1. 当  $VOUT\_CTRL = 0$  (LP-Stop模式) 时, MOSFET Q1断开, Q1漏极节点是浮动的。输出电压  $VOUT$  是最低值, 等于:

$$VOUT_0 = (R1 + R2) / R1 \times V_{FB} = (150 + 75) / 150 \times 0.8 = 1.2 \text{ V}$$

2. 当  $VOUT\_CTRL = 1$  (运行模式) 时, MOSFET Q1 闭合, Q1漏极节点接地 (相比 R3 的值, Q1  $R_{DS(on)}$  可以忽略)。输出电压  $VOUT$  是最高值, 等于:

$$VOUT_1 = (R1//R3 + R2) / R1//R3 \times V_{FB} = (111.2 + 75) / 111.2 \times 0.8 = 1.339 \text{ V}$$

R1 和 R2 需要首先选择, 以达到输出电压  $VOUT_0 = 1.2 \text{ V}$ 。

在第一步中, 为 R1 或 R2 选择一个任意值。在第二步中, 应选择 R3, 以达到  $VOUT_1 = 1.34 \text{ V}$ 。

R4 具有高阻值, 可增加密勒效应持续时间, 以减少 Q1 晶体管的导通延迟时间。应调整 R4 的阻值, 以便达到合理的输出电压转换速率 ( $VRM_{VDDCORE-SR-LVHV}$ ), 在 1 - 10 mV/ $\mu\text{s}$  之间。

## 7.4 5V DC~1.35 V DC - 1000 mA 应用的VRM示例

图17. 5 V~1.35 V - 1000 mA 应用的VRM详情

表12. 5 V~1.35 V - 1000 mA应用的VRM示例

| 元件                                | 说明                                                               |

|-----------------------------------|------------------------------------------------------------------|

| IC                                | 可调节3 A降压SMPS - VQFN-3x3 mm – Ti TLV62090RG                       |

| L                                 | 电感器 – 1 $\mu$ H – 3.22 A – 14 m $\Omega$ – Wurth 74404043010A    |

| CIN                               | MLCC – 10 $\mu$ F – 10 V – 0603 – Murata GRM188R61A106KE69D      |

| COUT                              | 2 x MLCC – 22 $\mu$ F – 6.3 V – 0603 – Murata GRM188R60J226MEA0J |

| C <sub>CP</sub> / C <sub>SS</sub> | MLCC – 10 nF – 16 V – 0402 – Yageo CC0402KRX7R7BB103             |

| R1                                | 160 k $\Omega$ - 1%                                              |

| R2                                | 110 k $\Omega$ - 1%                                              |

## 7.5 5V DC~3.3 V DC - 2000 mA应用的VRM示例

图18. 5 V~3.3 V - 2000 mA应用的VRM详情

表13. 5 V~3.3V - 2000 mA应用的VRM示例

| 元件                                | 说明                                                               |

|-----------------------------------|------------------------------------------------------------------|

| IC                                | 可调节3 A降压SMPS - VQFN-3x3 mm – Ti TLV62090RGT                      |

| L                                 | 电感器 – 1 $\mu$ H – 3.22 A – 14 m $\Omega$ – Wurth 74404043010A    |

| CIN                               | MLCC - 10 $\mu$ F - 10 V - 0603 - Murata GRM188R61A106KE69D      |

| COUT                              | 2 x MLCC – 22 $\mu$ F – 6.3 V – 0603 – Murata GRM188R60J226MEA0J |

| C <sub>CP</sub> / C <sub>SS</sub> | MLCC – 10 nF - 16 V - 0402 – Yageo CC0402KRX7R7BB103             |

| R1                                | 150 k $\Omega$ - 1%                                              |

| R2                                | 470 k $\Omega$ - 1%                                              |

## 8 版本历史

表14. 文档版本历史

| 日期         | 版本 | 变更                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2019年7月11日 | 1  | 初始版本。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2020年2月14日 | 2  | <p>增加了关于STM32MP15xD和STM32MP15xF器件（支持800 MHz扩展频率）的信息：</p> <ul style="list-style-type: none"> <li>增加了第 5 节：STM32MP15xD 和 STM32MP15xF 增强型 CPU 频率供应管理，<br/>第 6.2.1 节：面向 STM32MP15xD 和 STM32MP15xF 器件的 VDDCORE 电源域的 VRM 规范，<br/>第 7.3 节：5V DC~ 可扩展 1.34 V / 1.2 V DC - 1500 mA 应用的 VRM 示例以及第 7.3.1 节：Vout (R1, R2, R3, R4) 计算实例。</li> </ul> <p>更新了表 1：参考文档、图 1：分立电源拓扑示例，IO 位于 3.3 V 和 DDR3L 处和图 4：分立电源拓扑示例，IO 位于 1.8 V 和 DDR3L 处。</p> <p>更新了第 3.1.2 节：LDO 或 SMPS 的调节器拓扑建议、<br/>第 3.3 节：低功耗模式和故障恢复管理、<br/>第 6.2 节：VDDCORE 电源域的 VRM 规范和<br/>第 6.3 节：VDDQ_DDR 电源域 VRM 规范。</p> <p>修改了<br/>表 8：VDDQ_DDR 和 DDR3L IC 电源域的 VRM 规范中的注释 2。</p> <p>更改了第 7.4 节：5VDC~1.35VDC-1000 mA 应用的 VRM 示例（1000 mA 和 1.35V）的标题</p> <p>更改了表 13：5 V~3.3V - 2000 mA 应用的 VRM 示例（2000 mA 和 3.3V）的标题</p> |

表15. 中文文档版本历史

| 日期         | 版本 | 变更      |

|------------|----|---------|

| 2020年8月15日 | 1  | 中文初始版本。 |

**重要通知 - 请仔细阅读**

意法半导体公司及其子公司（“ST”）保留随时对 ST 产品和 / 或本文档进行变更、更正、增强、修改和改进的权利，恕不另行通知。买方在订货之前应获取关于 ST 产品的最新信息。ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对 ST 产品的选择和使用，ST 概不承担与应用协助或买方产品设计相关的任何责任。

ST 不对任何知识产权进行任何明示或默示的授权或许可。

转售的 ST 产品如有不同于此处提供的信息的规定，将导致 ST 针对该产品授予的任何保证失效。

ST 和 ST 徽标是 ST 的商标。若需 ST 商标的更多信息，请参考 [www.st.com/trademarks](http://www.st.com/trademarks)。所有其他产品或服务名称均为其各自所有者的财产。

本文档中的信息取代本文档所有早期版本中提供的信息。

© 2020 STMicroelectronics - 保留所有权利