## 引言

本文档提供了设计具有ST25R3916器件的电路板时的基本注意事项，以减少多余辐射，将整体底噪声保持在较低水平。

在布局阶段必须考虑ST25R3916与其他有源元件（如收据打印机或显示屏）之间的干扰，以确保干净的信号传输。

必须特别注意沿走线传播的信号以及每个信号的频谱内容。必须在时域和频域中分析信号，以跟踪返回信号源的无用辐射，并采取对策。

通过适当的PCB布局，可以最大限度地减少多种EMI问题，使应用符合FCC、RED和/或CISPR标准。

## 目录

|       |           |    |

|-------|-----------|----|

| 1     | 缩略语       | 4  |

| 2     | 一般建议      | 5  |

| 3     | 基本考虑      | 6  |

| 4     | 走线辐射      | 9  |

| 4.1   | 差分信号      | 9  |

| 4.1.1 | RFO和RFI布线 | 10 |

| 4.2   | 共模信号      | 12 |

| 4.2.1 | SPI数据信号布线 | 14 |

| 5     | 寄生元件和电流回路 | 15 |

| 6     | 去耦和旁路电容   | 16 |

| 7     | 供电滤波      | 19 |

| 8     | 散热焊盘      | 20 |

| 9     | 混合信号PCB布局 | 21 |

| 10    | 结论        | 23 |

| 11    | 版本历史      | 24 |

## 图片目录

|      |                    |    |

|------|--------------------|----|

| 图1.  | 方波                 | 6  |

| 图2.  | 方波的频谱              | 6  |

| 图3.  | 梯形波                | 6  |

| 图4.  | 低通滤波               | 7  |

| 图5.  | 低通滤波器在PCB上的位置      | 8  |

| 图6.  | 具有对称匹配布局的ST25R3916 | 9  |

| 图7.  | PCB的环形区域           | 10 |

| 图8.  | 匹配网络的布线            | 10 |

| 图9.  | 避免GND平面中的缝隙        | 12 |

| 图10. | 共模滤波器 - 在PCB的位置    | 13 |

| 图11. | 共模滤波器 - 原理图        | 13 |

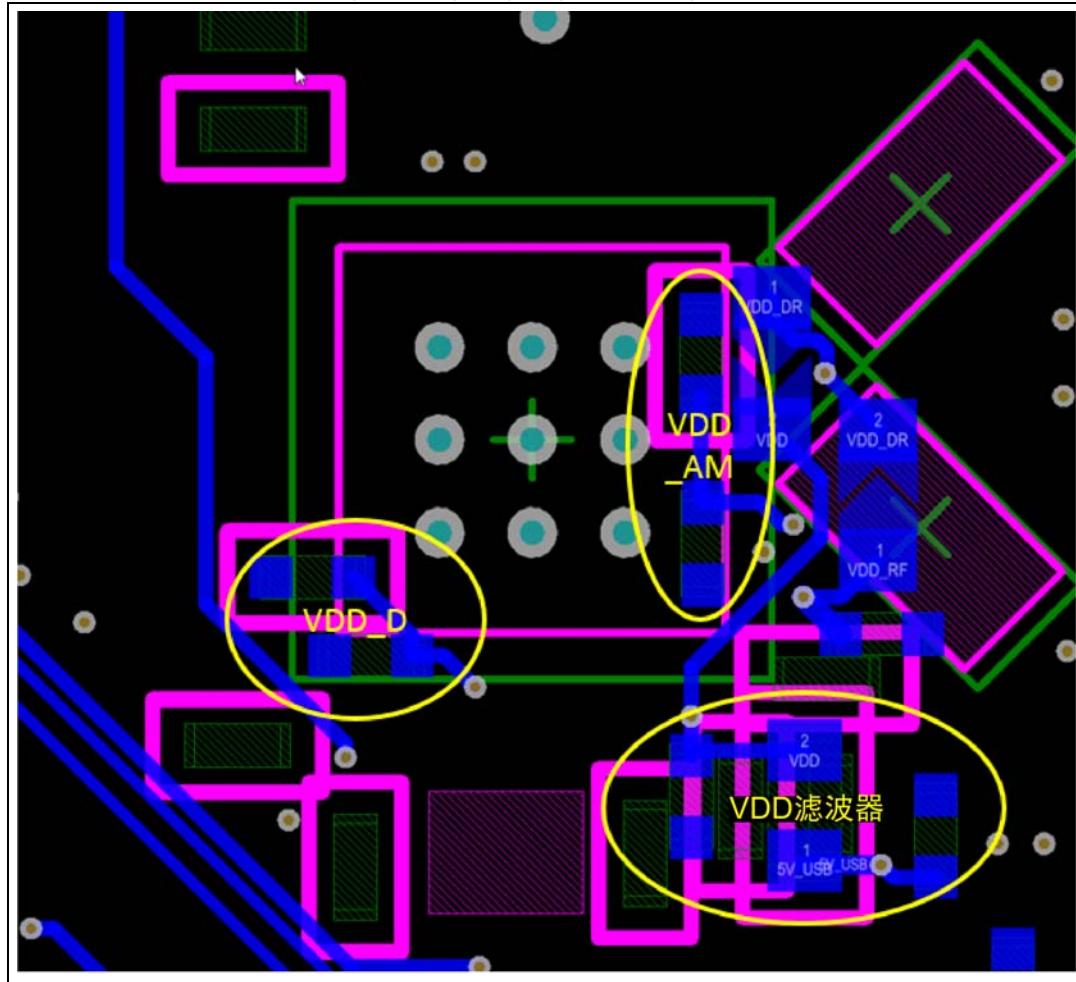

| 图12. | 去耦电容的位置 (顶视图)      | 16 |

| 图13. | 去耦电容的位置 (底视图)      | 17 |

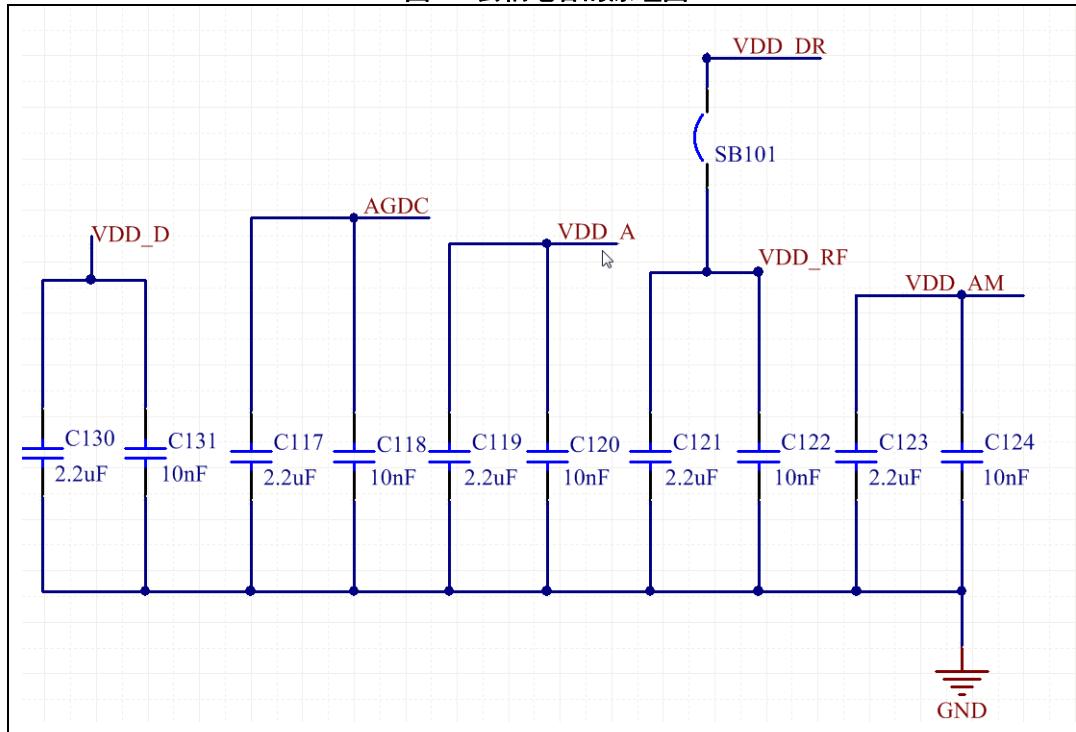

| 图14. | 去耦电容的原理图           | 18 |

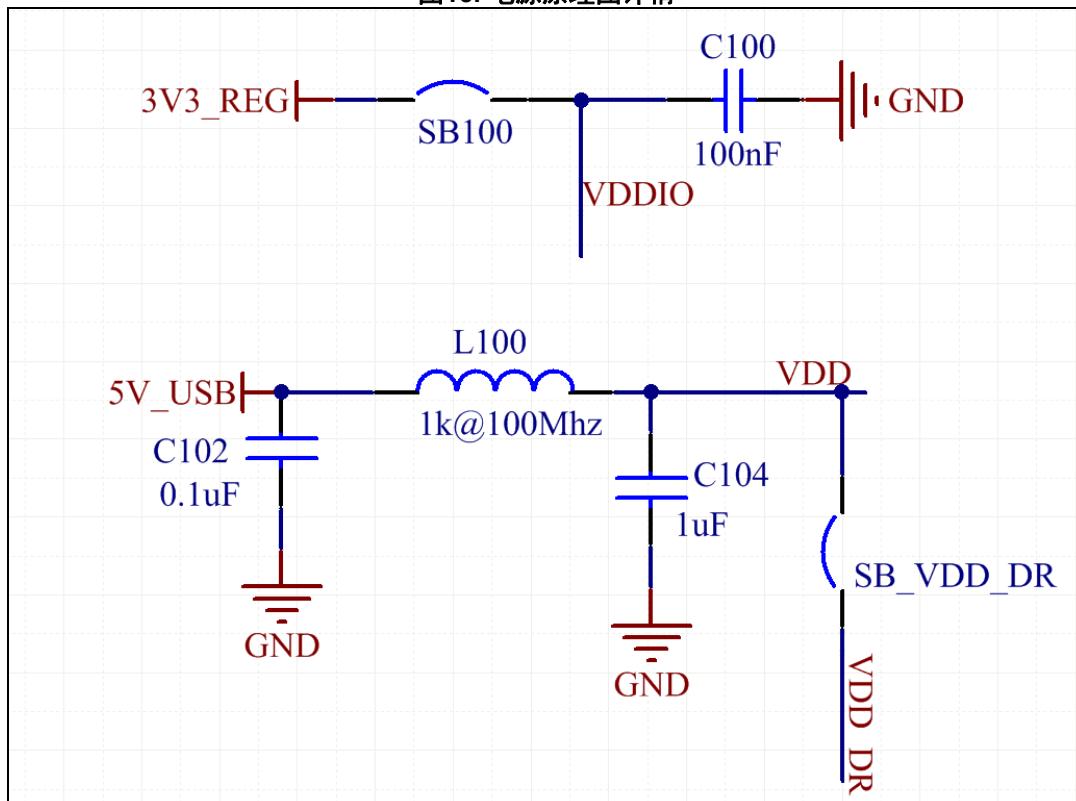

| 图15. | 电源原理图详情            | 19 |

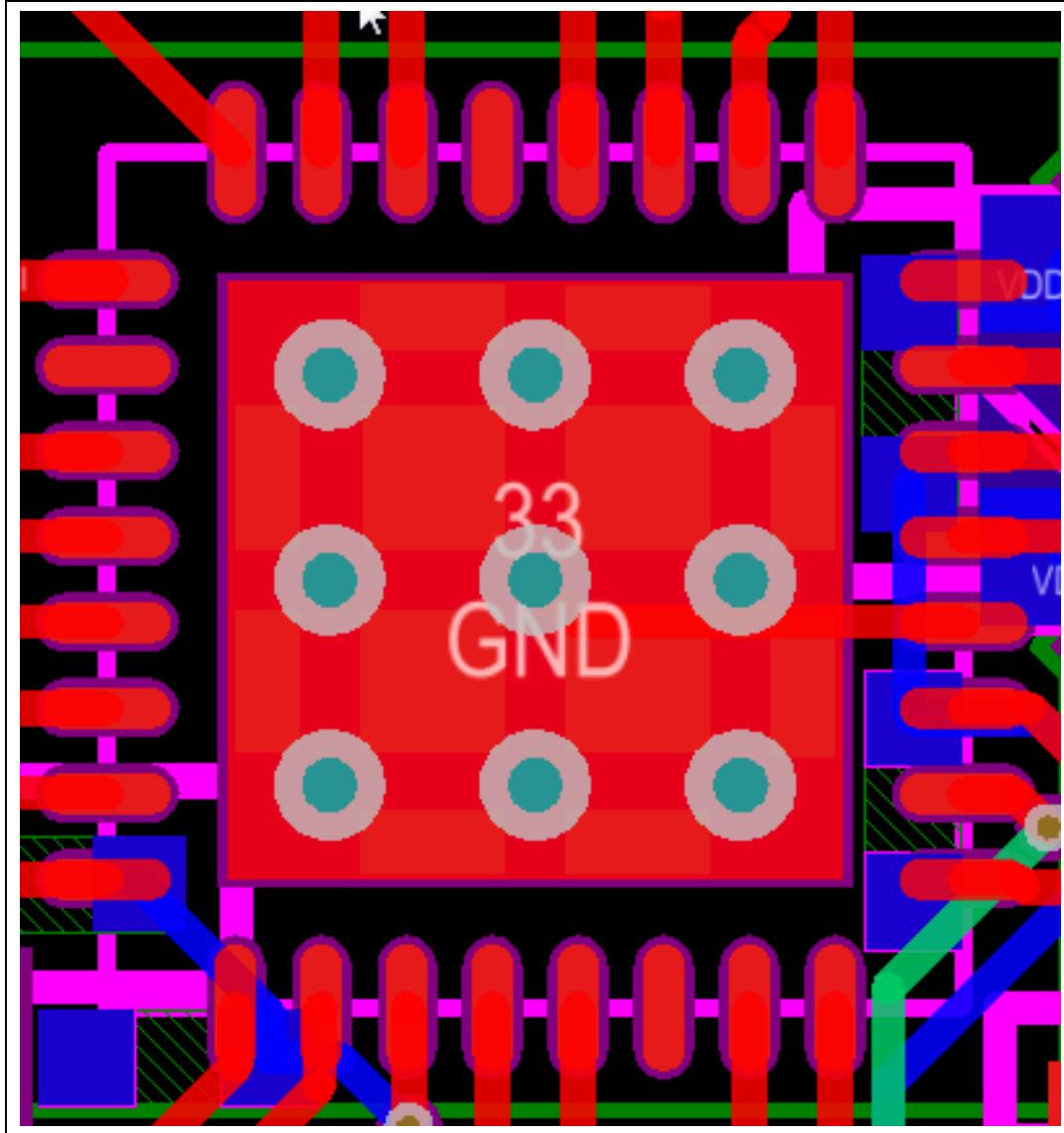

| 图16. | ST25R3916散热焊盘      | 20 |

| 图17. | 模拟和数字信号之间的垂直分离     | 22 |

| 图18. | 4层PCB配置            | 22 |

## 1 缩略语

|             |            |

|-------------|------------|

| <b>AGND</b> | 模拟GND      |

| <b>DGND</b> | 数字GND      |

| <b>EMC</b>  | 电磁兼容性      |

| <b>EMI</b>  | 电磁干扰       |

| <b>EUT</b>  | 被测发射器      |

| <b>ESD</b>  | 静电放电       |

| <b>GND</b>  | 电压接地（参考）电平 |

| <b>IC</b>   | 集成电路       |

| <b>PCB</b>  | 印刷电路板      |

| <b>RFI</b>  | 射频输入       |

| <b>RFO</b>  | 射频输出       |

| <b>USB</b>  | 通用串行总线     |

## 2 一般建议

在PCB设计中，有一些指导原则可有助于优化EMC性能

- 始终考虑并确定返回电流的流动方向和方式。

- 信号布线切勿穿过地平面的间隙。

- 将混合信号PCB的模拟和数字部分单独分区

- 请勿分割电流的返回平面；在电路板的模拟和数字部分下使用一个完整平面。

- 仅在电路板的数字部分中进行数字信号布线（适用于所有数字相关层）。

- 仅在电路板的模拟部分中进行模拟信号布线（适用于所有模拟相关层）。

- 如果接地或电源平面由于特定原因（即机械和/或电气）而被分割，则不要在相邻层上铺设任何走线穿过分割的区域。

- 必须越过电源平面分割处的走线（模拟或数字）必须位于完整接地平面（模拟或数字）的相邻层上。

- A/D和D/A转换器以及大多数其他混合信号IC应被视为具有数字部分的模拟设备，而不是具有模拟部分的数字设备。

- 混合信号IC引脚上的AGND和DGND标记指的是引脚在内部连接的位置，并不表示它们应在何处或如何进行外部连接。在大多数混合信号IC上，AGND和DGND引脚都应连接到模拟返回平面。

- 数字去耦电容应直接连接到数字接地引脚。

- 去耦电容器通过低电感路径，提供IC逻辑门开关时所需的部分或全部瞬态电源电流。

- 去耦电容用于短路或至少减少注入电源接地系统的噪声。

- 去耦不是将电容放置在IC附近以提供瞬态开关电流的作用；而是将L-C网络放置在IC附近以提供瞬态开关电流的作用。

- 对于低频去耦的有效性而言，去耦电容的值非常重要。

- 去耦电容的值在高频时并不重要。在高频时，最重要的标准是减小与去耦电容串联的电感值。

- 有效的高频去耦需要使用大量电容。

- 将去耦电容放置在尽可能靠近设备的位置。

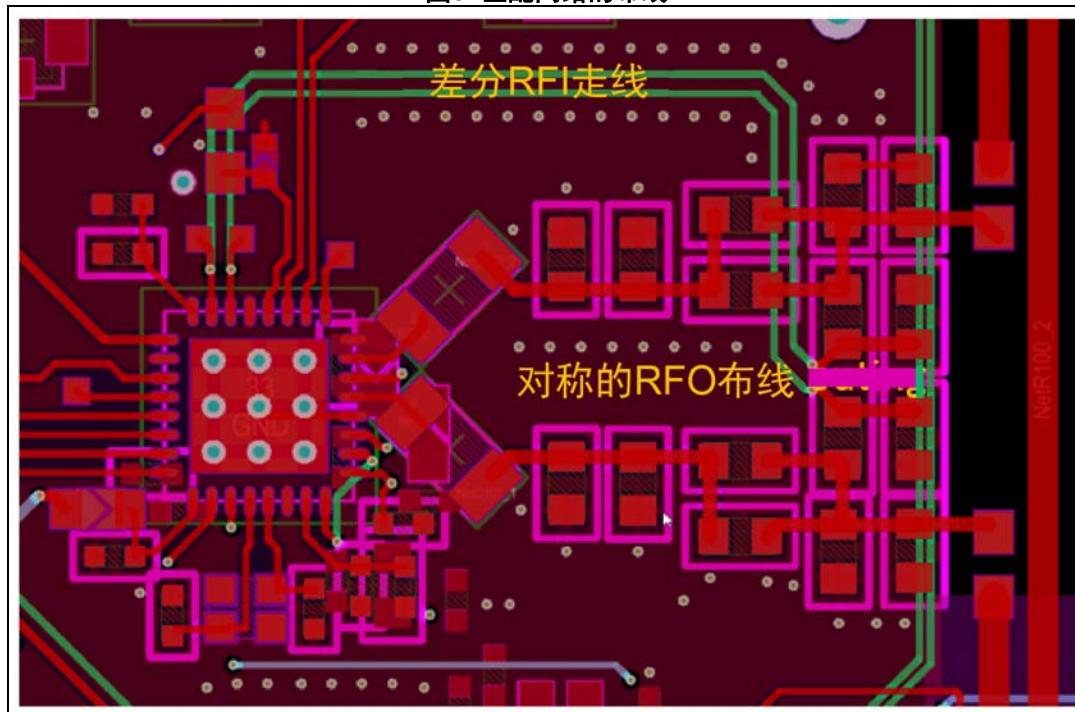

- 以对称方式布置RFI和RFO信号线，避免匹配网络的长信号走线。保持RFO1和RFO2的走线尽可能彼此靠近，这同样适用于RFI1和RFI2。

- 匹配元件需对称放置在靠近彼此的位置。

### 3 基本考虑

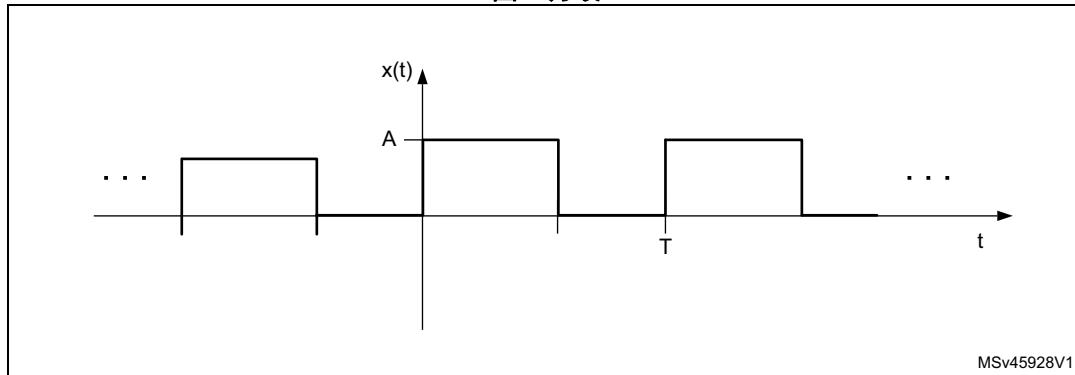

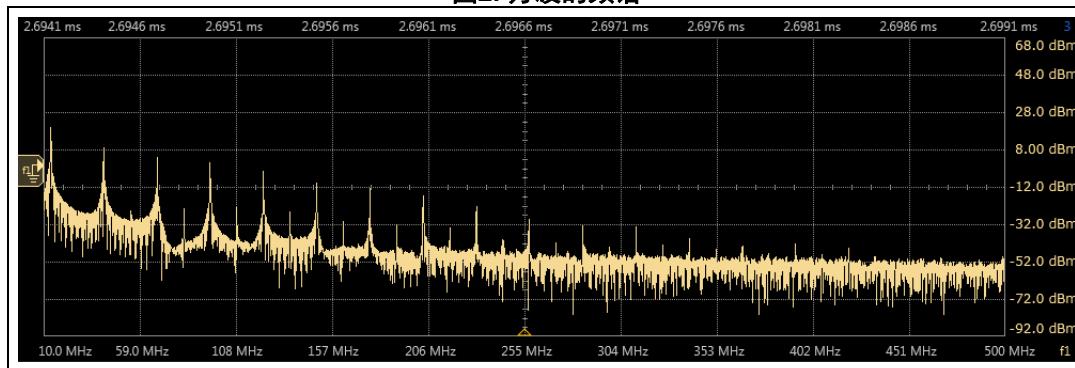

IC生成的大部分信号形态为周期性方波信号（图 1），频谱与图 2 所示相似。

图1. 方波

图2. 方波的频谱

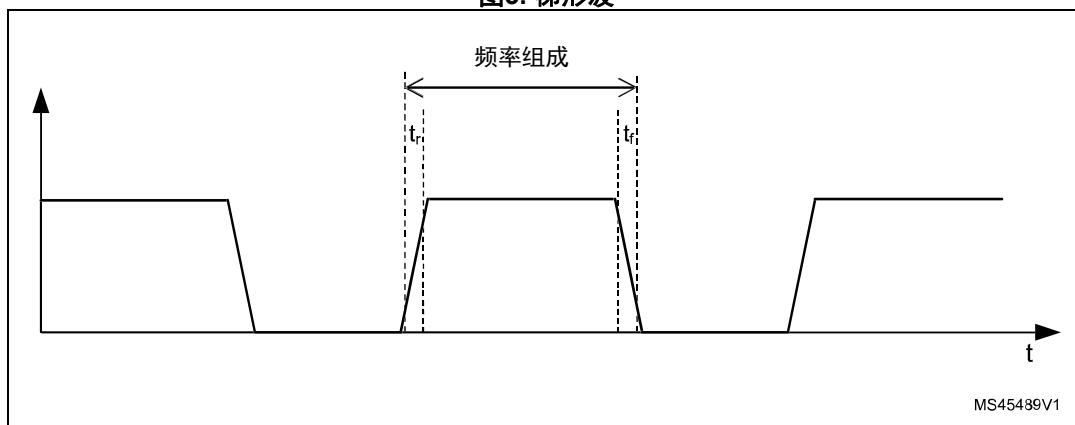

由于实际设备无法生成理想的方波，我们必须处理来自IC或时钟的梯形脉冲，其具有有限的上升和下降的转换时间（图 3）。高次谐波的幅度取决于信号的上升和下降时间，随着上升时间的延长而下降。

图3. 梯形波

对于 ST25R3916，转换速率是内部控制的。

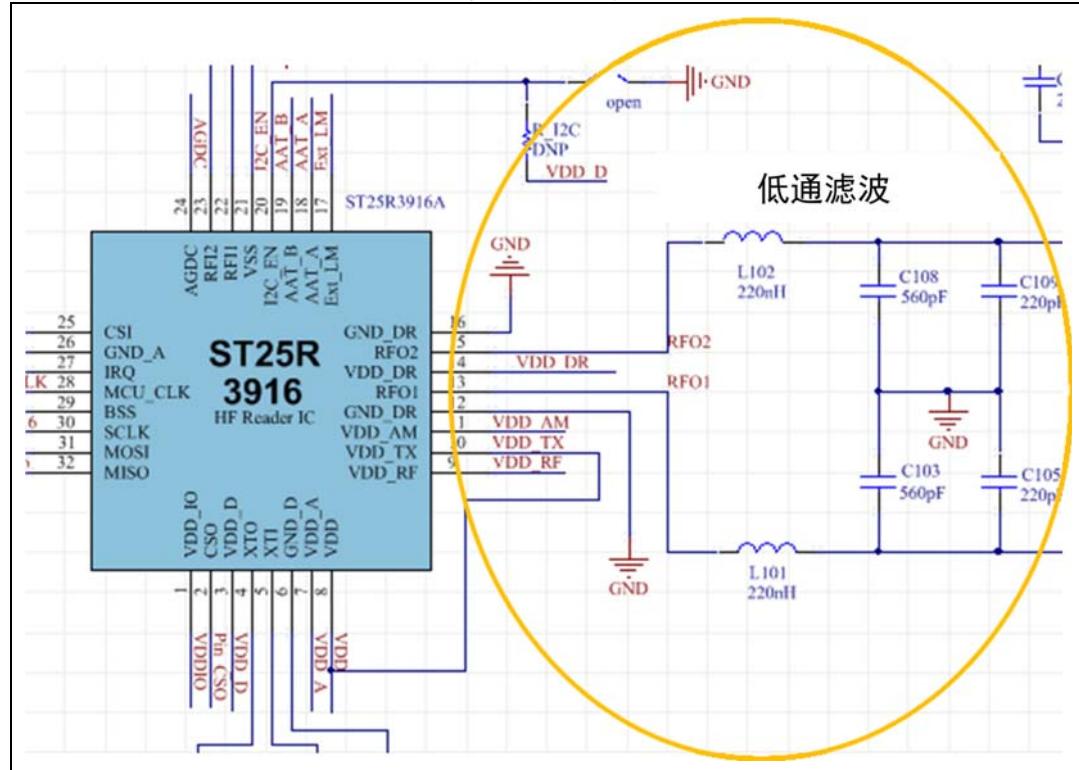

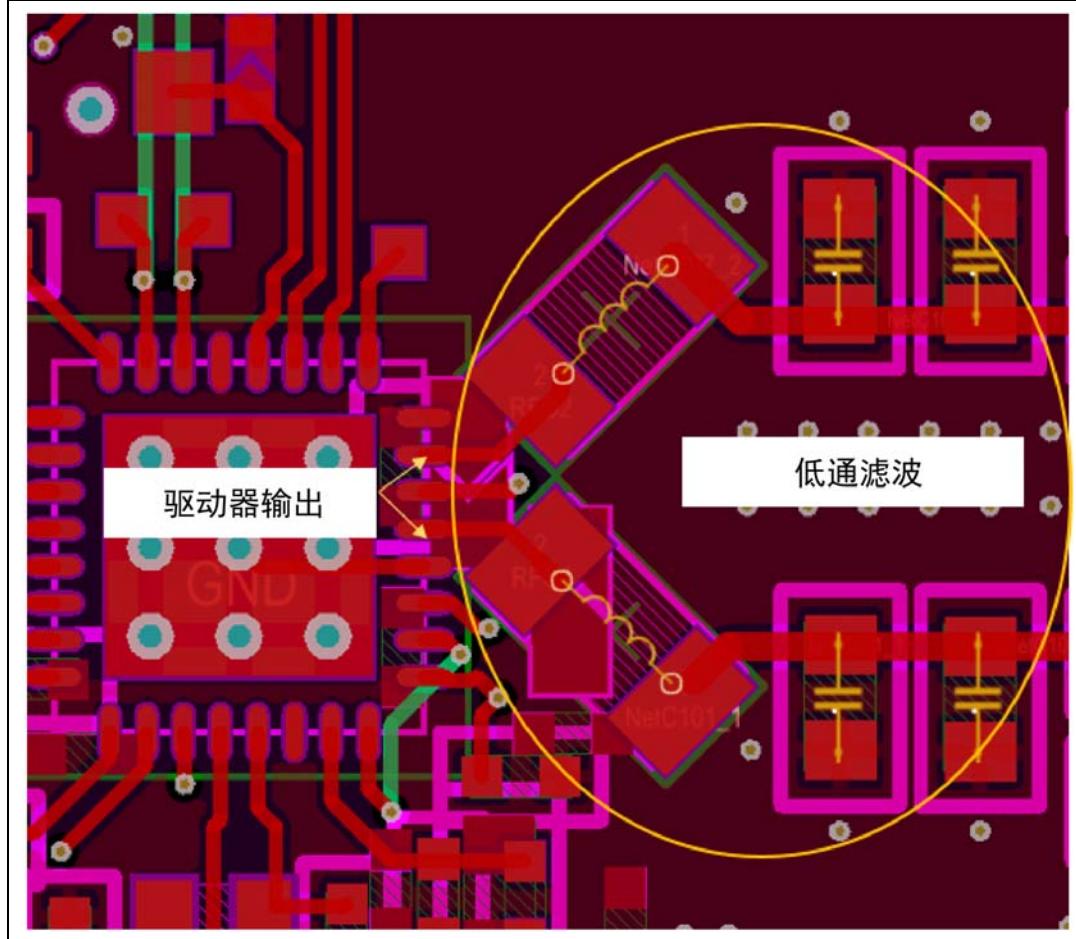

另一种减少谐波的方法是使用低通滤波来使边沿变圆。通过RF驱动器输出端的LC组合可实现上述方法，如图4所示。

图4. 低通滤波

务必在滤波器网络尽可能放置在靠近输出级的位置（如图 5 所示），以避免走线过长，产生无用辐射。

图5. 低通滤波器在PCB上的位置

## 4 走线辐射

可以在外露的走线中识别出其中一个辐射源。为了理解走线的辐射方法，必须在信号传播过程中分析信号。沿走线传播的信号可以分成两个主要部分，即差分信号和共模信号。

### 4.1 差分信号

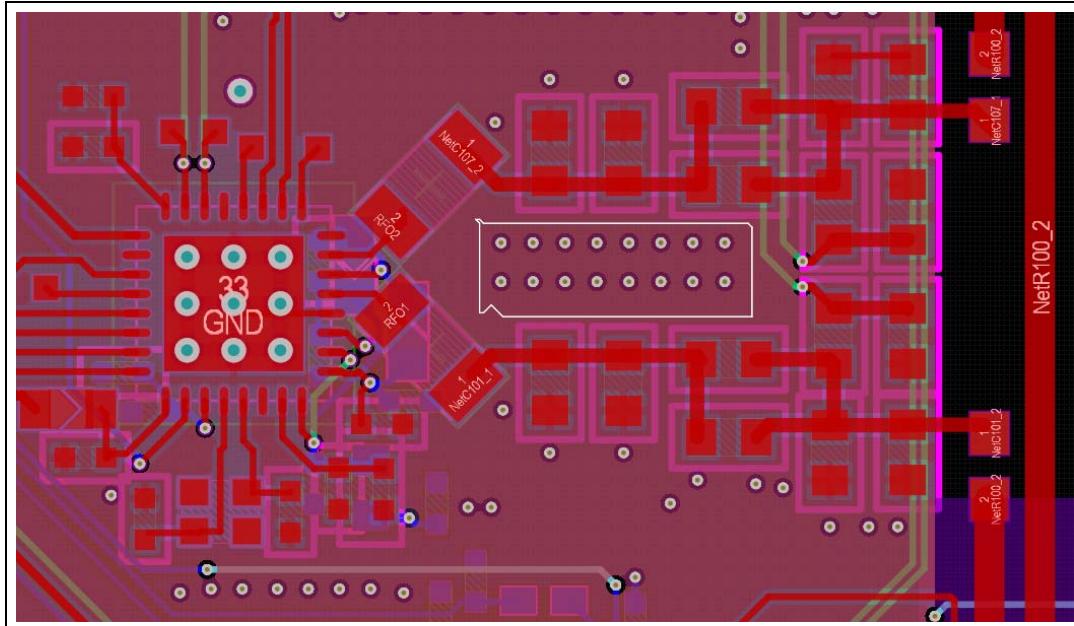

沿两条走线传播的差分信号的总辐射场趋于自身抵消，在理想条件下为零。同样的效果适用于以差分模式运行的ST25R3916输出驱动。然而，由于沿着走线的元件公差和信号不对称，可能出现电流差，从而产生非“准零”电场。因此，请注意以对称方式布局匹配拓扑。

图6. 具有对称匹配布局的ST25R3916

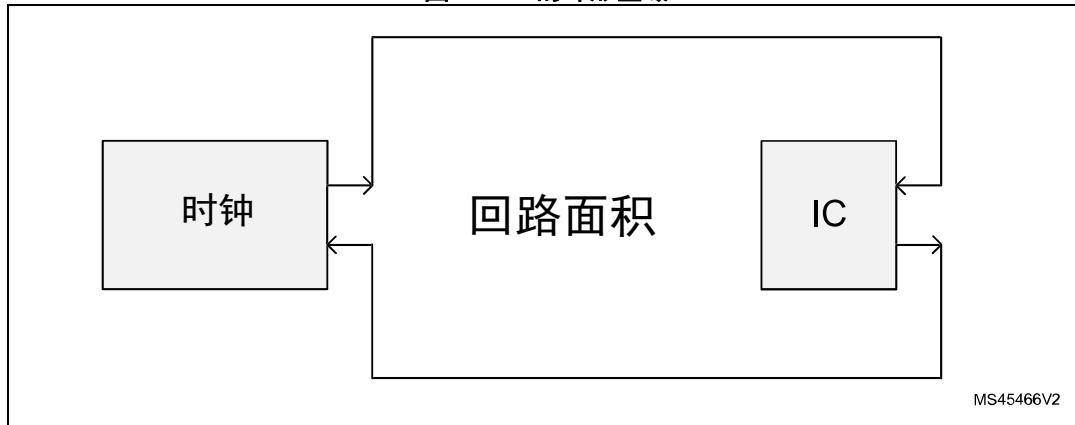

此外，为了控制差模辐射发射，务必最小化由信号走线及其电流回路形成的环形区域（参见图7）。特别是对于时钟信号，需要最小化长度，以形成尽可能小的环形区域。

图7. PCB的环形区域

#### 4.1.1 RFO和RFI布线

ST25R3916的发送和接收级为差分对，需要在PCB布局期间小心处理，以最大限度地减少无用信号耦合和辐射发射。这些信号应在内部层布线，但为了避免连接走线与匹配元件的大量通孔，完整的匹配网络放置在PCB的一侧（顶层）。返回电流将在走线下方的GND层流动。在匹配电路下方的GND层中没有切割，这一点非常重要。

图8. 匹配网络的布线

在匹配布局中应务必避免所谓的通孔，因为它们只会导致多余辐射。请注意匹配元件之间尽量靠近，以减少从RFO到天线馈线的走线长度。不建议在LC滤波器和剩余匹配元件之间使用长信号走线。RFO后的电感彼此垂直放置，以最小化耦合效应。

RFI线是对称布设的，并且与RFO线保持合理的距离。接收信号在匹配网络的中间点进行去耦，并与载波信号相对较低的串联电容交叉。切勿将RFI信号彼此分开布线，且不要使用不同的信号长度。

RFI线也可以穿过匹配网络的中间处走线至RFI引脚。

此外，沿RFO路径连接到GND的所有元件（电容）均使用多个通孔连接到GND，以最大限度地减少电感，从而避免无用的谐振。

## 4.2 共模信号

共模辐射主要来自PCB系统的连接电缆。

PCB参考接地平面的电感（以及对应的接地电压）是共模辐射的主要来源。共模辐射的产生效率高于差模辐射，即使少量的共模电流也会导致显著的发射问题。

为了减少共模发射

- 保持供电路径靠近电流回路

- 减少布线长度

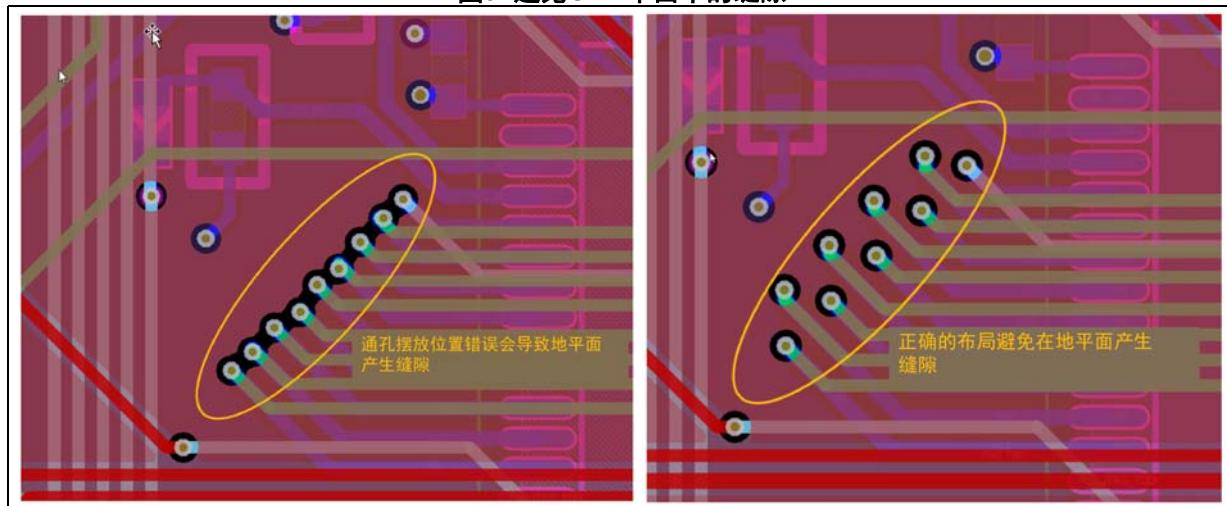

- 尽量降低共模电压（通常是接地电位）。可以通过使用完整接地平面或接地电网，以及避免接地平面中产生开槽（参见图9中的差异）来降低接地阻抗。

图9. 避免GND平面中的缝隙

注意连接线（若有），并正确屏蔽他们。例如，可以使用与其串联的共模电感来实现屏蔽，并在从封闭线到PCB接地的连接之间采取一些隔离措施。

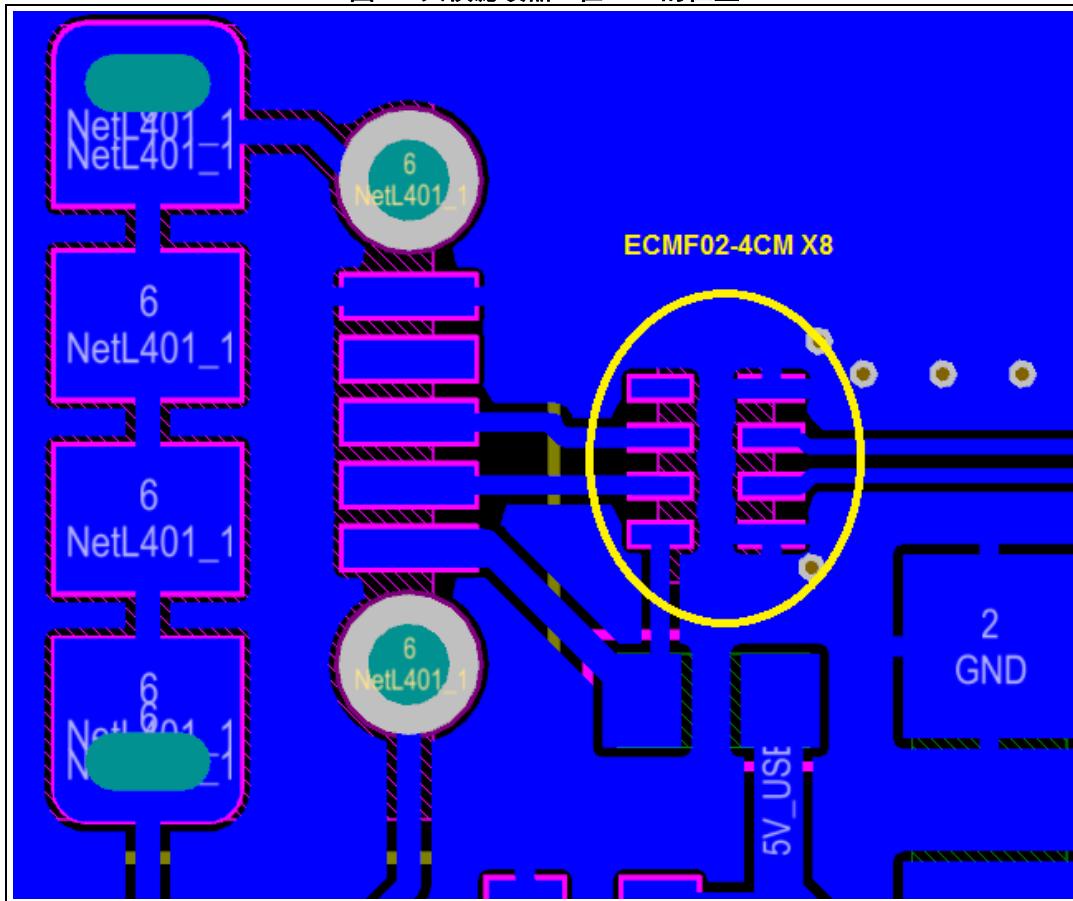

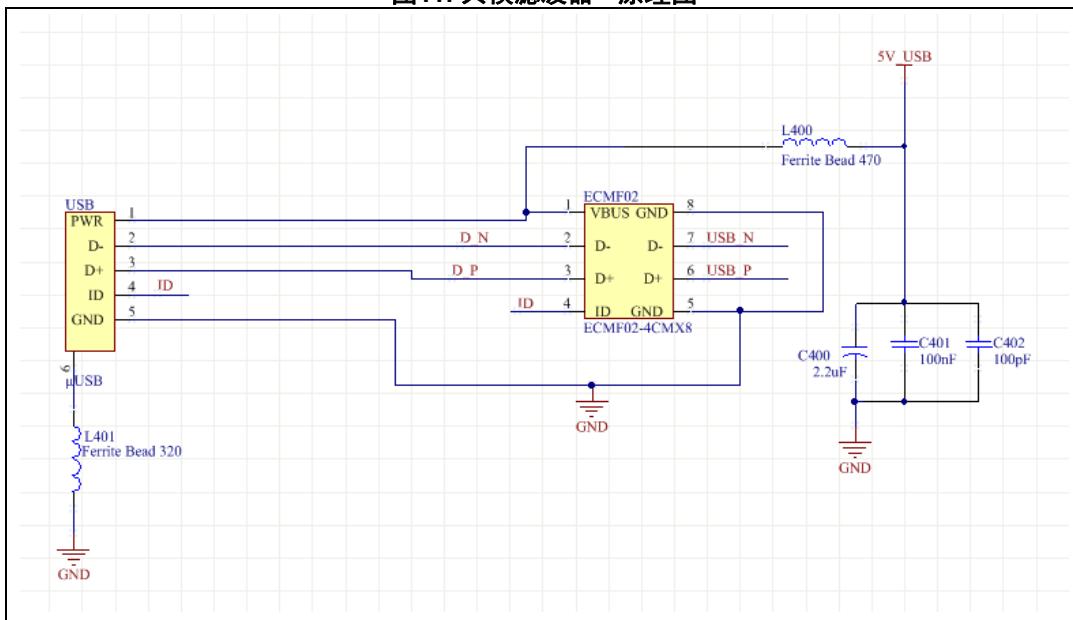

如图10和图11中示例显示的PCB和原理图，一个集成的共模滤波器（ECMF02-4CMX8）可用于USB D+和D-的线以及ESD保护。

图10. 共模滤波器 - 在PCB的位置

图11. 共模滤波器 - 原理图

#### 4.2.1 SPI数据信号布线

从ST25R3916到MCU的SPI数据信号必须尽可能以相同的长度和受控阻抗进行布线。

保持SPI接口具有较短的走线长度，并尽量减少使用通孔。

避免在晶体振荡器（例如产生27.12 MHz或13.56 MHz频率的振荡器）上进行SPI信号布线，以最大限度地减少串扰和信号失真。

## 5 寄生元件和电流回路

在PCB设计过程中，必须注意无源元件的选择及其寄生参数。

大多数情况下，元件制造商仅提供在低频率下或在与设计中所使用的频率不兼容的频率范围内的测量值。因此，设计人员必须了解设计中使用的每个无源元件在整个考虑到的频率范围内的精确值和寄生效应，以避免可能导致意外辐射效应的无用系统谐振。

需要结合寄生效应评估PCB上的电流回路。

所有电源的回流：它们以环路流动，并且回路对辐射发射有很大影响。请注意电源回流会根据频率而产生不同路径：在低频的情况下具有最低电阻的路径是最优选择，在高频范围下优先选择具有最低电感的路径。

如要了解回路电阻，通过计算带状线和PCB中微带线的阻抗，以识别具有高低阻抗的路径极为的重要。

## 6 去耦和旁路电容

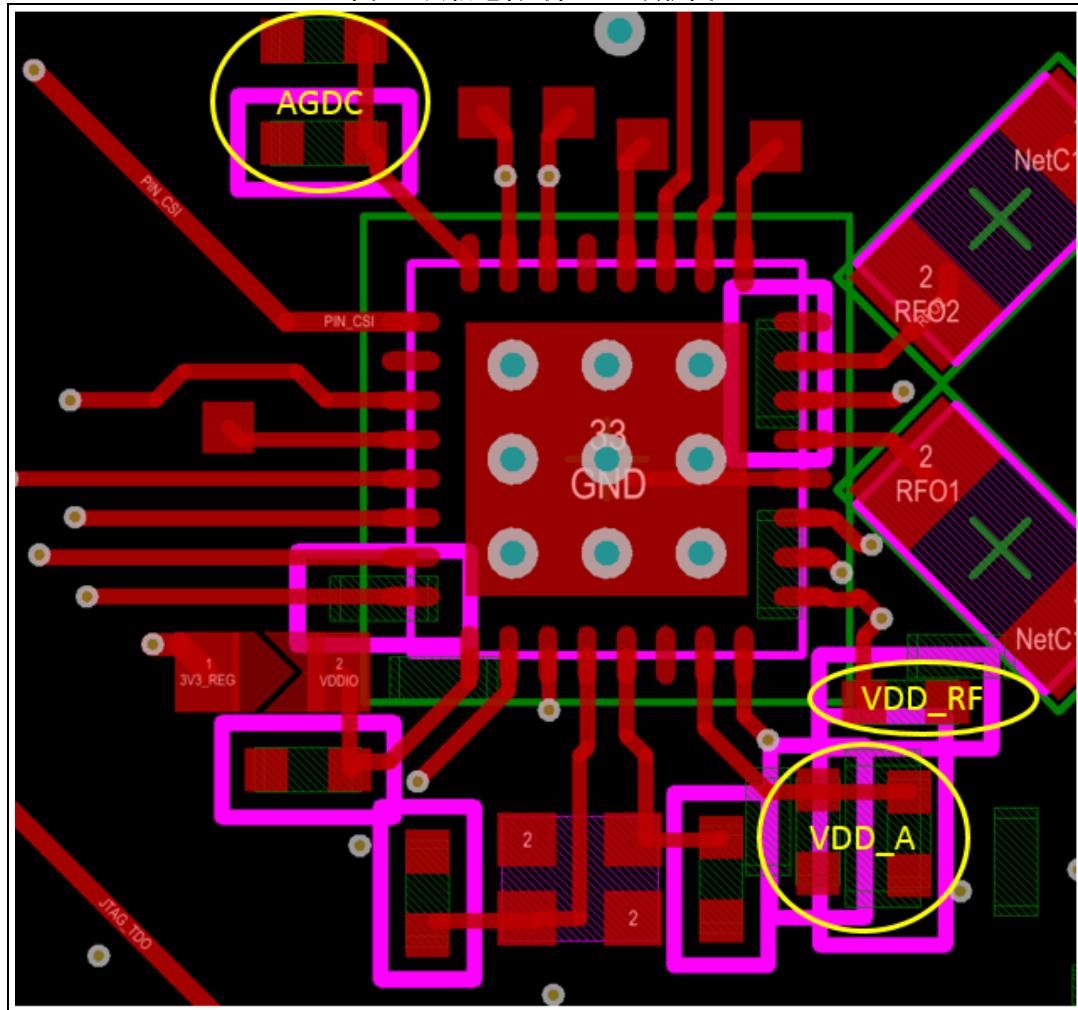

与ST25R3916稳压器和AGD电压引脚（VSP\_D、VSP\_A、VSP\_RF和AGD）相关的所有电容必须尽可能靠近芯片。

图 12 和 图 13 显示了去耦电容的典型布局，即  $2.2\mu\text{F} / 10\text{nF}$  并联组合。

图12. 去耦电容的位置（顶视图）

图13. 去耦电容的位置 (底视图)

图14. 去耦电容的原理图

## 7 供电滤波

外部噪声可以通过电源进入系统，类似地，内部噪声可以通过直流电源从电路板传导出去。建议在PCB供电系统设计中安装滤波器，以减少噪声和瞬态对线路的影响。共模和差模滤波都可应用于PCB。

ST25R3916 VDD引脚的电源由PI滤波器提供。电容的典型值为1至0.01  $\mu$ F；在所涉及的频率范围内，铁氧体磁环的典型电阻值在50至1500 $\Omega$  间（避免铁氧体磁环因直流电流而饱和）。

图15. 电源原理图详情

## 8

## 散热焊盘

ST25R3916下方的散热焊盘作为接地平面和散热器。该焊盘通过多个通孔连接到PCB接地平面，必须进行电镀以确保良好的焊接效果。多个通孔使该区域的总寄生电感保持在低水平。

图16. ST25R3916散热焊盘

## 9 混合信号PCB布局

当设计人员设计混合信号系统时，PCB布局定义中的主要问题是如何分开模拟和数字部件，以及如何处理将两个子系统之间的接地分离。

分割GND是因为需要为模拟和数字子系统保持分离的返回电流。两个子系统之间的分离可以通过两个接地（实际切割）的物理分离或通过其空间分离来实现。当使用多个具有共用GND连接的混合信号IC用于模拟和数字信号时，与单个GND配置相比，分开接地的方法可能导致更多问题。

在此情况下，建议仅使用一个电流返回平面，注意将PCB区域划分为数字和模拟区域；仅分别在模拟和数字区域中进行模拟和数字信号布线，以保持回路电流分离。

另外，使用分离的GND平面会产生其他问题，因为电源电流可能存在多个返回路径，进而可能存在电流回路。供电电流必须通过共用接地端返回，模拟和数字子系统都以此共用接地端为参考。由于存在电流环路会产生辐射，其发射电平与环路面积和电流强度成正比。

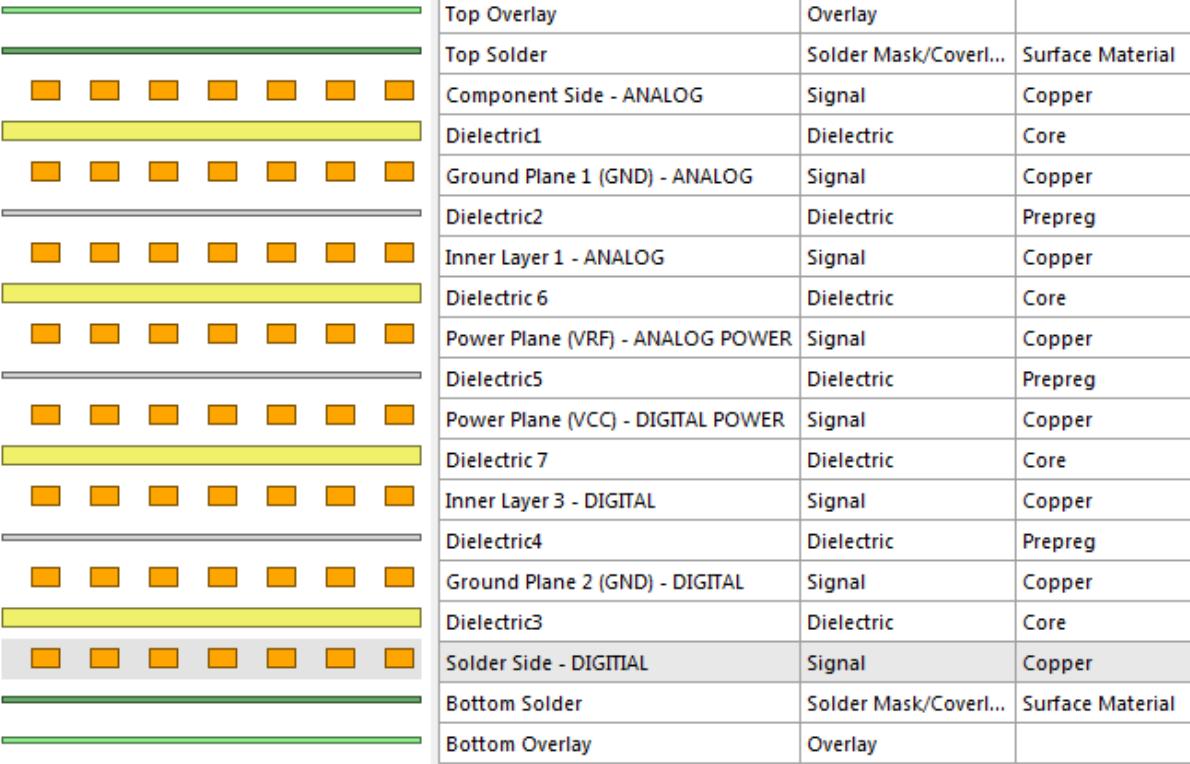

[图 17](#)显示了模拟和数字部分之间完全分离的8层PCB的典型配置。在此配置中，模拟元件放置在PCB的顶层，而数字元件放置在底层。

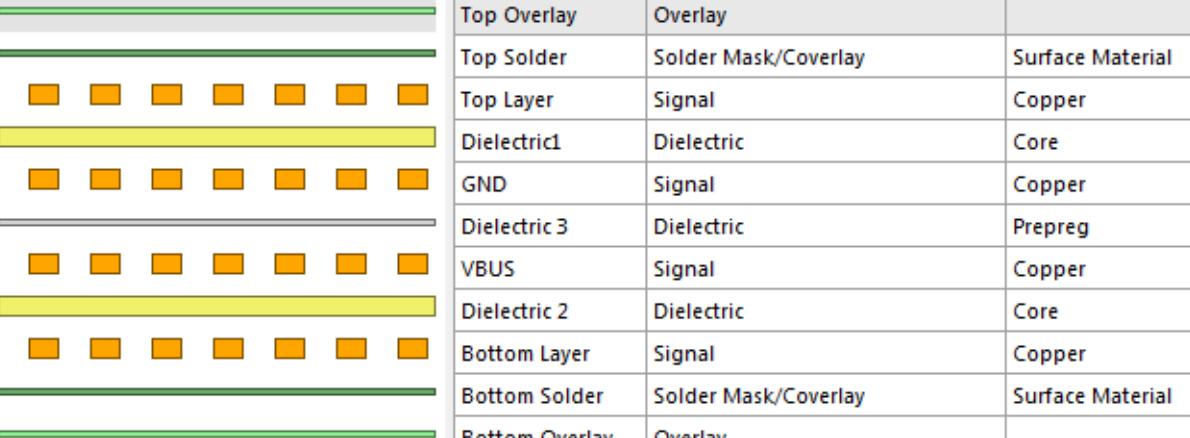

[图 18](#)是一个4层PCB层叠配置示例 信号在顶层和底层进行路由。内层由单独的GND和电源层组成。

图17. 模拟和数字信号之间的垂直分离

| Layer Name                        | Type                 | Material         |

|-----------------------------------|----------------------|------------------|

| Top Overlay                       | Overlay              |                  |

| Top Solder                        | Solder Mask/Coverlay | Surface Material |

| Component Side - ANALOG           | Signal               | Copper           |

| Dielectric1                       | Dielectric           | Core             |

| Ground Plane 1 (GND) - ANALOG     | Signal               | Copper           |

| Dielectric2                       | Dielectric           | Prepreg          |

| Inner Layer 1 - ANALOG            | Signal               | Copper           |

| Dielectric 6                      | Dielectric           | Core             |

| Power Plane (VRF) - ANALOG POWER  | Signal               | Copper           |

| Dielectric5                       | Dielectric           | Prepreg          |

| Power Plane (VCC) - DIGITAL POWER | Signal               | Copper           |

| Dielectric 7                      | Dielectric           | Core             |

| Inner Layer 3 - DIGITAL           | Signal               | Copper           |

| Dielectric4                       | Dielectric           | Prepreg          |

| Ground Plane 2 (GND) - DIGITAL    | Signal               | Copper           |

| Dielectric3                       | Dielectric           | Core             |

| Solder Side - DIGITAL             | Signal               | Copper           |

| Bottom Solder                     | Solder Mask/Coverlay | Surface Material |

| Bottom Overlay                    | Overlay              |                  |

图18. 4层PCB配置

| Layer Name     | Type                 | Material         |

|----------------|----------------------|------------------|

| Top Overlay    | Overlay              |                  |

| Top Solder     | Solder Mask/Coverlay | Surface Material |

| Top Layer      | Signal               | Copper           |

| Dielectric1    | Dielectric           | Core             |

| GND            | Signal               | Copper           |

| Dielectric 3   | Dielectric           | Prepreg          |

| VBUS           | Signal               | Copper           |

| Dielectric 2   | Dielectric           | Core             |

| Bottom Layer   | Signal               | Copper           |

| Bottom Solder  | Solder Mask/Coverlay | Surface Material |

| Bottom Overlay | Overlay              |                  |

## 10 结论

遵循本文档中说明的指导原则，可以避免在设计高功率RF系统时可能遇到的许多最常见的EMC问题和操作陷阱。

必须特别注意信号布线，以及信号所放置的PCB层。

在考虑PCB布局时，必须始终考虑PCB堆叠、元件放置、多个直流电压的处理、电流回路和通孔放置等因素。

用户请谨记，实现所需性能所需的最后一步通常在于优化的PCB布局。

## 11 版本历史

表1. 文档版本历史

| 日期              | 版本 | 变更                            |

|-----------------|----|-------------------------------|

| 2018年12月<br>20日 | 1  | 初始版本。                         |

| 2019年2月<br>26日  | 2  | 文档发布范围由意法半导体机密信息更新为意法半导体公开发布。 |

表2. 中文文档版本历史

| 日期             | 版本 | 变更      |

|----------------|----|---------|

| 2020年11月<br>3日 | 1  | 中文初始版本。 |

**重要通知 - 请仔细阅读**

意法半导体公司及其子公司（“ST”）保留随时对 ST 产品和 / 或本文档进行变更、更正、增强、修改和改进的权利，恕不另行通知。买方在订货之前应获取关于 ST 产品的最新信息。ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对 ST 产品的选择和使用，ST 概不承担与应用协助或买方产品设计相关的任何责任。

ST 不对任何知识产权进行任何明示或默示的授权或许可。

转售的 ST 产品如有不同于此处提供的信息的规定，将导致 ST 针对该产品授予的任何保证失效。

ST 和 ST 徽标是 ST 的商标。若需 ST 商标的更多信息，请参考 [www.st.com/trademarks](http://www.st.com/trademarks)。所有其他产品或服务名称均为其各自所有者的财产。

本文档中的信息取代本文档所有早期版本中提供的信息。

© 2020 STMicroelectronics - 保留所有权利