## LIS25BA: 带 TDM 接口的低噪声、高带宽 3 轴数字输出加速度计

### 引言

本文档旨在提供 ST LIS25BA 运动传感器相关的使用信息和应用提示。

LIS25BA 是一种高性能 3 轴 MEMS 加速度计，具有低噪声、高且平坦的带宽和时分复用（TDM）接口。

该器件具有 $\pm 3.85\text{ g}$  的满量程加速度范围，并能以 2400 Hz 的信号带宽测量加速度。

由于具有高带宽，LIS25BA 特别适用于可穿戴设备或智能耳机，并可以显著提高音频质量，尤其是在使用 ST MEMS 麦克风实现降噪功能的系统中。器件关键应用为骨骼振动检测、波束成形增强和语音检测增强。

LIS25BA 采用纤薄的小型塑料平面网格阵列封装(LGA)，可确保在更大的温度范围（-40 °C 至+85 °C）内正常工作。

---

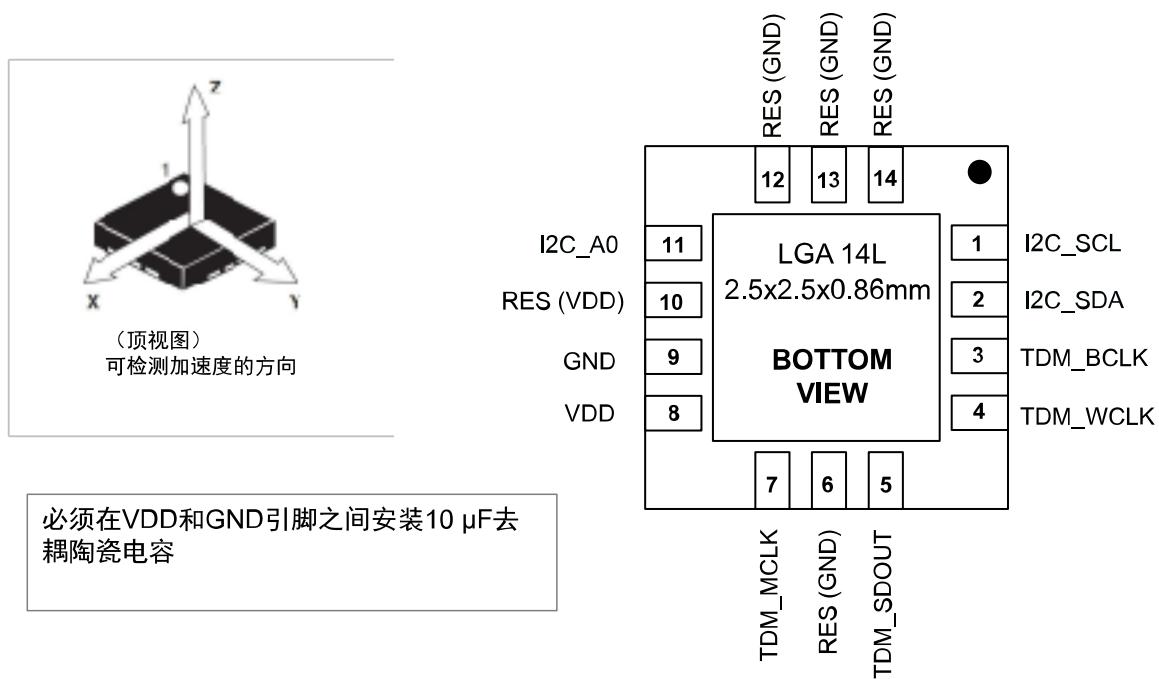

1 引脚说明

---

图 1. 引脚连接

| 引脚# | 名称        | 功能                          | 引脚状态        |

|-----|-----------|-----------------------------|-------------|

| 1   | I2C_SCL   | I <sup>2</sup> C 串行时钟- SCL  | 默认: 输入开漏    |

| 2   | I2C_SDA   | I <sup>2</sup> C 串行数据 - SDA | 默认: 输入开漏    |

| 3   | TDM_BCLK  | TDM 位时钟                     | 默认: 输入开漏    |

| 4   | TDM_WCLK  | TDM 字时钟                     | 默认: 输入开漏    |

| 5   | TDM_SDOUT | TDM 串行数据输出                  | 默认: 输入开漏    |

| 6   | RES (GND) | 与 GND 连接                    | 与 GND 连接    |

| 7   | TDM_MCLK  | TDM 主时钟                     | 默认: 输入开漏    |

| 8   | VDD       | 电源                          | 电源          |

| 9   | GND       | 0 V 电源                      | 0 V 电源      |

| 10  | RES (VDD) | 与 VDD 连接                    | 与 VDD 连接    |

| 11  | I2C_A0    | I <sup>2</sup> C 从设备地址选择    | 默认值: 带下拉的输入 |

| 12  | RES (GND) | 与 GND 连接                    | 与 GND 连接    |

| 13  | RES (GND) | 与 GND 连接                    | 与 GND 连接    |

| 14  | RES (GND) | 与 GND 连接                    | 与 GND 连接    |

## 2 寄存器

| 寄存器名          | 地址  | Bit7      | Bit6      | Bit5       | Bit4      | Bit3       | Bit2       | Bit1      | Bit0        |

|---------------|-----|-----------|-----------|------------|-----------|------------|------------|-----------|-------------|

| TEST_REG      | 0Bh | 0         | 0         | 0          | 0         | ST         | 0          | 0         | 0           |

| WHO_AM_I      | 0Fh | 0         | 0         | 1          | 0         | 0          | 0          | 0         | 0           |

| TDM_cmax      | 24h | 0         | 0         | 0          | 0         | TDM_cmax11 | TDM_cmax10 | TDM_cmax9 | TDM_cmax8   |

| TDM_cmax      | 25h | TDM_cmax7 | TDM_cmax6 | TDM_cmax5  | TDM_cmax4 | TDM_cmax3  | TDM_cmax2  | TDM_cmax1 | TDM_cmax0   |

| CTRL_REG      | 26h | 0         | 0         | PD         | 0         | 0          | 0          | 0         | 0           |

| TDM_CTRL_REG  | 2Eh | TDM_pd    | Delayed   | data_valid | mapping   | 0          | WCLK_fq1   | WCLK_fq0  | 0           |

| AXES_CTRL_REG | 2Fh | AXISZ_EN  | AXISY_EN  | AXISX_EN   | 0         | 0          | 0          | 0         | ODR_AUTO_EN |

## 3 工作模式

LIS25BA 具有两种工作模式：

- 禁用模式；

- 正常模式。

供电后，LIS25BA 执行一段 5.5 ms 的启动程序来加载修整参数。启动完成后，器件会自动配置为禁用模式。

LIS25BA 提供两种接口：

- I<sup>2</sup>C 数字接口，用于配置器件；

- TDM 接口，用于检索加速度数据。

当传感器处于禁用模式时，器件几乎所有内部模块都会关闭。I<sup>2</sup>C 数字接口保持激活，以便能够与器件进行通信。在正常模式下，可通过将 CTRL\_REG 寄存器的 PD 位置 0 来配置 LIS25BA：在正常模式下，感应链处于激活状态。

为了采集加速度输出数据，必须使能 TDM 接口。建议在使能接口前设置所有 TDM 接口时钟（MCLK、BCLK 和 WCLK）。可通过将 TDM\_CTRL\_REG 寄存器的 TDM\_pd 位置 0 来使能 TDM 接口。

### 3.1 TDM 接口配置

TDM 接口可通过 TDM\_CTRL\_REG 寄存器进行配置。

表 1. TDM\_CTRL\_REG (2Eh)

| b7     | b6      | b5         | b4      | b3 | b2       | b1       | b0 |

|--------|---------|------------|---------|----|----------|----------|----|

| TDM_pd | Delayed | data_valid | mapping | 0  | WCLK_fq1 | WCLK_fq0 | 0  |

- TDM\_pd:** TDM 使能。如果 TDM\_pd 位置 0，则 TDM 接口使能，否则禁用。

- Delayed:** TDM 延迟配置。如果 Delayed 位置 0，则 TDM 使用“不延迟”配置，否则使用“延迟”配置。选择“不延迟”配置时，在 WCLK 上升沿后的第一个上升/下降沿进行 SLOT0 数据采样（基于 data\_valid 位的值，如下文所述）；选择“延迟”配置时，在 WCLK 上升沿后的第二个上升/下降沿进行 SLOT0 数据采样。

- data\_valid:** TDM 数据有效配置。如果 data\_valid 位置 0，在位时钟（BCLK）的上升沿进行数据采样，否则在下降沿进行采样。

- mapping:** TDM 映射配置。如果 mapping 位置 0，分别在 SLOT0、SLOT1 和 SLOT2 中映射加速度计 X-Y-Z 数据，否则在 SLOT4、SLOT5 和 SLOT6 中映射。在未激活插槽的转换过程中，TDM\_SDOUT 引脚配置为高阻抗。

- WCLK\_fq:** TDM 时钟频率，下一节所述。

LIS25BA 为 TDM 接口提供了四种可能的配置：下表总结了与支持的每种 TDM 配置相关的 Delayed 和 data\_valid 配置。

表 2. TDM 配置

| Delayed | data_valid | TDM 配置                         |

|---------|------------|--------------------------------|

| 0       | 0          | WCLK 上升沿后 BCLK 的第一个上升沿上的 SLOT0 |

| 0       | 1          | WCLK 上升沿后 BCLK 的第一个下降沿上的 SLOT0 |

| 1       | 0          | WCLK 上升沿后 BCLK 的第二个上升沿上的 SLOT0 |

| 1       | 1          | WCLK 上升沿后 BCLK 的第二个下降沿上的 SLOT0 |

### 3.2 TDM 时钟频率

WCLK 信号的功能是识别帧的开始，特别是始于 WCLK 信号上升沿的帧。支持的 WCLK 宽度为：

- 16-slot 宽度（1024 个 BCLK 周期，50% 占空比）；

- 1-slot 宽度 (16 个 BCLK 周期) ;

- 1 个 BCLK 周期。

在 TDM 模式下, LIS25BA 可通过 TDM\_SDOUT 引脚以下列采样频率输出加速度计数据:

- WCLK = 8 kHz;

- WCLK = 16 kHz;

- WCLK = 24 kHz。

可以用两种不同的方式选择 TDM 时钟频率:

- 使用 TDM\_CTRL\_REG 寄存器的 WCLK\_fq[1:0]位。这种情况下, 必须将 AXES\_CTRL\_REG 寄存器的 ODR\_AUTO\_EN 位置 0。WCLK\_fq 位的可用配置如下:

- 00b: 采样频率等于 8 kHz;

- 01b: 采样频率等于 16 kHz;

- 10b: 采样频率等于 24 kHz。

- 使用将 MCLK 和 WCLK 作为输入接收的 ODR\_auto 功能块的输出 (如 LIS25BA 数据手册中所述), 按 MCLK 与 WCLK 之比计算当前采样频率。可通过将 AXES\_CTRL\_REG 寄存器的 ODR\_AUTO\_EN 位置 1 使能 ODR\_auto 功能块。根据 WCLK\_fq[1:0]位的值, 可能的 ODR\_auto 功能块输出如下:

- 00: 采样频率等于 8 kHz (MCLK/WCLK = 1536);

- 01: 采样频率等于 16 kHz (MCLK/WCLK = 768);

- 10: 采样频率等于 24 kHz (MCLK/WCLK = 512)。

注意: 如果 MCLK 与 WCLK 之比不是 1536、768 和 512, 则自动将采样频率强制为 8 kHz。

串行时钟 BCLK 的唯一目的是将数据移出 TDM\_SDOUT 串行端口。为此, TDM 接口使用一个内部计数器, 该计数器在检测到 WCLK 的上升沿时置为 1, 在达到 WCLK 周期中的最大 BCLK 数量时重置为 0。

WCLK 周期中包含的最大 BCLK 数量 (即 cmax) 可表示为 BCLK 和 WCLK 频率的函数, 并且可使用以下等式进行计算:

$$c_{\text{最大}} = \frac{BCLK}{WCLK} - 1$$

为了支持范围[1024 MHz, 12.288 MHz]内的串行时钟 BCLK 变量, 从而计算内部 TDM 计数器的正确最大值, 有两种可能的解决方案可供选择:

- cmax 值是 TDM 接口的输入, 设备可以自动计算。此功能默认使能, 可通过将 AXES\_CTRL\_REG 寄存器的 ODR\_AUTO\_EN 位置 0 进行禁用。

- 可通过寄存器 TDM\_cmax 设定 TDM cmax。

### 3.3 轴禁用

在 TDM 模式下, 为了减少工作期间的功耗, 主机处理器可以通过解除 AXES\_CTRL\_REG 寄存器中 AXISX\_EN、AXISY\_EN 或 AXISZ\_EN 位的置位选择性地关断每个 LIS25BA 加速度计轴。当轴被关断时, 相应的 TDM 插槽将处于高阻抗状态。

数据手册提供了每种模式 (单轴、双轴或三轴模式) 的典型和最大电流消耗。

### 3.4 配置切换

必须从 I<sup>2</sup>C 接口明确地激活 TDM 接口。必须丢弃使能 TDM 接口后的前 3 个采样: 这是因为接口同步外部 WCLK。此外, 可以动态地重新配置 TDM 协议, 但在这种情况下, TDM 配置变化后的前 3 个采样也将无效。

## 4 读取输出数据

### 4.1 启动序列

当器件上电时，器件会自动从内嵌的内存中加载校准系数到内部寄存器中。启动程序完成后，加速度计会自动进入禁用模式。

要启动加速度计并通过 TDM 接口采集加速度数据，必须通过 **CTRL\_REG** 寄存器的 **PD** 位选择“正常”工作模式，并通过 **TDM\_CTRL\_REG** 的 **TDM\_pd** 位使能 TDM 接口。

以下通用时序可用来配置加速度计：

1. 写入 **CTRL\_REG** = 00h // 正常模式

2. 为 TDM 接口提供 MCLK、BCLK 和 WCLK

3. 写入 **TDM\_CTRL\_REG** = 0xxx0000b // TDM 使能和配置选择

4. 等待 4.5 ms // 等待导通时间结束

5. 开始从 TDM 接口采集加速度数据

### 4.2 理解输出数据

测得的加速度数据会发送至通过 **TDM\_CTRL\_REG** 寄存器映射位配置的 TDM 接口插槽。

加速度输出数据表示 16 位二进制补码格式的数字。

从 TDM 接口的激活插槽检索到此数据后，必须通过乘以数据手册中提供的灵敏度值将加速度数据转换为 **mg** 值：0.122 mg / LSB（典型值）。

#### 4.2.1 输出数据示例

下表提供了加速度计数据的几个基本示例，这些数据是在器件受给定加速度影响时从 TDM 输出插槽读取的。

下表中所列值是在理想器件校准的假设下给出的（即，无偏移，无增益误差，...）。

| 加速度值[ <b>mg</b> ] | LSB (十六进制) | LSB (有符号十进制) |

|-------------------|------------|--------------|

| 0                 | 0000h      | 0            |

| 350 mg            | 0B34h      | 2868         |

| 1000 mg           | 2004h      | 8196         |

| -350 mg           | F44Ch      | -2868        |

| -1000 mg          | DFFCh      | -8196        |

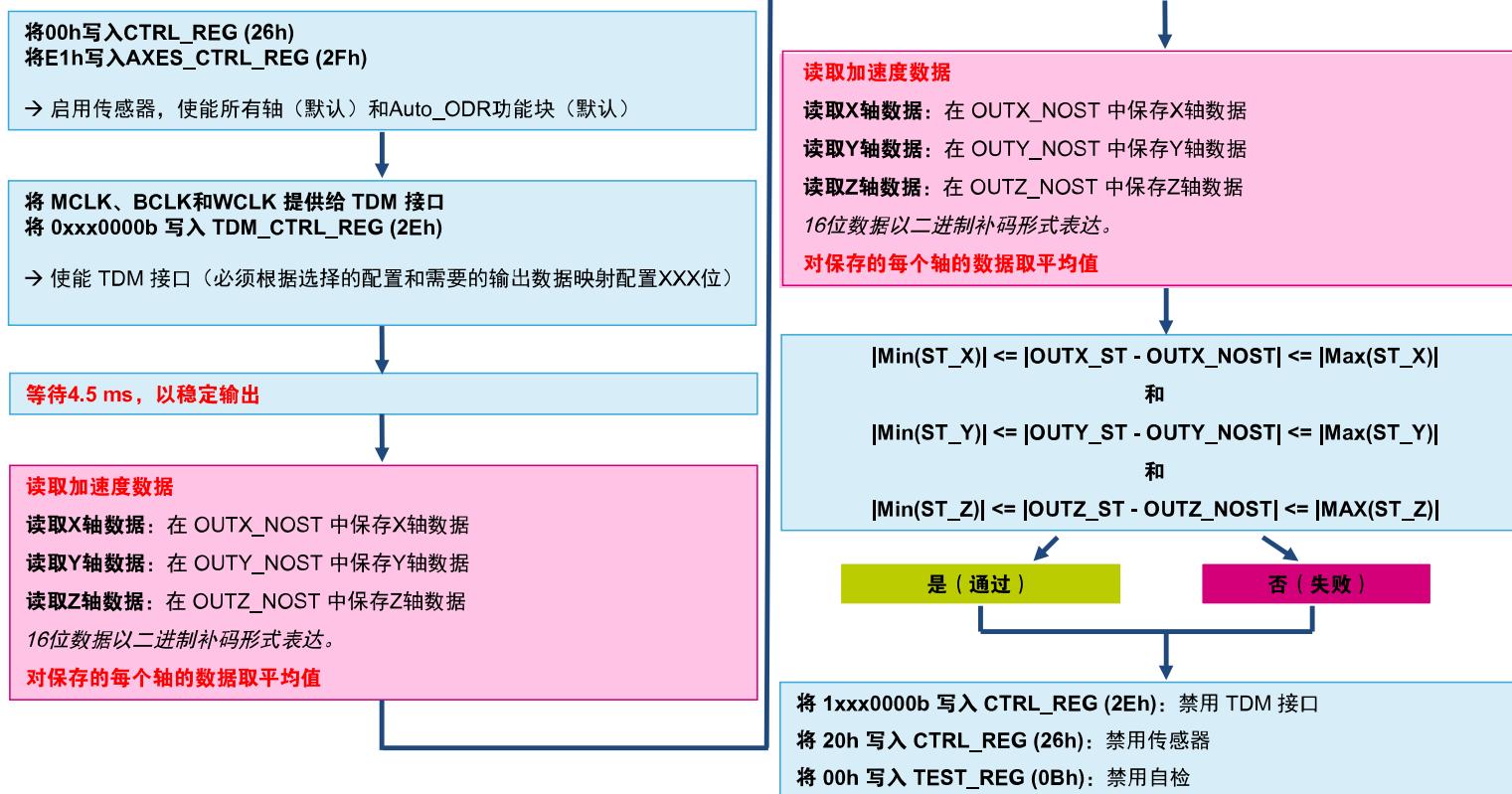

## 5 自检功能

嵌入式自检功能可支持无需移动器件而对其功能进行检查。

当自检使能时，传感器上会施加一个驱动力，模拟一定的输入加速度。这种情况下，传感器输出会在其 DC 电平上表现出变化，该电平通过灵敏度值关联到量程。

加速度计自检功能可通过 TEST\_REG 寄存器的 ST 位进行配置：当 ST 位置 0 时，自检功能关闭；当 ST 位置 1 时，该功能使能。

当加速度计自检功能激活时，传感器的输出由作用在传感器上的加速度和静电测试力的代数和给出。

该过程包括：

1. 使能加速度计和 TDM 接口；

2. 启动自检之前，对 5 个采样取平均；

3. 启动自检之后，对 5 个采样取平均；

4. 计算每个轴的绝对值差值，并验证它是否落在给定的范围内。数据表中给出了最小和最大值。

完整的自检过程如图 2. 加速度计自检步骤中所示。

图 2. 加速度计自检步骤

注：自检过程中请保持器件稳定

- I<sup>2</sup>C 接口

- TDM 接口

## 版本历史

表 3. 文档版本历史

| 日期              | 版本 | 变更   |

|-----------------|----|------|

| 2018 年 5 月 24 日 | 1  | 初始版本 |

## 目录

|            |                 |               |          |

|------------|-----------------|---------------|----------|

| <b>1</b>   | <b>引脚说明</b>     | <b>2</b>      |          |

| <b>2</b>   | <b>寄存器</b>      | <b>5</b>      |          |

| <b>3</b>   | <b>工作模式</b>     | <b>6</b>      |          |

| <b>3.1</b> | <b>TDM 接口配置</b> | <b>6</b>      |          |

| <b>3.2</b> | <b>TDM 时钟频率</b> | <b>6</b>      |          |

| <b>3.3</b> | <b>轴禁用</b>      | <b>7</b>      |          |

| <b>3.4</b> | <b>配置切换</b>     | <b>7</b>      |          |

| <b>4</b>   | <b>读取输出数据</b>   | <b>8</b>      |          |

| <b>4.1</b> | <b>启动序列</b>     | <b>8</b>      |          |

| <b>4.2</b> | <b>理解输出数据</b>   | <b>8</b>      |          |

|            | <b>4.2.1</b>    | <b>输出数据示例</b> | <b>8</b> |

| <b>5</b>   | <b>自检功能</b>     | <b>9</b>      |          |

|            | <b>版本历史</b>     | <b>11</b>     |          |

重要通知 - 请仔细阅读

意法半导体公司及其子公司（“ST”）保留随时对 ST 产品和/或本文档进行变更、更正、增强、修改和改进的权利，恕不另行通知。买方在订货之前应获取关于 ST 产品的最新信息。ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对 ST 产品的选择和使用，ST 概不承担与应用协助或买方产品设计相关的任何责任。

ST 不对任何知识产权进行任何明示或默示的授权或许可。

转售的 ST 产品如有不同于此处提供的信息的规定，将导致 ST 针对该产品授予的任何保证失效。

ST 和 ST 标志是 ST 的商标。关于 ST 商标的其他信息，请访问 [www.st.com/trademarks](http://www.st.com/trademarks)。其他所有产品或服务名称是其各自所有者的财产。

本文档中的信息取代本文档所有早期版本中提供的信息。

© 2019 STMicroelectronics - 保留所有权利