---

## STM32MP1 系列 MPU 的 DDR 配置

### 前言

本文档描述在 STM32MP1 系列 MPU 上配置 DDR 子系统 (DDRSS) 所需的流程和步骤。

通过设定 DDR 控制器 (DDRCTRL)、PHY 接口 (DDRPHYC) 和 SDRAM 模式寄存器的多个参数和设置完成 DDRSS 配置。根据 DDR 类型、DDR 大小、DRAM 拓扑、运行时间频率和 SDRAM 器件数据手册参数确定这些参数。所有这些参数必须在初始化序列期间设定。

STM32CubeMX DDR 测试套件使用直观的面板和菜单隐藏了与确定正确参数和初始化启动相关的复杂性 (请参考[6])。为了快速设置要运行的 DDRSS，用户只需提供很少几个输入即可完成配置。可以使用一些高级用户模式和特殊功能 (当它们对于应用而言十分重要时)。

在系统启动阶段，为了优化时序裕量，支持多种 PHY 调谐。可以使用 STM32CubeMX 启动这些调谐。PHY 调谐结果可以保存并在后续冷复位时恢复。

在启动阶段，用户可以运行大量测试套件。这些测试可以使用 STM32CubeMX 启动，并用于确认 DDR 配置的稳健性。

### 参考

- [1] STM32MP1 系列参考手册

- [2] JEDEC JESD79-3F DDR3 SDRAM 标准

- [3] JEDEC JESD209-2F LPDDR2 SDRAM 标准

- [4] JEDEC JESD209-3C LPDDR3 SDRAM 标准

- [5] STM32MP1 系列 DDR 存储器路由指南 (AN5122)

- [6] 用于 STM32MP1 系列的 STM32CubeMX

- [7] DDR-PHY 接口 (DFI) (<http://www.ddr-phy.org>)

## 1 概述

本文档适用于 STM32MP1 系列基于 Arm® 的 MPU。

提示 *Arm* 是 **Arm Limited** (或其子公司) 在美国和/或其他地区的注册商标。

## 2 DDR 子系统初始化和配置

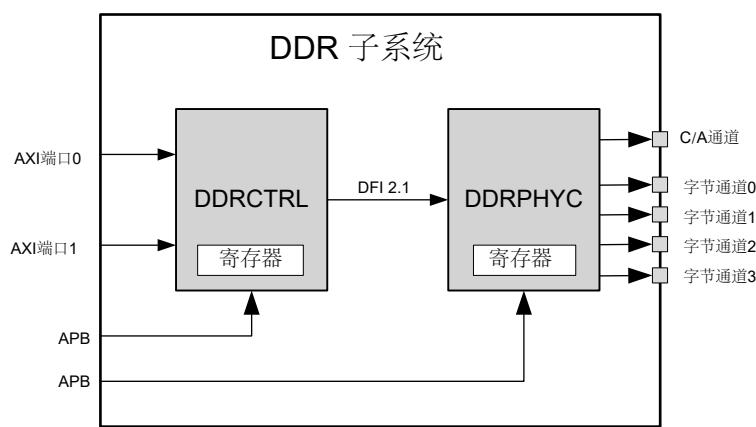

DDR 子系统包括 DDRCTRL 和 DDRPHYC (参见下图)。

DDRCTRL 支持在正常操作期间通过命令和刷新调度进行 DDR 命令调度。

DDRPHYC 是一种 DDR PHY 接口，具有连接 DDRCTRL 的 DFI 接口[7]和字节通道架构，适合连接频率不超过 533 MHz 的 DDR3/3L 和 LPDDR2/3。

DDRPHYC 完全支持具有多个 PHY 调谐选项 (内置) 的 DDR 初始化。DDRPHYC 包含 BIST 引擎，用于支持软件驱动的调谐。

图 1. DDR 子系统

### 2.1 DDRSS 和 SDRAM 初始化

器件根据 SDRAM 启动序列对电源、时钟和复位进行内部排序。

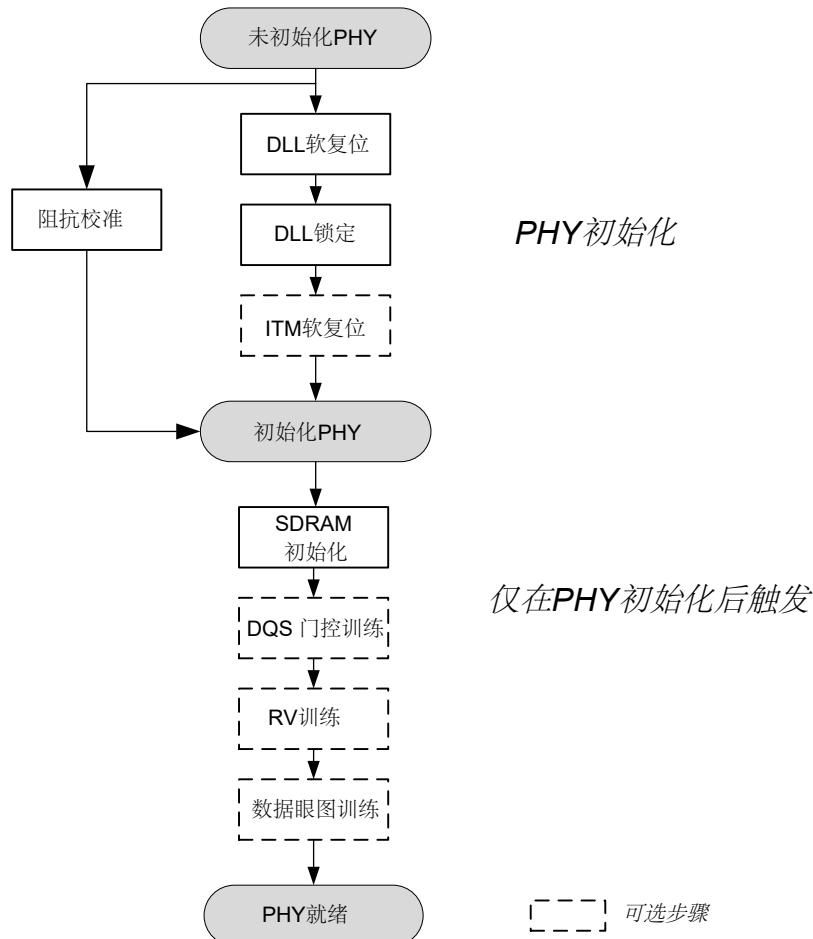

图 2 所示的 PHY 初始化序列由 DDRPHYC 物理实用模块 (PUB) 控制。这一基于 PUB 的初始化序列在 DDRPHYC 从复位状态释放后启动，并根据 DDRPHYC.PIR 寄存器进行排序。

初始化序列包括以下步骤：

1. DDRCTRL 和 DDRPHYC 初始化包括内部时序模块 (ITM) 复位以及 DLL 复位和锁定

2. DDRPHYC I/O 初始校准 (ZCAL)，与 DLL 锁定同时启动

3. 通过模式寄存器写入和校准命令执行 SDRAM 初始化

4. 内置 DQS 门控训练 (DQSTRN)

#### 提示

- 在 SSTL 模式下为所有 SDRAM 设置 DDRPHYC I/O。

- DQS 门控训练是可选的。但是，建议在每次初始化时运行内置 DQS 门控训练。

图 2. DDRPHYC 初始化序列

## 2.2 DDRCTRL 配置

大多数 DDRCTRL 寄存器是静态的，并在 DDRCTRL 从复位状态释放和 AXI 端口使能前加载。这是在 DDR 软件驱动器的支持下实现的。

在 DDRPHYC 和 DDCTRL 完成初始化后，DDR 子系统就绪，使能 AXI 端口是最后一个步骤。

通过从 STM32CubeMX DDR 面板选择的菜单/选项提供的极少信息确定 DDRCTRL 和 DDRPHYC 寄存器的配置。

然后，DDRSS 配置被保存并恢复到 DDRCTRL 和 DDRPHYC 寄存器，用于后续的复位和正常操作。

## 2.3 DDR 配置

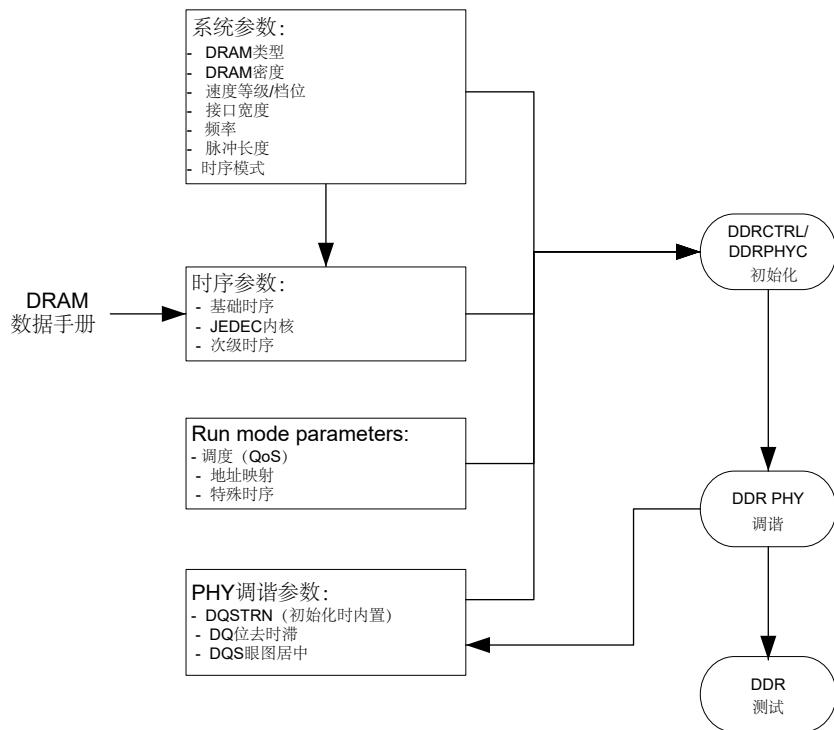

配置 DDR 所需的步骤如下：

1. 为 DDRCTRL 和 DDRPHYC 寄存器确定并设定合适值。

2. 启动 DDRCTRL 和 DDRPHYC 初始化序列。

3. 启动具有参数保存和恢复功能的 DDR 调谐（可选）。

4. 启动 DDR 测试（可选）。

完整配置流程和参数如下图所示。

图 3. DDR 初始化序列

按照第 3 节 配置参数中的类型描述配置参数。

## 2.4 DDR PHY 调谐

除了使用强制 DQS 门控训练 (DQSTRN) 确定读脉冲期间 DQS 门控的最佳位置, DDRPHYC 还支持两种读取时序优化, 即 PHY 调谐。

以下从 STM32CubeMX 驱动的软件例程支持 PHY 调谐, 以优化读时序裕量:

- DQS 门控训练 (可在 DDR PHY 调谐期间以交互方式启动的软件)

- DQ 位去时滞, 以补偿 DQ 位通道读取延迟

- DQS 眼图居中, 用于调节 DQS/DQS#延迟以实现最佳 DQ 采样

建议在系统初启阶段进行 PHY 调谐。为每个字节通道执行调谐。由于 PHY 调谐时间可能较长 (几十秒), 必须为后续复位和 PHY 初始化 (例如, 在冷复位和待机退出时) 保存和恢复调谐参数。更多详细信息, 请参见第 3.4 节 PHY 调谐。

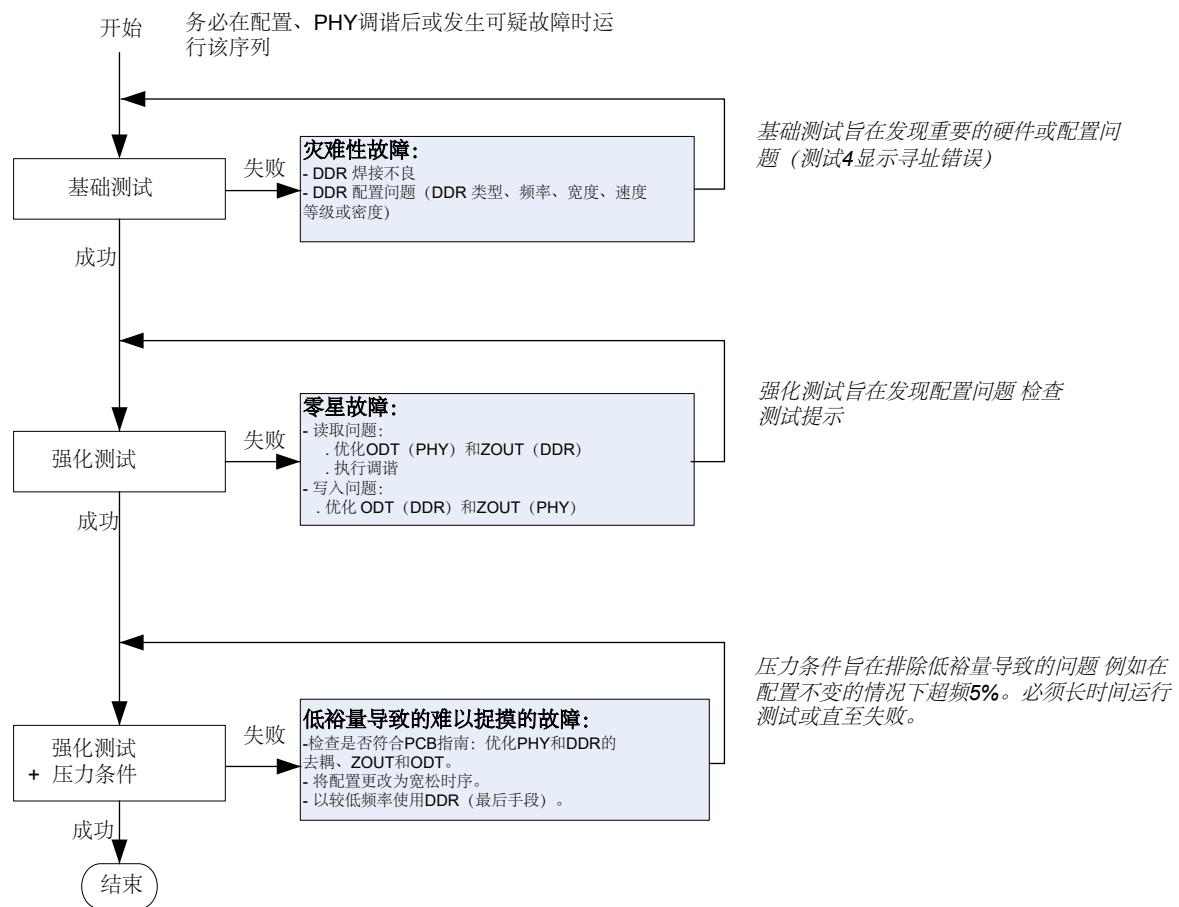

## 2.5 DDR 测试

在配置 DDR 并为优化时序调谐 PHY 后, 必须通过运行从 STM32CubeMX 启动的大量测试序列检查配置的稳健性。

在初启阶段使用 DDR 之前, 必须运行 STM32CubeMx 建议的所有测试和级别。

第 8 节 STM32CubeMX 的 DDR 测试中描述了 DDR 测试和测试流程, 以及故障诊断和处理措施。

DDR 子系统初启在 DDR 配置、调谐和压力测试成功后完成。保存配置参数用于正常运行模式初始化和 DDR run 模式。

## 3 配置参数

DDR 配置参数（无论适用于 DDRCTRL 还是 DDRPHYC）可分为以下几组：

- 系统参数：DDR 类型（DDR3/LPDDR2/3）、总线宽度（16 位/32 位）、时钟频率和密度。脉冲长度和时序模式取决于系统配置并由 STM32CubeMX 设置，用户只需在 DDR 配置面板中输入几个必填项。

- 时序参数，根据 DDR 时钟频率和 SDRAM 数据手册确定。该组包括以下参数：

- 基础时序

- JEDEC 内核时序

- 次级时序

- 运行模式和特殊参数，与性能调度、刷新时序和地址映射有关。从配置面板上推荐给用户的预定义设置中选择这些参数。STM32CubeMX DDR 配置提示了一些参数和选项（例如，设置特定模式或扩展温度支持）。

- PHY 调谐参数，与在初始化期间使用一些 PHY 内置模块或执行的软件序列确定的 PHY 时序有关。该组包括以下参数：

- DQS 门控训练（DQSTRN）

- DQ 通道位去时滞细步长延迟

- DQS 眼图居中细步长延迟

PHY 调谐结果可通过 STM32CubeMx 进行保存和恢复。更多详细信息，请参见[1]。

### 3.1 系统参数

大多数参数来自 STM32CubeMX 的引脚排列和时钟配置。DDR 面板上的用户选项用于选择下列参数：

- DDR 类型（DDR3/3L、LPDDR2 或 LPDDR3）

- 总线宽度（16 位或 32 位）

- DDR 密度（1、2、4、8 Gb）

STM32CubeMX 相应地更新了 DDR 接口焊球布局，强调了要连接到 SDRAM 的物理焊球。

按如下方式确定 DDR 拓扑选项：

- 两个16 位 BGA DDR3 以 fly-by 拓扑连接，并端接 RTT，实现 32 位DDR3。

- 对一个 16 位 BGA 进行点到点连接，实现16 位 DDR3。

- LPDDR2/3 为 16 或 32 位（通常为 32 位），采用点到点连接。

### 3.2 时序参数

STM32CubeMX 根据 DDR 频率和从配置面板菜单选择的 SDRAM 数据手册确定所有时序参数。

这些参数被加载到 DDRCTRL 和 DDRPHYC 寄存器中。DDRCTRL 使用时序参数进行命令调度。DDRPHYC 在 DRAM 初始化序列和模式寄存器加载期间会用到多个参数，并使用参数控制内置 DQS 门控训练（DQSTRN）序列。

DDR 时序分为多个不同的组，详情见下文。

#### 3.2.1 基础时序

基础时序是指标准时序三元组。以 DDR-1066 为例，

常用的值为 8-8-8、7-7-7 或 6-6-6。

#### 3.2.2 JEDEC 内核时序

JEDEC 内核时序因 DRAM 类型而异（请参考第 5 节、第 6 节 和 第 7 节 了解关于特定 SDRAM 类型的详细信息）。应谨慎使用典型数据手册或 JEDEC 表格中的这些时序，并且可以根据实际数据手册替换它们。

DDRCTRL 使用这些参数限制命令调度。

配置期间推荐以下两种时序模式：

- 最佳化时序模式，其中的时序是根据 DRAM 数据手册和时钟频率直接计算的。

- 宽松时序模式，所有严格内核时序以 1 个时钟周期的步长递增，以便在具体数据手册参数不确定时改善时序裕度。

### 3.2.3 次级时序

DDRCTRL 有大量要保存的寄存器和位字段，它们用于其时序行为的编程。

有多个 DRAM 特定的可编程次级参数（例如 ODT 时序位置），但它们均配置为默认值或预定义值且不得修改。

通过 STM32CubeMX 配置的次级参数如下：

- 刷新控制参数

- ZQ 控制

- ODT 控制

- 初始化时序（每种 DDR 类型使用的默认值）

## 3.3 运行模式参数

这些参数用于控制后面几节中列出的 DDRCTRL 功能和优化技巧。

### 3.3.1 低功耗模式设置

低功耗功能由 DDRCTRL 控制（例如，自动自刷新进入，参见[1]了解详细信息）。低功耗模式也可以从 RCC（复位和时钟控制）或软件（软件自动复位）进行控制。更多详细信息，请参见[1]。

### 3.3.2 地址映射

DDRCTRL 具有灵活的地址映射器，用于将 AXI 总线地址转换为 DRAM 存储行、区和列。

以下两种配置由 STM32CubeMX 预先确定：

- B/R/C（区/行/列），功耗最低

- R/B/C（行/区/列），最常见

#### 提示

DDRCTRL 的灵活地址映射器可以将各个 R/B/C 位映射到几乎任何序列中。确定相应的 ADDRMAP 寄存器并非易事。请参考[1]中的 DDRCTRL 部分获取详细信息。

### 3.3.3 QoS（服务质量）和调度

DDRCTRL 调度 DDR 命令，通过对 16 入口读取命令缓冲区和 16 入口写入命令缓冲区发出的输入命令进行读/写命令分组和调度存储区激活实现其最佳应用。这些缓冲区由内容可寻址存储区（CAM）构成。

DDRCTRL 根据已编程的设置，使用高级多层次仲裁方案实现 DDR 的最佳应用和低延迟。

DDRCTRL 具有一组丰富的仲裁政策和优化技巧，例如页面打开/关闭政策、流量映射到类和超时或调度器和端口仲裁控制。

根据流量分类和某些流量分类的超时设置确定命令仲裁。

DDRCTRL 通过优先级和/或超时（可以为每个 AXI 端口 0 和端口 1 分别设定）将输入 AXI 端口事务映射到流量分类。

对于读操作，有下列三个类别：

- HPR：将高优先级分配给存储，适合对延迟敏感的流量

- VPR：超时结束具有最高优先级，适合对延迟要求严格的流量

- LPR：优先级较低，适合尽力而为流量

对于写操作，有下列两个类别：

- VPW：超时结束具有最高优先级，适合对延迟要求严格的流量

- NPW：正常优先级，适合尽力而为流量

STM32CubeMX 推荐与 AXI 互联的端口分配和 QoS 设置相一致的预定义配置（请参考[1]了解详细信息）。

默认对每台主设备使用固定数量的 QoS 值。除将 LTDC 映射到端口 1 和主端口 QoS 之外，AXI 互联矩阵（AXIM）将所有主设备映射到端口 0，如下表所示。

表 1. 总线主设备 AXI 端口分配和 QoS 值

| 总线主设备 | 读/写 | 使用的端口 | 默认 QoS | 流量类别  | 读/写 QoS 区域 |

|-------|-----|-------|--------|-------|------------|

| CPU   | 读/写 | 0     | 12     | 对延迟敏感 | 2          |

| 总线主设备              | 读/写 | 使用的端口 | 默认 QoS | 流量类别            | 读/写 QoS 区域 |

|--------------------|-----|-------|--------|-----------------|------------|

| LTDC               | 读取  | 1     | 11     | 对延迟要求严格         |            |

| ETH                | 读/写 | 0     | 7      |                 |            |

| MCU <sup>(1)</sup> | 读/写 | 0     | 6      |                 |            |

| USBH               | 读/写 | 0     | 5      | 对延迟要求严格<br>尽力而为 | 1          |

| SDMMC1             | 读/写 | 0     | 4      |                 |            |

| SDMMC2             | 读/写 | 0     | 4      |                 |            |

| GPU                | 读/写 | 0     | 3      | 尽力而为            |            |

| DAP                | 读/写 | 0     | 2      |                 | 0          |

1. MCU 是指总线主设备 DMA1/2、OTG 和 SDMMC3。

DDRCTRL QoS 和调度参数设置如下：

- 建议对 x16 和 x32 使用两种 AXI 端口配置以改善 RT 流量，特别是映射到端口 1 的 LTDC

- 对于所有端口读取，QoS 值 (0 - 15) 到类的映射如下：

- 将  $12 \leq \text{QoS} \leq 15$  的区域 2 映射到 HPR。

- 将  $4 \leq \text{QoS} \leq 11$  的区域 1 映射到 VPR。

- 将  $0 \leq \text{QoS} \leq 3$  的区域 0 映射到 LPR。

- 对于所有端口写入，QoS 值 (0 - 15) 到类的映射如下：

- 将  $12 \leq \text{QoS} \leq 15$  的区域 2 映射到 VPW。

- 将  $4 \leq \text{QoS} \leq 11$  的区域 1 映射到 VPW。

- 将  $0 \leq \text{QoS} \leq 3$  的区域 0 映射到 NPW。

QoS 模型的描述如下：

- HPR 表示高优先级读取队列，适合对延迟敏感的流量，带宽有界限。

- VPR/VPW 表示优先级可变的读取/写入，适合对延迟要求严格或对实时性要求严格的流量。VPR 或 VPW 超时结束优先于 HPR。

- LPR/NPW 是尽力而为流量。

- 读取优先于写入。

- 为读取 CAM 分配了 HPR (3 个入口) 和 VPR/LPR (13 个入口)。

- DDRCTRL 具有抗饥饿特性，通过每个队列的 max\_starve/run\_length 控制：HPR 和 LPR 用于读取，WR 用于写入。

- 可以根据 r/wqos\_map\_timeout 参数按端口和区域指定 VPR/VPW 超时，以十六进制编码时钟周期数。该值越小，VPR/VPW 越快进入“已过期-VPR/VPW”状态，无论超时发生时事务是处于 AXI 端口队列中还是 CAM 存储中。

- 当行开头卡在 AXI 层时，端口老化可用于防止端口饥饿。由于不希望发生这种情况，因此端口老化不与推荐配置一起使用。

- 为了节约功耗，可以使用智能预充电政策而不是打开页面政策。

按下表所示确定参数和 DDRCTRL 寄存器。

提示

QoS 设置和调度控制参数是静态的，必须在 DDRCTRL 退出复位前的配置过程中进行设置。

表 2. QoS 和调度参数

| 调度器参数                 | 值   | 说明                      |

|-----------------------|-----|-------------------------|

| sched.rdw_idlet_gap   | 0x0 | RD/WR 事务存储之间的即时切换       |

| sched.lpr_num_entries | 0xC | HPR: 3 个入口; LPR: 13 个入口 |

| sched.pageclose       | 0x0 | 打开页面政策。                 |

| sched.prefer_write    | 0x0 | 读取总是优先于写入。              |

| sched.force_low_pri_n | 0x1 | 0: 强制全部为低优先级 (保留 1)     |

| 调度器参数                       | 值     | 说明                             |

|-----------------------------|-------|--------------------------------|

| sched1.pageclose_timer      | 0x0   | 对打开页面政策不可用                     |

| perfhp1.hpr_xact_run_length | 0x1   | HPR 的运行长度。                     |

| perfhp1.hpr_max_starve      | 0x1   | HPR 的饥饿控制设置为 1 个时钟周期           |

| perfpr1.lpr_xact_run_length | 0x8   | LPR 的运行长度。                     |

| perfpr1.lpr_max_starve      | 0x200 | LPR 的饥饿控制设置为 512 个时钟周期 (~1 μs) |

| perfwr1.w_xact_run_length   | 0x8   | 写入的运行长度。                       |

| perfwr1.w_max_starve        | 0x400 | WR 的饥饿控制设置为 1024 个时钟周期 (~2 μs) |

表 3. 每个 AXI 端口的 QoS 设置

| AXI 端口参数                     | 端口 0  | 端口 1  | 说明                            |

|------------------------------|-------|-------|-------------------------------|

| pcfgr.rdwr_ordered_en        | 0x1   | 0x1   | 在相同地址保存读/写顺序以确保一致性。           |

| pcfgr.rd_port_pagematch_en   | 0x0   | 0x0   | 对读操作禁用页面匹配使能。                 |

| pcfgr.rd_port_aging_en       | 0x0   | 0x0   | 使能 AXI 读端口老化。                 |

| pcfgr.rd_port_priority       | 0x0   | 0x0   | AXI 读取端口老化初始值以防止端口饥饿          |

| pcfgr.wr_port_pagematch_en   | 0x0   | 0x0   | 对写操作禁用页面匹配使能。                 |

| pcfgr.wr_port_aging_en       | 0x0   | 0x0   | 使能 AXI 写端口老化。                 |

| pcfgr.wr_port_priority       | 0x0   | 0x0   | AXI 写入端口老化初始值以防止端口饥饿          |

| pctrl.port_en                | 0x1   | 0x1   | 使能 AXI 端口。                    |

| pcfqqos0.rqos_map_region2    | 0x2   | 0x2   | 区域 2 设置为 HPR                  |

| pcfqqos0.rqos_map_region1    | 0x1   | 0x1   | 区域 1 设置为 LPR 或 VPR            |

| pcfqqos0.rqos_map_region0    | 0x0   | 0x0   | 区域 0 设置为 LPR                  |

| pcfqqos0.rqos_map_level2     | 0xB   | 0xB   | rqos > val 时为区域 2             |

| pcfqqos0.rqos_map_level1     | 0xA   | 0x3   | rqos ≤ val 时为区域 0             |

| pcfqqos1.rqos_map_timeoutr   | 0x80  | 0x80  | 红色队列在 VPR 过期前的超时设置为 128 个时钟周期 |

| pcfqqos1.rqos_map_timeoutb   | 0x100 | 0x40  | 蓝色队列在 VPR 过期前的超时设置为 256 个时钟周期 |

| pcfqqwqos0.wqos_map_region2  | 0x1   | 0x1   | 区域 2 设置为 NPW 或 VPW            |

| pcfqqwqos0.wqos_map_region1  | 0x1   | 0x1   | 区域 1 设置为 NPW 或 VPW            |

| pcfqqwqos0.wqos_map_region0  | 0x0   | 0x0   | 区域 0 设置为 NPW                  |

| pcfqqwqos0.wqos_map_level2   | 0xC   | 0xB   | wqos > val 时为区域 2             |

| pcfqqwqos0.wqos_map_level1   | 0xA   | 0x3   | wqos ≤ val 时为区域 0             |

| pcfqqwqos1.wqos_map_timeout2 | 0x100 | 0x100 | QoS 区域 2 在 VPW 过期前的写入超时       |

| pcfqqwqos1.wqos_map_timeout1 | 0x200 | 0x200 | QoS 区域 0 和 1 在 VPW 过期前的写入超时   |

表 4. DDRCTRL 调度和性能控制寄存器

| 寄存器         | 地址    | 值            | 说明                  |

|-------------|-------|--------------|---------------------|

| SCHED       | 0x250 | 0x00000C01   | 调度器控制寄存器            |

| SCHED1      | 0x254 | 0x00000000   | 调度器控制寄存器 1          |

| PERFHPR1    | 0x25C | 0x01000001   | 高优先级读 CAM 寄存器 1     |

| PERFLPR1    | 0x264 | 0x08000200   | 低优先级读 CAM 寄存器 1     |

| PERFWR1     | 0x26C | 0x08000400   | 写 CAM 寄存器 1         |

| PCFGR_0     | 0x404 | 0x00010000   | 端口 0 配置读寄存器         |

| PCFGW_0     | 0x408 | 0x00000000   | 端口 0 配置写寄存器         |

| PCTRL_0     | 0x490 | (0x00000001) | 端口 0 控制寄存器 (由驱动器管理) |

| PCFGQOS0_0  | 0x494 | 0x02100B0A   | 端口 0 读 QoS 配置寄存器 0  |

| PCFGQOS1_0  | 0x498 | 0x00800100   | 端口 0 读 QoS 配置寄存器 1  |

| PCFGWQOS0_0 | 0x49C | 0x01100C0A   | 端口 0 写 QoS 配置寄存器 0  |

| PCFGWQOS1_0 | 0x4A0 | 0x01000200   | 端口 0 写 QoS 配置寄存器 1  |

| PCFGR_1     | 0x4B4 | 0x00010000   | 端口 1 配置读寄存器         |

| PCFGW_1     | 0x4B8 | 0x00000000   | 端口 1 配置写寄存器         |

| PCTRL_1     | 0x540 | (0x00000001) | 端口 1 控制寄存器 (由驱动器管理) |

| PCFGQOS0_1  | 0x544 | 0x02100B03   | 端口 1 读 QoS 配置寄存器 0  |

| PCFGQOS1_1  | 0x548 | 0x00800040   | 端口 1 读 QoS 配置寄存器 1  |

| PCFGWQOS0_1 | 0x54C | 0x01100B03   | 端口 1 写 QoS 配置寄存器 0  |

| PCFGWQOS1_1 | 0x550 | 0x01000200   | 端口 1 写 QoS 配置寄存器 1  |

### 3.3.4 DDR 刷新控制器

根据时钟频率和 DRAM 刷新要求 (JEDEC) 对 DDRCTRL 刷新控制器进行编程。刷新参数由 STM32CubeMX 根据 JEDEC 时序 ( $t_{REFI}$  和  $t_{RFC}$ ) 确定并被编程到 DDRCTRL.RFSHTMG。

默认使用定期自动刷新。但是, DDRCTRL 还支持以下可选功能 (请参考[1]了解详细信息) :

- 具有推测性脉冲刷新超时的脉冲刷新

- LPDDR2/3 的按区刷新

- 软件发出刷新命令

- 默认使能通过模式寄存器 4 (MR4) 定期轮询检查 LPDDR2/3 温度降额, 以便自动调整刷新频率。

- 可以在 DDR3 配置期间设置 ASR/SRT 支持。

提示

### 3.4 PHY 调谐

在内置或由 STM32CubeMX 启动的 PHY 调谐流程中确定调谐参数。

DQSTRN 总是在使用 DDRPHYC 支持的内置序列执行 PHY 初始化时运行。DQSTRN 确定一个合适的窗口, 用于 DQS/DQS# 差分选通信号在前导和后导之间的四分之一位分辨率捕获 DQ 读数据 (请参考[1]的 DDRPHYC 部分了解详细信息)。

软件 DQSTRN 流程也可以通过 STM32CubeMx 启动。结果通过 DRPHYC.DXnDQSTR 字段、SL (系统延迟) 和 PS (相移) 值显示。

使用分辨率为~20 ps 的细步长延迟, DDRPHYC 支持 DQ 位去时滞和 DQS 眼图居中。通过从 STM32CubeMx 启动软件调谐流程确定最佳细步长延迟。由于这一流程可能较长, 必须将设置 (如果不同于默认设置) 保存并恢复到 DDRPHYC。

DQ 位去时滞允许对关于其采样 DQS 和 DQS# 上升沿和下降沿的每个读取 DQ 位使用细步长延迟。根据 DDRPHYC.DXnDQTR 字段的值显示结果。

DQS 眼图居中允许对每个读取 DQS 使用细步长延迟, 以优化对齐 DQ 数据的采样。根据 DDRPHYC.DXnDQSTR 字段的值显示结果。

为了执行以下任务，必须在最终的不同环境条件下在多块板上多次启动 DQ 位去时滞和 DQS 眼图居中调整：

- 确定要为所有板的 DXnDQTR 和 DXnDQSTR 寄存器保存和恢复的 DQ 和 DQS 细步长延迟最佳值。

- 根据下列标准，找到任何可疑的板布局设计问题：

- 对 DQ 位去时滞使用的 DQ 细步长延迟必须一致，在字节通道内部具有几乎相同的稳定值，即差异不得超过一个步长（步长数 0、1、2、3，编码为 DXnDQTR 相应位字段中的半字节 0、5、A、F）。

- 对眼图居中使用的 DQS#/DQS 细步长延迟必须一致，在字节通道内部具有几乎相同的稳定值，即差异不得超过一个步长（步长数-3 至+4 编码为 DXnDQSTR 相应位字段中的 0 至 7）。

- 为了找出任何可疑的板件问题，必须在各种不同环境条件下在多块板上多次启动 DQSTRN 软件。SL 和 PS 值可以在 DXnDQSTR 寄存器中找到。这些值还必须稳定一致，无显著差异（典型值为 SL = 1, PS = 3）。这是关于 SL、PS 的二进制计数器，因此，SL = 2, PS = 0 是 SL = 1, PS = 3 之后的下一个相位。

- 内置 DQSTRN 在初始化时运行，必须提供与调谐软件相同的值。

- 对于从设备 DLL 相位，调整时可以使用 18° 的步长。必须在调谐后实现对中，使相位达到 90°（可以在 DXnDLLCR 寄存器中确认）。

## 4 配置序列和参数

DDRSS 子系统设置序列如下：

1. 设置电源和时钟。

2. 释放 APB 域复位。

3. 加载 DDRCTRL 寄存器（跳过 DRAM 初始化）。

4. 释放 DDRCTRL 复位和 DDRPHYC 复位。

5. 加载 DDRPHYC 寄存器

6. 根据 DDRPHYC.PIR，通过 PUB 按下列步骤启动完整的 PHY 和 DDR 初始化：

- a. 初始化 DDRPHYC。

- b. 复位 DDR3 的 DRAM。

- c. 复位 DDL。

- d. 复位 ITM。

- e. 初始化 DRAM。

- f. 校准阻抗（位于 PHY 和 DRAM 的驱动器和 ODT）。

- g. 指示 DFI 初始化完成并等待 DDRCTRL 正常操作模式。

- h. 执行内置 DQSTRN。

- i. 使能两个 AXI 端口。

然后，可以在启动期间执行调谐和测试。

## 5 DDR3/3L 配置

### 5.1 关于 DDR3/3L 的一般注意事项

DDR3 和 DDR3L 配置相同, 但电源和  $V_{REF}$  除外, 如下所示:

- 对于 DDR3:  $V_{DD} = 1.5 \text{ V}$  且  $V_{REF} = 0.75 \text{ V}$

- 对于 DDR3L:  $V_{DD} = 1.35 \text{ V}$  且  $V_{REF} = 0.675 \text{ V}$

本文档中将它们统称为 DDR3 (请参考[2]了解详细信息)。

DDR3 可以用在具有 16 位接口的 BGA 中。DDR 工具支持下表中列出的配置。

DDR3 支持以下拓扑:

- 16 位: p2p 中一个 BGA, 密度范围为 1 - 8 Gb

- 32 位: fly-by 拓扑中两个 BGA, 每个晶片的密度范围为 1 - 4 Gb

表 5. DDR3 密度和拓扑

| 总 DDR 密度 (Mbytes) | 16 位接口           | 32 位接口           |

|-------------------|------------------|------------------|

| 128               | 1 个器件 x16 (1 Gb) | 不可用              |

| 256               | 1 个器件 x16 (2 Gb) | 2 个器件 x16 (1 Gb) |

| 512               | 1 个器件 x16 (4 Gb) | 2 个器件 x16 (2 Gb) |

| 1000              | 1 个器件 x16 (8 Gb) | 2 个器件 x16 (4 Gb) |

DDR 频率通过 STM32CubeMX 时钟配置进行设置, 并由 DDR 工具使用, 限制如下:

- $300 \text{ MHz} \leq \text{频率} \leq 533 \text{ MHz}$  (DLL 开启时 DDR3 下限为 300 MHz)

- 频率  $\leq 125 \text{ MHz}$  时 DDR3 DLL 关闭

DDR-1066 有三个速度档位 (G/F/E), 使用哪一个取决于 STM32CubeMX DDR 面板菜单选择 (分别为 0/1/2)。

JEDEC 速度等级和速度档位用于选择与 DDR-1066 (频率  $\leq 533 \text{ MHz}$ ) 最接近的匹配项, 并获取所有其他 JEDEC 时序参数。用户只需根据下表在 STM32CubeMx 中为 DRAM 输入数据手册中的选择符 (0、1 或 2)。

表 6. DDR3 数据手册的速度等级/速度档位预定值

| DDR3 速度档位 | DDR3 速度等级 |          |          |          |          |

|-----------|-----------|----------|----------|----------|----------|

|           | DDR-1066  | DDR-1333 | DDR-1600 | DDR-1866 | DDR-2133 |

| 否         | -         | -        | -        | -        | 1        |

| M         | -         | -        | -        | 1        | 1        |

| L         | -         | -        | -        | 1        | 2        |

| K         | -         | -        | 1        | 1        | 2        |

| J         | -         | 0        | 1        | 2        | -        |

| H         | -         | 1        | 2        | -        | -        |

| G         | 0         | 1        | 2        | -        | -        |

| F         | 1         | 2        | -        | -        | -        |

| E         | 2         | -        | -        | -        | -        |

默认选择数据手册选择符 0, 即对应于 533 MHz 时 8-8-8 基础三元组时序的保守时序。

CL/CWL 参数取决于数据手册选择符 (0、1 或 2) 对应的频率, 如下表所示。

表 7. CL/CWL 与频率及数据手册预定值

| 数据手册选择符 | 频率范围 (MHz)      |                       |                    |                    |

|---------|-----------------|-----------------------|--------------------|--------------------|

|         | $f \leq 125$    | $300 \leq f \leq 333$ | $303 < f \leq 400$ | $400 < f \leq 533$ |

| 0       | CL = 6, CWL = 6 | CL = 6, CWL = 6       | CL = 8, CWL = 6    | CL = 7, CWL = 6    |

| 1       |                 |                       |                    |                    |

| 2       |                 |                       |                    |                    |

有些时序参数的值可能低于 DDR-1066，并可能被 DDR 配置工具高级参数覆盖。但是，这对性能的影响微不足道。一般情况下，根据档位选择使用默认参数即可。

## 5.2 DDR3 上电序列、初始化和 ZQ 校准

DDR3 上电序列由 JEDEC 指定，VDD/VDDQ，从单一来源生成且电压斜坡 $< 200$  ms。

规定的 DDR3 初始化序列如下：

1. 可以选择让 RESET#维持低电平并持续至少 200  $\mu$ s（启动初始化）或 100 ns（上电初始化）。DDRPHYC 从复位发生开始时驱动 RESET#为低电平。因此，如果超过的时间达到 RESET#低电平时间，则可以跳过该步骤。

2. 在 RESET#释放后，等待至少 500  $\mu$ s，期间 CKE 为低电平。

3. 应用 NOP 并驱动 CKE 为高电平。

4. 等待时间至少为  $t_{XPR}$ 。

### 注意：

DDRPHYC、DDR 模式和 DDRCTRL 寄存器的设定必须一致。寄存器字段不匹配可能导致事务失败。在开始任何 SDRAM 事务前，确保所有寄存器字段的设定一致。

5. 发出加载模式寄存器 2 (MR2) 命令。

6. 发出加载模式寄存器 3 (MR3) 命令。

7. 发出加载模式寄存器 (MR1) 命令以设置参数并使能 DLL。

8. 发出加载模式寄存器 (MR0) 命令以设置参数并复位 DLL。

9. 发出 ZQ 校准命令。

10. 等待 512 个 SDRAM 时钟周期，让 DLL 锁定 ( $t_{DLLK}$ ) 并完成 ZQ 校准 ( $t_{ZQinit}$ )。

当通过 SDRAM 命令总线发布 DLL 复位命令时，此等待时间与步骤 8 相关。

DDR3 初始化完全由 DDRPHYC 控制。PTR0/1/2 寄存器定义针对时钟频率进行了调整的初始化时序参数。通过 PIR 寄存器触发完整初始化。

## 5.3 频率范围限制

时钟频率必须满足以下条件：

- 当 DLL 启用时， $300$  MHz  $\leq f \leq 533$  MHz。

- 当 DLL 停用时， $f < 125$  MHz。

由于 DLL 默认启用，DLL 停用模式显得不那么重要且不能直接使用。

## 5.4 片内端结 (ODT)

ODT 对于改善信号完整性十分重要。它们可以与所有 DDR3 拓扑 (16 位和 32 位接口) 配合使用。

ODT 适用于 DQ/DQS 字节通道，如下所述：

- 在读操作期间动态切换本地 PHY ODT。ODT 阻抗可通过 ZQ0CR1.ZPROG[7:4]进行编程 (参见表 8)。DQ/DQS 输出阻抗可通过 ZQ0CR1.ZPROG[3:0]和 ODT 阻抗值进行编程 (参见表 9)。

- 默认情况下，ZPROG[7:0] = 0x38，DQ/DQS 输出阻抗设置为  $53 \Omega$  且 ODT 设置为  $80 \Omega$ 。这些值可以在信号电平、信号反射与功耗优化之间实现良好平衡。

- DRAM ODT 在写操作期间通过 ODT 引脚进行动态切换。DDR 通过 RTT\_WR 进行设置（也称动态 ODT）并由 MR2[1:0]控制，如下所示：

- MR2[1:0] = 0b00: 禁用

- MR2[1:0] = 0b01: 60 Ω

- MR2[1:0] = 0b10: 120 Ω

## 提示

不使用 DDR3 RTT\_nom 模式，一个存储区不需要此模式。

DDR 侧的 DQ/QDS 输出阻抗由 MR1[1]设置，如下所示：

- MR1[1] = 0: 40 Ω

- MR1[1] = 1: 34 Ω

DDR3 的标称配置是将 DQ/DQS 输出阻抗设置为 40 Ω 并将 ODT 设置为 60 Ω（通过 MR2 模式寄存器设置）。

表 8. ODT 阻抗与 ZPROG 位 (RZQ = 240 Ω ± 1 %)

| ZPROG[7:4] | ODT DDR3/3L (Ω) |

|------------|-----------------|

| 0x0        | -               |

| 0x1        | 120             |

| 0x2        | 96              |

| 0x3        | 80              |

| 0x4        | 69              |

| 0x5        | 60              |

| 0x6        | 52              |

| 0x7        | 46              |

| 0x8        | 40              |

| 0x9        | 37              |

| 0xA        | 34              |

| 0xB        | 32              |

| 0xC        | 30              |

| 0xD        | 28              |

| 0xE        | 26.5            |

| 0xF        | 25              |

表 9. 输出阻抗与 ZPROG 位 ( $RZQ = 240 \Omega \pm 1\%$ )

| ZPROG[3:0] | ODT DDR3/3L ( $\Omega$ ) |

|------------|--------------------------|

| 0x0 to 0x4 | -                        |

| 0x5        | 80                       |

| 0x6        | 69                       |

| 0x7        | 60                       |

| 0x8        | 53                       |

| 0x9        | 48                       |

| 0xA        | 44                       |

| 0xB        | 40                       |

| 0xC        | 37                       |

| 0xD        | 34                       |

| 0xE        | 32                       |

| 0xF        | 30                       |

ODT 开启/关闭时序的控制如下：

- DDRPHYC 侧: DXnGCR.RTTOAL 和 DXnGCR.RTTOH 参数

ODT 在读操作 2.25 个周期前开启，并在最后一个字节 1 个周期后关闭。

- DDR 侧: 通过 ODT 引脚由 DDRCTRL 根据 ODTCFG.WR\_ODT\_DELAY 和 ODTCFG.WR\_ODT\_HOLD 进行控制

ODT 早于写入脉冲 WL-2 个周期，并在  $BL = 8$  后的 6 个周期内发生。

## 提示

PHY ODT 通过内部信号  $TE = 1$  激活，ODT 开/关切换可能导致显著的电流变化并可能影响电源分配网络，从而干扰 CK/CK# 并引起抖动。较高的 ODT 值可以减少电流变化，在发生问题时可以用来降低电源噪声。

## 5.5 命令/地址通道 (CA) 端接

RTT 端接用于 fly-by 拓扑的 32bit 和有条件的 16bit 配置中的命令/地址总线（请参考[5]了解详细信息）

RTT 端接的存在不影响 DDR 配置。

## 5.6 阻抗校准 (ZCAL)

本地 PHY 和 DDR PHY 的 DDR3 信号阻抗都必须准确。这是通过阻抗校准 (ZCAL)，即校准输出驱动器和 ODT 阻抗来完成的。

### 5.6.1 PHY

DDRPHYC 具有 ZCAL 引擎，用于将 SSTL I/O 阻抗调整为设定值，前提是  $RZQ = 240 \Omega \pm 1\%$ 。

ZCAL 在初始化期间自动触发。

也可以稍后通过软件启动 ZCAL。此外，DDRCTRL 还支持 DFI 控制器 PHY 更新，可用于按固定时间间隔（或在自刷新退出时）发出 ZCAL。

PHY 阻抗通过 ZPROG 进行编程，详情见第 5.4 节 片内终结 (ODT)。

### 5.6.2 DRAM

四个阻抗的校准如下文所述， $RZQ = 240 \Omega \pm 1\%$ :

- 驱动器上拉或下拉: 两个可能值,  $34 \Omega$  (默认值) 和  $40 \Omega$

- ODT 上拉或下拉: 多个可能值 (默认值 =  $60 \Omega$ )

DRAM 校准由 ZQCL 或 ZQCS 命令触发，如下所示:

- ZQCL 命令用于启动初始化序列中的初始校准，并通过 DDRPHYC 启动。该命令也可以稍后由 DDRCTRL 在自刷新退出时发出，具体取决于系统环境。ZQCL 耗时 256 个时钟周期。

- ZQCS 命令可用于执行周期性校准，以应对电压和温度变化。该命令由 DDRCTRL 按固定时间间隔发出。ZQCS 耗时 64 个时钟周期。

## 5.7 DLL 开启/关闭模式

DDR3 默认开启 DLL。DLL 关闭模式使用有限且意义不大。

但是，当处于 DDR3 掉电模式时，根据 MR0[12]，可以关闭 DLL 以节约功耗，详情如下：

- 当 MR0[12] = 0 (DDR3 缓慢退出模式) 时， $t_{XSDLL}$  应用于掉电退出 (PDE)。 $t_{XSDLL}$  是指从 PDE 到任何要求锁定 DLL 的命令之间有 512 个时钟周期延迟。

- 当 MR0[12] = 1 (DDR3 快速退出模式) 时，只将  $t_{XSDLL}$  应用于 PDE。

DDR 工具默认使用快速退出模式 (MR0[12] = 1)，以尽可能减少延迟对自动掉电进入的影响。

## 5.8 DDRPHYC 内置 DQSTRN

DQS 门控训练 (DQSTRN) 默认在初始化期间启动。DQSTRN 使用 DDR 阵列和读/写操作 (R/B/C，默认为 0)。

DDRPHYC 可能支持 DQSTRN 使用 MPR，但没有以选项的形式提供。

DQSTRN 完全由 PUB 寄存器控制：启动、R/B/C、模式和状态报告（参见[1]了解详细信息）。

## 5.9 DQ 读眼图训练和位去时滞支持 (可选)

这些参数由软件控制，并按字节通道存储在 DDRPHYC DXnDQTR/DQSTR 寄存器中。

在大多数情况下，默认值可以在时钟频率  $\leq 533$  MHz 时使用，但可能不是最佳值 (DQ 去时滞的目的是补偿轻微的 PCB 通道不匹配)。

## 5.10 DDR3 配置示例

本例显示了具有两个 4-Gb DDR3L 的板的 DDR3 配置。

时钟频率由 STM32CubeMx 时钟配置进行定义 (本例中为 528 MHz)。

DDR 类型和宽度在 STM32CubeMx 引脚排列和配置中进行定义。

本例中的值如下：

- DDR 类型：DDR3/DDR3L

- 宽度：32 位

- 密度：4 Gb

DDR 参数窗口中其他参数的设置如下 (通过滚动窗口菜单和勾选复选框)：

- 速度档位等级：DDR3-1066 / 8-8-8

- 读取期间的阻抗：Ron 40 Ω 且 ODT = 80 Ω (默认)

- 写入期间的阻抗：Ron 53 Ω 且 ODT = 60 Ω (默认)

- 地址映射配置：R/B/C

- 宽松时序模式：(复选框)

- 外壳温度超过 85°C (复选框)

- 数据手册选择：0

- Sched/Qos 选项：2

### 提示

根据以下接口宽度使能 PHY 字节通道：

- 在 32 位模式下启用所有字节通道

- 在 16 位模式下关闭 2/3 字节通道

宽松时序模式用于内核时序的递增 (每次增加 1)，以便改善时序裕量。当存在可疑故障时，必须执行递增。

下表中详细列出了以上配置的寄存器值。

表 10. DDRCTRL 和 DDRPHYC 时序寄存器值

| 外设设备    | 寄存器       | 地址    | 值          |

|---------|-----------|-------|------------|

| DDRCTRL | RFSHTMG   | 0x064 | 0x0040008B |

|         | DRAMTMG0  | 0x100 | 0x121B1214 |

|         | DRAMTMG1  | 0x104 | 0x000A041C |

|         | DRAMTMG2  | 0x108 | 0x0608090F |

|         | DRAMTMG3  | 0x10C | 0x0050400C |

|         | DRAMTMG4  | 0x110 | 0x08040608 |

|         | DRAMTMG5  | 0x114 | 0x06060403 |

|         | DRAMTMG6  | 0x118 | 0x02020002 |

|         | DRAMTMG7  | 0x11C | 0x00000202 |

|         | DRAMTMG8  | 0x120 | 0x00001005 |

|         | DRAMTMG14 | 0x138 | 0x000000A0 |

|         | ODTCFG    | 0x240 | 0x06000600 |

| DDRPHYC | PTR0      | 0x018 | 0x0022AA5B |

|         | PTR1      | 0x01C | 0x04841104 |

|         | PTR2      | 0x020 | 0x042DA068 |

|         | DTPR0     | 0x034 | 0x38D488D0 |

|         | DTPR1     | 0x038 | 0x098B00D8 |

|         | DTPR2     | 0x03C | 0x10023600 |

|         | MR0       | 0x040 | 0x00000840 |

|         | MR1       | 0x044 | 0x00000000 |

|         | MR2       | 0x048 | 0x00000248 |

表 11. DDRCTRL 和 DDRPHYC 常量寄存器值与 DDR3

| 外设设备    | 寄存器        | 地址    | 值            |

|---------|------------|-------|--------------|

| DDRCTRL | MSTR       | 0x000 | 0x00040401   |

|         | MRCTRL0    | 0x010 | 0x00000010   |

|         | MRCTRL1    | 0x014 | 0x00000000   |

|         | DERATEEN   | 0x020 | 0x00000000   |

|         | DERATEINT  | 0x024 | 0x00800000   |

|         | PWRCTL     | 0x030 | 0x00000000   |

|         | PWRTMG     | 0x034 | 0x00400010   |

|         | HWLPCTL    | 0x038 | 0x00000000   |

|         | RFSHCTL0   | 0x050 | 0x00210000   |

|         | RFSHCTL3   | 0x060 | 0x00000000   |

|         | CRCPARCTL0 | 0x0C0 | 0x00000000   |

|         | ZQCTL0     | 0x180 | 0xC2000040   |

|         | DFITMG0    | 0x190 | 0x02060105   |

|         | DFITMG1    | 0x194 | 0x00000202   |

|         | DFILPCFG0  | 0x198 | 0x07000000   |

|         | DFIUPD0    | 0x1A0 | 0xC0400003   |

|         | DFIUPD1    | 0x1A4 | 0x00000000   |

|         | DFIUPD2    | 0x1A8 | 0x00000000   |

|         | DFIPHYMSTR | 0x1C4 | 0x00000000   |

|         | ODTMAP     | 0x244 | (0x00000001) |

|         | DBG0       | 0x300 | 0x00000000   |

|         | DBG1       | 0x304 | 0x00000000   |

|         | DBGCMD     | 0x30C | 0x00000000   |

|         | POISONCFG  | 0x36C | 0x00000000   |

|         | PCCFG      | 0x400 | 0x00000010   |

|         | PGCR       | 0x008 | 0x01442E02   |

| DDRPHYC | ACIOCR     | 0x024 | 0x10400812   |

|         | DXCCR      | 0x028 | 0x00000C40   |

|         | DSGCR      | 0x02C | 0xF200001F   |

|         | DCR        | 0x030 | 0x0000000B   |

|         | MR3        | 0x04C | 0x00000000   |

|         | ODTCR      | 0x050 | 0x00010000   |

|         | ZQ0CR1     | 0x184 | 0x00000038   |

|         | DX0GCR     | 0x1C0 | 0x0000CE81   |

|         | DX1GCR     | 0x200 | 0x0000CE81   |

|         | DX2GCR     | 0x240 | 0x0000CE81   |

|         | DX3GCR     | 0x280 | 0x0000CE81   |

表 12. DDR3 的 DDRCTRL 地址映射寄存器值

| 寄存器       | 地址    | 值          |

|-----------|-------|------------|

| ADDRMAP1  | 0x204 | 0x00080808 |

| ADDRMAP2  | 0x208 | 0x00000000 |

| ADDRMAP3  | 0x20C | 0x00000000 |

| ADDRMAP4  | 0x210 | 0x00001F1F |

| ADDRMAP5  | 0x214 | 0x07070707 |

| ADDRMAP6  | 0x218 | 0x0F0F0707 |

| ADDRMAP9  | 0x224 | 0x00000000 |

| ADDRMAP10 | 0x228 | 0x00000000 |

| ADDRMAP11 | 0x22C | 0x00000000 |

表 13. DDR3 的 DDRCTRL QoS 调度寄存器值

| 寄存器         | 地址    | 值          |

|-------------|-------|------------|

| SCHED       | 0x250 | 0x00000C01 |

| SCHED1      | 0x254 | 0x00000000 |

| PERFHPR1    | 0x25C | 0x01000001 |

| PERFLPR1    | 0x264 | 0x08000200 |

| PERFWR1     | 0x26C | 0x08000400 |

| PCFGR_0     | 0x404 | 0x00010000 |

| PCFGW_0     | 0x408 | 0x00000000 |

| PCFGQOS0_0  | 0x494 | 0x02100C03 |

| PCFGQOS1_0  | 0x498 | 0x00800100 |

| PCFGWQOS0_0 | 0x49C | 0x01100C03 |

| PCFGWQOS1_0 | 0x4A0 | 0x01000200 |

| PCFGR_1     | 0x4B4 | 0x00010000 |

| PCFGW_1     | 0x4B8 | 0x00000000 |

| PCFGQOS0_1  | 0x544 | 0x02100C03 |

| PCFGQOS1_1  | 0x548 | 0x00800040 |

| PCFGWQOS0_1 | 0x54C | 0x01100C03 |

| PCFGWQOS1_1 | 0x550 | 0x01000200 |

低功耗特性如下：

- **掉电：**自动掉电选项（高级用户）

- **自刷新：**可通过软件（SSR）或硬件（HSR）控制或自动执行（ASR）（参见[1]的 RCC 部分了解详细信息）

扩展温度范围支持 ASR/SRT 模式（STM32Cube MX 选项）。DDR3 MR2 用于控制自刷新，以便支持扩展温度范围。对于扩展温度范围，必须通过让 ASR = 1 设置自动自刷新（当 DDR3 支持此可选 ASR 功能时）。如果不支持 AST，则可以使用 SRT 指示后续自刷新间隔的工作温度。

## 6 LPDDR2 配置

### 6.1 关于 LPDDR2 的一般注意事项

LPDDR2 分为 x32 和 x16，并具有多种封装焊球布局（BGA 和 PoP）。DDR 工具支持下表中列出的配置。支持的 LPDDR2-S4 配置的密度  $\geq 1 \text{ Gb}$ ，有 8 个存储区。

LPDDR2 支持以下拓扑：

- 16 位：一个BGA点对点连接，密度范围为 1 - 4 Gb（单晶片）

- 32 位：一个BGA点对点连接，密度范围为 1 - 4 Gb（单晶片）更多详细信息，请参见[3]。

表 14. LPDDR2 密度和拓扑

| 总 DDR 密度 (Mbytes) | 16 位接口           | 32 位接口           |

|-------------------|------------------|------------------|

| 128               | 1 个器件 x16 (1 Gb) | 1 个器件 x32 (1 Gb) |

| 256               | 1 个器件 x16 (2 Gb) | 1 个器件 x32 (2 Gb) |

| 512               | 1 个器件 x16 (4 Gb) | 1 个器件 x32 (4 Gb) |

**注意：**上表中列出的配置是具有 8 个存储区的 LPDDR2-S4。DDR 工具不支持具有 4 个存储区的密度较低的 LPDDR2-S2。LPDDR2 具有以下特性：

- 无 ODT，无 DLL 且无复位引脚

- CMOS I/O (DDRPHYC 以 SSTL 模式设置 I/O)

- 10-533 MHz 连续范围操作

- 特殊低功耗特性：PASR，温度控制的自刷新

- 按区刷新（高级用户）

- MRR MR4 轮询和刷新 T 降额（默认设置）

- 深度掉电（DPD）模式（由于 DPD 期间 LPDDR2 的内容丢失，此模式的意义不大，在此不做讨论）

### 6.2 LPDDR2 上电、初始化和 ZQ 校准

LPDDR2 需要两个电源 ( $V_{DD1} = 1.8 \text{ V}$ ,  $V_{DD2} = 1.2 \text{ V}$ ) 且  $V_{REF} = 0.6 \text{ V}$ 。

必须满足 LPDDR2 上电时序和以下电压斜坡：

- $< 20 \text{ ms}$  的斜坡

- $V_{DD2} > V_{DD1} - 200 \text{ mV}$

- $(V_{DD1}, V_{DD2}) > (V_{DDQ} - 200 \text{ mV}, V_{DDCA} - 200 \text{ mV})$

- CKE 低

- 所有输入和  $V_{REF}$  均处于供电范围以内

### 6.2.1 LPDDR2 初始化序列

规定的 LPDDR2 初始化序列如下：

- 等待至少 100 ns ( $t_{INIT1}$ )， CKE 被驱动为低电平。

- 应用 NOP 并将 CKE 置为高电平。

- 等待至少 200  $\mu$ s ( $t_{INIT3}$ )。

- 发出 RESET 命令。

- 等待至少 1  $\mu$ s + 10  $\mu$ s ( $t_{INIT4} + t_{INIT5}$ )。

- 发出 ZQ 校准命令。

- 等待至少 1  $\mu$ s ( $t_{ZQINIT}$ )。

- 向 MR1 发出写模式寄存器命令。

- 向 MR2 发出写模式寄存器命令。

- 向 MR3 发出写模式寄存器命令。

LPDDR2 初始化完全由 DDRPHYC 控制。PTR0/1/2 寄存器定义针对时钟频率进行了调整的初始化时序参数。通过 PIR 寄存器触发完整初始化。

### 6.2.2 LPDDR2 特有的设置

LPDDR2 特有的设置如下：

- 扩展时钟频率范围：10 MHz - 533 MHz

- LPDDR2 无 DLL：从低功耗模式（PDN 和自刷新）和更低功耗状态快速退出

- I/O：CMOS 模式，无端接，无 ODT， $Z_{OUT} = 48 \Omega$ （为了优化信号发送，建议对 DDRPHY 和 LPDDR2 使用）

- 将用于 DQS 消抖滤波的 DQS/DQS#上拉/下拉电阻设置为最大值 688  $\Omega$

- 当频率 > 200 MHz 时，DDRPHYC DLL 启用。当频率  $\leq 200$  MHz 时，DDRPHYC DLL 被旁路以减少功率耗散。

- ZQ 校准、SRX 后 ZQCL 和按固定间隔执行 ZQCS（高级用户选项）

- 低功耗选项：DDRCTRL 可以设置 ASR 和预充电掉电。

- DQSTRN 门控扩展用于补偿因缺少 DLL 导致的  $t_{DQSCK}$  变化。

- MR4 轮询（温度）默认使能。

当频率 > 200 MHz 时，DDRPHYC I/O 必须处于 SSTL 模式。

### 提示

## 6.3 频率范围限制

时钟频率必须满足以下条件：

- $10 \text{ MHz} \leq \text{CLK} \leq 100 \text{ MHz}$  (DDRPHYC DLL 为旁路模式且  $bp200 = 1$ )

- $100 \text{ MHz} < \text{CLK} \leq 200 \text{ MHz}$  (DDRPHYC DLL 为旁路模式且  $bp200 = 0$ )

- $200 \text{ MHz} < \text{CLK} \leq 533 \text{ MHz}$  (DDRPHYC DLL 启用)

## 6.4 输出阻抗

根据 MR3 寄存器设置 LPDDR2 I/O 阻抗，如下表所示。

表 15. LPDDR2 输出阻抗与 MR3 位 (RZQ = 240 Ω ± 1 %)

| MR3[3:0] | LPDDR2 $Z_{OUT}$ (Ω) |

|----------|----------------------|

| 0x0      | 保留                   |

| 0x1      | 34.3                 |

| 0x2      | 40 (默认)              |

| 0x3      | 48                   |

| 0x4      | 60                   |

| 0x5      | 68.6                 |

| 0x6      | 80                   |

| 0x7      | 120                  |

| 其它       | 保留                   |

为确保信号完整性 (SI) 并减少无端接接口的过冲，建议使  $Z_{OUT} = 48 \Omega$ 。

根据 DDRPHYC\_ZQ0CR1.ZPROG 设置 DDRPHYC I/O 阻抗，如下表所示。

表 16. 输出阻抗与 ZPROG 位 (RZQ = 240 Ω ± 1 %)

| ZPROG[3:0] | PHY $Z_{OUT}$ (Ω) |

|------------|-------------------|

| 0x0 至 0x4  | -                 |

| 0x5        | 80                |

| 0x6        | 69                |

| 0x7        | 60                |

| 0x8        | 53                |

| 0x9        | 48 (推荐值)          |

| 0xA        | 44                |

| 0xB        | 40 (默认)           |

| 0xC        | 37                |

| 0xD        | 34                |

| 0xE        | 32                |

| 0xF        | 30                |

## 6.5 命令/地址通道 (CA)

LPDDR2 命令和地址被编码到 CA [9:0] 线并使用 DDR 发送。

## 6.6 阻抗校准 (ZCAL)

对照外部板载  $R = 240 \Omega$  校准 DDRPHYC 和 LPDDR2 ZOUT。

ZCAL 总是在 DDR 初始化期间启动。随后，可以在 SRX 时触发和按固定时间间隔触发 ZCAL (高级用户)。ZCAL 支持输出驱动 ( $Z_{OUT}$ ) 校准。

ODT 不适用于 LPDDR2。

### 6.6.1 本地 PHY

ZCAL 在初始化期间自动触发且可以稍后由软件启动。

根据表 16 中的 ZPROG 值进行驱动器上拉和下拉。

### 6.6.2 DDR

LPDDR2 阻抗校准通过模式寄存器 (MR10) 命令发起。有四种 ZQ 校准命令，相关时序如下：

- tZQINIT 对应于初始化校准。

- tZQRESET 用于将 ZQ 复位至默认设置。参见模式寄存器 10 (MR10) 获取命令代码说明。

- ZQCL 命令用于长时间校准。该命令用于在上电初始化序列中执行初始校准。ZQCL 既可以通过 DDRPHYC 启动，也可以通过 DDRCTRL 稍后发出命令，具体取决于系统环境。ZQCL 耗时 256 个时钟周期。

- ZQCS 命令用于短时间校准。该命令可用于执行周期性校准，以应对电压和温度变化。ZQCS 由 DDRCTRL 按固定时间间隔发出，耗时 64 个时钟周期。

## 6.7 DDRPHYC 内置 DQSTRN

DDRPHYC 支持默认在初始化期间启动的硬件内置 DQSTRN。

DQSTRN 使用 DDR 阵列和读/写操作 (R/B/C, 默认为 0)。DQSTRN 完全由 DDRPHYC 寄存器控制：启动、R/B/C 使用、模式和状态报告。

#### 提示

在低频率下，DQSTRN 可以确定更少步骤。在不使用系统延迟 (SL) 和相移 (PS) 预确定值及 DQSTRN 的情况下，甚至可能有唯一有效步骤。这种情况下，直接使用预定义值设置 DXnDQSTR 和 DXnDQTR 寄存器或保留默认值 (对于 360° 移位，SL = 0 且 PS = 2)。

## 6.8 DQ 读眼图训练和位去时滞支持 (可选)

这些参数由软件控制，必须在设计初启时完成且与物理时序有关。训练值可以保存和恢复，以便取代默认值。

这些参数被加载到 DDRPHYC DXnDQTR/DQSTR 寄存器中，其中 n 表示字节通道。默认值可以在频率 ≤ 533 MHz 时使用，但可能不是最佳值 (DQ 去时滞的目的是补偿轻微的 PCB 通道不匹配)。

在被 DDRPHYC 接收时，DQS 和 DQ 信号的边缘默认对齐。

## 6.9 LPDDR2 配置示例

本例显示了具有一个 4-Gb LPDDR2 的板的 LPDDR2 配置。

时钟频率由 STM32CubeMx 时钟配置进行定义 (本例中为 528 MHz)。

DDR 类型和宽度在 STM32CubeMx 引脚排列和配置中进行定义。

本例中的值如下：

- DDR 类型：LPDDR2

- 宽度：32 位

- 密度：4 Gb

DDR 参数窗口中其他参数的设置如下 (通过滚动窗口菜单和勾选复选框)：

- 读取期间的阻抗：Ron 48 Ω (默认)

- 写入期间的阻抗：Ron 48 Ω (默认)

- 脉冲长度：8

- 地址映射配置：R/B/C

- 宽松时序模式：(复选框)

STM32CubeMx DDR 配置工具推荐并列出来自典型数据手册的 JEDEC 时序参数。如果与 LPDDR2 数据手册不一致，可以被覆盖。

#### 提示

LPDDR2 无档位。选择一组时序参数 (数据手册选择符 = 0)。根据频率自动选择 RL/WL。

根据以下接口宽度配置 PHY 字节通道：

- 16 位模式：字节通道 0/1 开启且字节通道 2/3 关闭

- 32 位模式：全部四个字节通道都开启

根据密度将系统地址灵活地映射到 DDR B/R/C。用户可以从以下两个预定义选项中选择一个：

- **R/B/C** (行/区/列, 默认设置), 使用区交叉, 以稍微优化性能但功耗更高

- **B/R/C** (区/行/列, 默认设置), 可以改善功耗, 但在发生区冲突时性能变差。

宽松时序模式可以用于内核时序的递增 (每次增加 1), 以便改善时序裕量。当存在可疑故障时, 必须执行递增。可以从 STM32CubeMX 中的预定义 **sched/QoS** 参数集选择 AXI 端口映射、QoS 设置和 DDRCTRL 调度器超时的值。

默认使用 QoS 类型 2, 它适用于大多数用例, 具有以下的特性:

- 队列抗饥饿支持

- 三种读流量类型 (**HPR/VPR/LPR**)

- **VPR** 过期的低超时

## 7

## LPDDR3 配置

与 LPDDR2 一样，当频率  $\leq 533$  MHz 时支持 LPDDR3，且无 ODT。

相比于 LPDDR2，LPDDR3 的限制很少：仅 BL8 且  $Z_{OUT}$  阻抗设置更少。

## 提示

**BL8** 是 LPDDR3 的强制条件。

更多详细信息，请参见[\[4\]](#)。

相比于频率，LPDDR3 的时序差异和 RL/WL 限制很少。此外，由于支持更高频率，LPDDR3 的一些模式寄存器值范围更大，在更低频率时有一些 RL/WL 限制（例如，支持 RL=3/WL=1（可选））。

LPDDR3 的特性如下：

- 无 DLL 且无复位引脚

- CMOS I/O (DDRPHYC 被配置为 I/O 置于 SSTL 模式)

- 10-533 MHz 连续范围工作

- 特殊低功耗特性：PASR，温度控制的自刷新

- 按区刷新（高级用户）

- MRR MR4 轮询和刷新 T 降额（默认设置）

- 深度掉电（DPD）模式（由于 DPD 期间 LPDDR2 的内容丢失，此模式的意义不大，在此不做讨论）

## 提示

根据 JEDEC209-3C，LPDDR3 有 x16 和 x32 的 1、2、4、6 和 8-Gbit 及更高密度的产品。但是，现有 LPDDR3 是所有可能配置的一小部分。配置工具中的例子使用的是最常见的配置 8-Gb 密度 x32。

## 8 STM32CubeMX 的 DDR 测试

STM32CubeMX 支持大量 DDR 测试套装，启动选中的测试可以确认 DDR 配置稳健性或捕获难以捉摸的潜在错误。测试描述见第 8.1 节。第 8.2 节 和 第 8.3 节 中指出了测试失败的不同原因和可能的纠正措施。第 8.4 节 中展示了完整的测试流程。

软件（包括测试）可以下载到 SRAM，并从 STM32CubeMX 控制执行。

STM32CubeMX 可提供关于测试目的、参数、最终限制和失败的潜在根本原因的大量在线信息。

### 8.1 测试说明

测试分为以下三种类型：

- **基础测试：**这些简单且快速运行的测试旨在发现快速消失的重要配置或硬件问题。

- **强化测试：**这些测试使用广泛覆盖数据和地址的模式测试噪声和 SSO 特性、高吞吐量或交叉读/写。测试运行时间可能较长，具体取决于参数。强化测试可采用渐进式部署，在启动较长的全面性测试序列前进行试测。

- **压力测试：**这些测试的强度加大，在条件收紧（例如频率稍微增加 10-20 MHz）、参数有时滞（例如细步长延迟增加）或使用特定的频率选择性模式的情况下执行。

这些测试旨在发现配置的低裕量问题，这些问题可能导致难以捉摸的错误，并最终在以后的运行中导致崩溃。

压力测试活动务必在系统初启期间执行。如果存在可疑故障，也可以运行压力测试。任何测试及其时滞参数必须以精确地找到观察到的故障为导向（例如，当错误与特定的位或字节有关时）。

下表详细列出了所有可用测试。

表 17. 测试列表

| 测试编号 | 测试名称       | 类型   | 说明                                                                        |

|------|------------|------|---------------------------------------------------------------------------|

| 1    | 简单数据总线     | 基本   | 确认每个数据总线信号都可以在给定地址驱动为高电平。                                                 |

| 2    | 数据总线走 0    | 基本   | 确认每个数据总线信号都可以驱动为低电平。                                                      |

| 3    | 数据总线走 1    | 基本   | 确认每个数据总线信号都可以驱动为高电平。                                                      |

| 4    | 地址总线       | 基本   | 通过对相关地址位执行走 1 测试和检查混叠来确认存储区中的每个地址总线。                                      |

| 5    | 存储设备       | 强化   | 对整个存储区执行读/写操作。使用值 0 和 1 写入并回读每个数据位。                                       |

| 6    | 同步切换输出     | 强化   | 通过执行同步切换输出在地址范围内对数据总线施压。写入一个伪随机数并读回。                                      |

| 7    | 噪声         | 强化   | 在强制切换所有数据总线的同时确认读/写操作。                                                    |

| 8    | 噪声脉冲       | 强化   | 在强制切换所有数据总线的同时确认读/写操作（基于 8 字脉冲的测试）。                                       |

| 9    | 随机         | 强化   | 在一个区域使用伪随机数确认读/写操作。                                                       |

| 10   | 频率选择性模式    | 强化加压 | 通过对 16 和 32 位数据总线宽度使用 0/1 模式和分频器模式（F/1、F/2 和 F/4）执行连续的写入 8 字脉冲操作，对数据总线施压。 |

| 11   | 连续块        | 强化   | 众所周知的用户空间存储器测试程序（经过修改）。                                                   |

| 12   | 棋盘         |      |                                                                           |

| 13   | 位扩展        |      |                                                                           |

| 14   | 位翻转        |      |                                                                           |

| 15   | 走 1        |      |                                                                           |

| 16   | 走 0        |      |                                                                           |

| 17   | 无限读取       | 基本   | 执行特定模式的无限读取（仅适用于调试和实验室使用，不可见）。                                            |

| 18   | 无限写入       | 基本   | 执行对 DDR 的无限写访问（仅适用于调试和实验室使用，不可见）。                                         |

| 任意   | 超频         | 强化加压 | 运行 1 级强化测试，DDR 时钟频率上升~5%（不超过 30 MHz）。                                     |

| 任意   | DQS 时序裕量检查 | 强化加压 | 运行 1 级强化测试，分步增加细步长 DQ 和 DQS 延迟。                                           |

## 8.2

## 故障分类

故障类型描述如下：

- 灾难性故障：**执行基础测试时发生的故障，通常是重大的配置或硬件问题导致的。原因可能或多或少地体现在测试报告中。

- 零星故障：**非强化测试导致的不频繁的故障。必须识别故障共性和模式，以便查明其根本原因（例如，它们可能影响特定的位或字节通道或可以对它们进行读取或写入）。

## 8.3 测试失败时的可能措施

最常用的措施是修改配置以纠正错误设置，或为参数增加更多裕量，然后重启测试序列。

如果测试失败与 **PHY** 时序裕量或环境条件有关，则必须更改配置设置并重新运行 **DDR** 初始化，包括 **ZCAL** 和 **DQSTRN**。

如果测试失败与读取期间特定的位或字节的时序有关，可以运行 **PHY** 调谐并对照之前的结果检查结果（**DQ** 和 **DQS** 细步长延迟设置）。

## 8.4 测试流程

整个流程如下图所示。

图 4. DDR 测试流程示意图

## 9 高级用户配置

下表列出了高级用户可以更改的一些功能和模式，附带它们的简短说明以及对 DDR 类型的适用性。修改 STM32CubeMx 推荐的默认值时要使用的寄存器可以在[1]中找到。

**提示** STM32CubeMX 支持 ASR/SRT 选项。默认通过 MR4 轮询检查温度降额。STM32CubeMx 支持非标准阻抗和 ODT。

表 18. 高级用户功能和参数

| 特性             | DDR3 | LPDDR2/3 | 说明                                                                                                                                                                     |

|----------------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 按存储区刷新         | 否    | 是        | $t_{RFCpb} < t_{RFCab}$<br>按区刷新快于所有区刷新。提高LPDDR2/3 DDR 系统延迟的可预测性。                                                                                                       |

| 脉冲刷新           | 是    | 是        | 将自动刷新命令分组（最多 9 个）的选项<br>延迟定期刷新以改善刷新命令的调度。                                                                                                                              |

| 非标准 BL         | 否    | 是        | 仅限 LPDDR2。LPDDR2 脉冲可以是 4、8 或 16。                                                                                                                                       |

| 脉冲斩波           | 是    | 否        | 脉冲斩波：BC4<br>用于提前终止脉冲（MSTR.BURSTCHOP 位）                                                                                                                                 |

| 灵活的地址映射        | 是    | 是        | 使用 RBC/BRC 扩展短选择列表<br>可以为行/区/列位交叉设定几乎任何位顺序，但不容易预见哪种设置更好。确定寄存器位的过程很繁琐。需使用地址边界检查测试程序确认寄存器设置。                                                                             |

| 自定义 QoS 设置     | 是    | 是        | AXI 互联层的默认 QoS 和端口映射集<br>提供标准 QoS 设置选择列表。                                                                                                                              |

| ASR/SRT        | 是    | 否        | $T_{CASE} > 85^{\circ}\text{C}$ 时适用，使刷新频率翻倍<br>基于 DDR 传感器 SRT/ASR 的 SRT 指导软件和 ASR 自动化是互斥的，由 DDR3 模式寄存器控制。                                                              |

| 温度降额           | 否    | 是        | $T_{CASE} > 85^{\circ}\text{C}$ 时适用，降低刷新频率<br>DDRCTRL 支持 MR4 的自动轮询。可以根据预计温度梯度设置轮询频率。使用 DERATEEN/DERATEINT 寄存器控制。LPDDR2/3 的默认间隔为~20 ms @400 MHz。                        |

| 非标准 ZQ 和 ODT 值 | 是    | 否        | 默认 DDR3 ZQ = 40 且 ODT = 60<br>DDR3 ZQ 可以设置为 34 或 40 欧姆。ODT 可以设置为关闭、120、60 或 40。通过模式寄存器更改 DDR 阻抗。DDRPHYC ZQ 和 ODT 由 ZQ0CR0/1 寄存器 ZPROG 控制。                              |

| 非标准 ODT 方案     | 是    | 否        | DDR RTT_nom 默认关闭且 RTT_wr = 60。DDPHY 动态 ODT。不建议更改这些设置。                                                                                                                  |

| 快速/慢速 PD 退出    | 是    | 否        | 目前 MR0[12] = 1。快速退出模式（PD 期间 DDR3 DLL 开启）                                                                                                                               |

| 自动 ZCAL        | 是    | 是        | 默认情况下，禁止以固定间隔执行 SRX 后 ZQCL 和 ZQCS。当存在在任务模式下或自刷新周期内可能导致 ZQ 超出范围 ( $> +/-10\%$ ) 的显著环境 (T) 变化时，可以使能这两种功能。                                                                |

| SRX 时的 ZCAL    | 是    | 是        | 对于 DDRPHYC，可通过软件管理自刷新退出时的 ZCAL 和按固定间隔执行的 ZCAL，但通常不需要这样做。按固定间隔执行的 ZCAL 可能增加 DDR 的不良系统延迟。                                                                                |

| 低功耗模式          | 是    | 是        | ASR1/HSR1 模式<br>DDRCTRL 低功耗计数器可用于跳变到掉电（时钟停止或不停止）和一段空闲时间后的自刷新。LPDDR2/3 也支持跳变到 DPD，但因 LPDDR2/3 内容的原因不使用。自动自刷新 ASR 适用于 DDR3。但是，相比于软件支持的自刷新（SSR），具有 ASR 的启发式方法不会带来显著的功耗节省。 |

| 特性             | DDR3 | LPDDR2/3 | 说明                                                                                                                                                                                                                                                         |

|----------------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDDRPHYC 自定义设置 | 是    | 是        | <p>DDDRPHYC 设置可以修改:</p> <ul style="list-style-type: none"><li>• <b>PHY 调谐:</b> DQ/DQS 细步长 (由调谐工具提供)</li><li>• <b>ZCAL 超控</b></li><li>• <b>特定功能和模式:</b> DQS 激活门控 (最后一次 DQS 下降时 DQS 门控关闭)</li><li>• <b>漂移补偿</b></li><li>• <b>DQS 门控扩展, 固定延迟/无泡</b></li></ul> |

## 版本历史

表 19. 文档版本历史

| 日期             | 版本 | 变更    |

|----------------|----|-------|

| 2019 年 2 月 6 日 | 1  | 初始版本。 |

## 目录

|              |                             |           |

|--------------|-----------------------------|-----------|

| <b>1</b>     | <b>概述</b>                   | <b>2</b>  |

| <b>2</b>     | <b>DDR 子系统初始化和配置</b>        | <b>3</b>  |

| <b>2.1</b>   | <b>DDRSS 和 SDRAM 初始化</b>    | <b>3</b>  |

| <b>2.2</b>   | <b>DDRCTRL 配置</b>           | <b>4</b>  |

| <b>2.3</b>   | <b>DDR 配置</b>               | <b>4</b>  |

| <b>2.4</b>   | <b>DDR PHY 调谐</b>           | <b>5</b>  |

| <b>2.5</b>   | <b>DDR 测试</b>               | <b>5</b>  |

| <b>3</b>     | <b>配置参数</b>                 | <b>6</b>  |

| <b>3.1</b>   | <b>系统参数</b>                 | <b>6</b>  |

| <b>3.2</b>   | <b>时序参数</b>                 | <b>6</b>  |

| <b>3.2.1</b> | <b>基础时序</b>                 | <b>6</b>  |

| <b>3.2.2</b> | <b>JEDEC 内核时序</b>           | <b>6</b>  |

| <b>3.2.3</b> | <b>次级时序</b>                 | <b>7</b>  |

| <b>3.3</b>   | <b>运行模式参数</b>               | <b>7</b>  |

| <b>3.3.1</b> | <b>低功耗模式设置</b>              | <b>7</b>  |

| <b>3.3.2</b> | <b>地址映射</b>                 | <b>7</b>  |

| <b>3.3.3</b> | <b>QoS (服务质量) 和调度</b>       | <b>7</b>  |

| <b>3.3.4</b> | <b>DDR 刷新控制器</b>            | <b>10</b> |

| <b>3.4</b>   | <b>PHY 调谐</b>               | <b>10</b> |

| <b>4</b>     | <b>配置序列和参数</b>              | <b>12</b> |

| <b>5</b>     | <b>DDR3/3L 配置</b>           | <b>13</b> |

| <b>5.1</b>   | <b>关于 DDR3/3L 的一般注意事项</b>   | <b>13</b> |

| <b>5.2</b>   | <b>DDR3 上电序列、初始化和 ZQ 校准</b> | <b>14</b> |

| <b>5.3</b>   | <b>频率范围限制</b>               | <b>14</b> |

| <b>5.4</b>   | <b>片内端接 (ODT)</b>           | <b>14</b> |

| <b>5.5</b>   | <b>命令/地址通道 (CA) 端接</b>      | <b>16</b> |

| <b>5.6</b>   | <b>阻抗校准 (ZCAL)</b>          | <b>16</b> |

| <b>5.6.1</b> | <b>PHY</b>                  | <b>16</b> |

| <b>5.6.2</b> | <b>DRAM</b>                 | <b>16</b> |

|       |                                |    |

|-------|--------------------------------|----|

| 5.7   | DLL 开启/关闭模式 . . . . .          | 17 |

| 5.8   | DDRPHYC 内置 DQSTRN . . . . .    | 17 |

| 5.9   | DQ 读眼图训练和位去时滞支持 (可选) . . . . . | 17 |

| 5.10  | DDR3 配置示例 . . . . .            | 17 |

| 6     | LPDDR2 配置 . . . . .            | 21 |

| 6.1   | 关于 LPDDR2 的一般注意事项 . . . . .    | 21 |

| 6.2   | LPDDR2 上电、初始化和 ZQ 校准 . . . . . | 22 |

| 6.2.1 | LPDDR2 初始化序列 . . . . .         | 22 |

| 6.2.2 | LPDDR2 特有的设置 . . . . .         | 21 |

| 6.3   | 频率范围限制 . . . . .               | 22 |

| 6.4   | 输出阻抗 . . . . .                 | 23 |

| 6.5   | 命令/地址通道 (CA) . . . . .         | 23 |

| 6.6   | 阻抗校准 (ZCAL) . . . . .          | 23 |

| 6.6.1 | 本地 PHY . . . . .               | 24 |

| 6.6.2 | DDR . . . . .                  | 24 |

| 6.7   | DDRPHYC 内置 DQSTRN . . . . .    | 24 |

| 6.8   | DQ 读眼图训练和位去时滞支持 (可选) . . . . . | 24 |

| 6.9   | LPDDR2 配置示例 . . . . .          | 24 |

| 7     | LPDDR3 配置 . . . . .            | 26 |

| 8     | STM32CubeMX 的 DDR 测试 . . . . . | 27 |

| 8.1   | 测试说明 . . . . .                 | 27 |

| 8.2   | 故障分类 . . . . .                 | 28 |

| 8.3   | 测试失败时的可能措施 . . . . .           | 29 |

| 8.4   | 测试流程 . . . . .                 | 29 |

| 9     | 高级用户配置 . . . . .               | 30 |

|       | 版本历史 . . . . .                 | 32 |

|       | 目录 . . . . .                   | 33 |

|       | 表一览 . . . . .                  | 35 |

|       | 图一览 . . . . .                  | 36 |

## 表一览

|       |                                                  |    |

|-------|--------------------------------------------------|----|

| 表 1.  | 总线主设备 AXI 端口分配和 QoS 值 . . . . .                  | 6  |

| 表 2.  | QoS 和调度参数 . . . . .                              | 7  |

| 表 3.  | 每个 AXI 端口的 QoS 设置. . . . .                       | 8  |

| 表 4.  | DDRCTRL 调度和性能控制寄存器 . . . . .                     | 9  |

| 表 5.  | DDR3 密度和拓扑 . . . . .                             | 12 |

| 表 6.  | DDR3 数据手册的速度等级/速度档位预定值 . . . . .                 | 12 |

| 表 7.  | CL/CWL 与频率及数据手册预定值 . . . . .                     | 13 |

| 表 8.  | ODT 阻抗与 ZPROG 位 (RZQ = 240 Ω ± 1 %) . . . . .    | 14 |

| 表 9.  | 输出阻抗与 ZPROG 位 (RZQ = 240 Ω ± 1 %) . . . . .      | 15 |

| 表 10. | DDRCTRL 和 DDRPHYC 时序寄存器值 . . . . .               | 17 |

| 表 11. | DDRCTRL 和 DDRPHYC 常量寄存器值与 DDR3 . . . . .         | 18 |

| 表 12. | DDR3 的 DDRCTRL 地址映射寄存器值. . . . .                 | 19 |

| 表 13. | DDR3 的 DDRCTRL QoS 调度寄存器值 . . . . .              | 19 |

| 表 14. | LPDDR2 密度和拓扑 . . . . .                           | 20 |

| 表 15. | LPDDR2 输出阻抗与 MR3 位 (RZQ = 240 Ω ± 1 %) . . . . . | 22 |

| 表 16. | 输出阻抗与 ZPROG 位 (RZQ = 240 Ω ± 1 %) . . . . .      | 22 |

| 表 17. | 测试列表. . . . .                                    | 27 |

| 表 18. | 高级用户功能和参数. . . . .                               | 29 |

| 表 19. | 文档版本历史 . . . . .                                 | 31 |

## 图一览

|      |                         |    |

|------|-------------------------|----|

| 图 1. | DDR 子系统 . . . . .       | 3  |

| 图 2. | DDRPHYC 初始化序列 . . . . . | 3  |

| 图 3. | DDR 初始化序列 . . . . .     | 3  |

| 图 4. | DDR 测试流程示意图. . . . .    | 28 |

IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to [www.st.com/trademarks](http://www.st.com/trademarks). All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2019 STMicroelectronics – All rights reserved