## 引言

本应用笔记提供如何在STM32MP1系列应用程序PCB上实现DDR3、DDR3L、LPDDR2、LPDDR3内存接口的指南。它提供了接口原理图、布局实现规则和最佳实践。

# 目录

|          |                                     |           |

|----------|-------------------------------------|-----------|

| <b>1</b> | <b>设计界面约束 . . . . .</b>             | <b>6</b>  |

| <b>2</b> | <b>内存架构选项 . . . . .</b>             | <b>7</b>  |

| 2.1      | 32位DDR3/DDR3L接口 . . . . .           | 7         |

| 2.2      | 16位DDR3/DDR3L接口 . . . . .           | 8         |

| 2.3      | 32位LPDDR2/LPDDR3接口 . . . . .        | 10        |

| 2.4      | 16位LPDDR2/LPDDR3接口 . . . . .        | 10        |

| <b>3</b> | <b>DDR3/DDR3L原理图实现 . . . . .</b>    | <b>12</b> |

| 3.1      | 标准fly-by拓扑 . . . . .                | 12        |

| 3.2      | 成本优化的点对点拓扑 . . . . .                | 12        |

| 3.3      | 其它信号 . . . . .                      | 12        |

| 3.4      | 电源和参考电压 . . . . .                   | 13        |

| <b>4</b> | <b>LPDDR2/LPDDR3原理图实现 . . . . .</b> | <b>14</b> |

| 4.1      | 点对点拓扑 . . . . .                     | 14        |

| 4.2      | 其它信号 . . . . .                      | 14        |

| 4.3      | 电源和参考电压 . . . . .                   | 14        |

| <b>5</b> | <b>PCB设计考虑因素 . . . . .</b>          | <b>16</b> |

| 5.1      | 走线隔离距离 . . . . .                    | 16        |

| 5.2      | 长度均衡 . . . . .                      | 17        |

| 5.3      | 阻抗 . . . . .                        | 18        |

| 5.4      | 四层板的层分配 . . . . .                   | 18        |

| 5.5      | VDD_DDR电源平面规范 . . . . .             | 18        |

| 5.6      | 换层电容器 . . . . .                     | 19        |

| 5.7      | 去耦电容器类型 . . . . .                   | 20        |

| 5.8      | 使用去耦电容器的高频电容使连接电感 . . . . . 最小化     | 21        |

| 5.8.1    | 在顶层放置电容器 . . . . .                  | 21        |

| 5.8.2    | 在底层放置电容器 . . . . .                  | 22        |

| <b>6</b> | <b>内存布局规则 . . . . .</b>             | <b>24</b> |

---

|       |                                       |    |

|-------|---------------------------------------|----|

| 6.1   | 32位内存接口的数据信号规则 .....                  | 24 |

| 6.2   | 16位内存接口的数据信号规则 .....                  | 25 |

| 6.3   | 地址和控制（A/C）信号规则 .....                  | 25 |

| 6.4   | ZQ 信号 .....                           | 26 |

| 6.5   | 电源平面规则 .....                          | 26 |

| 6.5.1 | VDD_DDR（VDD_DDR2对应LPDDR2/3）电源平面 ..... | 26 |

| 6.5.2 | VTT电源平面规则 .....                       | 27 |

|       | 版本历史 .....                            | 28 |

## 表格索引

|     |                          |    |

|-----|--------------------------|----|

| 表1. | STM32MP1系列封装总览 . . . . . | 7  |

| 表2. | 文档版本历史 . . . . .         | 28 |

| 表3. | 中文文档版本历史 . . . . .       | 28 |

## 图片目录

|      |                                               |    |

|------|-----------------------------------------------|----|

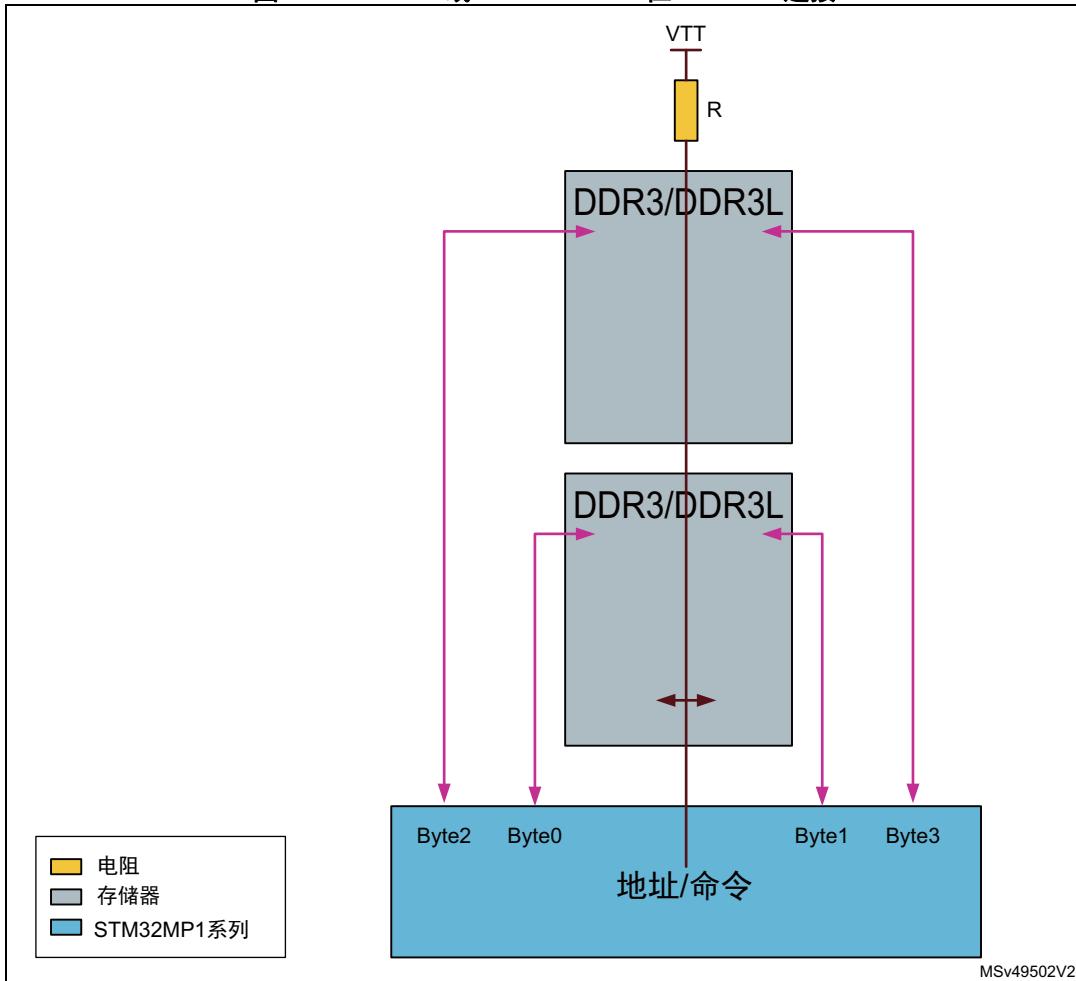

| 图1.  | LFBGA448或TFBGA361 32位DDR3/3L连接 . . . . .      | 7  |

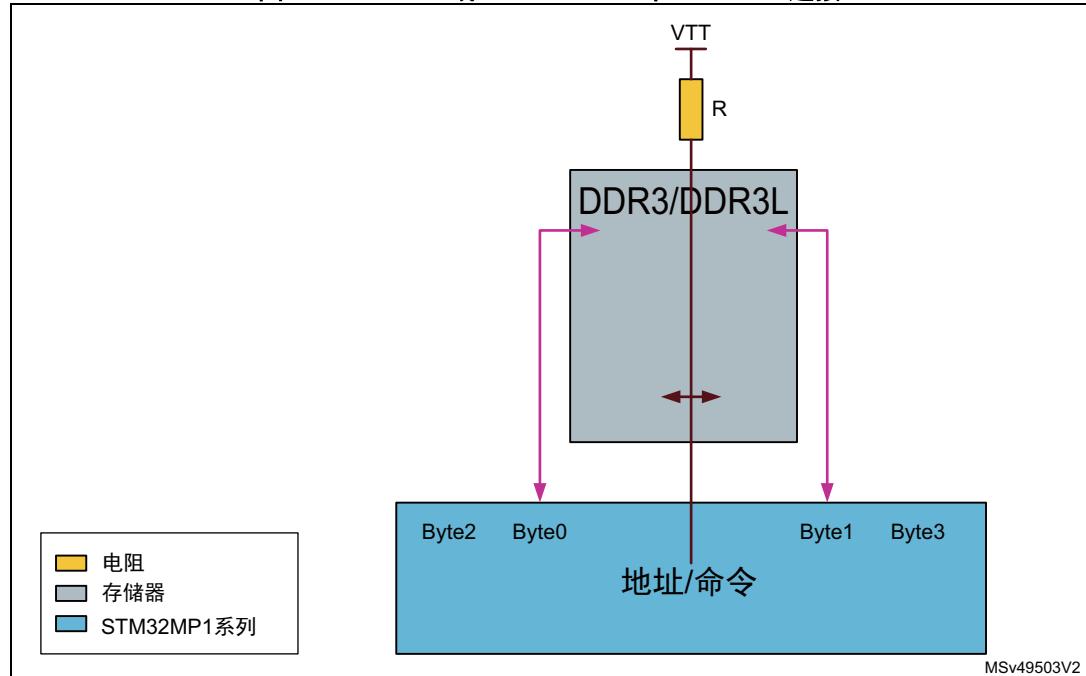

| 图2.  | LFBGA448或TFBGA361 16位DDR3/3L连接 . . . . .      | 8  |

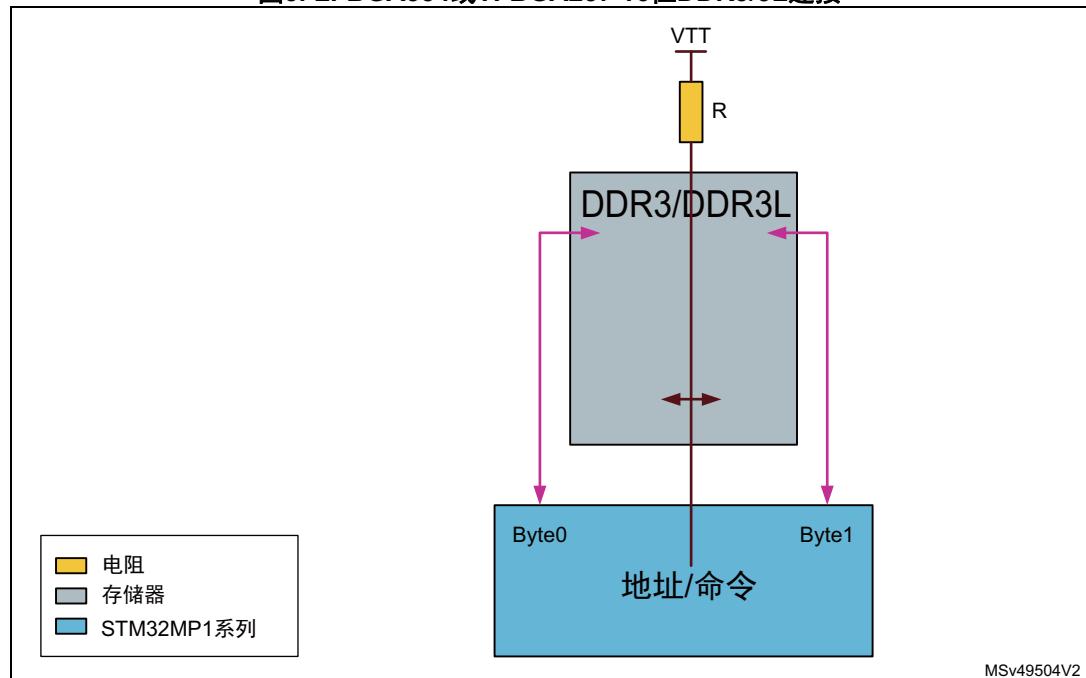

| 图3.  | LFBGA354或TFBGA257 16位DDR3/3L连接 . . . . .      | 8  |

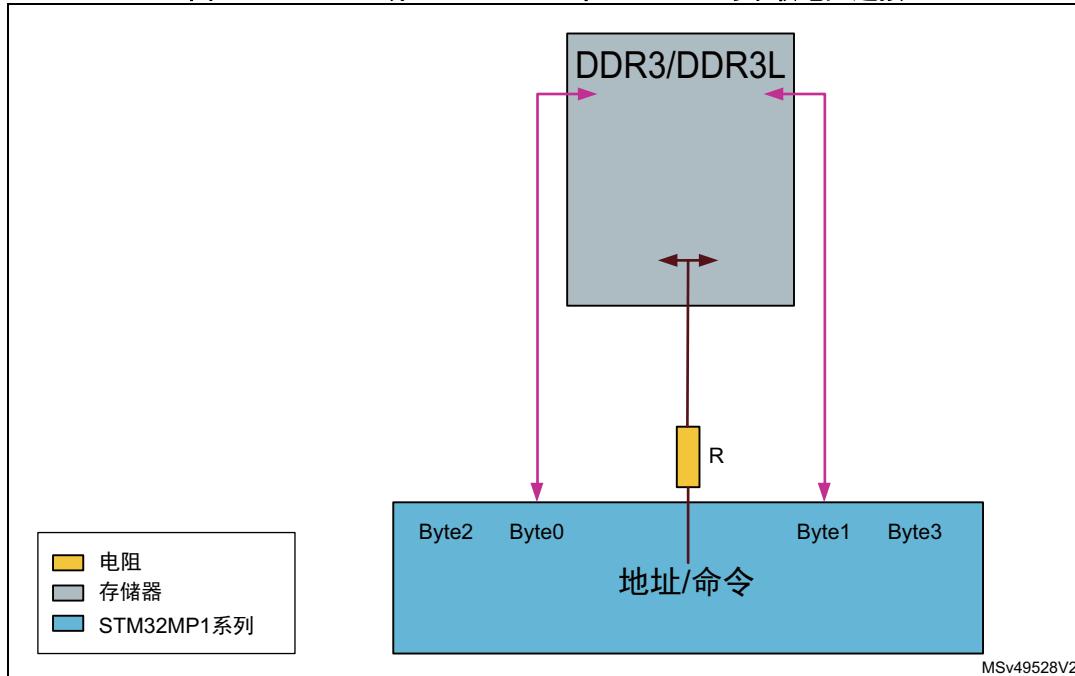

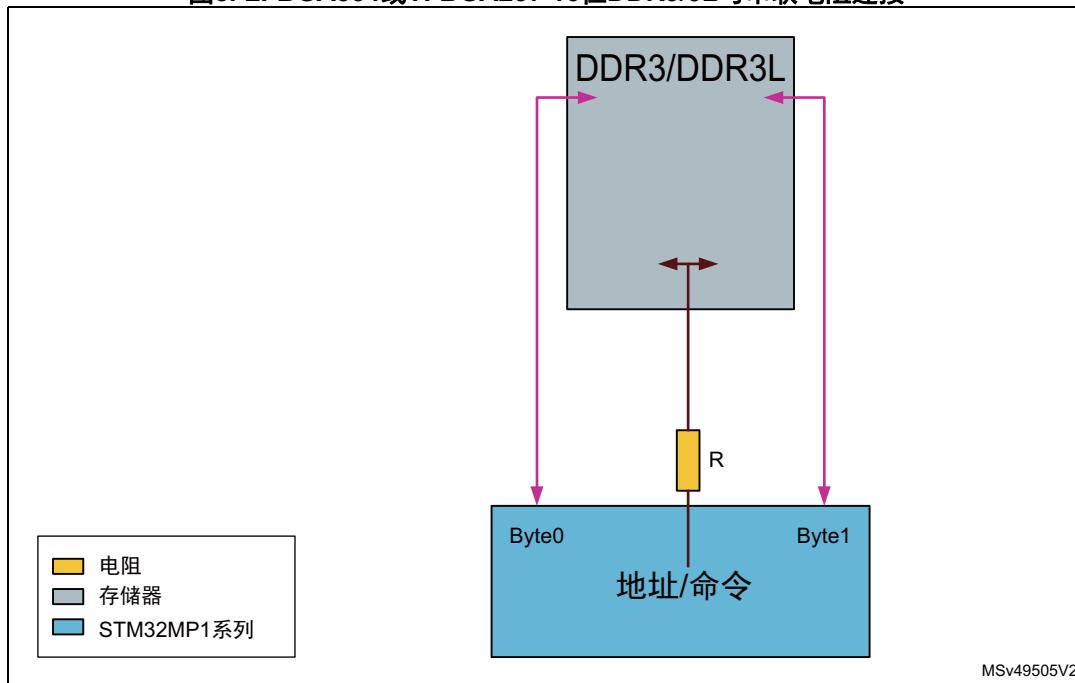

| 图4.  | LFBGA448或TFBGA361 16位DDR3/3L与串联电阻连接 . . . . . | 9  |

| 图5.  | LFBGA354或TFBGA257 16位DDR3/3L与串联电阻连接 . . . . . | 9  |

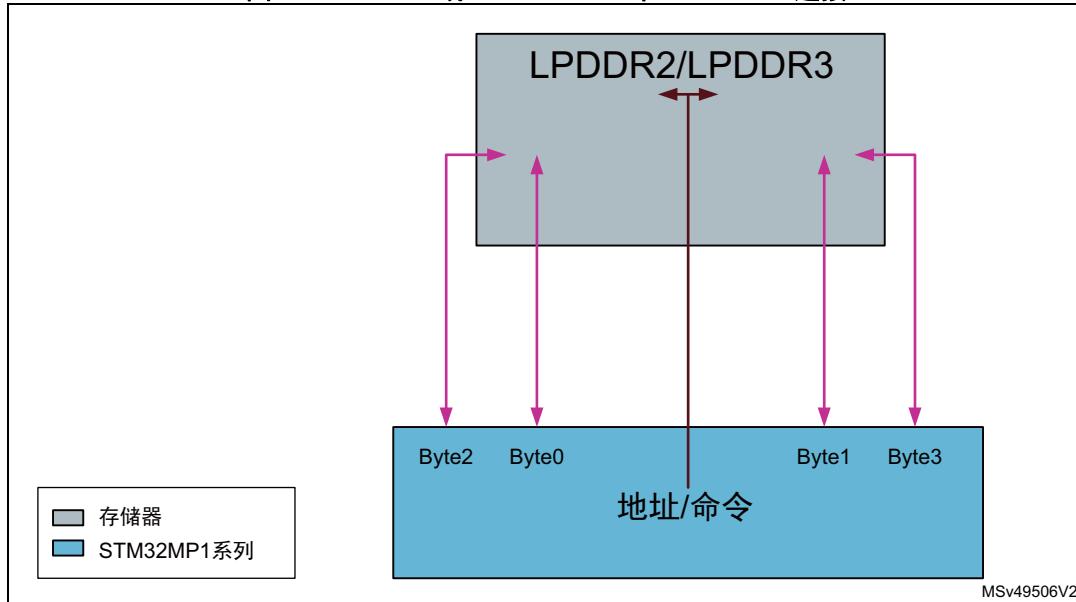

| 图6.  | LFBGA448或TFBGA361 32位LPDDR2/3连接 . . . . .     | 10 |

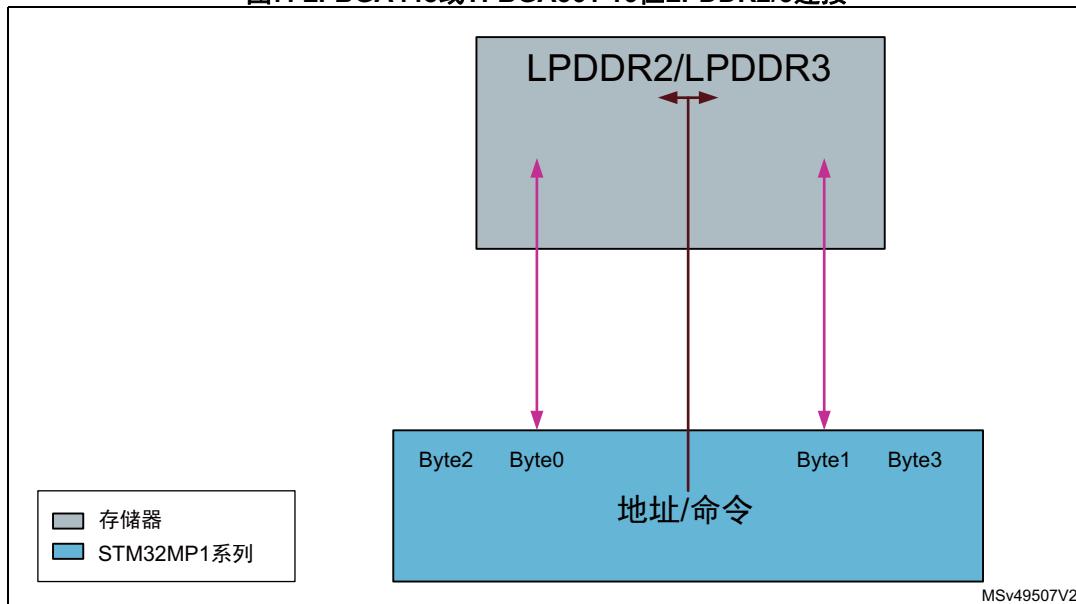

| 图7.  | LFBGA448或TFBGA361 16位LPDDR2/3连接 . . . . .     | 10 |

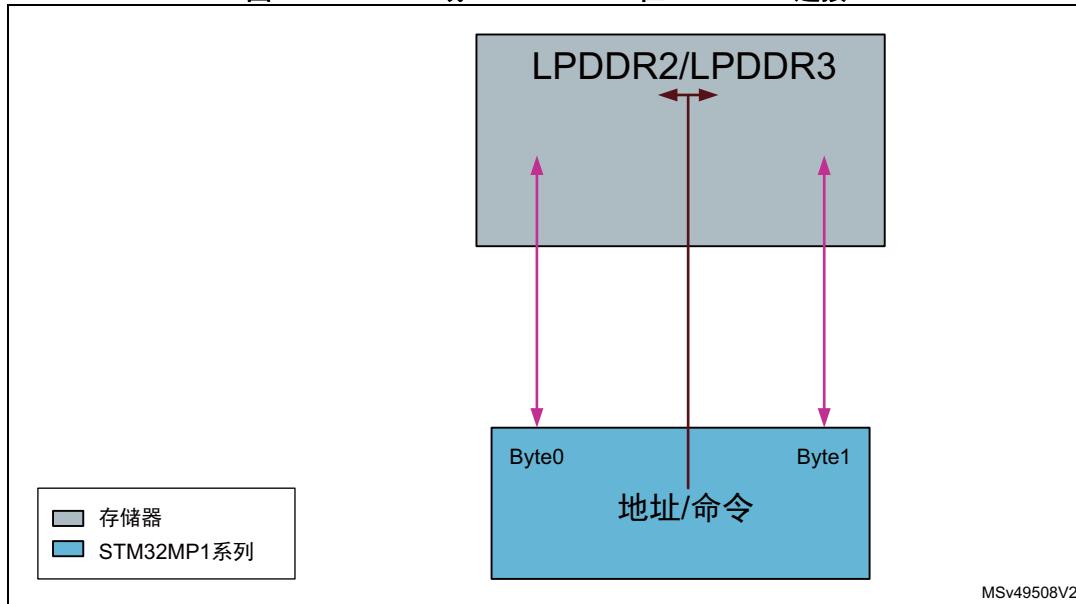

| 图8.  | LFBGA354或TFBGA257 16位LPDDR2/3连接 . . . . .     | 11 |

| 图9.  | S-3S隔离规则插图 . . . . .                          | 16 |

| 图10. | 长度均衡模式 . . . . .                              | 17 |

| 图11. | DDR3L A/C信号布局及相应电源平面示例 . . . . .              | 19 |

| 图12. | 使用换层电容器 . . . . .                             | 20 |

| 图13. | 在顶层放置一个高频电容器 . . . . .                        | 22 |

| 图14. | 置于底层的高频电容器 . . . . .                          | 22 |

| 图15. | 在底层放置一个高频电容器 . . . . .                        | 23 |

| 图16. | VTT电源平面孤岛布局 . . . . .                         | 27 |

## 1 设计界面约束

STM32MP1系列是基于Arm<sup>®(a)</sup> Cortex<sup>®</sup>处理器的STM32 32位器件。

STM32MP1系列内存接口可以满足不同类型的内存需要：

- 数据速率为1066Mbps的DDR3和DDR3L，电压为1.5V的DDR3和1.35V的DDR3L。更多关于DDR3 SDRAM的信息可以在JEDEC DDR3 SDRAM标准JESD79-3F上找到。

- LPDDR2和LPDDR3的数据速率为1066 Mbps，电压为1.2 V。更多关于LPDDR2和LPDDR3的信息可以在JEDEC LPDDR2标准JESD209-2F和JEDEC LPDDR3标准JESD209-3C上找到。

低电压和高数据速率有助于在读眼图开启方面获得更窄的偏差，也可能使系统更加不稳定。

因此，在使用内存接口时，需要考虑许多约束和设计敏度。例如：

大多数信号是单端信号，只有时钟信号是差分信号。

信号可以点对点连接，也可以采用fly-by拓扑。

由于板尺寸不断减小，在设计DDR接口时存在一些挑战，这可能会对接口造成性能限制。

此外，由于STM32MP1系列和内存器件接口上的DDR连接都是固定的，因此在物理布局方面的灵活性可能非常有限。

- 需要维持最小数量的信号路由，不能进一步减少。

- 需要管理阻抗约束。

为了确保正确的信号和电源完整性，必须遵守走线隔离、长度均衡、配电、去耦和阻抗匹配等基本设计规则。

本文档列出了必须应用的规则，以便在4层PCB中实现最先进的内存接口。

意法半导体强烈建议继续沿用意法半导体参考设计的布局。

这些布局已经过考验，并被证明是稳定可靠的。

arm

---

a. Arm是Arm Limited（或其子公司）在美国和其他地区的注册商标。

## 2 内存架构选项

有几个选项可能与内存的封装和类型有关：

表1. STM32MP1系列封装总览

| 封装类型     | TFBGA257<br>(10 × 10 mm) | LFBGA354<br>(16 × 16 mm) | TFBGA361<br>(12 × 12 mm) | LFBGA448<br>(18 × 18 mm) |

|----------|--------------------------|--------------------------|--------------------------|--------------------------|

| 16/32位接口 | -                        | -                        | X                        | X                        |

| 16位接口    | X                        | X                        | -                        | -                        |

### 2.1 32位DDR3/DDR3L接口

对于32位DDR3或DDR3L接口，在fly-by拓扑中使用两个16位DDR3/3L。

图1. LFBGA448或TFBGA361 32位DDR3/3L连接

这种设计的优点是，它可以驱动1GB内存（2 \* 4 Gbits），但需要更大的PCB体积。

## 2.2 16位DDR3/DDR3L接口

对于16位DDR3或DDR3L接口，使用一个16位DDR3/3L。

通过这种配置，它可以驱动高达1 Gb的内存（ $1 * 8 \text{ Gbits}$ ）。

在32位接口上，只使用字节0和1，让字节2和3不连接。

图2. LFBGA448或TFBGA361 16位DDR3/3L连接

图3. LFBGA354或TFBGA257 16位DDR3/3L连接

连接一个DDR3/3L的其他可能性：如果终端电阻没有使用，在每个地址和接近STM32MP1系列的命令行上串联电阻。

图4. LFBGA448或TFBGA361 16位DDR3/3L与串联电阻连接

图5. LFBGA354或TFBGA257 16位DDR3/3L与串联电阻连接

## 2.3 32位LPDDR2/LPDDR3接口

对于32位LPDDR接口，在点对点连接中使用一个32位LPDDR2/3。

图6. LFBGA448或TFBGA361 32位LPDDR2/3连接

## 2.4 16位LPDDR2/LPDDR3接口

对于16位LPDDR接口，在点对点连接中使用一个16位LPDDR2/3。

在32位接口上，只使用字节0和1，让字节2和3不连接。

图7. LFBGA448或TFBGA361 16位LPDDR2/3连接

图8. LFBGA354或TFBGA257 16位LPDDR2/3连接

## 3 DDR3/DDR3L原理图实现

DDR实现应包含以下要素。

### 3.1 标准fly-by拓扑

标准fly-by拓扑包含：

- 分布式A/C总线，VTT (VDD\_DDR/2) 端56 Ω板载终端电阻

- 差分时钟，分给所有DDR器件

- 使用一个100 Ω电阻实现CLK\_N/CLK\_P信号的差分端接。

- 必须有一个数据总线的点对点连接（4个可交换字节，同一个字节中的可交换位），包括：

- 32数据信号位 (DQ)

- 4个数据屏蔽信号 (DQMx)

- 4个差分时钟 (DQSx\_N/DQSx\_P)

### 3.2 成本优化的点对点拓扑

如果有单DDR芯片接口，可以使用这种拓扑。它包括：

- 每个A/C总线的点对点连接，没有板载端接

- 建议为DDR芯片的每个A/C使用33 Ω串联电阻，以减少反射

- 通过一个100 Ω电阻对CLK\_N/CLK\_P信号进行差分端接。

- 数据总线的点对点连接（2个可交换字节，同一个字节中的可交换位）

- 16数据信号位 (DQ)

- 2个数据屏蔽信号 (DQMx)

- 2个差分时钟 (DQSx\_N/DQSx\_P)

### 3.3 其它信号

此外，在原理图中还应包括下列信号：

- DDR\_RESETN

DDR\_RESETN是从DDR控制器到DDR器件的异步低速复位信号。需要一个10kΩ下拉电阻。该信号在通电期间或需要复位时被驱动为低电平。否则，默认情况下信号应该被驱动为高电平。

- ZQ

为了进行DDR阻抗校准，该信号要求在信号球和接地之间按如下方式放置电阻：

- 必须在每个DDR芯片上的ZQ球和接地平面之间放置一个 $240\Omega$  (+/- 1%) 电阻。

- STM32MP1系列器件的ZQ球和接地平面之间也必须放置一个 $240\Omega$  (+/- 1%) 电阻。

- CKE

CKE在DRAM上启用（注册为高）和禁用（注册为低）内部电路和时钟。需要一个 $10\text{ k}\Omega$ 下拉电阻。

## 3.4 电源和参考电压

必须提供以下电源和参考电压元件：

- VREF参考电压（相当于VDD\_DDR /2）

这是STM32MP1系列和DDR3/3L器件所需的参考电压，以确保正确采样A/C和数据信号。其噪声等级必须保持非常低的水平，正如在JEDEC标准中描述的那样。

建议的两种解决方案：

- 为每个器件配备独立的VREF发生器（VREFCA、VREFDQ）。

每个VREF发生器基于一个 $2\text{ k}\Omega$  (+/- 1%) 电阻桥（来自VDD\_DDR）和一个本地 $100\text{ nF}$ 去耦电容器。

产生的参考电压VREF应尽可能接近其相应的信号球。

- 每个器件的通用VREF。

来自外部IC的VREF发生器与一个本地 $100\text{ nF}$ 去耦电容器一起提供给每个器件。

STPMIC可以提供VREF。

- VTT电源（相当于VDD\_DDR /2）

VTT电源仅用于使用fly-by拓扑的DDR3/3L接口。

这是地址和控制（A/C）信号的端接电压。

建议使用外部VTT电压发生器。STPMIC可以提供VTT。

需要很强的VTT去耦，尽可能接近终端电阻。

- VDD\_DDR电源平面

这是DDR接口电源，相当于面向DDR3的 $1.5\text{ V}$ （ $1.425\text{--}1.575\text{ V}$ ）或面向DDR3L的 $1.35\text{ V}$ （ $1.283\text{--}1.45\text{ V}$ ）。

对于DDR和STM32MP1系列，该平面需要与接地平面相关的强制去耦电容器，以及靠近每个电源引脚的大容量电容器和高频电容器。

## 4 LPDDR2/LPDDR3原理图实现

LPDDR2/3实现应包含以下要素。

### 4.1 点对点拓扑

标准点对点拓扑包含：

- 分布式12 A/C信号

- 差分时钟，使用一个 $100\ \Omega$ 电阻实现实现CLK\_N/CLK\_P信号的差分端接。

- 必须有一个数据总线的点对点连接（32位LPDDR2/3为4字节，16位LPDDR2/3为2字节），包括：

- 32数据信号位（DQ）。LPDDR2/3的字节0必须连接到STM32MP1系列的字节0，但是不能在该字节内交换位。其他3个字节是可交换的，同一字节中的位也是可交换的。

- 4个数据屏蔽信号（DQMx）。

- 4个差分时钟（DQSx\_N/DQSx\_P）。

### 4.2 其它信号

此外，在原理图中还应包括下列信号：

- ZQ

为了进行LPDDR2/3阻抗校准，该信号要求在信号球和接地之间按如下方式放置电阻：

- 必须在LPDDR2/3芯片上的ZQ球和接地平面之间放置一个 $240\Omega$  (+/- 1%) 电阻。

- STM32MP1系列器件的ZQ球和接地平面之间也必须放置一个 $240\Omega$  (+/- 1%) 电阻。

- CKE

CKE在DRAM上启用（注册为高）和禁用（注册为低）内部电路和时钟。需要一个 $10\ k\Omega$ 下拉电阻。

### 4.3 电源和参考电压

必须提供以下电源和参考电压元件：

- VREF参考电压（相当于VDD2\_DDR /2）

这是STM32MP1系列和LPDDR2/3器件所需的参考电压，以确保正确采样A/C和数据信号。其噪声等级必须保持非常低的水平，正如在JEDEC标准中描述的那样。

建议的两种解决方案：

- 独立VREF发生器（VREFCA、VREFDQ）。

每个VREF发生器基于一个 $2\ k\Omega$  (+/- 1%) 电阻桥（来自VDD2\_DDR）和一个本地

100 nF去耦电容器。

产生的参考电压VREF应尽可能接近其相应的球。

- 通用VREF（VREFCA、VREFDQ）。

来自外部IC的VREF发生器与一个本地100 nF去耦电容器一起提供给LPDDR2/3。STPMIC可以提供VREF。

- VDD2\_DDR电源平面

这是LPDDR2/3接口电源，相当于1.2 V（1.14-1.30 V）。

对于LPDDR2/3和STM32MP1系列，该平面需要与接地平面相关的强制去耦电容器，以及靠近每个电源引脚的大容量电容器和高频电容器。

- VDD1\_DDR电源

这是LPDDR2/3的核心电源，相当于1.8 V（1.7-1.95 V）。

## 5 PCB设计考虑因素

下面将详细介绍PCB设计的基本考虑因素。这是一个非详尽列表，涉及敏感信号设计中需要遵循的良好实践。

### 5.1 走线隔离距离

必须在每处走线周围提供最小的隔离距离，以减少由邻近走线（有时称为“入侵者”）引起的串扰、故障和抖动。

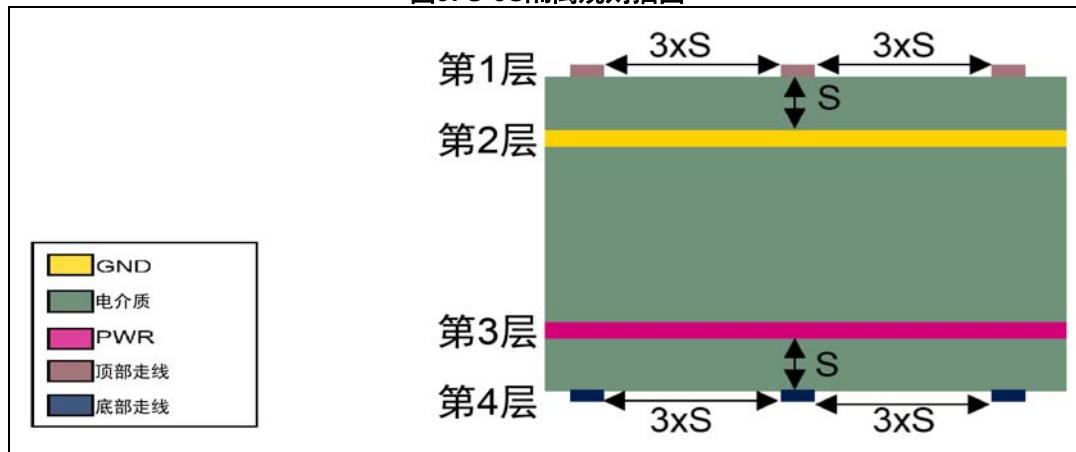

#### S-3S隔离规则

如果S是走线与其参考平面（与顶层走线对应的GND平面，与底层走线对应的电源平面）之间的距离，如果走线与其直接邻居之间的距离大于或等于 $3 \times S$ ，则可以说该走线处于隔离状态。[图 9](#)显示了此规则的实际应用。

图9. S-3S隔离规则插图

换句话说，S-3S是最小隔离/间隔规则。

如果走线之间有更大的间隔可用，它必须被用来传输信号（S-4S、S-10S...）。走线之间的间隔越大，信号隔离和噪声抗扰性越好。

由于扇出约束，S-3S规则不适用于BGA器件覆盖的区域（内存和STM32MP1系列）。

当S-3S规则不适用时，与该规则相冲突的分段长度必须最小化。

必须尽量避免使用S-1S布局。如果S-3S规则不适用，尽可能最大化走线之间的距离（S-2S规则）比使用S-1S布局更可取。

## 5.2 长度均衡

同一组信号在到达目的地时，必须具有匹配的设置和保持时间。因此，可能需要走线长度均衡，以便满足这些时序约束。

必须考虑整个信号通路（从STM32MP1系列芯片到存储芯片），以及封装和PCB长度。

对于数据信号，内部延迟调整能力可排除或减少长度均衡方面的要求。

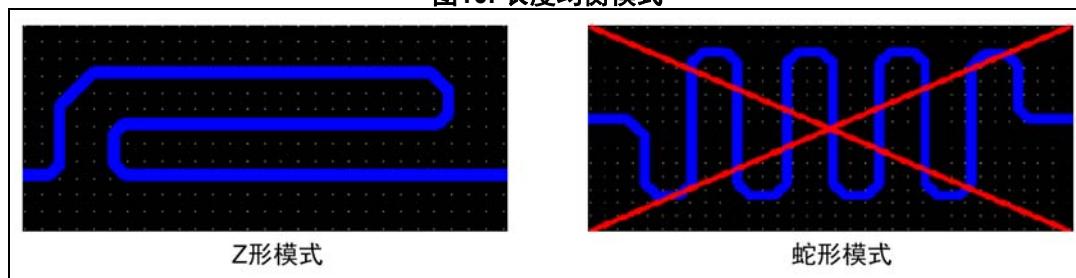

长度均衡模式

当路由走线以均衡长度时，某些模式应优先于其他模式。例如，不推荐使用蛇形走线，因为它们可能引发正交传播，从而损害信号的完整性。

最好采用Z形模式。

图10. 长度均衡模式

S-3S隔离规则也必须适用于均衡模式，这意味着相同走线各部分之间的最小距离应大于或等于S-3S。

如果是差分信号：

- 不允许对内长度均衡

- N和P之间的间隔必须是恒定的

- 对于差分对，应考虑N和P信号的平均值长度：

$$L_{sig} = \frac{L_{sigN} + L_{sigP}}{2}$$

意法半导体的模板和长度均衡表可帮助简化信号走线长度均衡任务。这些表包括封装的走线长度。请联系您当地的意法半导体销售办事处获取相关信息。

## 5.3 阻抗

一般来说，驱动阻抗（ZDRV）通常是 $34\Omega$ 或 $40\Omega$ ，而片内终端阻抗（ZODT）通常是 $60\Omega$ 。板阻抗必须控制，以根据走线几何参数（宽度和间距）和板的堆叠保证适当的传输线设置。对于DDR3/3L和LPDDR2/3接口，意法半导体建议使用以下阻抗：

- 对于单端信号： $55\Omega \pm 10\%$ 。

- 对于差分信号： $100\Omega$  差分  $\pm 10\%$ 。

## 5.4 四层板的层分配

层的分配和实现必须如下所述，没有例外：

- 顶层

- 该层专用于那些具有最高灵敏度的走线。

- 走线以统一的内部接地（GND）平面为参考点。

- 没有阻抗中断。

- 有噪声的电源不允许有耦合。

- 2层（GND）内层

- 该层是统一的内部接地（GND）平面。

- 它必须通过一个通孔矩阵连接到顶部和底部的GND区域。

- 3层（VDD\_DDR对应于DDR3/3L，或VDD\_DDR2对应于LPDDR2/3）内层

- 该层是专用电源平面，为板上配电单元供电。

- 底层

- 这是用于走线的第二信号层。由于参考电源平面的不连续，该层可能会有阻抗中断。

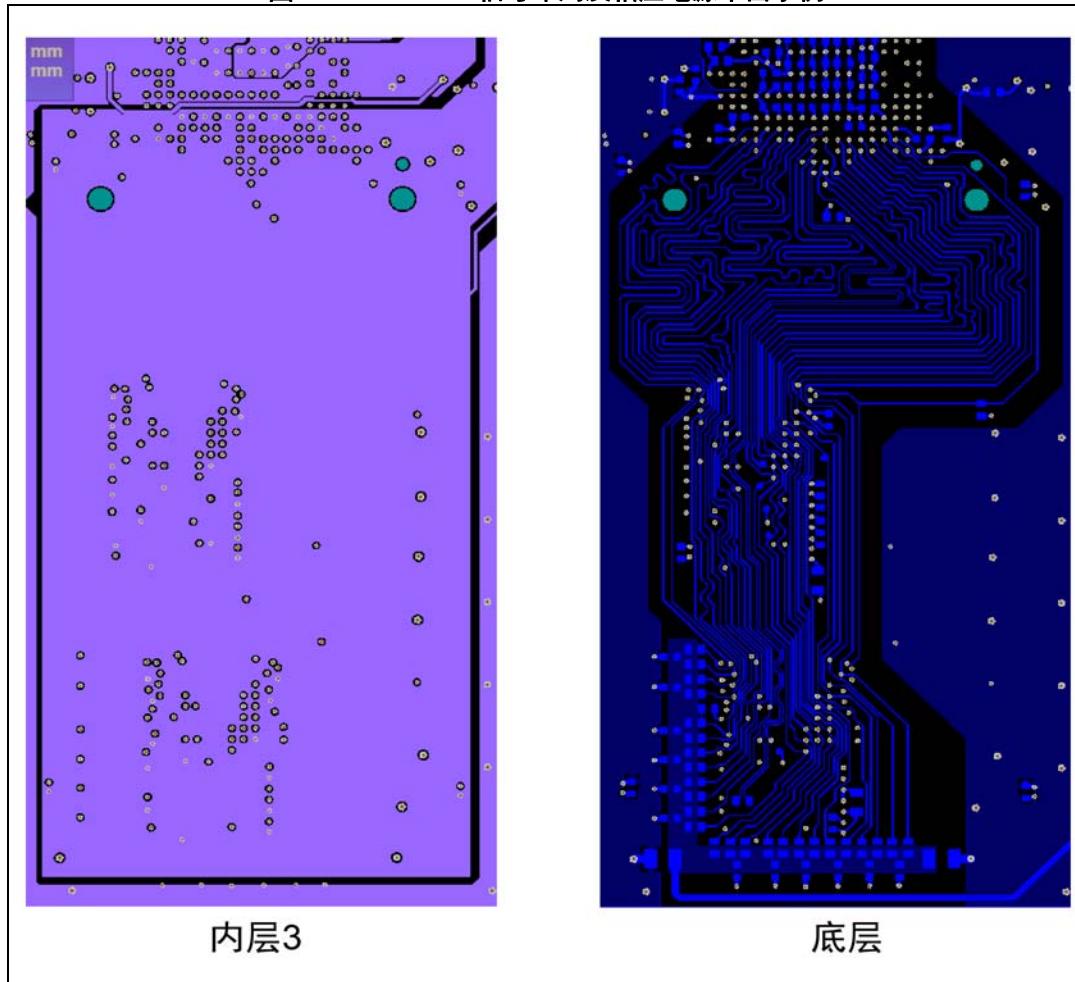

## 5.5 VDD\_DDR电源平面规范

通常情况下，A/C信号被安排在4层PCB的底层。

内层3必须是一个统一的VDD\_DDR（VDD\_DDR2对应于LPDDR2/3）电源平面，该电源平面与内存底层信号完全重叠，以避免因走线以多个电源平面为参考点而导致阻抗中断。

图11. DDR3L A/C信号布局及相应电源平面示例

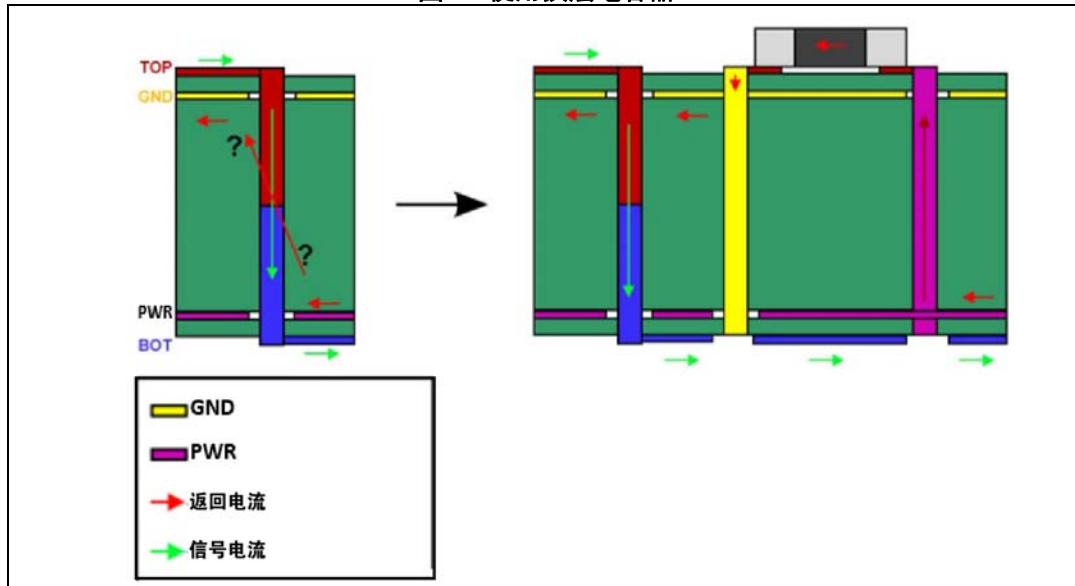

## 5.6 换层电容器

当一个敏感信号从PCB的顶层移动到底层（反之亦然）时，必须在尽可能靠近信号通孔的位置放置一个100 nF的电容器。

该电容器应该从一端连接到2层（GND），从另一端连接到3层（DDR3/3L对应于VDD\_DDR，LPDDR2/3对应于VDD\_DDR2）。

为了给信号提供高频返回电流参考路径，该设计要求是绝对必要的。

该电容器可以放置在底层或顶层（如图 12中所示）。

图12. 使用换层电容器

在实践中，当多个信号使PCB同一区域内的层（例如在A/C总线分配的情况下）发生变化时，可能无法将一个单一电容器置于每个通孔附近。

在这种情况下，解决方案是为一组通孔增加一个单一电容器。用户应在板设计过程中尝试使用尽可能多的电容器，这些电容器应放在尽可能靠近通孔区域的位置。

## 5.7 去耦电容器类型

为了避免电压下降和因此造成的眼图闭合和错误的数据传输，电源完整性至关重要。

核心和敏感电源（如VDD\_DDR）必须使用内部电源平面进行布局（使用最大宽度），以使分布阻抗最小化。

除此之外，还需要去耦电容器。有两种类型：

- 大容量电容器

这些电容器为低频、大电流需要提供板载能量罐。电容值的范围从 $10 \mu\text{F}$ 到 $100 \mu\text{F}$ 。

您应该参考意法半导体的参考设计来选择适合您电源需求的电容值。

大容量电容器不需要放在离其目的地非常近的位置。

- 高频电容器

高频（HF）电容器为高频电流爆发提供本地能量罐。高频电容器必须放在尽可能接近目的地（电源引脚或球）的位置。为了减少连接电感，更好的做法是使用较少的电容器，但要放在最佳位置。

## 5.8 使用去耦电容器的高频电容使连接电感最小化

去耦电容器的放置必须确保连接电感最小化。

电容器离其目的地越近，效率就越高。这一规则尤其适用于高频电容器。

另一个因素是电容器放在顶层还是底层。

将电容器放在顶层时，其去耦效率远胜于放在底层。

然而，电容器的位置选择可能受到BGA扇出的限制。

为此，我们寻求电容放置方面的最佳实践，以最小化顶层和底层的连接电感并提高去耦效率。

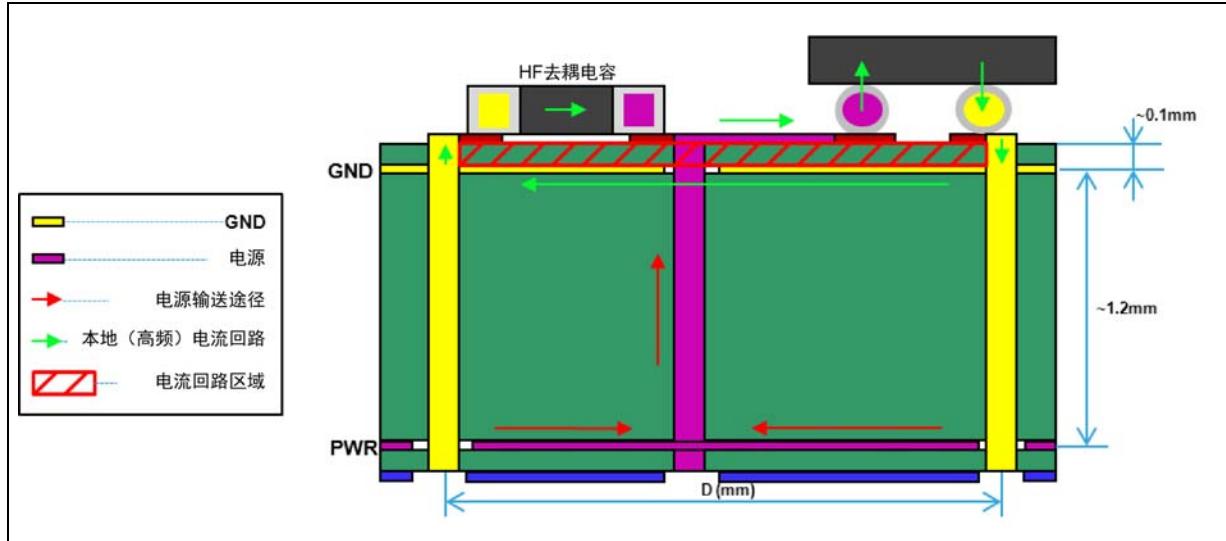

### 5.8.1 在顶层放置电容器

由于封装的限制，放置在PCB顶层的电容器不能太接近BGA球。

然而，由于GND层在堆叠中的位置（GND是返回电流层），如果电容器是通过顶层直接电源走线连接到BGA球，则其连接电感仍比电容器位置更靠近且位于底层时小。

所得到的连接电感量与电流回路的面积有直接联系。

因此将电容器放置在顶层具有以下特点：

- 优点

- 电流回路面积小，导致连接电感低，去耦能力强。

- 它允许在底层为其他信号布局留出可用空间。由于内存A/C走线布局通常在底层，这就为A/C长度均衡/间隔要求提供更多灵活性。

- 缺点

- 由于扇出约束，将电容器放置在顶层通常不可能实现主BGA去耦。

如果可能，尝试通过顶层直接电源连接，在顶层放置一个高频电容器。2层（GND）提供了最近的返回路径，确保较小的电流回路面积和最佳的去耦效率。

例如，在图 13中所示的布局中，得到的电流回路面积为：

$$\text{Current loop area} = 0.1 \times D$$

所以，如果D等于5 mm，电流回路面积为 $0.5\text{mm}^2$ 。

图13. 在顶层放置一个高频电容器

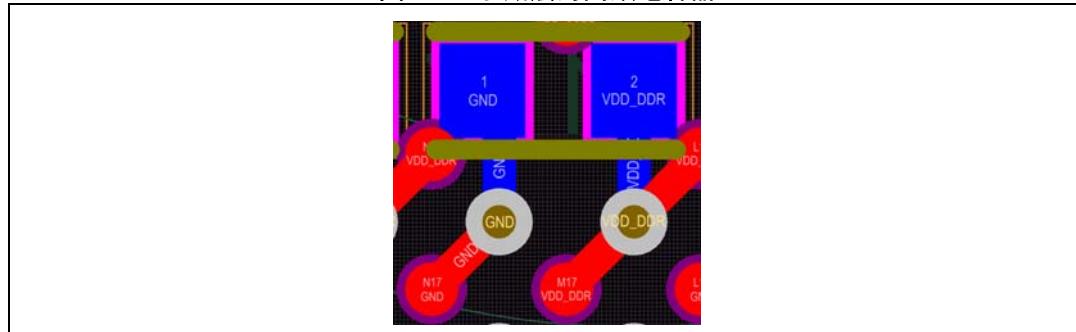

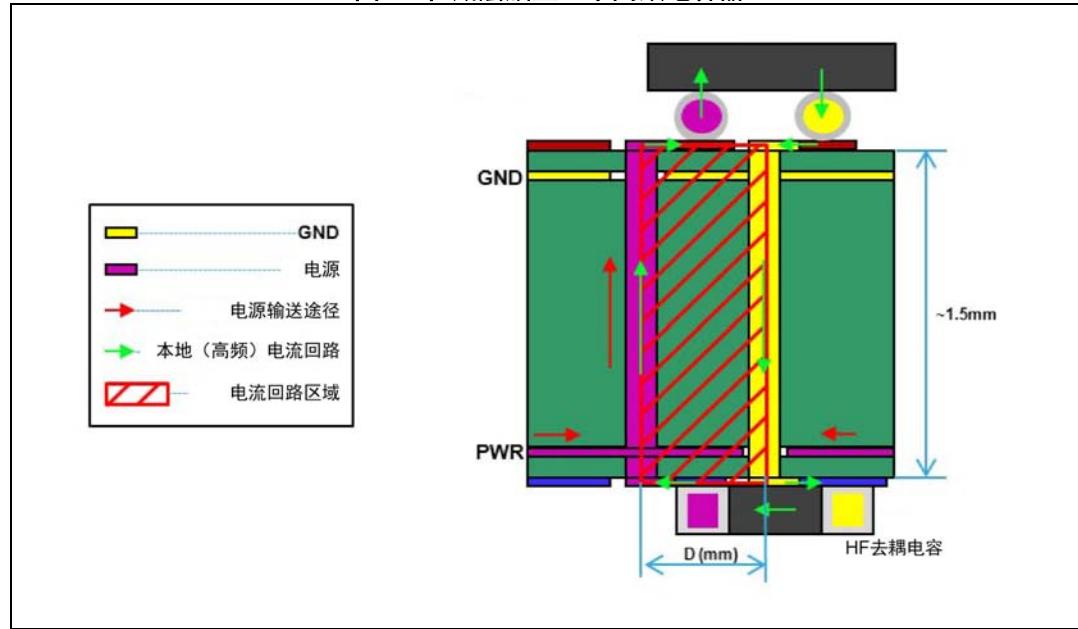

### 5.8.2 在底层放置电容器

如果不能进行顶层去耦，电容器必须放置在底层。

由于电流回路面积更大，虽然连接电感比将电容器放置在顶层时要高，但在大多数情况下，将电容器放置在底层仍然是主BGA的唯一去耦选择。对这种放置方式进行优化时，要遵循一些基本的实现规则。为达到最佳效果，可将电容器放在BGA球的正下方。

图14. 置于底层的高频电容器

当在底层放置高频电容器时，目标是确保连接尽可能短，并将良好的通孔放置在BGA下面，如图 14 中所示。

在下面的例子中，最终的电流回路面积为：

$$\text{Current loop area} = 1.5 \times D$$

如果D等于1.0 mm，产生的电流回路面积是 $1.5 \text{ mm}^2$ ；相比之下，如果放置在顶层，5 mm的距离会产生 $0.5 \text{ mm}^2$ 的电流回路面积。

换句话说，如果电容器位于顶层且离电源球15 mm，与电容器位于底层且直接放在电源球下方的效率是一样的。

这说明电容器放置在顶层的效率比放置在底层的效率更高。

图15. 在底层放置一个高频电容器

## 6 内存布局规则

该规则基于基本的PCB设计规则，是一项最佳实践守则，可用于内存接口（具体取决于信号类型）。

### 6.1 32位内存接口的数据信号规则

有四种超过4字节的差分/独立信号组：

- 字节0 = DQ[7:0], DQM0, DQS0\_N和DQS0\_P,

- 字节1 = DQ[15:8], DQM1, DQS1\_N和DQS1\_P,

- 字节2 = DQ[23:16], DQM2, DQS2\_N和DQS2\_P,

- 字节3 = DQ[31:24], DQM3, DQS3\_N和DQS3\_P,

对于这些数据信号，请应用下列规则：

- 这些数据信号应仅在PCB的顶层进行路由。

- 只要可能，将S-3S隔离规则作为最低要求。

当信号非常靠近内存芯片或STM32MP1系列器件时，会受到高通孔密度和BGA脚间距的限制，这种情况是唯一的例外。

当S-3S规则不适用时，必须对布局进行设计以优化隔离规则（S-2S, S-1.5S...）。分段（S-1S是唯一选择时）必须尽可能短。

- 对于DDR3和DDR3L，由于fly-by拓扑用于两个16位DDR3/3L，不要对所有字节应用相同的板上长度均衡，但对第一个DDR3/3L的所有字节和第二个DDR3/3L的所有字节应用以下规则：

- DQ或DQM到DQS\_N/DQS\_P +/- 40 mils (1.016 mm)

- DQS\_N/DQS\_P的长度必须比CLK\_N/CLK\_P长度 (CLK\_N/CLK\_P必须是最长的走线) 短0到590 mils (14.986 mm)。

- 第二个DDR3/3L的字节长度与第一个DDR3/3L的字节长度相比，最大不能超过1300mils (33.02 mm)

- 对于LPDDR2和LPDDR3，由于使用点对点拓扑，对每个字节应用以下规则：

- DQ或DQM到DQS\_N/DQS\_P +/- 40 mils (1.016 mm)

- DQS\_N/DQS\_P的长度必须比CLK\_N/CLK\_P长度 (CLK\_N/CLK\_P必须是最长的走线) 短0到590 mils (14.986 mm)。

$$\text{Trace length} = \text{substrate length} + \text{via length} + \text{board track length}$$

$$\text{Differential trace length (DSQS\_N/DQS\_P)} = \frac{\text{Trace length N} + \text{Trace length P}}{2}$$

- 信号排序、BGA扇出和布局示例，请参考意法半导体的参考设计。

## 6.2 16位内存接口的数据信号规则

有二种超过2字节的差分/独立信号组：

- 字节0 = DQ[7:0], DQM0, DQS0\_N和DQS0\_P

- 字节1 = DQ[15:8], DQM1, DQS1\_N和DQS1\_P

对于一个16位的DDR3/3L或LPDDR2/3，以下规则适用于两种字节：

- DQ或DQM到DQS\_N/DQS\_P +/- 40 mils (1.016 mm)

- DQS\_N/DQS\_P的长度必须比CLK\_N/CLK\_P长度（CLK\_N/CLK\_P必须是最长的走线）短0到590 mils (14.986 mm)。

因为fly-by拓扑中有两个8位DDR3/3L，下面的规则应用于字节0和字节1，为确保字节0的走线长度与字节1的走线长度不相同：

- DQ/DQM到DQS\_N/DQS\_P +/- 40 mils (1.016 mm)

- DQS\_N/DQS\_P的长度必须比CLK\_N/CLK\_P长度（CLK\_N/CLK\_P必须是最长的走线）短0到590 mils (14.986 mm)。

- 字节1的长度与字节0的长度相比，最大1300mils (33.02 mm)

## 6.3 地址和控制（A/C）信号规则

下列信号包括在这些组中：

- 对于DDR3/3L A[15:0], BA[2:0], RASN, CASN, WEN, CSN, CKE, ODT, CLK\_N, CLK\_P

- 对于LPDDR2/3 A[9:0], CSN, CKE, CLK\_N, CLK\_P

A/C信号应遵循以下设计原则：

- PCB底层必须用于将A/C分配到内存器件。顶层专为到内存芯片的连接（短线）和A/C总线交叉而预留。

- 只要可能，将S-3S隔离规则作为最低要求。

当信号非常靠近内存芯片或STM32MP1系列器件时，会受到高通孔密度和BGA脚间距的限制，这种情况是唯一的例外。

当S-3S规则不适用时，必须对布局进行设计以优化隔离规则（S-2S, S-1.5S...）。分段（S-1S是唯一选择时）必须尽可能短。

- 长度均衡规则：

A/C的长度必须比CLK\_N / CLK\_P长度短0到40 mils (1.016 mm)

CLK\_N / CLK\_P最大长度4.72英寸 (12 cm)

Trace length = substrate length + via length + board track length

$$\text{Differential trace length (CLK_N/CLK_P)} = \frac{\text{Trace length N} + \text{Trace length P}}{2}$$

- 如果是用于DDR3/3L的fly-by拓扑：

相比第一个DDR3/3L的A/C、CLK\_N/CLK\_P的长度，第二个DDR3/3L的A/C、CLK\_N/CLK\_P的长度最大不能超过其1300 mils（33.02 mm）。

信号排序、BGA扇出和布局示例请参考意法半导体的参考设计。

## 6.4 ZQ 信号

该信号的布局应确保从球到参考电阻器的走线尽可能短。应注意确保与任何有噪声的入侵信号充分隔离。

## 6.5 电源平面规则

电源平面设计应遵循以下规则。

### 6.5.1 VDD\_DDR (VDD\_DDR2对应LPDDR2/3) 电源平面

- 该平面应为位于第3层的统一电源平面。

- 该电源平面必须与底层上的每一个DDR3/3L（LPDDR2/3）走线重叠，以避免阻抗不连续。

- VDD\_DDR电源平面与VDD\_DDR电源的连接、与STM32MP1系列器件的连接、以及与每个内存器件的连接必须通过多个通孔完成。

- 必须应用标准去耦规则：

- 大容量电容器必须放置在稳压器和STM32MP1系列和内存器件之间

- 高频去耦电容器必须放置在尽可能靠近每个电源引脚的位置，遵循[第 5.8 节](#)中列出的低连接电感建议。

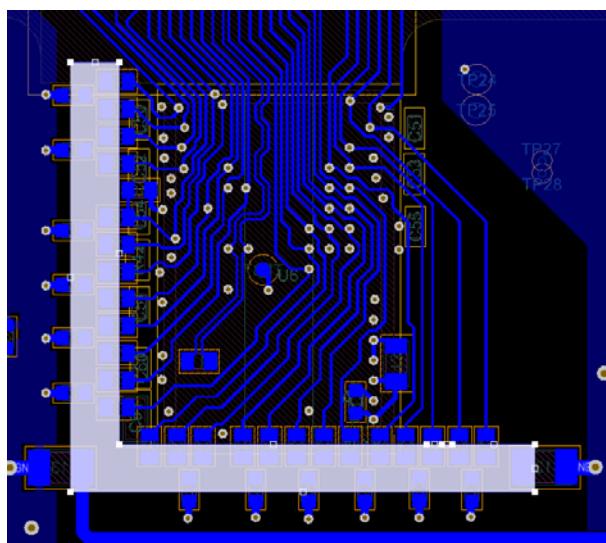

### 6.5.2 VTT电源平面规则

VTT电源仅用于使用fly-by拓扑的DDR3/3L接口。

- VTT端接电压必须被视为电源。

- 由于VDD\_DDR约束（第3层中的一个统一平面，与DDR区域重叠），VTT布局必须作为底层上的一个孤岛进行管理。请参见图 16。

- VTT调节器应靠近RTT终端。

- 对于两个RTT终端电阻，必须预留一个高频电容器，且必须放置在与其尽可能接近的位置。

- 大容量电容器可以放置在VTT调节器和终端之间的任何位置。

- 在VTT孤岛周围留有足够的间距，以减少串扰。

图16. VTT电源平面孤岛布局

## 版本历史

表2. 文档版本历史

| 日期         | 版本 | 变更                                                                                                                                       |

|------------|----|------------------------------------------------------------------------------------------------------------------------------------------|

| 2018年1月31日 | 1  | 初始版本                                                                                                                                     |

| 2019年2月1日  | 2  | 替换内容：<br>-STM32MP15系列替换为STM32MP1系列<br>更新了：<br>-关于数据、地址和控制信号规则，参见 <a href="#">第6.1节</a> 、 <a href="#">第6.2节</a> 、以及 <a href="#">第6.3节</a> |

| 2019年2月6日  | 3  | 替换内容：<br>-STPMU1替换为STPMIC                                                                                                                |

表3. 中文文档版本历史

| 日期         | 版本 | 变更     |

|------------|----|--------|

| 2021年1月14日 | 1  | 中文初始版本 |

**重要通知 - 请仔细阅读**

意法半导体公司及其子公司（“ST”）保留随时对 ST 产品和 / 或本文档进行变更、更正、增强、修改和改进的权利，恕不另行通知。买方在订货之前应获取关于 ST 产品的最新信息。ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对 ST 产品的选择和使用，ST 概不承担与应用协助或买方产品设计相关的任何责任。

ST 不对任何知识产权进行任何明示或默示的授权或许可。

转售的 ST 产品如有不同于此处提供的信息的规定，将导致 ST 针对该产品授予的任何保证失效。

ST 和 ST 徽标是 ST 的商标。若需 ST 商标的更多信息，请参考 [www.st.com/trademarks](http://www.st.com/trademarks)。所有其他产品或服务名称均为其各自所有者的财产。

本文档中的信息取代本文档所有早期版本中提供的信息。

© 2021 STMicroelectronics - 保留所有权利