---

如何利用STM32F413/F423系列SRAM的性能优势

---

## 前言

在嵌入式设计中，对大量数据的需求不断增加。存储器（特别是RAM）已成为十分宝贵的资源，了解该存储器的最佳使用方式是获得最佳性能的关键所在。

本应用笔记旨在帮助用户通过研究不同场景，从STM32F413/F423微控制器的更高SRAM性能和更低功耗中获益。

主要目标是介绍架构设计和系统模块功能，可以对它们进行调整以优化应用。

# 目录

|          |                                |           |

|----------|--------------------------------|-----------|

| <b>1</b> | <b>STM32F413/F423系统架构概述</b>    | <b>5</b>  |

| 1.1      | STM32F413/F423内核总线             | 5         |

| 1.2      | 嵌入式SRAM                        | 6         |

| 1.3      | 性能和功耗的比较研究                     | 6         |

| 1.3.1    | 第一种场景：从闪存执行代码，同时数据存放在SRAM1中    | 7         |

| 1.3.2    | 第二种场景：从SRAM2执行代码，同时数据存放在SRAM1中 | 8         |

| 1.3.3    | 性能结果的比较研究                      | 9         |

| 1.3.4    | 功耗结果的比较研究                      | 9         |

| <b>2</b> | <b>结论</b>                      | <b>10</b> |

| <b>3</b> | <b>版本历史</b>                    | <b>11</b> |

## 表格索引

|     |                |    |

|-----|----------------|----|

| 表1. | 性能结果总结 .....   | 9  |

| 表2. | 功耗结果总结 .....   | 9  |

| 表3. | 文档版本历史 .....   | 11 |

| 表4. | 中文文档版本历史 ..... | 11 |

## 图片索引

|     |                               |   |

|-----|-------------------------------|---|

| 图1. | STM32F413/F423系统架构 . . . . .  | 5 |

| 图2. | 场景1：性能配置 . . . . .            | 7 |

| 图3. | 场景1：MDK-ARM分散加载描述文件 . . . . . | 7 |

| 图4. | 场景2：性能配置 . . . . .            | 8 |

| 图5. | 场景2：MDK-ARM分散加载描述文件 . . . . . | 8 |

# 1 STM32F413/F423系统架构概述

优化系统性能的第一步是了解系统的高层架构。

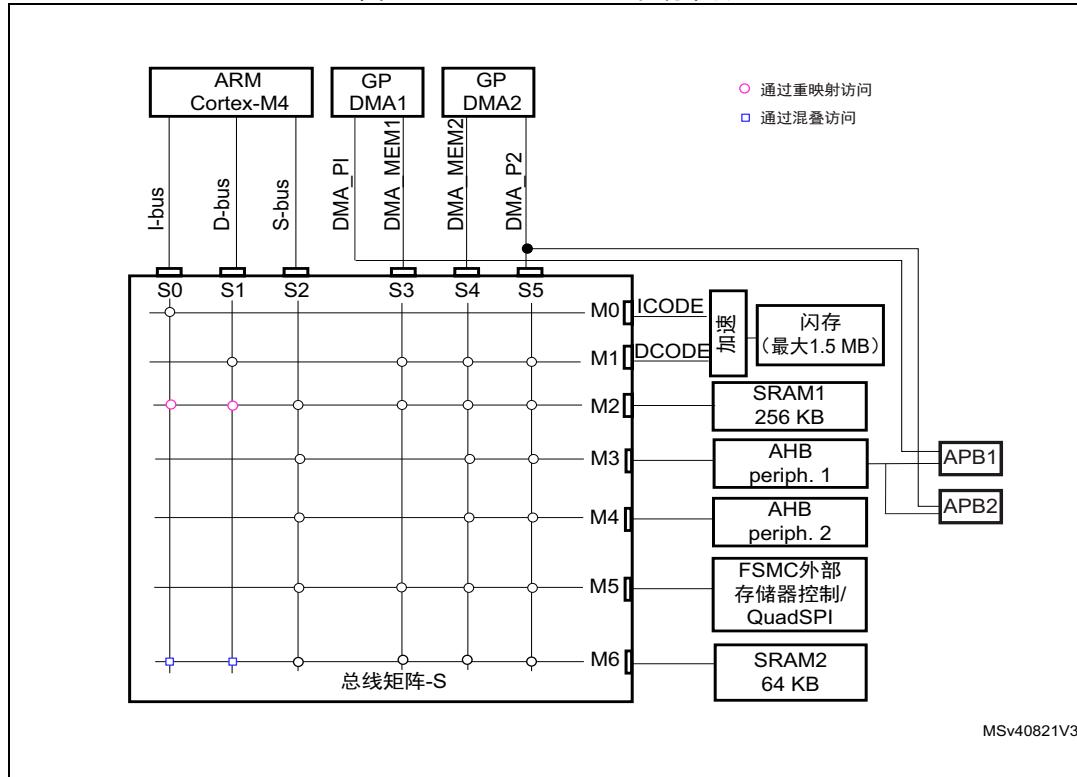

图 1 显示了 STM32F4 系列的简化框图。

图1. STM32F413/F423系统架构

## 1.1 STM32F413/F423内核总线

STM32F413/F423器件基于带有FPU（浮点单元）内核的Cortex<sup>®</sup>-M4内核，它使用哈佛体系结构，结合存储器映射总线。

总线矩阵提供从主设备到从设备的访问，可实现并发访问和高效运行。

- I-bus：内核用来从包含代码的存储器（内部闪存/SRAM）取指令的指令总线。

- D-bus：内核用来进行文字加载和对/从包含代码或数据的存储器（内部闪存/SRAM）进行调试访问的数据总线。

- S-Bus：内核用来访问外设或SRAM中数据的系统总线。也可通过该总线取指令。该总线的访问目标是内部SRAM，AHB 1外设包括APB外设和AHB2外设。

## 1.2 嵌入式SRAM

STM32F413/F423具有320 K字节SRAM。

该内置SRAM分为两块：

- 映射到地址0x2000\_0000的SRAM1，所有AHB主设备均可访问。

- 映射到地址0x2004\_0000的SRAM2，所有AHB主设备均可访问。

在STM32F413/F423中，可按以下方式访问SRAM2：

- 可通过I-Code总线取指令。通过D-Code总线执行数据访问。

- 可通过系统总线取指令和访问数据。

- 数据访问是别名。指令访问不是别名。

独立总线在加载或存储指令时十分有用，因为可以同时取指令和访问数据，无需插入总线矩阵仲裁。

当SRAM2被映射到地址范围0x1000 0000至0x1000 FFFF时，CPU可通过I-bus和D-bus访问SRAM2存储器。

系统总线的访问周期时间取决于访问类型：

- 系统总线数据访问不会增加内核的延时。

- 指令访问会增加一个等待状态的内核延时。

将代码和数据存入两个SRAM块有助于提高并行能力和整体性能。

注：对于典型应用，通过在SRAM2中插入关键代码和在SRAM1中插入数据和堆栈可获得最佳性能。

## 1.3 性能和功耗的比较研究

使用Core-Mark算法执行性能和功耗的比较研究。

按照上述建议和以下系统配置执行该算法：

系统配置：

1. 从闪存执行

2. 从SRAM执行

测试条件：

- 在室温20°C和V<sub>DD</sub>=3.3V的条件下执行测试。

- 如果从闪存运行，

- ART使能

- 添加3个等待状态（WS）。

### 1.3.1 第一种场景：从闪存执行代码，同时数据存放在SRAM1中

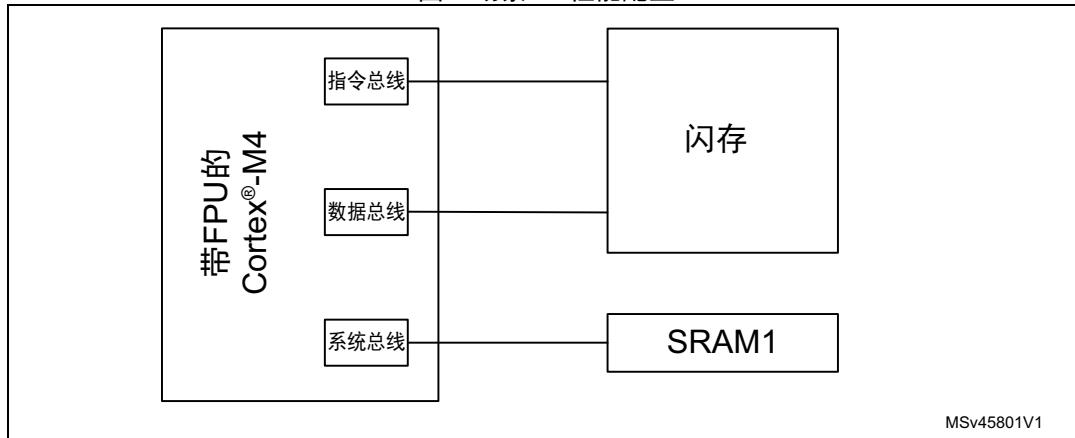

图 2 显示了第一种场景：

图2. 场景1：性能配置

图 3 显示了MDK-ARM分散加载描述文件。

图3. 场景1：MDK-ARM分散加载描述文件

```

1 ; ****

2 ; *** Scatter-Loading Description File generated by uVision ***

3 ; ****

4

5 LR_IROM1 0x08000000 0x00180000 { ; load region size_region

6   ER_IROM1 0x08000000 0x00180000 { ; load address = execution address

7     *.o (RESET, +First)

8     *(InRoot$$Sections)

9     .ANY (+RO)

10   }

11   RW_IRAM1 0x20000000 0x00050000 { ; RW data

12     .ANY (+RW +ZI)

13   }

14 }

```

### 1.3.2 第二种场景：从SRAM2执行代码，同时数据存放在SRAM1中

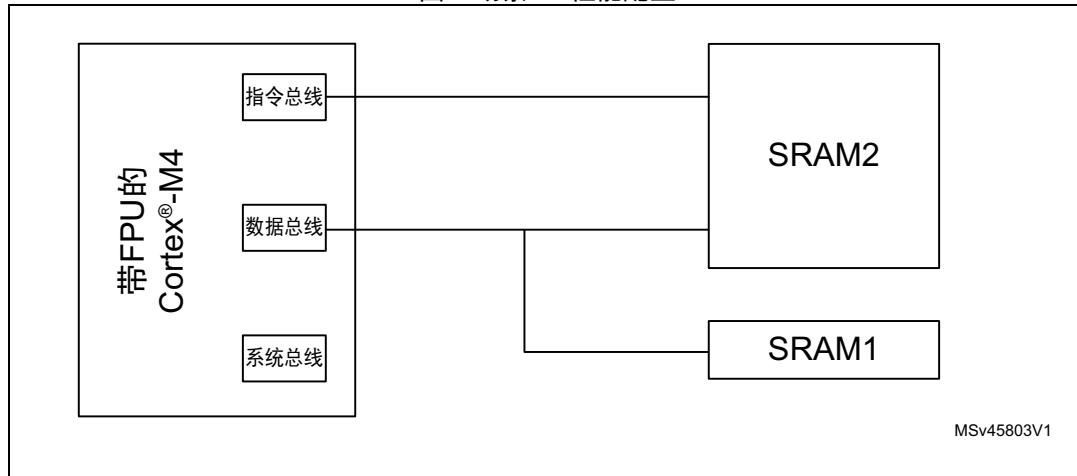

图 2 显示了第二种场景：

图4. 场景2：性能配置

图 5 显示了通过KEIL MDK获得的MDK-ARM分散加载描述文件。

图5. 场景2：MDK-ARM分散加载描述文件

```

1 ; ****

2 ; *** Scatter-Loading Description File generated by uVision ***

3 ; ****

4

5 LR_IROM1 0x10000000 0x8000 { ; load region size_region

6 ER_IROM1 0x10000000 0x8000 { ; load address = execution address

7 *.o (RESET, +First)

8 *(InRoot$$Sections)

9 .ANY (+RO)

10 }

11

12 RW_IRAM1 0x20008000 0x4000 { ; RW data

13 .ANY (+RW +ZI)

14

15 }

16 }

17

```

### 1.3.3 性能结果的比较研究

表 1 显示了获得的结果：

表1. 性能结果总结

| 系统时钟100 MHz |         |                                |

|-------------|---------|--------------------------------|

|             | 从闪存执行代码 | 从SRAM2执行代码<br>和<br>数据存放在SRAM1中 |

| 分数          | 3.39    | 3.41                           |

### 1.3.4 功耗结果的比较研究

表 2 显示了获得的结果：

表2. 功耗结果总结

| 系统时钟100 MHz |         |                                |

|-------------|---------|--------------------------------|

|             | 从闪存执行代码 | 从SRAM2执行代码<br>和<br>数据存放在SRAM1中 |

| 功耗[mA]      | 22.91   | 21.54                          |

注： 第二种配置下获得的最佳性能和最低功耗：从SRAM2执行代码，同时数据存放在SRAM1中。

## 2 结论

本应用笔记描述了通过SRAM优化性能和功耗的技术，是对STM32F413/F423数据手册和参考手册的补充。

### 3 版本历史

表3. 文档版本历史

| 日期         | 版本 | 变更    |

|------------|----|-------|

| 2017年4月18日 | 1  | 初始版本。 |

表4. 中文文档版本历史

| 日期         | 版本 | 变更      |

|------------|----|---------|

| 2018年5月11日 | 1  | 中文初始版本。 |

**重要通知 - 请仔细阅读**

意法半导体公司及其子公司（“ST”）保留随时对 ST 产品和 / 或本文档进行变更、更正、增强、修改和改进的权利，恕不另行通知。买方在订货之前应获取关于 ST 产品的最新信息。ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对 ST 产品的选择和使用， ST 概不承担与应用协助或买方产品设计相关的任何责任。

ST 不对任何知识产权进行任何明示或默示的授权或许可。

转售的 ST 产品如有不同于此处提供的信息的规定，将导致 ST 针对该产品授予的任何保证失效。

ST 和 ST 徽标是 ST 的商标。所有其他产品或服务名称均为其各自所有者的财产。

本文档中的信息取代本文档所有早期版本中提供的信息。本文档的中文版本为英文版本的翻译件，仅供参考之用；若中文版本与英文版本有任何冲突或不一致，则以英文版本为准。

© 2018 STMicroelectronics - 保留所有权利