# 参考資料

life.augmented

AN1709

## アプリケーション・ノート

### ST 製マイクロコントローラの EMC 設計ガイド

#### 概要

より高い性能と複雑さ、およびコスト削減への継続的な要望により、半導体業界には、高密度設計技術とより高いクロック周波数の両方を備えたマイクロコントローラの開発が求められています。このような設計により、必然的にノイズ輻射および、ノイズ感度は高くなります。したがって、アプリケーション開発では、ファームウェアと PCB レイアウトの設計およびシステム・レベルでの設計に EMC 対策強化手法を適用することが必要になっています。本資料では、ST マイクロエレクトロニクスのマイクロコントローラの EMC 機能と適合規格について説明し、アプリケーション設計者が最適な水準の EMC 性能が得られるようにすることを目的としています。

# 参考資料

## 目次

AN1709

## 目次

|          |                                           |           |

|----------|-------------------------------------------|-----------|

| <b>1</b> | <b>EMC の定義</b>                            | <b>6</b>  |

| 1.1      | EMC                                       | 6         |

| 1.2      | EMS                                       | 6         |

| 1.3      | EMI                                       | 6         |

| <b>2</b> | <b>ST マイクロエレクトロニクス製マイクロコントローラの EMC 特性</b> | <b>7</b>  |

| 2.1      | 電磁感受性 (EMS)                               | 7         |

| 2.1.1    | 機能性 EMS 試験                                | 7         |

| 2.1.2    | ラッチャップ (LU)                               | 11        |

| 2.1.3    | 絶対電気的感度                                   | 12        |

| 2.2      | 電磁干渉 (EMI)                                | 14        |

| 2.2.1    | EMI 放射試験                                  | 14        |

| 2.2.2    | EMI レベル分類                                 | 17        |

| <b>3</b> | <b>ST の MCU 設計方針と EMC 固有の機能</b>           | <b>19</b> |

| 3.1      | 感受性                                       | 19        |

| 3.1.1    | ブラウンアウト・リセット (BOR)                        | 19        |

| 3.1.2    | プログラム可能な電圧検出器 (PVD)                       | 20        |

| 3.1.3    | I/O 機能とプロパティ                              | 22        |

| 3.2      | 輻射                                        | 25        |

| 3.2.1    | 内部 PLL                                    | 25        |

| 3.2.2    | グローバルな低消費電力手法                             | 26        |

| 3.2.3    | 出力の I/O 電流制限およびエッジ・タイミング制御                | 27        |

| <b>4</b> | <b>MCU を使用したアプリケーションの EMC ガイドライン</b>      | <b>28</b> |

| 4.1      | ハードウェア                                    | 28        |

| 4.1.1    | PCB レイアウトの最適化                             | 28        |

| 4.1.2    | 電源のフィルタリング                                | 29        |

| 4.1.3    | I/O 設定                                    | 30        |

| 4.1.4    | シールド                                      | 30        |

| 4.2      | ESD 保護取り扱い上の注意点                           | 31        |

| 4.3      | ファームウェア                                   | 31        |

| 4.4      | EMC 関連組織へのウェブ・リンク                         | 31        |

# 参考資料

AN1709

目次

|            |                                    |    |

|------------|------------------------------------|----|

| 5          | 結論 .....                           | 32 |

| 付録 A       | 2015 年 12 月 14 日よりも前の EMI 分類 ..... | 33 |

| 改版履歴 ..... | 35                                 |    |

# 参考資料

表の一覧

AN1709

## 表の一覧

|       |                                              |    |

|-------|----------------------------------------------|----|

| 表 1.  | ESD 規格 .....                                 | 7  |

| 表 2.  | FTB 規格 .....                                 | 9  |

| 表 3.  | ST の ESD 深刻度 レベル .....                       | 10 |

| 表 4.  | ST の動作 クラス .....                             | 11 |

| 表 5.  | F_ESD/FTB の目標 レベルと許容限界 .....                 | 11 |

| 表 6.  | F_ESD/FTB 試験結果の表現例 .....                     | 11 |

| 表 7.  | STM32L062K8 のラッチアップ試験結果の例 .....              | 12 |

| 表 8.  | 周波数範囲に対するスペクトラム・アナライザの分解能帯域幅（広帯域の EMI） ..... | 17 |

| 表 9.  | STM32 での EMI 結果の例 .....                      | 18 |

| 表 10. | 周波数範囲に対するスペクトラム・アナライザの分解能帯域幅（狭帯域の EMI） ..... | 34 |

| 表 11. | 文書改版履歴 .....                                 | 35 |

| 表 12. | 日本語版文書改版履歴 .....                             | 35 |

## 図の一覧

|       |                                                 |    |

|-------|-------------------------------------------------|----|

| 図 1.  | ESD 試験機器 . . . . .                              | 8  |

| 図 2.  | 接触モード放電で一般的に見られる ESD 電流波形 . . . . .             | 8  |

| 図 3.  | ESD ジェネレータの概略回路図 . . . . .                      | 9  |

| 図 4.  | FTB 波形の図 . . . . .                              | 9  |

| 図 5.  | 結合回路網 . . . . .                                 | 10 |

| 図 6.  | 絶対電気的感度の試験モデル . . . . .                         | 13 |

| 図 7.  | STM32 の試験ボード回路の例 . . . . .                      | 15 |

| 図 8.  | IEC 61967-2 規格に基づく試験プリント回路ボードの仕様 . . . . .      | 16 |

| 図 9.  | IEC61967-2 の分類チャート . . . . .                    | 17 |

| 図 10. | ST の社内 EMI レベル分類 . . . . .                      | 18 |

| 図 11. | ST 製マイクロコントローラに搭載されている固有機能の概要 . . . . .         | 19 |

| 図 12. | ブラウンアウト・リセットとリセットの比較 . . . . .                  | 20 |

| 図 13. | PVD を使用した VDD の監視 . . . . .                     | 21 |

| 図 14. | デジタル入出力 - プッシュプル . . . . .                      | 23 |

| 図 15. | デジタル入出力 - 真のオープンドレイン出力 . . . . .                | 24 |

| 図 16. | デジタル入出力 - プッシュプル出力 - アナログ・マルチプレクサ入力 . . . . .   | 25 |

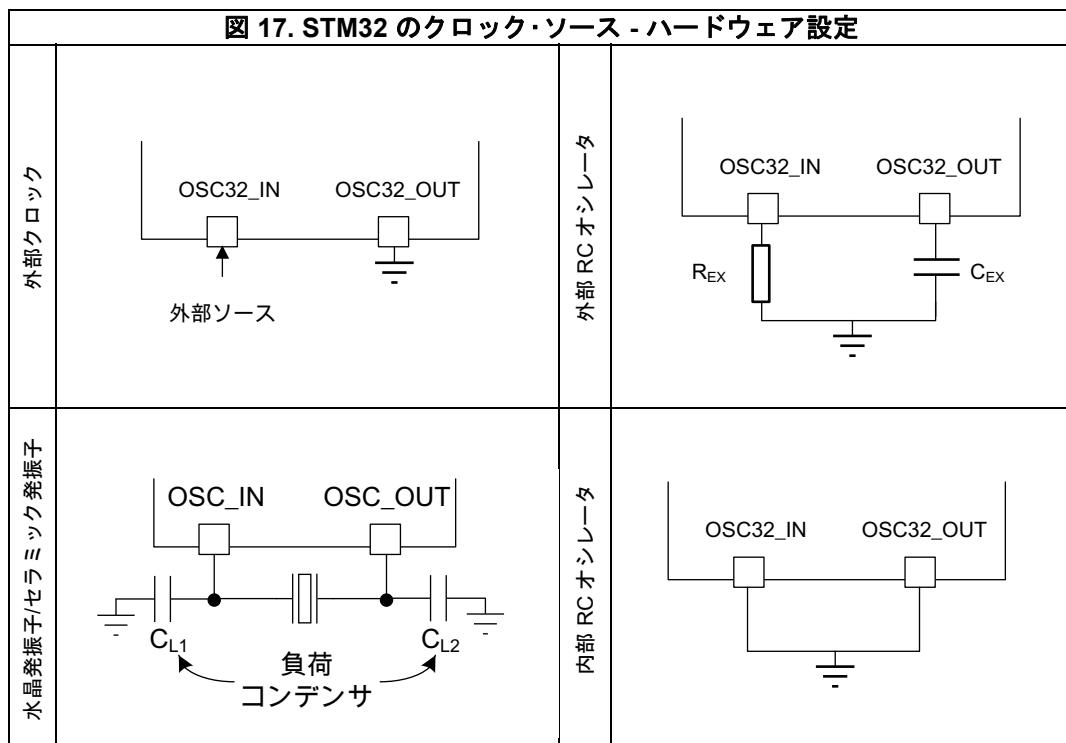

| 図 17. | STM32 のクロック・ソース - ハードウェア設定 . . . . .            | 27 |

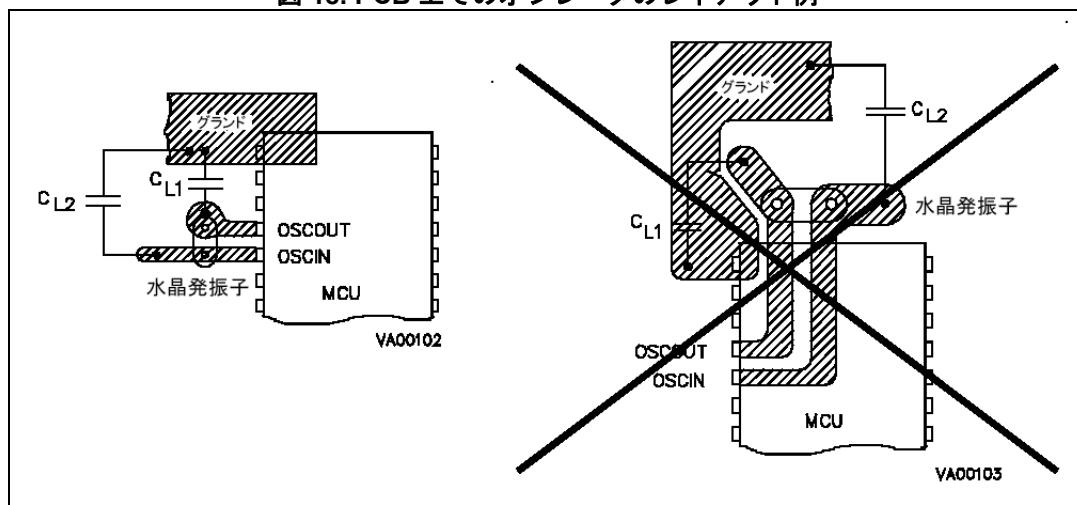

| 図 18. | PCB 上でのオシレータのレイアウト例 . . . . .                   | 28 |

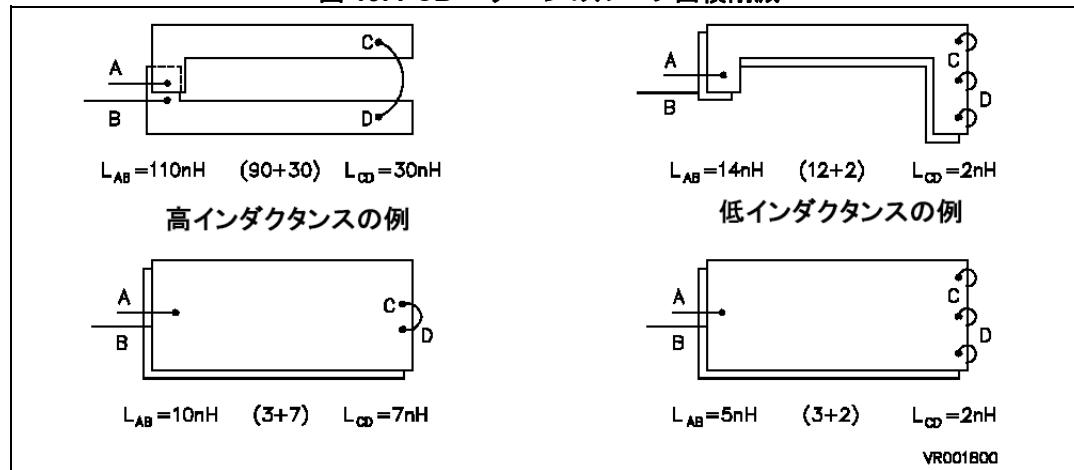

| 図 19. | PCB パターンのループ面積削減 . . . . .                      | 29 |

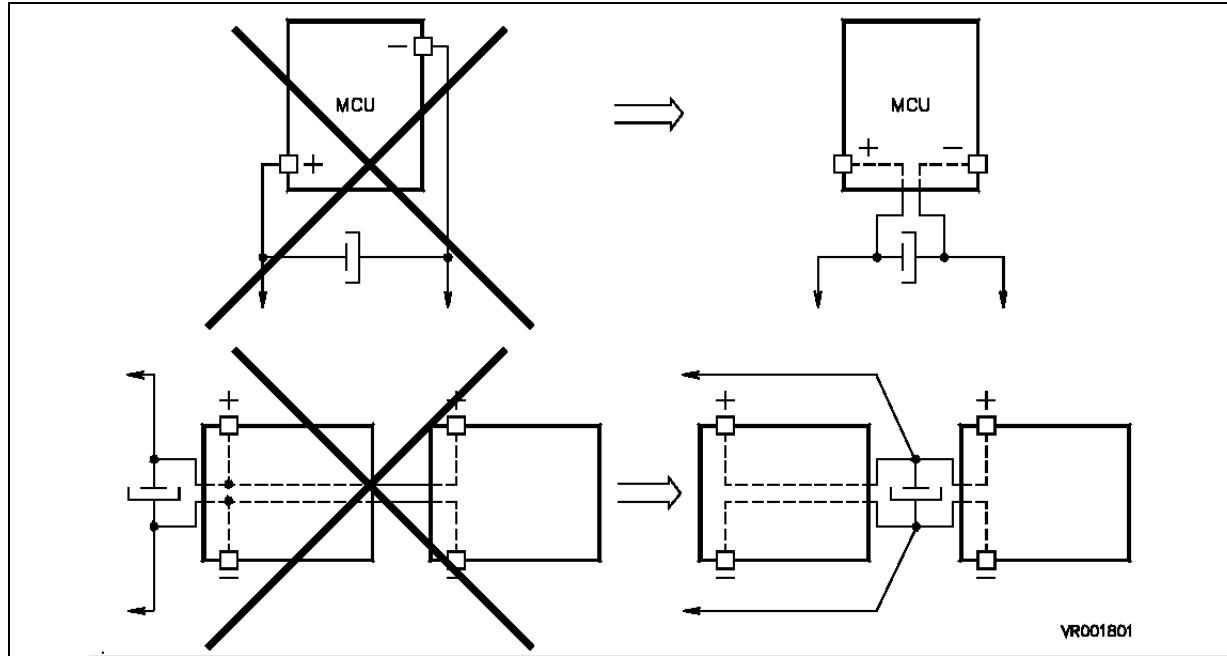

| 図 20. | 電源のレイアウト例 . . . . .                             | 30 |

| 図 21. | 2015 年 12 月 14 日よりも前の ST 社内 EMI レベル分類 . . . . . | 33 |

# 参考資料

## 1 EMC の定義

### 1.1 EMC

電磁両立性（ElectroMagnetic Compatibility : EMC）とは、システムが通常環境に存在する電磁現象に妨害されず適切に動作し、同時に他の機器に干渉するような電気的妨害を生成しない能力を指します。

### 1.2 EMS

電磁感受性（ElectroMagnetic Susceptibility : EMS）とは、電気的妨害と伝導性電気ノイズに対してデバイスが備える耐性を指します。静電気放電（ElectroStatic Discharge : ESD）とファスト・トランジエント・バースト（Fast Transient Burst : FTB）の各試験により、望ましくない電磁環境でデバイスを動作させたときの信頼性レベルを判断します。

### 1.3 EMI

電磁干渉（ElectroMagnetic Interference : EMI）とは、機器から発生する伝導性電気ノイズと放射性電気ノイズのレベルを指します。伝導性輻射は、ケーブルなどのあらゆる相互接続ライン上を伝搬します。放射性輻射は自由空間を伝搬します。

## 2 ST マイクロエレクトロニクス製マイクロコントローラの EMC 特性

### 2.1 電磁感受性 (EMS)

次の 2 種類の試験を実施します。

- 電源供給状態にしたデバイスの試験（機能性 EMS 試験およびラッチアップ）：ストレスを印加した状態でデバイスの動作を監視します。

- 電源供給状態にしていないデバイスの試験（絶対電気感受性）：ストレス印加後のデバイスの機能性と整合性を試験機器上で確認します。

#### 2.1.1 機能性 EMS 試験

機能性試験では、アプリケーションで動作している ST 製マイクロコントローラの堅牢性を測定します。簡単なプログラム (I/O ポートを通じて 2 個の LED をトグルするプログラム) に基づいて、製品がランナウェー (障害発生) 状態になるまで 2 種類の EMC イベントで製品にストレスを印加します。

##### 機能性静電気放電試験 (F\_ESD 試験)

この試験は、あらゆる新製品のマイクロコントローラ・デバイスを対象として実施されています。各ピンを、それぞれ 1 回の正または負の静電気放電で試験します。この試験により、チップ内部で発生する障害を調査します。その結果、該当のマイクロコントローラについて、ESD に対する感受性が高いピンを保護するための使用上の詳しい推奨事項を導くことができます。

高電圧の静電気には、自然発生するものと人間由来のものとがあります。実際の条件下でデバイスを試験するために、このような現象を再現できる試験機器もあります。試験機器、試験手順、試験規格については、以降で説明します。

ST 製マイクロコントローラの F\_ESD 適合試験では、[表 1](#) に示す規格を参考として使用しています。

表 1. ESD 規格

| 欧州規格         | 国際規格          | 説明         |

|--------------|---------------|------------|

| EN 61000-4-2 | IEC 61000-4-2 | 伝導性 ESD 試験 |

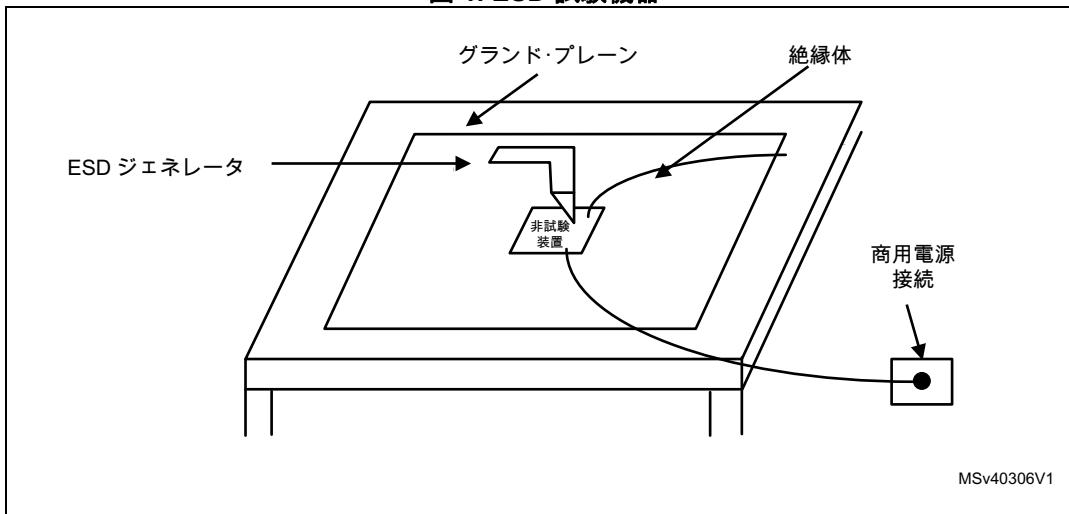

F\_ESD 試験では、信号源と電力増幅器を使用して、マイクロコントローラに印可する高電圧の静電場を生成します。絶縁体には円錐形チップを使用します。このチップを、試験対象デバイス (DUT) または試験対象機器 (EUT) の上に置き、ここに静電気を放電します ([図 1](#) を参照)。

# 参考資料

図 1. ESD 試験機器

F\_ESD 試験を実施するためにここで使用している試験機器は、IEC 61000-4-2 規格準拠の NSG 435 ジェネレータ (TESEQ) です。MCU の各ピンに静電気を直接放電します。

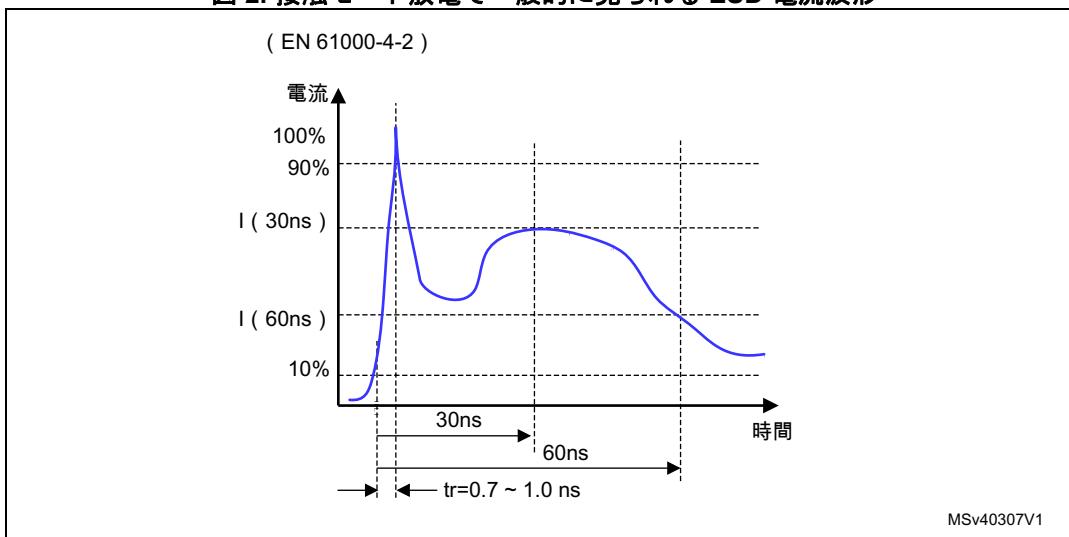

図 2. 接触モード放電で一般的に見られる ESD 電流波形

# 参考資料

AN1709

ST マイクロエレクトロニクス製マイクロコントローラの EMC 特性

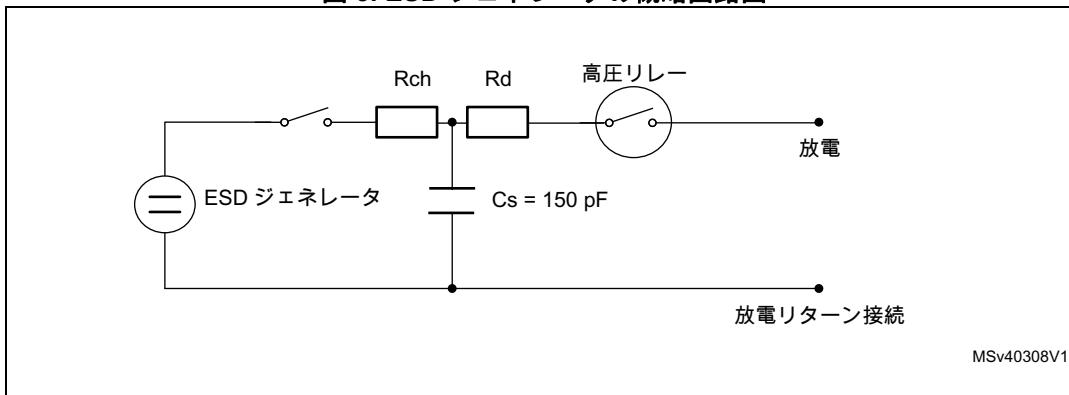

図 3. ESD ジェネレータの概略回路図

1.  $R_{ch} = 50 \text{ M}\Omega$ 、 $R_d = 330 \Omega$ 。

## ファスト・トランジェント・バースト (FTB)

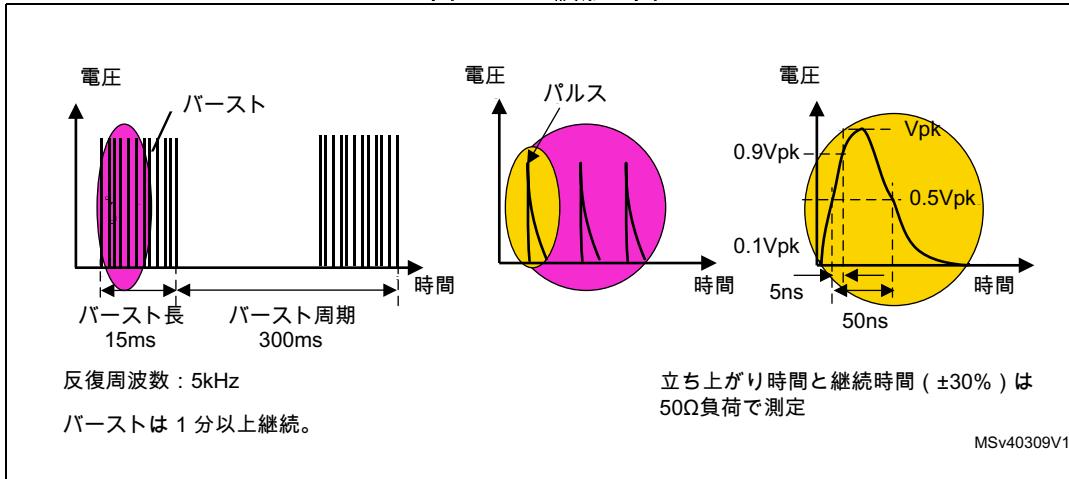

この試験は機能性 ESD よりも複雑な試験であり、短時間の高レベル放射性妨害の中にデバイスを置いて評価します。発生頻度は低く回復不能なマイクロコントローラの状態（クラス B またはクラス C）を検出するうえで効果的です。コンデンサの結合回路網を通じてマイクロコントローラの電源ラインに FTB 妨害（図 4 を参照）を印加します。

ST 製マイクロコントローラの FTB 試験には、表 2 に示す規格との相関性があります。

表 2. FTB 規格

| 欧州規格        | 国際規格          | 説明                |

|-------------|---------------|-------------------|

| EN61000-4-4 | IEC 61000-4-4 | ファスト・トランジェント・バースト |

図 4. FTB 波形の図

スパイクの周波数は 5 kHz です。15 ミリ秒間継続するスパイクのバーストを 300 ミリ秒間隔でジェネレータから発生します（スパイク数は 75）。

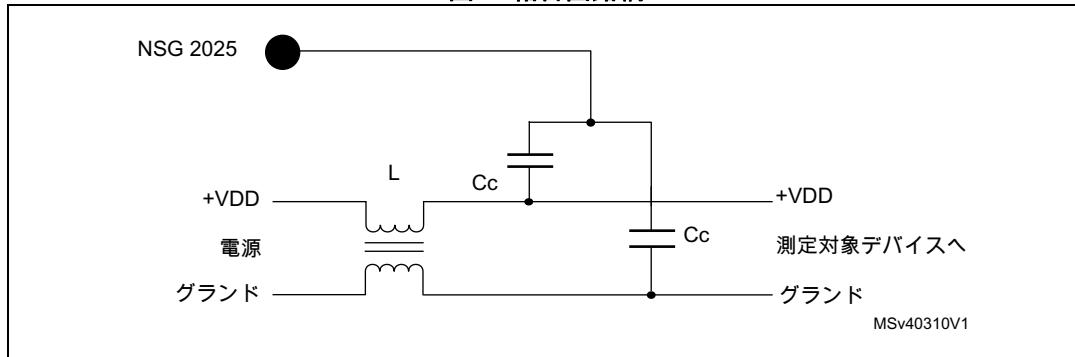

このファスト・トランジェントは、コンデンサ  $C_C$  による結合回路を介して DUT に印加します（図 5 を参照）。

# 参考資料

図 5. 結合回路網

この測定はグランド・プレーン上で実施します。ジェネレータは、短いリード線でグランド・プレーンに接続します。ファスト・トランジエントの供給ケーブルは、グランド・プレーン上 10 cm に保持します。DUT は、絶縁物を介してグランド・プレーン上 10 cm に配置します。デバイスに障害が発生するまで、FTB の電圧を上げながら試験を継続します。

目的とするアプリケーションにはどの ST 製マイクロコントローラが適切であるかをアプリケーションの設計段階で判断するうえで、重大性レベルとクラスが効果的です。これらの判断基準は、データシートに感受性レベル（重大性レベル）と動作の種類（クラス）として示されています。

## ST の深刻度レベルと動作クラス

IEC 61000-4-2 規格と IEC 61000-4-4 規格は、マイクロコントローラなどの半導体部品に具体的には言及していません。通常、電磁ストレスは、コネクタ、商用電源、電源回路など、システムの半導体以外の部品に印加されます。F\_ESD 試験と FTB 試験のエネルギー・レベルは、物理法則に従い、マイクロコントローラに達する前に低下します。さまざまな使用環境で MCU が示す動作に関して ST が収集した膨大な統計データを使用して、ST の F\_ESD 試験や FTB 試験の電圧と IEC 61000-4-2/61000-4-4 の深刻度レベルとの相関チャートが開発されてきました（表 3 を参照）。

表 3. ST の ESD 深刻度レベル

| 深刻度レベル           | ESD 規格<br>(IEC 61000-4-2)<br>(kV) | FTB 規格<br>(IEC 61000-4-4)<br>(kV) | ST 社内の ESD<br>EMC 試験 (kV) | ST 社内の FTB<br>EMC 試験 (kV) |

|------------------|-----------------------------------|-----------------------------------|---------------------------|---------------------------|

| 1                | 2                                 | 0.5                               | ≤ 0.5                     | ≤ 0.5                     |

| 2                | 4                                 | 1                                 | ≤ 1                       | ≤ 1                       |

| 3                | 6                                 | 2                                 | ≤ 1.5                     | ≤ 1.5                     |

| 4                | 8                                 | 4                                 | ≤ 2                       | ≤ 2.5                     |

| 5 <sup>(1)</sup> | >8                                | >4                                | 該当なし                      | > 2.5                     |

1. ST マイクロエレクトロニクスでは、2015 年 12 月 14 日付けで深刻度レベル 5 が導入されました。それ以前の製品は、レベル 5 を満足する可能性があってもレベル 4 としています。

ESD ストレス下にある MCU の動作は、この深刻度レベルのほか、EN 50082-2 規格に従い、表 4 に示す別の動作クラスに分類できます。

# 参考資料

表 4. ST の動作クラス

| クラス A   | クラス B                  | クラス C                       | クラス D        |

|---------|------------------------|-----------------------------|--------------|

| 障害の検出なし | 障害が検出されたが、妨害を受けた後で自己回復 | 正常な機能を回復するために、ユーザによる外部措置が必要 | 正常な機能の回復が不可能 |

「許容限界」を下回る ST 製マイクロコントローラはすべて、不良品として製品化を却下されます。ST が良好な EMS 性能として定義したレベルが「目標レベル」となります。

以下の動作が見られると **クラス B** に該当します。

- 寄生的なリセット動作がファームウェアで正しく管理されている（望ましいケース）。

- アプリケーションで、ペリフェラルのレジスタやメモリへの誤ったプログラミングから回復できる。

- ウォッチドッグなどのファームウェア実装でロック状態から回復できる。

以下の動作が見られると **クラス C** に該当します。

- アプリケーションでは、ペリフェラルのレジスタやメモリへの誤ったプログラミングから回復できない。

- アプリケーションのロック状態からの回復には、ユーザによる外部措置が必要。

ST の目標と許容限界を [表 5](#) に示します。

表 5. F\_ESD/FTB の目標レベルと許容限界

|       | 許容限界   | 目標レベル   |

|-------|--------|---------|

| F_ESD | 0.5 kV | >1 kV   |

| FTB   | 0.5 kV | >1.5 kV |

許容限界と目標レベルの間にあるデバイスは、ノイズの影響を比較的受けやすい状態にあります。感受性に関連する問題を避けるために、システム設計段階では格段の注意を要します。

F\_ESD/FTB 試験の結果の ST のデータシートにおける表現方法について [表 6](#) に示します。

表 6. F\_ESD/FTB 試験結果の表現例

| 記号           | 定格値                                                                     | 条件                              | 深刻度/基準  |

|--------------|-------------------------------------------------------------------------|---------------------------------|---------|

| $V_{F\_ESD}$ | 機能に対する妨害を引き起こすために、任意の I/O ピンに印加する電圧の限度値                                 | $T_A=+25\text{ }^\circ\text{C}$ | 2/A、3/B |

| $V_{FTB}$    | 機能に対する妨害を引き起こすために、100 pF を介して VSS ピンと VDD ピンに印加するファスト・トランジェント電圧のバースト限度値 | $T_A=+25\text{ }^\circ\text{C}$ | 3/B     |

## 2.1.2 ラッチアップ (LU)

### 静的ラッチアップ (LU) 試験

ラッチアップとは、寄生的なサイリスタ構造の形成を引き起こす過剰なストレスによって大電流が消費され、初期状態を回復するには電源からデバイスを切り離すことが必要になる現象を指します。

この過剰なストレスとなり得るのは、電圧サージや電流サージ、電流や電圧の急激な変化など、寄生的なサイリスタ構造が自己持続する原因となるあらゆる異常条件です。

低インピーダンス経路を流れる電流が振幅または継続時間の面で十分に制限されていれば、ラッチアップによってデバイスが損傷することはありません。

この試験は EIA/JESD 78 IC ラッチアップ規格に準拠しています。

真のラッチアップには自己持続性があるので、ラッチアップがトリガされると、デバイスへの電源を遮断しない限り、大電流が流れる状態が持続します。トリガ電圧を取り除くと大電流状態が停止する場合に発生するラッチアップは、一時的なラッチアップ状態と見なされます。

ラッチアップ性能を評価するには、次に挙げる 2 種類の相互補完的な静的試験を 10 個の部品で実施する必要があります。

- **電源過電圧**（各電源ピンに印加）は、ユーザによって引き起こされる電源への過渡的な過電圧の印加された状態をシミュレーションします。

- **電流注入**（各入力ピン、出力ピン、および設定可能な I/O ピンに印加）は、アプリケーションによって引き起こされるピンに対する最大定格条件を超える電圧が印加された状態をシミュレーションするものです。その例として、リングングに起因する  $V_{DD}$  を超える過大なオーバーシュートやグランド・レベルを下回るアンダーシュートがピンに印加された状態があります。

ラッチアップ試験の結果の ST のデータシートにおける表現方法について [表 7](#) に示します。

表 7. STM32L062K8 のラッチアップ試験結果の例

| 記号 | パラメータ        | 条件                                     | クラス <sup>(1)</sup> |

|----|--------------|----------------------------------------|--------------------|

| LU | 静的ラッチアップ・クラス | JESD78A に適合する $T_A=+125^\circ\text{C}$ | II レベル A           |

1. クラスの説明 : 「A」クラスは ST マイクロエレクトロニクスの社内仕様です。このクラスの限度値は JEDEC 仕様よりも厳しいので、クラス A に該当するデバイスは JEDEC 規格を上回る性能を備えています。「B」クラスは、すべての JEDEC 基準（国際規格）を厳格に満たしています。

### 動的ラッチアップ (DLU) 試験

マイクロコントローラ動作中の ESD 放電に対するラッチアップの感受性について製品を評価します。

ラッチアップが発生するまで、電圧を上げながら静電気放電を部品の各ピンに供給します。ラッチアップが発生しない最大許容電圧を試験結果とします。

DLU 試験の方法と特性評価 : マイクロコントローラを動作状態とした 3 つのサンプルの各ピンに静電気放電を印加して（正電圧で 1 回、続いて負電圧で 1 回）、動的モードでのラッチアップ性能を評価します。電源を代表値に設定し、マイクロコントローラのピンに可能な限り近い位置にオシレータを接続して、部品をリセット・モードに設定します。

LU/DLU 試験機器は、機能性 EMS 試験で使用したものと同様です（[図 1](#) を参照）。

### 2.1.3 絶対電気的感度

この試験は、ESD による破壊に対する部品の耐性を評価するために実施します。

この電気試験プログラムに適合しないデバイスはすべて不具合デバイスとして分類されます。

自動 ESD 試験機を使用し、各サンプルのピンに、ピンごとの組み合わせに従って、静電気放電（正電圧パルスの後に 1 秒の時間をおいて負電圧パルス）を印加します。サンプルの数は、デバイスで放電の対象とするピンの数で決まります（n をピン数として、3 個  $\times$   $(n + 1)$ ）。

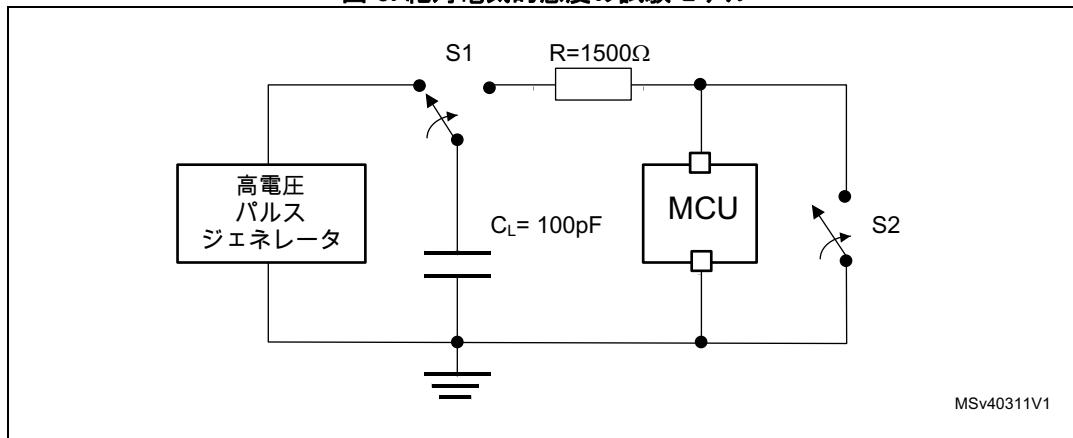

通常は、人体モデル (HBM) とチャージ・デバイス・モデル (CDM) の 2 種類のモデルをシミュレーションします。すべての部品を生産試験機で再試験し、静的および動的パラメータが引き続きデバイスのデータシートに適合していることを確認します（[図 6](#) を参照）。

どちらのモデルでも、ESD 試験中は部品に通電しません。

# 参考資料

AN1709

ST マイクロエレクトロニクス製マイクロコントローラの EMC 特性

この試験は JESD22-A114A/A115A 規格に適合しています。図 6 および以下の試験手順を参照してください。

図 6. 絶対電気的感度の試験モデル

## 人体モデルの試験手順

HBM での ESD パルスでは、人体から試験対象デバイスに直接転送される静電荷をシミュレーションします。スイッチング部品と  $1.5\text{ K}\Omega$  の直列抵抗を通じて、 $100\text{ pF}$  のコンデンサを放電します。この方法は、ESD に対するデバイスの感度を分類するために最も多用されている業界モデルです。

- S1 を使用して、高電圧パルス発生回路で  $C_L$  を充電します。

- S1 をパルス発生回路側から R 側に切り替えます。

- $C_L$  が R (人体抵抗) を通じてマイクロコントローラに放電されます。

- パルス印加期間終了後、S2 を  $10 \sim 100$  ミリ秒間閉じて、マイクロコントローラがチャージ状態に維持されないようにします。次のパルスを印加する前に、S2 を  $10$  ミリ秒間以上開きます。

## チャージ・デバイス・モデル (CDM)

CDM の詳細については、アプリケーション・ノート「Electrostatic discharge sensitivity measurement」(AN1181) を参照してください。

## 2.2 電磁干渉 (EMI)

### 2.2.1 EMI 放射試験

この試験には、IEC 61967-2 規格との相関性があります。

アプリケーション環境でマイクロコントローラがどの程度放射ノイズの要因になるかを、この試験で良好に評価できます。この試験では、デバイスから放射されるノイズに大きく影響する MCU チップと同様にパッケージも考慮されます。

一般的に、所定のパッケージ・ファミリに属するパッケージが小さいほど、発生するノイズも少なくなります。

EMI の要因となる程度が大きい順に各パッケージを以下に挙げます。

- SOP

- QFP

- TQFP

- FBGA

- CSP

この試験では、TEM モードセル (Transverse ElectroMagnetic mode CELL、GTEM とも呼ばれます) を使用します。TEM モードセルでは、試験ボードを 90°回転することで、2 方向の放射ノイズの測定が可能です。

注：

2015 年 12 月 14 日より、輻射測定周波数範囲の上限が、1 GHz から、設定が異なる 2 GHz に引き上げられています。この変更の理由と特徴については、100 kHz ~ 1 GHz で測定したデータの分類方法と合わせて、[付録 A：2015 年 12 月 14 日よりも前の EMI 分類](#)で詳しく説明しています。

#### 試験の説明

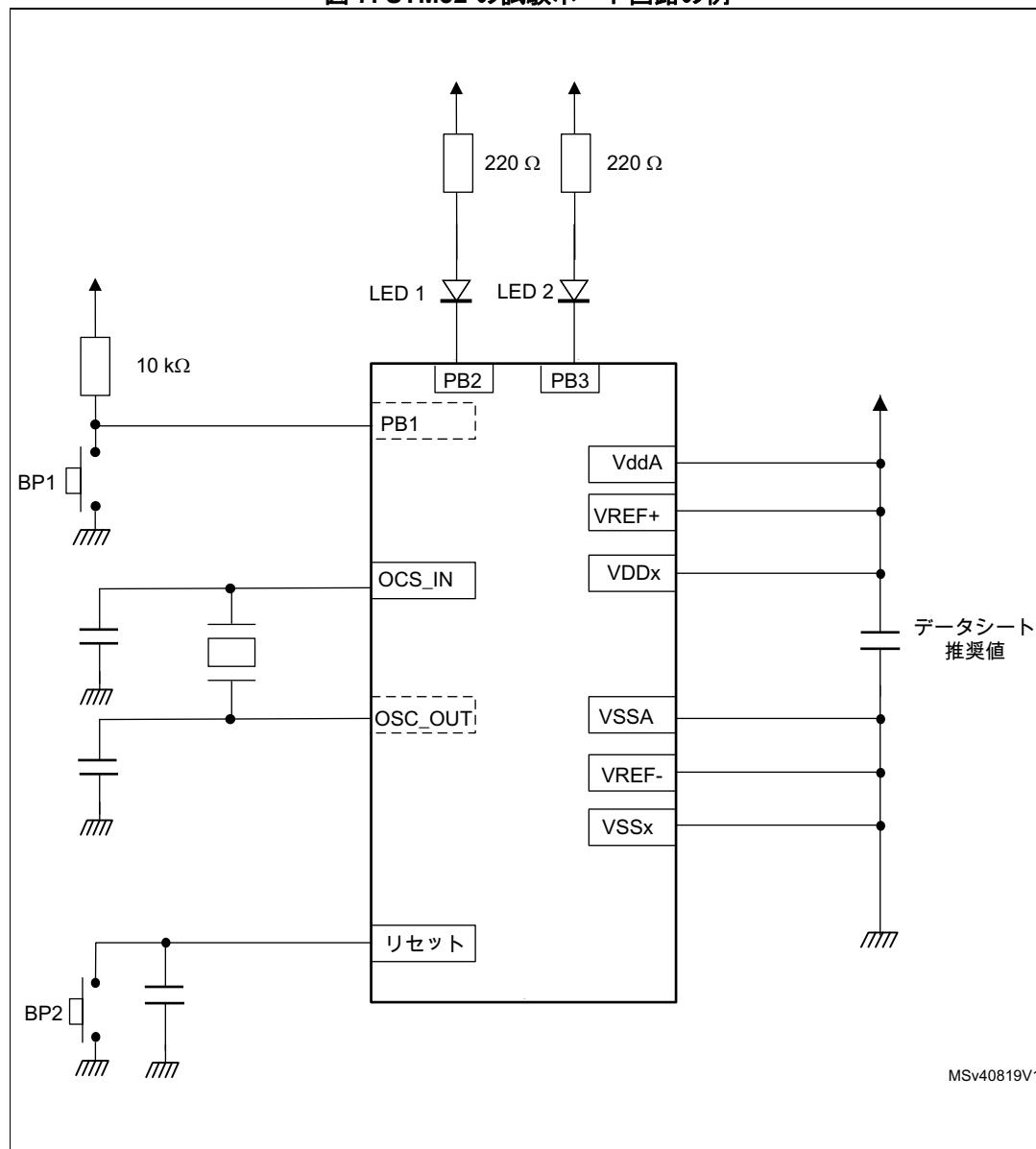

この試験で実行するファームウェアは、I/O ポートを通じて 2 個の LED の点灯を切り替える簡単なアプリケーションを使用したものです。

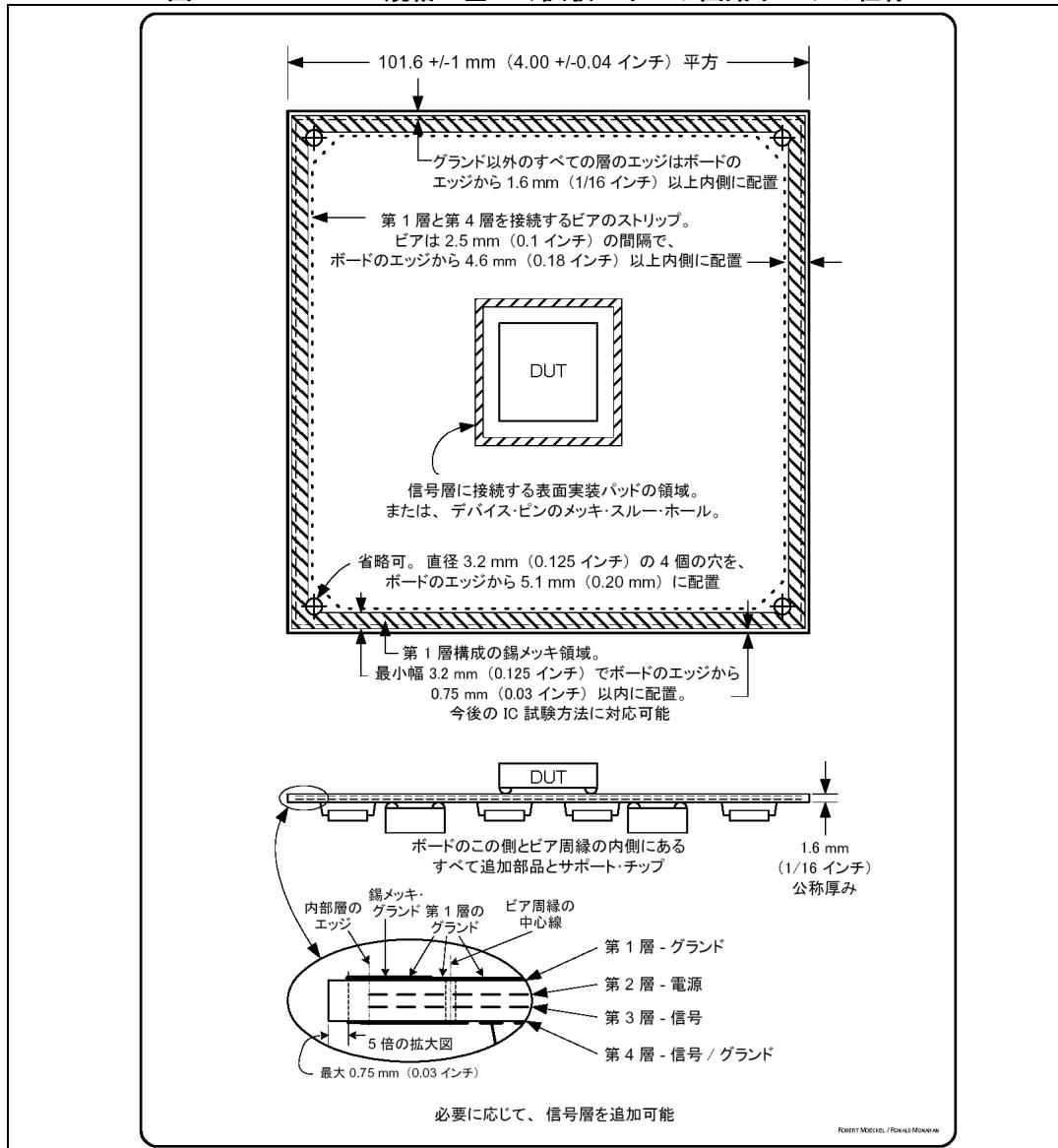

試験ハードウェアに関する IEC61967 の主要な規定は次のとおりです（[図 8](#) を参照）。

- 100 x 100 mm 平方のボード

- 2 層以上のボード（理想的には 4 層）

- TEM モードセルとの接触を確保するためにグランドに接続して両サイドに設けた 5 mm の導電性エッジ

MCU EMC 試験ボードの一般的な回路例を[図 7](#) に示します。

# 参考資料

図 7. STM32 の試験ボード回路の例

# 参考資料

図 8. IEC 61967-2 規格に基づく試験プリント回路ボードの仕様

# 参考資料

AN1709

ST マイクロエレクトロニクス製マイクロコントローラの EMC 特性

## スペクトラム・アナライザの設定

IEC61967-1 規格では、スペクトラム・アナライザのハードウェアとソフトウェアの各種設定を規定しています。この規定とは別に、測定対象信号が狭帯域であるか広帯域であるかに応じて、分解能帯域幅を選択する必要があります。

輻射測定周波数範囲に対する分解能帯域幅（RBW）を表 8 に示します。

表 8. 周波数範囲に対するスペクトラム・アナライザの分解能帯域幅

(広帯域の EMI)

| 周波数範囲 (MHz) | 分解能帯域幅 (RBW) | 検出器   |

|-------------|--------------|-------|

| 0.1 ~ 1     | 10 kHz       | ピーク検出 |

| 1 ~ 10      | 10 kHz       |       |

| 10 ~ 100    | 10 kHz       |       |

| 100 ~ 1000  | 100 kHz      |       |

| 1000 ~ 2000 | 1 MHz        |       |

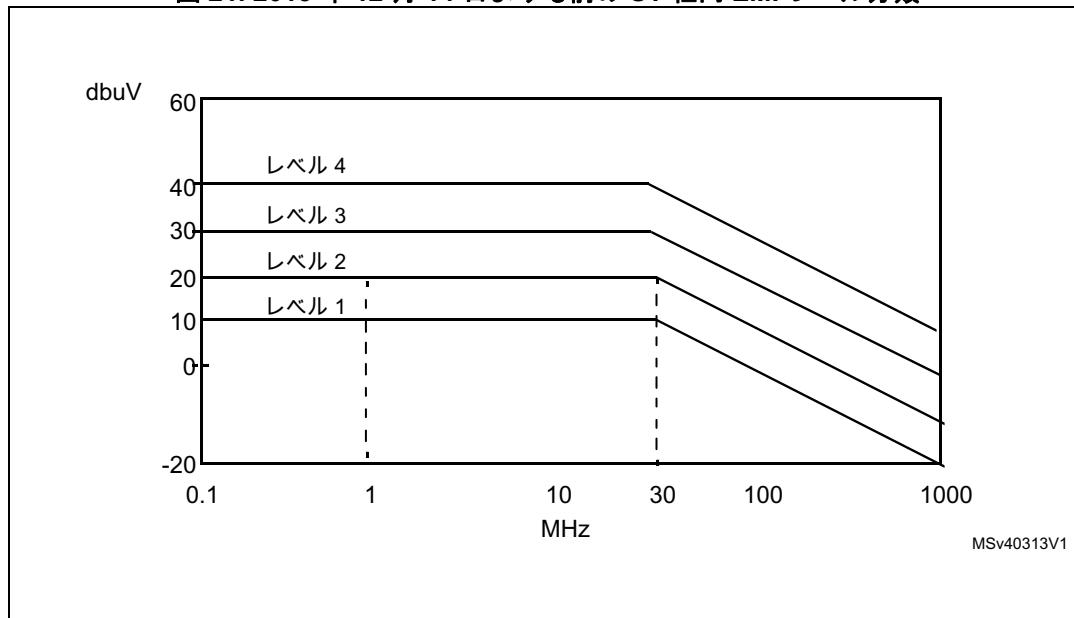

## 2.2.2 EMI レベル分類

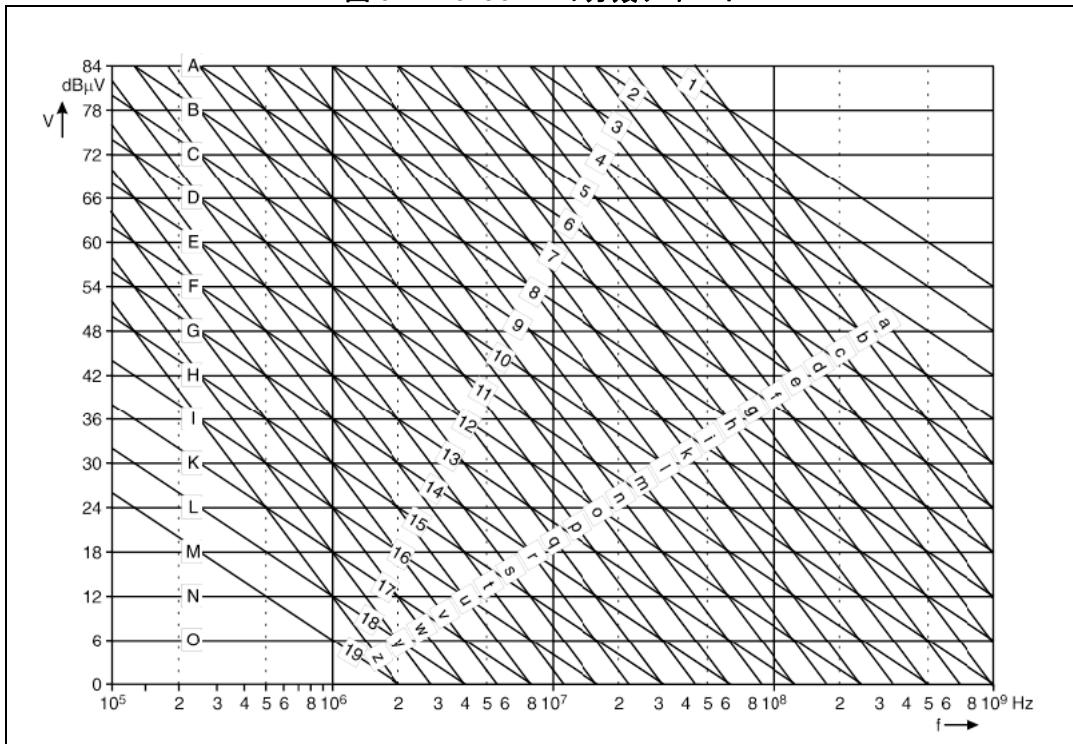

EMI 分類は、国際規格 IEC61967-2 の Annex D-3 に基づいています（図 9 を参照）。

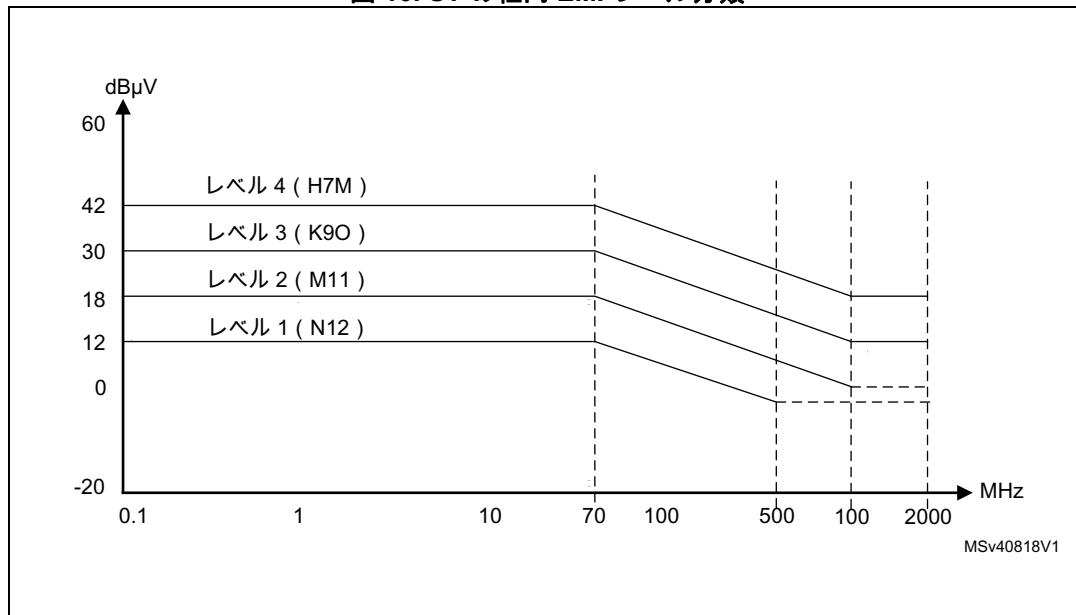

この規格で規定している特性レベル図では、2 文字と数字 1 文字の組み合わせを使用して、EMI スペクトラムの合成と分類が示されています。この方法を使用して、ST 製マイクロコントローラごとの EMI リスクを推定するために、主要な 4 種類のスペクトラム・パターン（図 9 を参照）が、この図から抽出されています。図 10 は、これら 4 種類の分類パターンを示しています。

図 9. IEC61967-2 の分類チャート

# 参考資料

図 10. ST の社内 EMI レベル分類

注 :

レベル 2 に適合するには、1 GHz を超える帯域でピークが検出されないことが必要です。

レベル 1 に適合するには、500 MHz を超える帯域でピークが検出されないことが必要です。

ST の経験則により、各 EMI レベルに伴う潜在的なリスクは以下のように定義されています。

- レベル 4 を超える場合 : EMI レベルに起因する高いリスクが存在

- レベル 4 : EMI 基準適合のためのコストが必要

- レベル 3 : 中程度の EMI リスク

- レベル 2 : 最小限の EMI リスク

- レベル 1 : きわめて低い EMI リスク

EMI 試験の結果の ST のデータシートにおける表現方法について表 9 に示します。

表 9. STM32 での EMI 結果の例

| 記号               | パラメータ   | 条件                                                                                         | 監視対象<br>周波数帯域    | Max vs. [fosc/fCPU] | 単位   |

|------------------|---------|--------------------------------------------------------------------------------------------|------------------|---------------------|------|

|                  |         |                                                                                            |                  | 8/216 MHz           |      |

| S <sub>EMI</sub> | ピーク・レベル | V <sub>DD</sub> =3.6 V、T <sub>A</sub> =+25 °C、<br>BGA216 パッケージ<br>(IEC61967-2 に適合する<br>条件) | 0.1 MHz ~ 30 MHz | 3                   | dBmV |

|                  |         |                                                                                            | 30 MHz ~ 130 MHz | 10                  |      |

|                  |         |                                                                                            | 130 MHz ~ 1 GHz  | 12                  |      |

|                  |         |                                                                                            | 1 GHz ~ 2 GHz    | 7                   |      |

|                  |         |                                                                                            | EMI レベル          | 3                   |      |

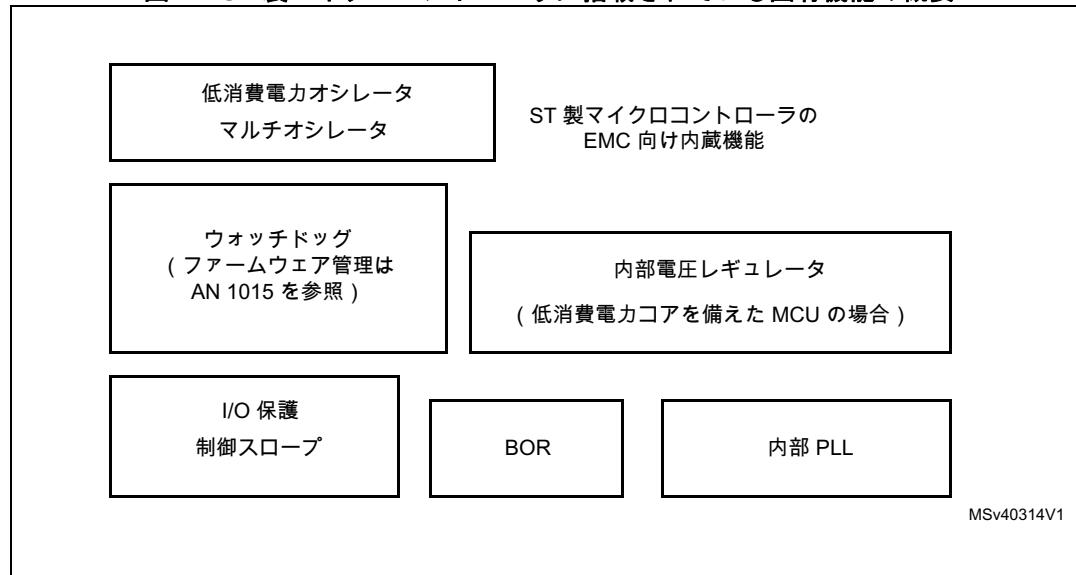

## 3 ST の MCU 設計方針と EMC 固有の機能

新製品の初期仕様では、MCU のターゲット・アプリケーションによって発生する EMC 上の制約を見極めたうえで EMC 固有の機能が実装されます。ここで取り上げている各種機能のうち、個々の製品にどれが搭載されているかについては、その製品のデータシートを参照してください。

図 11. ST 製マイクロコントローラに搭載されている固有機能の概要

### 3.1 感受性

#### 3.1.1 ブラウンアウト・リセット (BOR)

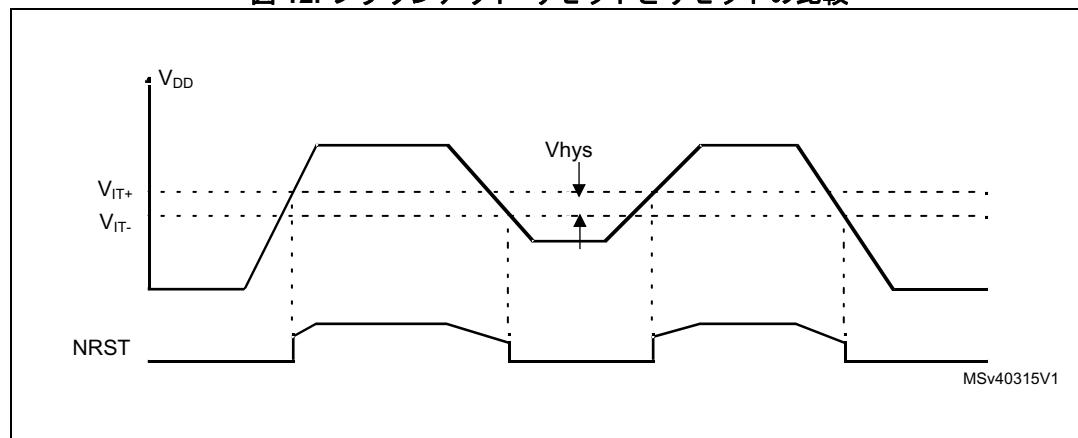

BOR の目的は、マイクロコントローラが必ず安全な動作範囲 (図 13 を参照) で動作させることです。EMS の観点からすると、BOR があることで MCU の堅牢性が向上し、外部からの妨害で電源が影響を受けてもアプリケーションが安全に回復できます。

$V_{DD}$  がその最低動作電圧を下回ると、マイクロコントローラの正常な動作を保証できなくなります。命令のデコードと実行やメモリの読み取りを実行するうえで十分な電力が得られなくなります。 $V_{DD}$  が BOR レベルを下回ると、予測不能な動作を防止するために、マイクロコントローラはリセット状態 (内部リセットが High) になります。マイクロコントローラが再起動する際の発振動作を避けるために、ヒステリシスを設定するレベルがいくつかあります。BOR が発生すると、ビットはハードウェアによってセットされます。このビットを使用してアプリケーションを回復できます。

電源電圧  $V_{DD}$  が基準値  $V_{IT^-}$  を下回ると、ブラウンアウト・リセット機能によって静的リセットが生成されます。これは、マイクロコントローラがリセット状態を保持することで、確実に電源のオンとオフを実行できることを意味しています (図 12 を参照)。

MCU が実行を開始して、電源から電流を引き込むときに寄生的なリセットが発生しないように、電圧低下の基準値である  $V_{IT^-}$  は、電源オンの基準値  $V_{IT^+}$  よりも低くなっています (ヒステリシス)。

$V_{DD}$  が以下の値を下回ると、BOR 回路でリセットが生成されます。

- $V_{DD}$  が上昇するときは  $V_{IT^+}$

- $V_{DD}$  が下降するときは  $V_{IT^-}$

BOR 機能の動作を図 12 に示します。

オプション・バイトを使用して、この電圧閾値を低、中、高に設定できます。

$V_{DD}$  の最小値（オシレータ周波数に対して保証されている値）を  $V_{IT^-}$  よりも高くすると、MCU で可能なモードは以下の 2 種類のみになります。

- 全面的にソフトウェアで制御されるモード

- 静的で安全なリセット・モード

これらの条件下では、外部リセット・ハードウェアを必要とせずに、アプリケーションは必ず安全に動作します。

ブラウンアウト・リセット状態では NRST ピンが Low に保持されているので、MCU で他のデバイスをリセットできます。

注： BOR を使用すると、外部リセット回路を必要とせずにデバイスを使用できます。

BOR は、オプション・バイトで選択できるオプション機能です。製品の仕様を参照してください。

図 12. ブラウンアウト・リセットとリセットの比較

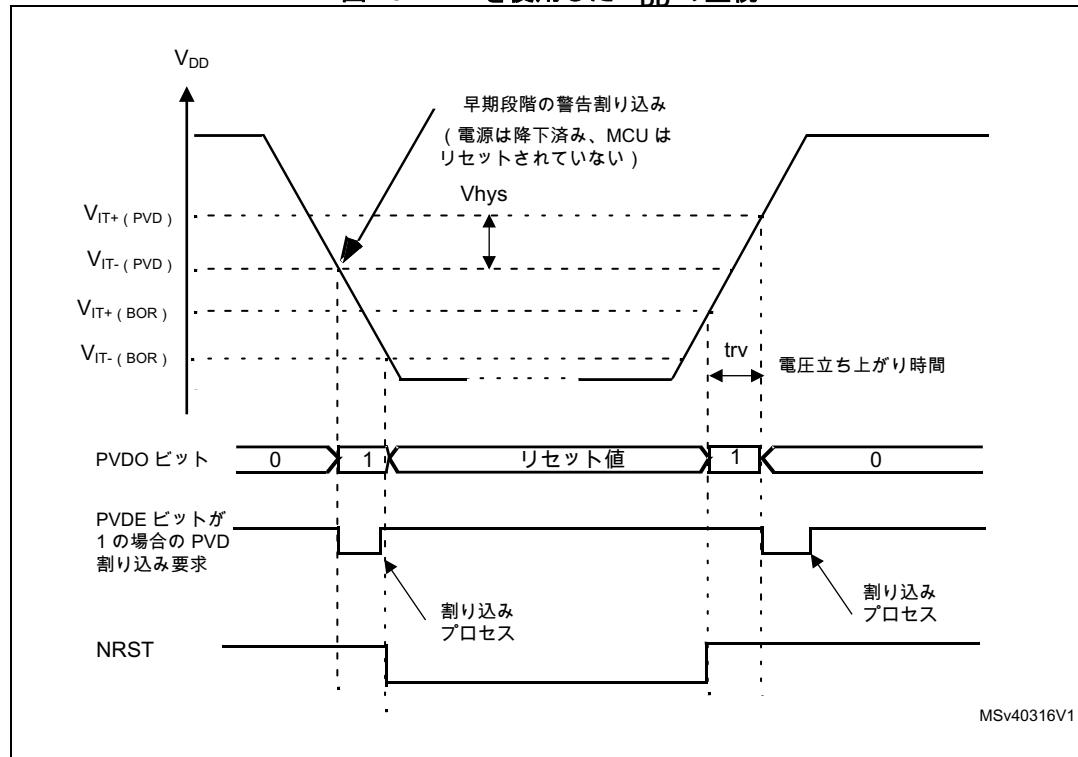

### 3.1.2 プログラム可能な電圧検出器 (PVD)

BOR 同様に、この機能も、電源が外部ノイズによる妨害を受けてもマイクロコントローラが安全に動作できるようにすることで、EMS 性能が向上します。

また、PVD にもさまざまなレベルがあるので (BOR レベルよりも約 200 mV 高い電圧)、BOR によるリセットが発生する前にワーニングを得ることができます。電源電圧が PVD の閾値に達すると割り込みが生成され、電源がデバイスに対して正しいレベル (製品のデータシートを参照) に復帰するまでの間、何らかのユーザ措置の要求や、割り込みルーチンによるアプリケーションのシャットダウンなどを実行することができます。

#### 例

$f_{CPU}$  が 8 ~ 16 MHz の場合、最低動作電圧レベルは 3.5 V です。

PVD の機能は、基準電圧である  $V_{IT^-}$  および  $V_{IT^+}$  とメイン電源電圧である  $V_{DD}$  とのアナログ比較に基づいて動作します。寄生的な検出を防止するために、降下する電圧に対する基準値  $V_{IT^-}$  は、上昇する電圧に対する基準値  $V_{IT^+}$  よりも低くなっています (ヒステリシス)。

PVD のコンパレータ出力は、リアル・タイム・ステータス・ビット (PVDO) を使用してアプリケーション・ソフトウェアで直接読み出すことができます。このビットは読み出し専用です。

# 参考資料

AN1709

ST の MCU 設計方針と EMC 固有の機能

PVD の電圧閾値は、オプション・バイトで設定する BOR の閾値を基準としています（該当製品のデータシートを参照）。

PVD 割り込みを有効にすると、閾値である  $V_{IT+}(PVD)$  または  $V_{IT-}(PVD)$  (PVDO ビットがトグル) に電源電圧が達すると割り込みが生成されます。

電圧が降下する条件下では、PVD 割り込みが早期段階のワーニングとして機能するので、BOR によってマイクロコントローラがリセットされる前にソフトウェアで安全にシャットダウンできます（図 13 を参照）。

電源電圧の立ち上がりエッジでの割り込みを使用して、 $V_{DD}$  のワーニング状態が終了したことをアプリケーションに通知します。

電源電圧の立ち上がり時間  $t_{rv}$  が 256 CPU サイクルまたは 4096 CPU サイクル未満（マイクロコントローラのリセット遅延時間によります）である場合は、電源電圧が  $V_{IT+}(PVD)$  に達しても PVD 割り込みは生成されません。

$t_{rv}$  が 256 CPU サイクルまたは 4096 CPU サイクルを超える場合は以下のいずれかになります。

- 閾値  $V_{IT+}(PVD)$  に達する前に PVD 割り込みが有効になった場合は、2 回の PVD 割り込みを受け取ります。1 回目は PVDE ビットがセットされたとき、2 回目は電源電圧が閾値に達したときにそれぞれ発生します。

- 閾値  $V_{IT+}(PVD)$  に達した後で PVD 割り込みが有効になった場合は 1 回の PVD 割り込みのみが発生します。

図 13. PVD を使用した  $V_{DD}$  の監視

### 3.1.3 I/O 機能とプロパティ

集積回路のデータシートには、回路の損傷を防止するために控えめな限界と条件が記載されていますが、回路内部の故障メカニズムを理解していると、ハードウェア・システムの設計で有用なことがあります。賢明な保護設計により、不適切な電圧と条件に遭遇するリスクを低減できるからです。

最大定格や最大条件の非遵守によって発生する可能性のある損傷をすべて分類し、予測することは不可能です。これは、故障の発生に関する可変要因の数が膨大であるからです。実際、ある過電圧の条件を適用する場合、デバイスへの影響は、ロットごとのプロセスのばらつき、動作温度、マイクロコントローラと他のデバイスとの外部インターフェース条件などで大幅に異なります。

以降のセクションでは、システム設計者がマイクロコントローラ・デバイスが損傷するリスクを低減するうえで効果的な、背景となる技術情報を取り上げます。

#### 静電気放電とラッチアップ

高電圧静電気はデバイスの恒久的な損傷を引き起こす可能性がありますが、通常、CMOS 集積回路は、このような静電気への露出に対する感度は高いです。多く見られる故障として酸化薄膜の絶縁破壊があり、漏洩電流の増加や、ときには短絡の原因となります。

集積回路で発生することが多い現象としてラッチアップもあります。この現象では、寄生的なバイポーラ構造やシリコン制御整流器 (SCR) の不要なターン・オン動作によってデバイス温度が異常上昇し、短時間で破壊される可能性があります。これらの意図しない構造は、寄生的なバイポーラ・トランジスタのエミッタ、ベース、コレクタとして動作する P 領域と N 領域で形成されます。この構造では、ウェルとサブストレートのシリコンが持つバルク抵抗が、SCR 構造上の抵抗として機能します。 $V_{SS}$  未満の電圧または  $V_{DD}$  を超える電圧を印加したとき、SCR の寄生抵抗に電圧降下が発生するほどの電流が流れると、SCR がオン状態になる可能性があります。この SCR をオフ状態にするには、デバイスへの電源供給を遮断する必要があります。

ST マイクロエレクトロニクスによる設計では、レイアウトとプロセスの工夫により、静電気放電 (ESD) とラッチアップによる影響を低減する対応策を導入しています。当然のことながら、デバイスを破壊する試験であることから、すべてのデバイスを試験することはできません。製品の信頼性を保証するためには、品質保証に関する ST マイクロエレクトロニクスの社内規格と社内勧告に従い、デバイスのグループに対する破壊試験を実施しています（[セクション 2.1.2 : ラッチアップ \(LU\)](#) を参照）。

#### 保護インターフェース

ST 製マイクロコントローラの入出力回路は、ESD とラッチアップの問題を考慮して設計されていますが、ST 製マイクロコントローラのピンに不適切な電圧が印加され、大電流が注入されるようなアプリケーションとシステムでは、損傷のリスクを低減するハードウェア対策を実装することを強くお勧めします。このようなストレス条件を防止するには、通常はローパス・フィルタとクランプ・ダイオードを使用すれば十分です。

適切な範囲外の電圧と電流が発生するリスクは、システム内部よりも外部からの信号で高くなります。ノイズによる影響や制御不能なスパイクは、内部信号よりも外部信号で発生する確率が高いからです。フィルタなどの専用インターフェース回路を採用することで、予期しないタイミングの遅延やシステム全体の処理速度の低下などマイクロコントローラの総合性能が影響を受ける可能性がある点には注意が必要です。

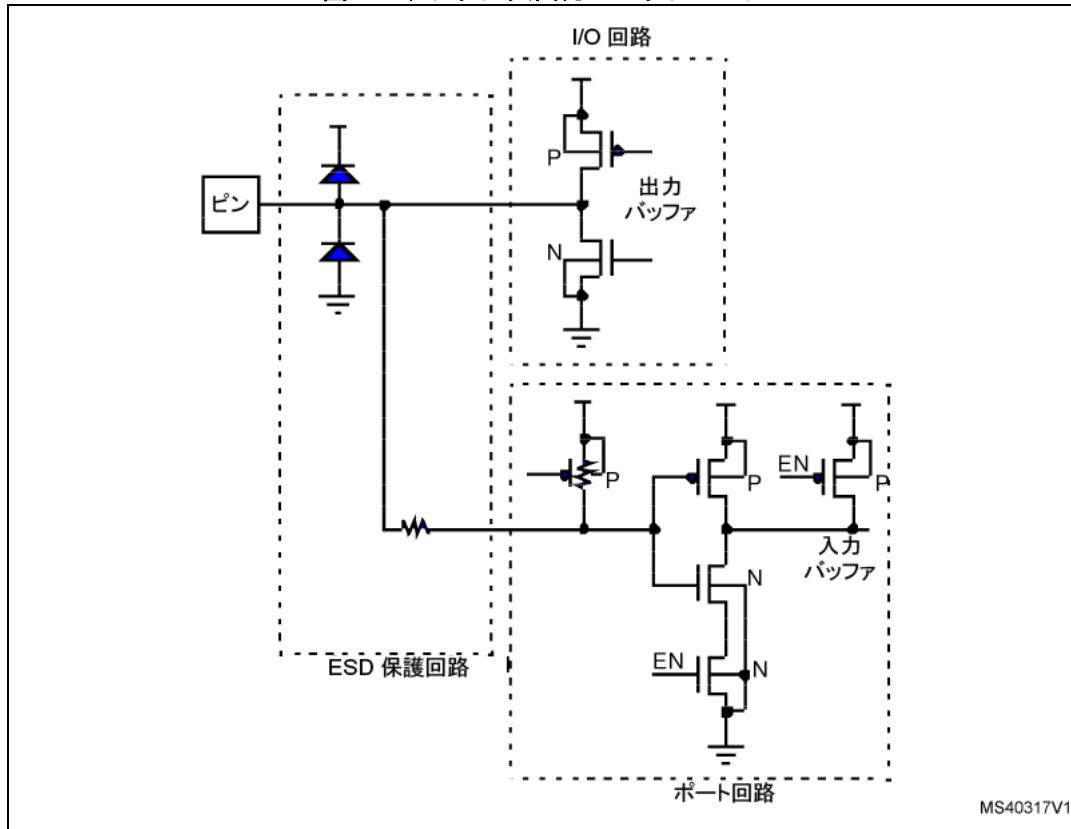

図 14. デジタル入出力 - プッシュプル

## 内部回路：デジタル I/O ピン

ST 製マイクロコントローラで、入力としても出力としても動作できるピンの回路を図 14 に示します。この回路は、一般的な入力バッファを備え、出力バッファにはプッシュプル設定を採用しています。入力部分を使用しているときに出力バッファを無効にすることはできますが、不適切な条件が発生すると、バッファの MOS トランジスタ自体がピンの動作に影響する可能性があることは明らかです。事実、出力バッファの p チャネル・トランジスタは、V<sub>DD</sub> に直結したダイオードを形成し（ドレンの p 型拡散層がピンに接続され、n 型ウェルが V<sub>DD</sub> に接続）、出力バッファの n チャネル・トランジスタは、V<sub>SS</sub> に接続したダイオードを形成します（p 型サブストレートが V<sub>SS</sub> に接続され、ドレンの n 型拡散層がピンに接続）。これらのダイオードと並列に、ESD イベントからロジックを保護するために専用の回路（MOS、ダイオード、および入力直列抵抗）が実装されています。

これらの増設デバイスの最も重要な特性は、正常な動作モードには干渉せず、限界を逸脱した条件が発生したときは、ロジック回路の恒久的な損傷を防止するように動作する必要があることです。

使用している MCU によっては、I/O ポートの該当するレジスタに書き込むことで、オープンドレイン出力としても動作するようにプログラムできる I/O ピンを備えていることがあります。出力バッファの p チャネル・トランジスタのゲートは無効になっていますが、物理的にはこのトランジスタは存在しているので、V<sub>DD</sub> に接続したダイオードとしては機能している点に留意することが重要です。用途によっては、ピンに印加される電圧が V<sub>DD</sub> の値を超えることがあります（たとえば、マイクロコントローラの電源がオフの状態で、外部ラインが高い電圧を維持している場合）。このような条件下では、ダイオードを通じて電流が注入されるので、デバイスに恒久的な損傷を与えるリスクが発生します。

どのような場合も、I/O ピンをオープンドレインとしてプログラムしておくことで、システムの複数のピンが同じポイントに接続された場合の保護機能が得られます。当然のことながら、出力ドライバ

# 参考資料

の競合を避けるために、これらのピンのうち、どの時点でも出力となるピンは 1 本のみとなるようなプログラム上の措置がソフトウェア側で必要です。電流が競合するリスクを低減するために、これらのピンを出力オーブンドレインとして設定することをお勧めします。

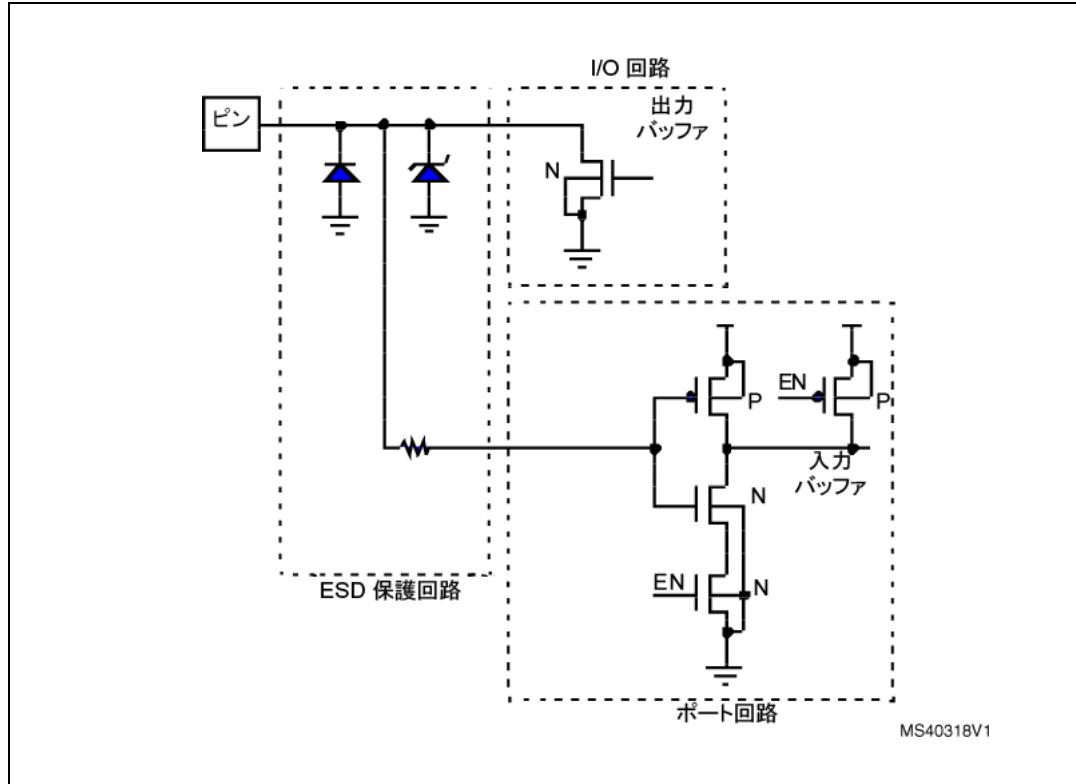

図 15. デジタル入出力 - 真のオーブンドレイン出力

真のオーブンドレイン・ピンの回路を図 15 に示します。この場合は、 $V_{DD}$  への接続経路 (p チャネル・ドライバ、ESD 保護ダイオード、内部的な弱いプルアップ) がすべて取り除かれています。これは、システムがマイクロコントローラの電源をオフにすることで、デバイスに電流が注入されることなく、ピンに高い電圧を維持できるようにすることを目的としたものです。複数のデバイスが 1 本のシリアル・バスに接続されている場合は、このような条件が普通に発生する可能性があります。通信に関与していないデバイスがあれば、その電源をオフにすることでシステムの電流消費を削減できます。

不適切なレベルの負電圧がマイクロコントローラの I/O ピンに印加されても、(プッシュプル出力と真のオーブンドレイン出力のどちらでも) クランプ・ダイオードが必ず存在してアクティブになっています (ESD 保護回路と n チャネル・ドライバを参照)。

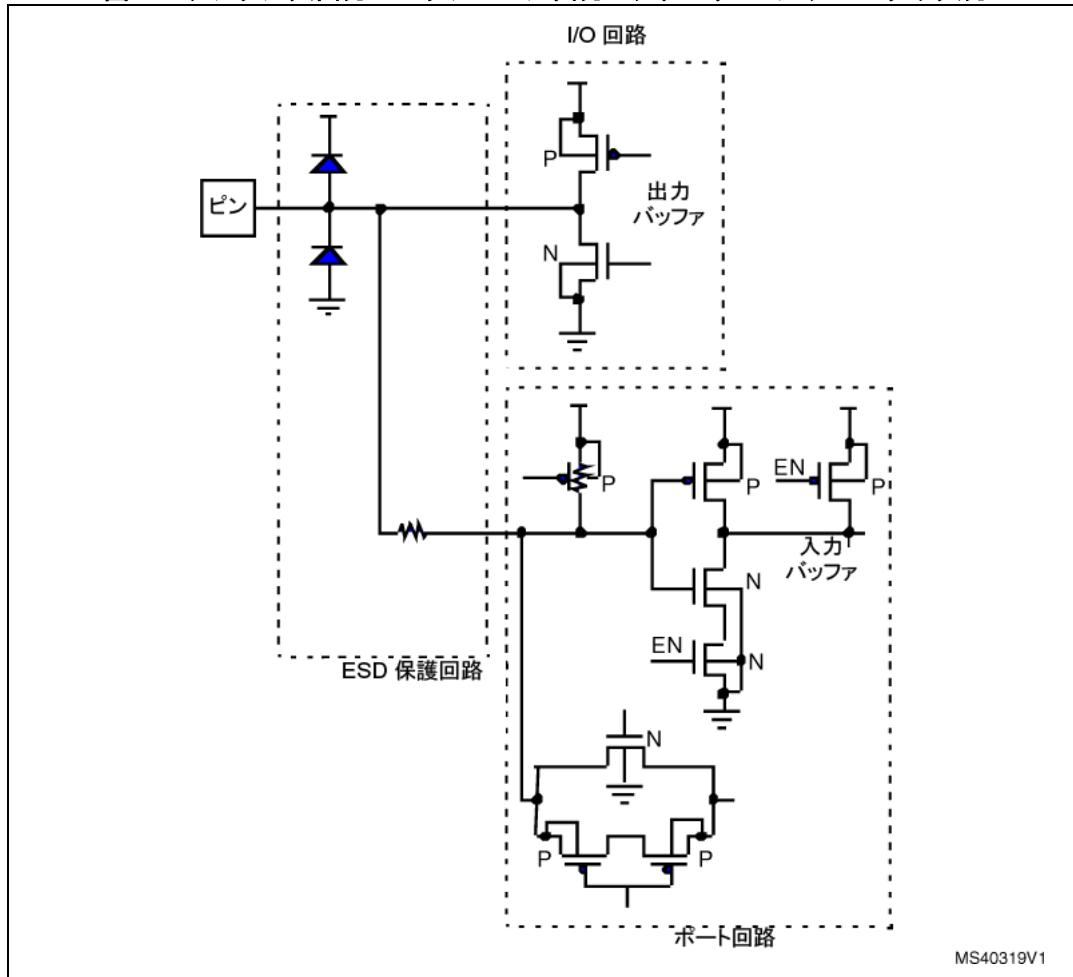

## 内部回路：アナログ入力ピン

アナログ入力に使用されている内部回路を図 16 に示します。根本的には、これはアナログ・デジタル変換器 (ADC) の入力チャネルを選択するためのアナログ・マルチプレクサを追加したデジタル I/O です。

マルチプレクサの p チャネル・トランジスタと n チャネル・トランジスタが存在することで、不適切な電圧条件が発生したときのピンの動作が影響を受ける可能性があります。これらのトランジスタは、低ノイズのロジックで制御され、p チャネル・トランジスタの n 型ウェルも含め、 $AV_{DD}$  と  $AV_{SS}$  によってバイアスされています。意図しない電流注入を防止するために、アナログ電源電圧とデジタル電源電圧の両方を基準とした入力電圧値を必ず確認することが重要です。このような電流注入を制限しないと、デバイスが破壊されることがあります。

図 16. デジタル入出力 - プッシュプル出力 - アナログ・マルチプレクサ入力

## 3.2 輻射

### 3.2.1 内部 PLL

ST 製マイクロコントローラの中には、プログラム可能な PLL クロック・ジェネレータを内蔵し、3 ~ 25 MHz の標準的な水晶発振子を使用して数百 MHz までの広範囲な内部周波数が得られるものがあります。この機能により、廉価な中程度の周波数の水晶発振子を使用して ST 製マイクロコントローラを動作し、高い内部周波数による高水準のシステム性能を実現できます。高周波数ソースはチップ内部に封入されているので、PCB (プリント回路ボード) のパターンや外部部品には高周波信号が流出しません。これによって、アプリケーションで発生する可能性のあるノイズ輻射を低減できます。

PLL 回路網を使用することで、CPU クロックに対して外部の散発性妨害 (グリッチ) をフィルタすることができます。

## 3.2.2 グローバルな低消費電力手法

### 低消費電力オシレータ

オシレータは、主なノイズ発生源のひとつです。このノイズ輻射を低減するには、オシレータによって発生する電流を制限します。

ST 製マイクロコントローラの中には、マルチオシレータ・ブロック (MO) で構成する 4 種類のクロック・ソースによってメイン・クロックを生成できるものがあります。この機能によって、設計者は、コスト、性能、ノイズ輻射の面から最適なトレードオフを容易に選択できます。クロック・ソースを、そのノイズが多い順に以下に挙げます。

- 外部ソース

- 水晶発振子またはセラミック発振子によるオシレータ

- 内部高周波 RC オシレータ

各オシレータは、消費電力の面から所定の周波数範囲において最適化されていて、オプション・バイトで選択できます。関連するハードウェア設定を図 17 に示します。それぞれの詳細については、データシートの電気的特性のセクションを参照してください。

#### 外部クロック・ソース

外部クロック・モードでは、デューティ・サイクルが 50% 程のクロック信号（矩形波、正弦波、または三角波）で OSC1 ピンを駆動する必要があります。OSC2 ピンはグランドに接続します。

#### 水晶発振子/セラミック・オシレータ

このオシレータ群には、マイクロコントローラのメイン・クロック上できわめて正確なレートを生成できる利点があります。消費電力を低減するために、周波数範囲がそれぞれ異なる 5 つのオシレータからいずれかを選択する必要があります。この選択にはオプション・バイトを使用します（周波数範囲の詳細については、マイクロコントローラのデータシートを参照してください）。マルチオシレータのこのモードでは、出力の波形ひずみと発振開始時の整定時間を最小限にするために、発振子と負荷コンデンサを可能な限りオシレータ・ピンの近くに実装する必要があります。負荷コンデンサの値は、選択したオシレータに応じて調整する必要があります。

オシレータの発振開始に必要な遅延を避けるために、これらのオシレータは RESET フェーズでも停止しません。

#### 内部 RC オシレータ

内部 RC オシレータは、周波数精度が低いという短所はあるものの、最もコスト効果の高い方法です。その周波数は、数 MHz 台の低い範囲にあります。このモードでは、2 本のオシレータ・ピンをグランドに接続する必要があります。

プロセスのばらつきによって、ロットごとにいくらかの変動があります (20 ~ 60%)。

プロセス補償機能を内蔵した ST 製マイクロコントローラもあります（製品仕様を参照してください）。この補償機能を「トリミング可能な内部 RC オシレータ」と呼んでいます。この試験操作の手順では、プロセスのばらつきが解析され、その結果に基づいて内部オシレータが較正されます。この較正によって内部 RC に 1% の精度が得られます。この手順はユーザ側で実行することもできます。

# 参考資料

ST マルチオシレータ・システムは柔軟性を主眼に設計されており、システム設計者は、輻射、精度、およびコストの条件の最適な妥協点を特定できます。

## 内部電圧レギュレータ（低消費電力コアを備えた MCU の場合）

ST 製マイクロコントローラの中には、外部電源経由で内部電圧レギュレータを使用してコアに電源供給しているものもあります。

この電圧レギュレータでは、MCU コアに起因する EMI を以下の 2 点の効果によって低減できます。

- CPU の電源の低電圧化

- 外部 MCU 電源と CPU 電源の分離

オシレータの使用方法については、アプリケーション・ノート「Oscillator design guide for STM8S, STM8A and STM32 microcontrollers」(AN2867) を参照してください。

## 3.2.3 出力の I/O 電流制限およびエッジ・タイミング制御

ST 製マイクロコントローラには複数の出力バッファが内蔵されていますが、これらのスイッチング時の寄生発振を防止するために、そのスイッチング速度が制御されています。MCU の設計では、ノイズと速度とのトレードオフが図られています。

## 4 MCU を使用したアプリケーションの EMC ガイドライン

多岐にわたるアプリケーションから得られた経験に基づくガイドラインを以下に示します。

### 4.1 ハードウェア

ノイズの主な受容先と生成源は、プリント回路ボード（PCB）のパターンと配線であり、それらが MCU に近い場合にその傾向が顕著です。したがって、ノイズを防止するために最初に講じるべき措置は、PCB のレイアウトと電源の設計に関するものです。

一般的に、MCU 周辺の部品点数が少ないほど、ノイズに対する耐性は高くなります。たとえば、ROM を持たないソリューションは、内蔵メモリ回路に比べると、ノイズに対する感度が高く、より大きなノイズ源となることが一般的です。

#### 4.1.1 PCB レイアウトの最適化

基本的には、励起するとアンテナとして機能するパターンや部品がノイズを受信し、発信します。どのループやパターンにも寄生インダクタンスと寄生静電容量が存在し、電流、電圧、電磁束の変動があると、エネルギーを放射したり、吸収したりします。

MCU チップ自体は、その寸法が EMI 信号の波長よりも小さいので、EMI に対する耐性が高く、EMI の生成も少なくなっています（GHz 帯域の EMI 信号の波長は数十 cm ですが、チップのサイズは一般的に数 mm 台です）。したがって、ループが小さく、ワイヤが短い单一チップのソリューションであればノイズの問題は少なくなります。

PCB レベルでの最初の措置は、アンテナになる可能性のある部分を少なくすることです。MCU に接続されている電源、オシレータ、I/O などのループとワイヤには特別な注意を払うようにします。オシレータのループは高周波で動作しているので、図 18 に示すように特に小さくする必要があります。

一般的に PCB パターンのインダクタンスと静電容量の両方を小さくすることは困難です。経験則からすると、ほとんどの場合はインダクタンスを最小限にすることが先決です。

図 18. PCB 上でのオシレータのレイアウト例

PCB パターンの長さと面積を小さくすることで、そのインダクタンスを小さくすることができます。そのようなレイアウトを実現するには、PCB の同じ層でパターンのループを互いに近く配置するか、別々の層で上下に配置します（図 19）。このようにすることでループの面積が小さくなり、互いの電

# 参考資料

AN1709

MCU を使用したアプリケーションの EMC ガイドライン

磁界が減少します。

インダクタンス値とワイヤ・ループで決まる面積との比率の大きさは  $10 \text{ nH/cm}^2$  前後です。インダクタンスが低いワイヤとして、同軸ケーブルやツイスト・ペア・ケーブルのほか、1 層をグランド層、別の 1 層を電源層とした多層 PCB があります。PCB パターンの拡大や電流に対して並列に接続した複数の小容量コンデンサに起因して、PCB パターンの電流密度が小さくなることもあります。

重要な条件下では、MCU と PCB 間の距離も最小限にする必要があります。これは、MCU とその周囲との間に形成されるループの面積を最小限にすることです。この条件を実現するには、セラミック MCU パッケージをプラスチック・パッケージに変更することやデュアル・イン・ライン・パッケージの代わりに表面実装を使用することにより、MCU パッケージと PCB との間に介在するソケットを排除します。

注： ボードのビアはインダクタンスとして機能します。ビアの使用を可能な限り避けるようにします。必要に応じて複数のビアを使用します。

図 19. PCB パターンのループ面積削減

注： この試験は両面 PCB で実施されています。絶縁ボードの厚さは 1.5 mm、銅箔の厚さは 0.13 mm、ボード全体のサイズは 65 x 200 mm です。

## 4.1.2 電源のフィルタリング

電源は回路のすべての部品で使用されているので、特別の注意が必要であると考える必要があります。信号レベルと電源電流が干渉しないように、電源のループをデカップリングする必要があります。1 か所のノードを回路の共通点としたスター配線を使用することで、このようなループを互いに分離できます（図 20）。

MCU の電源ピンにきわめて近い位置にデカップリング・コンデンサを配置して、発生するループを最小限にします。このコンデンサは、入力保護ダイオードを通じて MCU から流出する寄生電流を、電圧の顕著な上昇を伴わずに吸収できる静電容量を持つことも必要です。このようなボードのデカップリングは電解コンデンサ（一般的には  $10 \sim 100 \mu\text{F}$ ）で実現できます。電解コンデンサに使用されている誘電体が、大きな静電容量を備えているからです。ただし、電解コンデンサは高周波域（一般的には 10 MHz 以上）でインダクタンスとしての性質も示します。一方、セラミック・コンデンサやプラスチック・コンデンサは高周波域でも容量性を維持します。高周波で動作している重要なチップの高周波域デカップリングとしては、たとえば  $0.1 \sim 1 \mu\text{F}$  のセラミック・コンデンサを使用します。

図 20. 電源のレイアウト例

### 4.1.3 I/O 設定

オープン（フローティング）ピンは回路に対する潜在的に危険を起こす要因となります。

アプリケーションで使用していない I/O ピンは、出力 Low の状態に設定することをお勧めします。これによって電流消費を最小限にすることもできます。

マイクロコントローラを使用したアプリケーションでは、SPI、I2C クロック、USB、PWM などの高速デジタル I/O と通信インターフェースが輻射の主な発生源となります。ここでは立ち上がり時間と立ち下がり時間が重要です。一般的には、RC ロー・パス・フィルタを追加した設計とします。

### 4.1.4 シールド

ノイズに対する感度と輻射を低減するうえでシールドは効果的ですが、その効果はシールドとして選択した材料（透磁性が高く、抵抗率が低いこと）および安定した電圧源に接続しているかどうかに直接左右されます。このような接続として、低直列インピーダンス（低インダクタンス、低抵抗）を介したデカップリング・コンデンサへの接続などがあります。

主な妨害の発生源が MCU ボードの近くに存在し、それが強い  $dV/dt$  ジェネレータ（変圧器やクラウドストロンなど）であると、静電場によってノイズが伝搬します。ノイズ源と制御ボード間の重大なカッピングは容量性です。銅などの導電性の高いシールド材を使用して、制御ボードを囲むフレーム・ケージを構成すると、ノイズに対する耐性が飛躍的に向上します。

強い摂動源が  $dl/dt$  ジェネレータ（リレーなど）である場合は、それが強い電磁界の発生源になります。したがって、ボードのノイズ耐性の向上を図るには、シールド材料（合金など）透磁性がきわめて重要です。また、高いシールド効果を確保するには、シールド上の穴の数とサイズを可能な限り小さくする必要があります。

重要な条件下では、MCU の下にグランド・プレーンを配置することと、デバイスと PCB の間に介在するソケットを排除することで、ノイズに対する MCU の感度を低くすることができます。実際、これら両方の措置を講じることで、MCU、その電源、その I/O と PCB との間に存在する見かけ上のループ面積が減少します。

## 4.2 ESD 保護取り扱い上の注意点

ESD 損傷に対するマイクロコントローラ・デバイスの感度を判断する詳しい手順については、アプリケーション・ノート「Electrostatic discharge sensitivity measurement」(AN1181) を参照してください。

## 4.3 ファームウェア

この部分は、ST のウェブサイトに用意されている専用アプリケーション・ノート (AN1015) を参照してください。

## 4.4 EMC 関連組織へのウェブ・リンク

- FCC : 米国連邦通信委員会 - <http://www.fcc.gov>

- EIA : 米国電子工業会 - <http://www.eia.org/>

- SAE : 米国自動車技術者協会 - <http://www.sae.org>

- IEC : 国際電気標準会議 - <http://www.iec.ch>

- CENELEC : 欧州電気技術規格調整委員会 - <http://www.cenelec.be>

- JEDEC : 電子デバイス技術合同協議会 - <http://www.jedec.org>

## 5 結論

どのようなマイクロコントローラ・アプリケーションでも、その開発着手段階で EMC 要件を検討する必要があります。ST 製マイクロコントローラのデータシートに記述されている規格、機能、およびパラメータは、システム設計者が目的とするアプリケーションに最適な部品を判断するうえで効果的です。EMC とシステムの安定性を最適化するには、ハードウェアとファームウェアに関する注意事項を考慮する必要があります。

# 参考資料

AN1709

2015年12月14日よりも前のEMI分類

## 付録A 2015年12月14日よりも前のEMI分類

ここで取り上げる情報はセクション 2.2.1 : EMI 放射試験を補完するものです。

2015年12月14日より、輻射測定周波数範囲の上限が1GHzから2GHzに引き上げられています。これにより、分解能帯域幅(RBW)が大きくなりました。この変更は、マイクロコントローラの進歩に伴うものです。最近のマイクロコントローラでは、PLLの遙倍係数を高くすることで、これまで以上に高い周波数の内部クロックを内蔵するようになっています。その周波数は、200MHzを超えることもあります。これにより、高周波の広帯域高調波輻射が発生するようになりました。

その結果、新しいスペクトラム・アナライザ設定に合わせて、ST社内のEMIレベル分類パターンが更新および調整されています。

100kHz ~ 1GHz の周波数範囲で 2015年12月14日よりも前に実施された測定に関連するデータについては、図 21 および表 10 を参照してください。

図 21. 2015年12月14日よりも前のST社内EMIレベル分類

STの経験則により、各EMIレベルに伴う潜在的なリスクは以下のように定義されています。

- レベル4を超える場合 : EMIレベルに起因する高いリスクが存在

- レベル4 : EMI基準適合のためのコストが必要

- レベル3 : 中程度のEMIリスク

- レベル2 : 最小限のEMIリスク

- レベル1 : きわめて低いEMIリスク

# 参考資料

2015年12月14日よりも前のEMI分類

AN1709

表 10. 周波数範囲に対するスペクトラム・アナライザの分解能帯域幅

(狭帯域のEMI)

| 周波数範囲 (MHz) | 分解能帯域幅 | 検出器の種類 |

|-------------|--------|--------|

| 0.1 ~ 1     | 1 kHz  | ピーク検出  |

| 1 ~ 10      | 1 kHz  |        |

| 10 ~ 100    | 1 kHz  |        |

| 100 ~ 1000  | 9 kHz  |        |

# 参考資料

AN1709

改版履歴

## 改版履歴

表 11. 文書改版履歴

| 日付             | 版 | 変更内容                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2003 年 9 月     | 1 | 初版発行                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2016 年 2 月 3 日 | 2 | <p>IEC 1000 規格を IEC 61000 に変更。</p> <p>セクション 2.1.1 : 機能性 EMS 試験で、NSG 435 プロバイダを変更。表 3 : ST の ESD 深刻度レベルを更新。</p> <p>修正した表 7 で、静的ラッチアップの例を STM32L062K8 に変更。</p> <p>セクション 2.1.2 : ラッチアップ (LU) から ST72F521 の DLU 試験結果例の表を削除。</p> <p>セクション 2.1.3 : 絶対電気的感度 :</p> <ul style="list-style-type: none"><li>- ESD 試験中は部品に通電しないことを追記。</li><li>- 機械モデルを削除。</li><li>- セクション : チャージ・デバイス・モデル (CDM) を追加。</li></ul> <p>セクション 2.2 : 電磁干渉 (EMI) を更新。</p> <p>セクション 3.1 : 感受性 :</p> <ul style="list-style-type: none"><li>- 低電圧検出器 (LVD) をブラウンアウト・リセット (BOR) に置き換え。</li><li>- <u>RESET</u> を NRST に置き換え。</li><li>- 最大動作周波数対電源電圧の図を削除。</li><li>- 補助電圧検出器 (AVD) をプログラム可能な電圧検出器 (PVD) に置き換え。</li><li>- 複数の <math>V_{DD}</math> と <math>V_{SS}</math> に関するセクションを削除。</li></ul> <p>セクション 3.2.1 : 内部 PLL を更新。</p> <p>セクション : 内部 RC オシレータおよびセクション : 内部電圧レギュレータ (低消費電力コアを備えた MCU の場合) を更新。</p> <p>セクション 4.2 : ESD 保護取り扱い上の注意点にトレイを追加。</p> <p>付録 A : 2015 年 12 月 14 日よりも前の EMI 分類を追加。</p> |

表 12. 日本語版文書改版履歴

| 日付         | 版 | 変更内容      |

|------------|---|-----------|

| 2018 年 6 月 | 1 | 日本語版 初版発行 |

**重要なお知らせ（よくお読み下さい）**

STMicroelectronics NV およびその子会社（以下、ST）は、ST製品及び本書の内容をいつでも予告なく変更、修正、改善、改定及び改良する権利を留保します。購入される方は、発注前にST製品に関する最新の関連情報を必ず入手してください。ST 製品は、注文請書発行時点での有効なST の販売条件に従って販売されます。

ST製品の選択並びに使用については購入される方が全ての責任を負うものとします。購入される方の製品上の操作や設計に関してST は一切の責任を負いません。

明示又は默示を問わず、STは本書においていかなる知的財産権の実施権も許諾致しません。

本書で説明されている情報とは異なる条件でST 製品が再販された場合、その製品についてSTが与えたいかなる保証も無効となります。

ST およびST ロゴはSTMicroelectronics の商標です。その他の製品またはサービスの名称は、それぞれの所有者に帰属します。

本書の情報は本書の以前のバージョンで提供された全ての情報に優先し、これに代わるものです。

この資料は、STMicroelectronics NV 並びにその子会社(以下ST)が英文で記述した資料（以下、「正規英語版資料」）を、皆様のご理解の一助として頂くためにSTマイクロエレクトロニクス(株)が英文から和文へ翻訳して作成したものです。この資料は現行の正規英語版資料の近時の更新に対応していない場合があります。この資料は、あくまでも正規英語版資料をご理解頂くための補助的参考資料のみにご利用下さい。この資料で説明される製品のご検討及びご採用にあたりましては、必ず最新の正規英語版資料を事前にご確認下さい。ST及びSTマイクロエレクトロニクス(株)は、現行の正規英語版資料の更新により製品に関する最新の情報を提供しているにも関わらず、当該英語版資料に対応した更新がなされていないこの資料の情報に基づいて発生した問題や障害などにつきましては如何なる責任も負いません。

© 2018 STMicroelectronics - All rights reserved