## OTP programming for M0-9 SPI devices

### Introduction

OTP (one-time programmable) is a type of non-volatile memory that can be programmed only once and cannot be modified later. This means that once a '1' has been written into the OTP memory, it cannot be erased.

In an integrated circuit, data is usually processed by a series of functional blocks. Each of them has one or more inputs and one or more outputs. With DIAO technology through OTP, it is possible to program the OTP memory to directly associate an input to a specific output without the need of an intermediate functional block. This approach offers several advantages to end customer: the possibility to use the same device in different configurations, reduce the number of microcontroller I/Os dedicated to parallel commands, define the appropriate strategy for fail safe operation. Furthermore, it reduces the number of functional blocks required to process data, simplifying the design of the integrated circuit, and reducing power consumption.

### 1 How to program

The direct input assignment to output through OTP is achievable by setting two dedicated bits per channel in the OTP memory map documented in the product datasheets, in the OTP programming chapter (here below an example for six channels VN9D30Q100F):

Bit 1, bit 0 Bit 1, bit 0 Bit 1, bit 0 Bit 1, bit 0 OTP memory map (register 3Eh) 00(1) 01 10 11 CH<sub>5</sub> DI0 DI0 DI1 **OFF** CH4 DI1 DI1 DI0 **OFF** CH3 DI1 DI0 DI1 OFF CH2 DI1 DI0 DI1 OFF CH1 DI1 DI0 DI1 **OFF** CH<sub>0</sub> DI0 DI0 DI1 OFF

Table 1. OTP memory map for VN9D30Q100F

The device is provided with the default configuration corresponding to the first column in the previous table (00). A customized configuration for each channel is possible by changing the two dedicated bits.

Each output status Register (OUTSRx) per channel contains the bits DIOTP1, DIOTP0 which report the assigned direct input signal to the channel. In addition, DIENSR bit reflects the logic state of the assigned direct input. Here below an example of output status registers for six channels VN9D30Q100F:

Table 2. Address 20 h to 25 h - output status registers channels 0 to 5

| Bit | Name            | Access | Reset | Content                                                                                                                                                                |

|-----|-----------------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | DIENSR          | R      | 0     | Direct input status, image of associated DI logic level (according to OTP allocation)                                                                                  |

| 14  | DIOTP1          | R      | х     | Associated Dix input description bit 1                                                                                                                                 |

| 13  | DIOTP0          | R      | х     | Associated Dix input description bit 0                                                                                                                                 |

| 12  | CHFBSRx         | R      | 0     | Channel feedback status. Combination of OTDIFF, OT, OVERLOAD detection (VDS at turn-off)                                                                               |

| 11  | VDSFSRx         | R/C    | 0     | VDS feedback status. This bit is '1' if VDS is high at turn-off, indicative of a potential overload condition                                                          |

| 10  | STKFLTRx        | R/C    | 0     | Output stuck to Vcc/openload off state status                                                                                                                          |

| 9   | OLPUSRx         | R      | 0     | Output pull up generator status                                                                                                                                        |

| 8   | CHLOFFS<br>Rx   | R/C    | 0     | Channel Latch-off status. This bit is set when overload blanking time has elapsed and channel is latched off. This bit must be cleared to re-enable the output channel |

| 7   | RST             | R/C    | 1     | Chip Reset                                                                                                                                                             |

| 6   | SPIE            | R/C    | 0     | SPI Error                                                                                                                                                              |

| 5   | PWMCLOC<br>KLOW | R/C    | х     | PWM Clock Frequency too low                                                                                                                                            |

| 4   | VCCUV           | R      | х     | VCC Undervoltage                                                                                                                                                       |

| 3   | Not Used        | R      | 0     |                                                                                                                                                                        |

| 2   | Not Used        | R      | 0     |                                                                                                                                                                        |

| 1   | Not Used        | R      | 0     |                                                                                                                                                                        |

| 0   | PARITY          | R      | 1     |                                                                                                                                                                        |

UM3268 - Rev 1 page 2/12

<sup>1.</sup> Represents the default configuration.

## 2 OTP programming procedure description

OTP programming mode can be entered by using the following dedicated procedure.

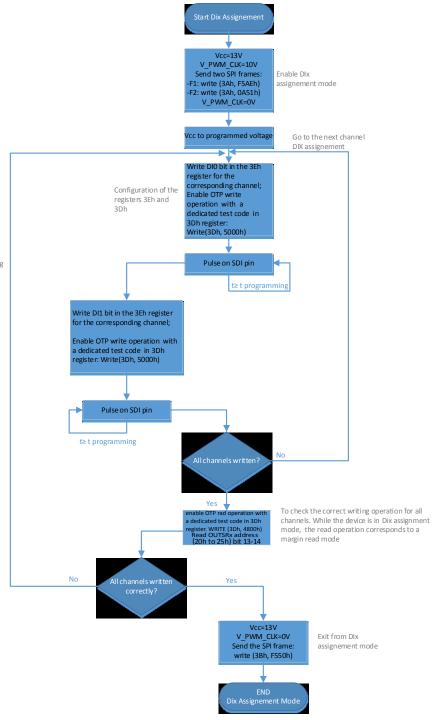

OTP programming procedure to move from the DIx default assignment to a new configuration, consists of the following four steps:

- 1. Enter the DIx assignment mode.

- 2. Perform the OTP Write operation of the new DIx assignment.

- 3. Perform the Read back operation of the DIx registers to check the correct writing operation.

- 4. Exit from the DIx assignment mode

UM3268 - Rev 1 page 3/12

### Description of each OTP programming step:

#### 1. Enter the DIx assignment mode:

- The battery voltage (Vcc) must be set to 13 V.

- Apply a voltage of 10 V on PWM\_CLK pin.

- Perform the following two dedicated SPI communications at the specified address 3Ah.

Table 3. SPI frame

| 1 <sup>st</sup> SPI | frame   | 2 <sup>nd</sup> SPI frame |         |  |  |

|---------------------|---------|---------------------------|---------|--|--|

| Address             | Content | Address                   | Content |  |  |

| 3Ah                 | F5AEh   | 3Ah                       | 0A51h   |  |  |

Release the PWM CLK pin to 0 V;

#### 2. Perform the OTP write operation of the new DIx assignment:

- Increase the battery voltage (V<sub>cc</sub>) to programming voltage (needed to perform the writing operation).

- Enable OTP write operation with the following dedicated SPI frame in the 3Dh register:

- Write (3Dh, 5000h).

- Send data to be written through the SPI interface to the "test data register 3Eh" (only one bit set to '1' at a time) for each channel.

Table 4. Test data register 3Eh for VN9D30Q100F:

| Dlx assignment |       |       |       |       |       |       |       |       |       |       |       |               |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| CI             | h5    | CI    | h4    | CI    | h3    | CI    | h2    | CI    | h1    | Cl    | า0    |               |

| bit 1          | bit 0 | bit 1 | bit 0 | bit 1 | bit 0 | bit 1 | bit 0 | bit 1 | bit 0 | bit 1 | bit 0 | parity<br>bit |

| n              | n     | n     | n     | n     | n     | n     | n     | n     | n     | n     | n     | Р             |

- Apply a pulse on the SDI pin to trigger the write operation in OTP:

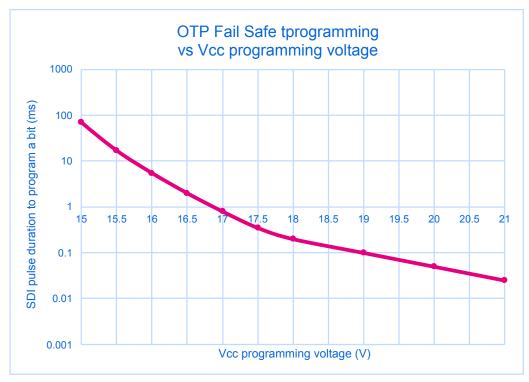

- $^{\circ}$  Min pulse duration is dependent on the applied V<sub>cc</sub> voltage (see Figure 1. Flow chart). (Only one "b" may be high on each write command. To write the configuration 00 00 00 11, for instance, this procedure must be repeated twice with successive write commands: first write 00 00 00 01, second write 00 00 00 10).

### 3. Perform a read back from registers of a new DIx assignment to check the correct writing operation:

- This operation will check the correct writing operation for all channels.

- Send a WRITE command to Address 3Dh: Write (3Dh, 4801h).

- Apply a 2 μs pulse on the SDI pin to trigger the read back operation in OTP.

- While the device is set in « Dix assignment mode», the read operation of the OUTSRx register (for example for VN9D30Q100: address 20h to 25h - bit 13,14) corresponds to a margin read mode.

### 4. Exit from DIx assignment mode:

- Set the PWM CLK pin low.

- Perform the dedicated SPI communication at the specified address 3Bh:

Table 5. SPI frame

| SPI frame |         |  |  |  |

|-----------|---------|--|--|--|

| Address   | Content |  |  |  |

| 3Bh       | F550h   |  |  |  |

Note: It is not possible to exit from DIx assignment mode if the PWM\_CLK pin remains above 8 V.

UM3268 - Rev 1 page 4/12

### 3 OTP write flow chart

Figure 1. Flow chart

Repeat the writing operation for the wrong channel. It is possible to repeat the operation for two consecutive writing

cycles

UM3268 - Rev 1 page 5/12

UM3268 - Rev 1 page 6/12

## 4 OTP programming circuit for M0-9 SPI possible solution

R1 2.2k Q1 BC857 Q2 BC846 OTP\_ENABLE 47R uC GND M0-SPI\_1 R5 1k PWM\_CLK PWM\_CLK 3.3V Zener MMBZ5226BLT1G M0-SPI\_2 PWM\_CLK GND M0-SPI\_3 PWM\_CLK

Figure 3. OTP Programming Circuit for M0-9 SPI

Table 6. Bill of materials

| Quantity | Comment       | Designator     | Footprint |

|----------|---------------|----------------|-----------|

| 1        | MMBZ5226BLT1G | D1             | SOT23     |

| 1        | BC857         | Q1             | SOT23     |

| 1        | BC846         | Q2             | SOT23     |

| 4        | 2.2k          | R1, R6, R7, R8 | 0805_R    |

| 1        | 2.7k          | R2             | 0805_R    |

| 1        | 12k           | R3             | 0805_R    |

| 1        | 47R           | R4             | 0805_R    |

| 1        | 1k            | R5             | 0805_R    |

### Circuit Characteristic:

- V<sub>cc</sub>=12.6 V, Total consumption 19mA, PWM\_CLK pin current= 0.85 mA

- AMR of PWM\_CLK pin guaranteed up to V<sub>cc</sub>=18.4 V (2.9 mA)

- Pin clamp voltage 10.9 V

- Max frequency = 600 kHz

UM3268 - Rev 1 page 7/12

## **Revision history**

Table 7. Document revision history

| Date        | Revision | Changes        |

|-------------|----------|----------------|

| 12-Feb-2024 | 1        | First release. |

UM3268 - Rev 1 page 8/12

## **Contents**

| 1    | How to program                                         | 2   |

|------|--------------------------------------------------------|-----|

| 2    | OTP programming procedure description                  | 3   |

| 3    | OTP write flow chart                                   | 5   |

| 4    | OTP programming circuit for M0-9 SPI possible solution | 7   |

| Rev  | vision history                                         | 8   |

| List | t of tables                                            | .10 |

| List | t of figures                                           | .11 |

## **List of tables**

| Table 1. | OTP memory map for VN9D30Q100F                                 |

|----------|----------------------------------------------------------------|

|          | Address 20 h to 25 h – output status registers channels 0 to 5 |

| Table 3. | SPI frame                                                      |

| Table 4. | Test data register 3Eh for VN9D30Q100F:                        |

| Table 5. | SPI frame                                                      |

| Table 6. | Bill of materials                                              |

| Table 7. | Document revision history                                      |

UM3268 - Rev 1 page 10/12

# **List of figures**

| Figure 1. | Flow chart                                          | 5 |

|-----------|-----------------------------------------------------|---|

| Figure 2. | tprogramming vs V <sub>CC</sub> programming voltage | 6 |

| Figure 3. | OTP Programming Circuit for M0-9 SPI                | 7 |

UM3268 - Rev 1 page 11/12

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

UM3268 - Rev 1 page 12/12