# How to proceed with boot ROM on STM32N6 MCUs

#### Introduction

This document describes the boot ROM code for the STMicroelectronics Arm® Cortex®-M55 core-based STM32N6 microcontroller (MCU) cluster, mainly from a black-box perspective, and serves as a guideline for users of boot ROM code functionality.

It provides a description of how boot ROM code interacts with other components in the system, covering both hardware and software interfaces. It also describes the application boot image formats supported by the boot ROM code.

This document applies to the STM32N6 MCU devices. It focuses on the startup firmware located in the boot ROM of the STM32N6 MCU, which executes on the Arm<sup>®</sup> Cortex<sup>®</sup>-M55.

This specification follows a commonly used syntax to represent requirements: the key words "MUST," "MUST NOT," "REQUIRED," "SHOULD," "SHOULD NOT," "RECOMMENDED," "MAY," and "OPTIONAL" are interpreted as described in RFC 2119 [13].

- MUST: This word, or the terms "REQUIRED" or "SHALL," means that the definition is an absolute requirement of the specification.

- MUST NOT: This phrase, or the phrase "SHALL NOT," means that the definition is an absolute prohibition of the specification.

- **SHOULD**: This word, or the adjective "RECOMMENDED," means that there may exist valid reasons in particular circumstances to ignore a particular item. However, the full implications must be understood and carefully weighed before choosing a different course.

- **SHOULD NOT**: This phrase, or the phrase "NOT RECOMMENDED," means that there may exist valid reasons in particular circumstances when the particular behavior is acceptable or even useful. However, the full implications must be understood and the case carefully weighed before implementing any behavior described with this label.

- MAY: This word, or the adjective "OPTIONAL," means that an item is truly optional. One vendor may choose to include the item because a particular marketplace requires it or because the vendor feels that it enhances the product, while another vendor may omit the same item. An implementation that does not include a particular option must be prepared to interoperate with another implementation that does include the option, though perhaps with reduced functionality. Similarly, an implementation that does include a particular option must be prepared to interoperate with another implementation that does not include the option, except, of course, for the feature that the option provides.

# 1 General information

This document applies to STM32N6 Arm®-based MCUs.

STM32N6 MCUs are microcontrollers that are based on the Arm® Cortex®-M55.

Note: Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

**Table 1. Referenced documents**

| N°  | Description                                                                   |

|-----|-------------------------------------------------------------------------------|

| [1] | Reference manual STM32N647/657xx Arm®-based 32-bit MCUs (RM0486)              |

| [2] | SD Specifications Part 1 Physical Layer Simplified Specification version 6.00 |

Table 2. Glossary

| Acronyms   | Meanings                                                                         |

|------------|----------------------------------------------------------------------------------|

| Bootloader | Software that loads and runs some other software, typically an operating system. |

| Boot ROM   | Boot firmware stored in Cortex®-M55 ROM, also named ROM code.                    |

| BSEC       | Boot and security block: it is used to manipulate OTP fuse words.                |

| CRYP       | Cryptography                                                                     |

| CM55       | Cortex®-M55                                                                      |

| CPvK       | CUK private key                                                                  |

| CUK        | Chip unique key                                                                  |

| E1CPvK     | TK1 encrypted chip private key                                                   |

| ECC        | Error correcting code                                                            |

| ECDSA      | Elliptic curve digital signature algorithm                                       |

| FSBL       | First stage bootloader: name of the binary loaded by the boot ROM code.          |

| HDPL       | Hardware protection level                                                        |

| MBR        | Master boot record                                                               |

| MCU        | Microcontroller unit                                                             |

| OTP        | One-time programmable fuse bits                                                  |

| RHUK       | The root hardware unique key: nonvolatile hardware secret unique per device      |

| UART       | Universal asynchronous receiver transmitter                                      |

| USB HS     | USB high-speed profile at 480 Mbps                                               |

UM3234 - Rev 3 page 2/50

# 2 Description

#### 2.1 Boot ROM features and functions

The boot ROM code is the initial code executed on Arm<sup>®</sup> Cortex<sup>®</sup>-M55 at power-on or reset of the STM32N6 MCU or Arm<sup>®</sup> Cortex<sup>®</sup>-M55. This boot ROM code resides in the STM32N6 on-chip boot ROM IP and typically implements the first stage of a multistage boot sequence.

The main boot ROM code features and functions are:

- Basic system initialization

- Detection of reset source, specific reset condition, and chip mode

- Bootstrapping from an attached boot memory device supporting various types of memory devices

- Downloading code over serial boot interfaces and jumping to the downloaded code

- Implementation of USB 2.0 device according to USB 2.0 HS supporting DFU 1.1

- Handling life cycle

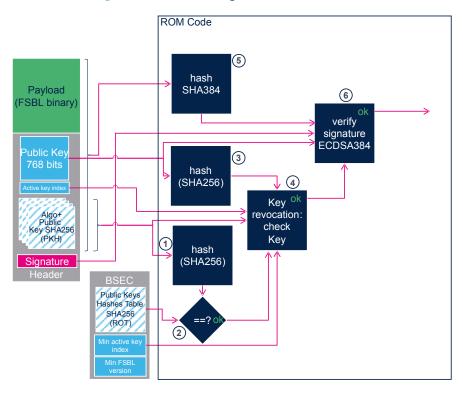

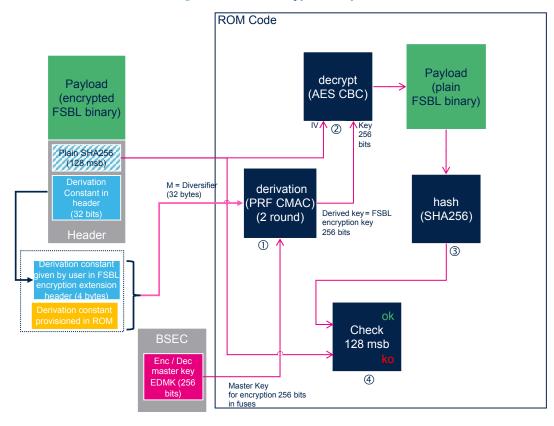

- Validation of signed images using hardware accelerators for cryptographic functions

- Support of configuration options (customization), mainly via fuses

- Support of ST key provisioning

- Support of SSP, OEM key provisioning

- · Support of blocking failure processing

See also the following subchapters for further details.

# 2.1.1 Applicable reset types

The boot ROM code placed in the STM32N6 MCU boot ROM function is generally executed whenever the Arm<sup>®</sup> Cortex<sup>®</sup>-M55 in the STM32N6 MCU is released from reset. Depending on the detected type of reset, different branches within the boot ROM code implementation are executed.

The following logical reset types are applicable and distinguished by the boot ROM code:

- SYSTEM: Logical system reset

- ST\_KEY\_PROVISIONING: Logical reset of the ST key provisioning stage condition with SFT and PIN

resets

#### 2.1.2 Supported boot memory devices

The boot memory device is the external flash memory device attached to the STM32N6 MCU on which the first stage bootloader (FSBL) is located. The boot ROM code first loads the FSBL into the internal RAM of the STM32N6 MCU and analyze it from there.

The boot ROM code supports the following types of boot memory devices:

- sNOR x4 and x8 flash devices

- HyperFlash™ Flash device

- SD memory card device (SD specifications V6.0)

- eMMC type of embedded memory card devices (eMMC specifications V5.1)

#### 2.1.3 Supported serial boot interfaces

The boot ROM code provides functionality for downloading code over a serial boot interface into the internal RAM of the STM32N6 MCU. Typically, downloading code over a serial boot interface is used to update the FSBL stored on a flash-type attached boot memory device.

The boot ROM code supports the following types of serial boot interfaces:

- USART type of serial interface using three different USART hardware function instances

- USB interface (USB 2.0 HS)

UM3234 - Rev 3 page 3/50

#### 2.1.4 Supported life cycle

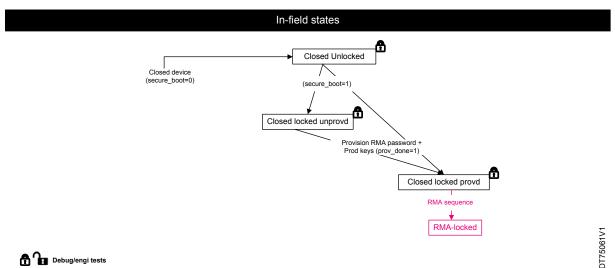

The life cycle defines the states that determine the behavior and available features of the STM32N6 MCU device during the different steps of its life. The value of fuses determines the life cycle state. The BSEC function controls these fuses. Figure 1 shows the STM32N6 MCU life cycle flow.

Figure 1. STM32N6 life cycle

The STM32N6 chip life cycles are described in the STM32N6 security architecture document. The STM32N6 chip life cycles are set through fuses. The detailed fuse configuration to select the STM32N6 life cycle is described in Section 3.2.6 and the fuses handled by the boot ROM are listed in Section 3.11.1.

The boot ROM code follows this life cycle to provide the expected features according to the life cycle state, as described in Table 3.

STM32N6 life cycle **OEM-FSBL** secure ST-FSBL secure boot ST key provisioning **Development boot** state boot x (1) CLOSED/UNLOCKED 0 Χ 0 CLOSED/LOCKED/ x <sup>(2)</sup> 0 0 0 **UNPROVD** CLOSED/LOCKED/ 0 x <sup>(2)</sup> 0 0 **PROVD**

Table 3. Boot ROM code scenario following the STM32N6 life cycle.

- 1. Authentication is not mandatory.

- 2. Secure boot enforced: authentication is mandatory.

The ST-RSSE-FW (formerly named ST-FSBL) and OEM-FSBL secure boot use cases are also detailed in the following sections.

UM3234 - Rev 3 page 4/50

# 2.2 Boot ROM flow diagram

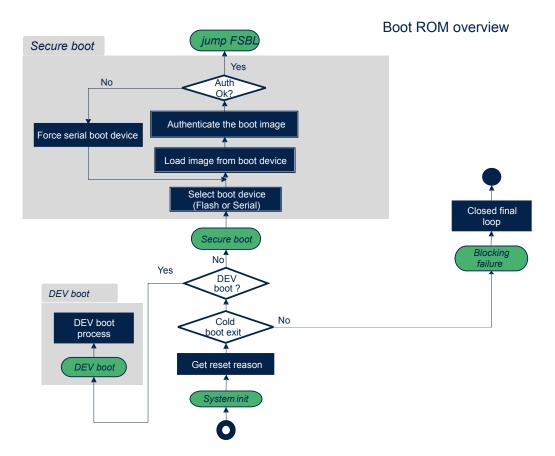

Figure 2 depicts the overall boot ROM code flow diagram, showing the main activities and branches implemented in the STM32N6 boot ROM code. More detailed descriptions are provided in the subsequent chapters of this document

Figure 2. Boot ROM code flow diagram

F75062V1

UM3234 - Rev 3 page 5/50

# 3 Interfaces

#### 3.1 Boot ROM hardware function

Figure 3 shows the layout of the boot ROM function of the STM32N6 device. In the boot ROM hardware function, there are three defined word address boundaries that allow the definition of SEC and NSEC areas, as well as always mapped (AM) and unmappable areas (UM).

Nonsecure (47 Kbytes) 0x0801FFFF Checksum (32 bytes) 0x0801FFF0 PAD Region Nonsecure or secure Always mapped 9Kbytes **NSEC AM Code** Wordaddr3\* 0x0801DC00 Nonsecure or Secure unmappable 38 Kbytes NSEC UM Code Secure (81 Kbytes) Wordaddr2\* 0x180143FF 0x08014400 Secure unmappable SEC UM Code 49 Kbytes 0x18007C00 Secure always Mapped 32 Kbytes SEC AM Code 0x18001000 boot ROM version Reset Vector 0x18000000 (secure alias)

Figure 3. Boot ROM function layout

\*Word addresses defined in boot ROM

# 3.2 Initialization steps and evaluation of reset condition and boot scenario

#### 3.2.1 Exception vector setting

In the Arm<sup>®</sup> Cortex<sup>®</sup>-M55 core, a vector table allows handling exception handlers, with one defined for each secure and nonsecure area. An undefined exception handler results in a blocking failure scenario, which is detailed in a specific chapter of this document. Index 0 of the vector table holds the address of the Main Stack Pointer (MSP). The next index is the ResetHandler vector. The start of the vector table is executed when the reset of the Arm<sup>®</sup> Cortex<sup>®</sup>-M55 core is released. It means that it sets the MSP and then executes the ResetHandler exception.

# 3.2.2 TrustZone® protection, RISAF, and cache handling

The boot ROM code implements TrustZone<sup>®</sup> protection, RISAF, and a cache handling mechanism. Table 4 shows the state of the security mechanisms depending on the boot ROM scenario executed.

Table 4. TrustZone® support setting following boot ROM scenario

| STM32N6 life cycle state | Boot ROM scenario | SAU/MPU                             | RISAF                 | Cache               |

|--------------------------|-------------------|-------------------------------------|-----------------------|---------------------|

| CLOSED-UNLOCKED          | DEV Boot          | Disabled SAU and reset MPU settings | Clear RISAF3 settings | Disable cache       |

| CLOSED-UNLOCKED          | OEM FSBL          | Disabled SAU and reset MPU settings | Clear RISAF3 settings | Keep ICACHE enabled |

UM3234 - Rev 3 page 6/50

| STM32N6 life cycle state | Boot ROM scenario | SAU/MPU                                            | RISAF                                      | Cache                                               |

|--------------------------|-------------------|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------|

| CLOSED-LOCKED-PROVD      | OEM FSBL          | Disable SAU and MPU setting update <sup>(1)</sup>  | Clear RISAF3 settings                      | Keep ICACHE enabled                                 |

| CLOSED-LOCKED-UNPROVD    | ST boot extension | Disabled SAU and MPU setting update <sup>(1)</sup> | Clear RISAF3 settings                      | Keep ICACHE enabled                                 |

| All life cycles          | Blocking failure  | SAU and MPU<br>settings kept                       | RISAF3 settings to allow only SEC accesses | Disable ICACHE,<br>disable DCACHE if<br>secure boot |

<sup>1.</sup> If required, setunexecutable na payload area.

#### 3.2.2.1 IDAU / SAU / MPU

An external implementation defined attribution unit (IDAU) controlled by hardware determines the security state of a memory region. In combination with the IDAU, the boot ROM code defines eight regions using the internal secure attribution unit (SAU). The SAU is programmable in the secure state. Table 5 shows the boot ROM code configuration settings of the SAU.

Note:

When a region is not defined, it is marked as secure by default. When the SAU and IDAU provide different settings for the security attribute, the most conservative one is selected. Additionally, the SAU region granularity is 32 bytes.

| SAU region | Address range | Security attribute         | Mapping                                                                               |

|------------|---------------|----------------------------|---------------------------------------------------------------------------------------|

| 0          | 0x08010000    | Nonsecure                  | NSEC ROM                                                                              |

| 0          | 0x0801FFFF    | Nonsecure                  | NSEC ROW                                                                              |

| 1          | 0x18007C00    | Cooura noncoura callable   | NSC ROM                                                                               |

| 1          | 0x18007FFF    | Secure, nonsecure-callable | NSC ROW                                                                               |

| 2          | 0x20000000    | Nonsecure                  | DTCM, SRAM1, SRAM2 until                                                              |

| 2          | 0x24101FFF    | Nonsecure                  | secure boot ROM data                                                                  |

| _          | 0x24104000    |                            | SRAM2 nonsecure boot ROM data, reserved area, download buffer, SRAM3, and other SRAMs |

| 3          | 0x2FFFFFF     | Nonsecure                  |                                                                                       |

| 4          | 0x30000000    | Cooura noncoura callable   | DTCM, SRAM1                                                                           |

| 4          | 0x340FFFF     | Secure, nonsecure-callable |                                                                                       |

| 5          | 0x34106000    | Secure, nonsecure-callable | SRAM2 reserved area, download                                                         |

| 3          | 0x3FFFFFF     | Secure, nonsecure-canable  | buffer, and other SRAMS                                                               |

| 6          | 0x4000000     | Nonsecure                  | Nancoura aligning paripharala                                                         |

| 0          | 0x4FFFFFF     | Nonsecure                  | Nonsecure aliasing peripherals                                                        |

| 7          | 0x60000000    | Noncoura                   | Nonsecure external devices and                                                        |

|            | 0xFFFFFFF     | Nonsecure                  | core peripherals                                                                      |

Table 5. SAU Region Address Mapping and Security Attributes

The boot ROM code also sets the MPU\_S (from secure) to segment memory regions in AXI SRAM2, primarily to restrict execution rights in selected regions. Through MPU settings, execution is allowed only in the region containing the authenticated binary, thereby excluding the nonauthenticated payload. See details on the nonauthenticated payload in Section 4.2.

This implies that the FSBL code must be aligned on 32-byte addresses (start and end addresses).

UM3234 - Rev 3 page 7/50

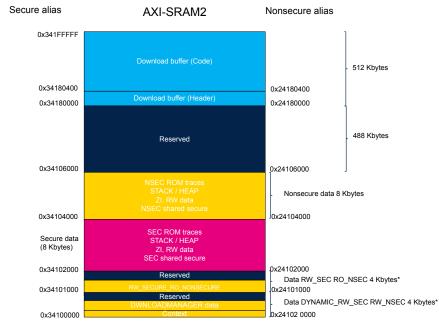

#### 3.2.2.2 RISAF handling

The boot ROM code handles all its data in AXI SRAM2 internal RAM. The AXI SRAM2 layout is detailed in Section 3.9.2. To protect and isolate its data, the boot ROM code configures the RISAF3 hardware functional block, dedicated to RISAF for AXI SRAM2 internal memory. The boot ROM code configures seven regions inside RISAF3, as described in Figure 4, and dynamically sets each region depending on the boot ROM code phase being executed.

Absolute address AXI-SRAM2 0x\*41FFFFF 512 KBytes AREA4 Shared area Sec/Nsec + dynamic Init, download phase, authentication phase 0x\*4180240 0x\*4180000 Not applicable Reserved 488 Kbytes 0x\*4106000 8 Kbytes AREA3 Non Shared Sec/Nsec + Static area : access by Nsec only: (Nonsecure data) 0x\*4104000 SEC ROM traces 8 Kbytes Already covered By SAU protection 0x\*4102000 4 Kbytes\*\* AREA2 Shared Data Sec/Nsec + static (Bootcore config and status) 0x\*4101000 4 Kbytes\*\* AREA1 Shared Data Sec/Nsec + dynamic change at authentication switch Nsec→Sec 0x\*4100000

Figure 4. RISAF3 region configuration

#### \*\*: size required by RISAF3 AXI SRAM2 granularity (of 4 Kbytes)

#### 3.2.2.3 Cache handling

The boot ROM code enables the instruction cache in a secure state in the early stage of the boot flow. In addition, the boot ROM code enables data cache during secure boot execution to speed up data access during authentication and decryption processing. At the end of secure boot execution, the boot ROM code cleans and invalidates the data cache.

Before jumping to the payload code, the boot ROM code configures the caches as described in Table 4.

#### 3.2.3 Reset condition determination

The boot ROM code evaluates which reset source has caused the system to restart. The source of a reset is determined by reading the RCC\_HWRSR register. Then, it requests the clearing of this register to avoid accumulating reset reasons. Next, it evaluates the setting of relevant bits.

The following reset sources are applicable for and distinguished by the boot ROM code:

- PIN: Pin reset of STM32N6xx MCU triggered by NRST pin (external reset)

- POR: Power-on reset (cold) of STM32N6xx MCU triggered by power-on/off reset block

- **BOR**: Brownout reset of STM32N6xx triggered by brownout reset block

- **SFT**: Software reset of STM32N6xx triggered by the Arm<sup>®</sup> Cortex<sup>®</sup>-M55

- WWDG: Windows watchdog reset of STM32N6xx triggered by internal window watchdog timer

- IWDG: Independent watchdog reset of STM32N6xx triggered by internal independent watchdog timer

- LPWRILL: Low-power mode security reset of STM32N6xx triggered by internal power signal

UM3234 - Rev 3 page 8/50

<sup>: 2</sup> for non secure alias and 3 for secure alias: NOTE: RISAF3 address is an offset from start of AXI-SRAM2 and is not impacted by alias part

According to the bit settings, reset types are defined as follows:

Table 6. Reset source analysis and reset type selection

| PIN RST | POR RST | BOR RST | SFT RST | WWDG RST | IWDG RST | LPWRILL RST | Reset type   |

|---------|---------|---------|---------|----------|----------|-------------|--------------|

| 1       | 0       | 0       | 0       | 0        | 0        | 0           | System reset |

| 0       | 1       | 0       | 0       | 0        | 0        | 0           | System reset |

| 0       | 0       | 1       | 0       | 0        | 0        | 0           | System reset |

| 0       | 0       | 0       | 1       | 0        | 0        | 0           | System reset |

| 0       | 0       | 0       | 0       | 1        | 0        | 0           | System reset |

| 0       | 0       | 0       | 0       | 0        | 1        | 0           | System reset |

| 0       | 0       | 0       | 0       | 0        | 0        | 1           | System reset |

#### 3.2.4 Watchdog timer handling

The boot ROM code reloads the independent watchdog (IWDG) if a fuse enables the IWDG. Blowing a fuse (OTP WORD124.bit0) starts the IWDG on reset.

#### 3.2.5 Tamper determination

The reference manual [1] details the tampered function and types of tampers. An application can define two types of tampers:

- Potential tamper: This tamper blocks some strategic resources (crypto blocks and some memories) but

does not erase them immediately.

- Confirmed tamper: This tamper automatically erases secrets and keeps crypto blocks in reset.

In the case of a potential tamper, the boot ROM code activates protection against the tamper effect, that is, unblocking crypto blocks at the beginning of its execution. This allows the loading and execution of the FSBL. Before jumping to the FSBL or in a blocking failure scenario, the boot ROM code deactivates the protection. The application decides to filter the potential tamper and eventually confirm it. In the case of a confirmed tamper, the boot ROM code ends in an infinite loop.

Additionally, the boot ROM code handles an added tamper mechanism called boot tamper. In this case, the tampers are configured through fuses and are applicable during the boot process. The following OTPs support this feature:

- OTP\_WORD29.1: Enables the configuration of tampers in boot ROM.

- OTP\_WORD56.[0..7]: Enables external tamper from 1 to 8 (TAMP1 to TAMP8).

- OTP\_WORD56.[8..18]: Enables internal tamper from 1 to 11 (ITAMP1 to ITAMP11, excluding ITAMP10).

- OTP\_WORD57.[0..7]: Configures TAMP1 to TAMP8 as either confirmed or potential tamper.

- OTP\_WORD57.[8..18]: Configures ITAMP1 to ITAMP11 (excluding ITAMP10) as either confirmed or potential tamper.

- OTP\_WORD58.[0..7]: Configures the mode level (0: low, 1: high) of each external tamper from TAMP1 to TAMP8.

For more information, see Section 3.11.1 that details the OTP list used by the boot ROM code.

#### 3.2.6 Life cycle level determination

The boot ROM code determines the applied life cycle level at an early stage of the boot flow. It is based on fuses and is detailed in Table 7.

Table 7. Life cycle fuse configuration

| STM32N6 life cycle State | Fuse configuration                                                                                                         |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------|

| CLOSED_LOCKED_UNPROVD    | CLOSED_UNLOCKED fuse configuration + OTP_WORD124.20 = 1 (DFT_disable bit) + OTP_WORD18 = 0xF (secure_boot)                 |

| CLOSED_LOCKED_PROVD      | CLOSED_UNLOCKED fuse configuration + OTP_WORD124.20 = 1 (DFT_disable bit) + OTP_WORD18 = 0x1EF (secure_boot and prov_done) |

UM3234 - Rev 3 page 9/50

HyperFlash<sup>™</sup> device, connected to XSPIM\_P2

#### 3.2.7 Boot ROM configuration determination

The boot ROM code evaluates the selected boot configuration. The boot configuration defines which type of external boot memory device or serial boot is selected, or if dev boot is applicable. The boot configuration is either specified using external pins or by fuses.

The following categories of external boot memory devices are supported:

- sNOR x4 and x8 flash devices

- HyperFlash<sup>™</sup> flash device

- SD memory card device (SD specifications V6.0)

- eMMC type of embedded memory card devices (eMMC specifications V5.1)

Applied boot memory **Boot Config. Attached boot Description** setup Dev boot mode selected in CLOSED-0 Dev boot UNLOCKED life cycle Serial boot monitors in parallel USB and Serial boot 1 **USART links** 2 SD device SD1 SD device, connected to SDMMC1 3 SD device SD2 SD device, connected to SDMMC2 4 eMMC device eMMC1 eMMC device, connected to SDMMC1 5 eMMC device eMMC2 eMMC device, connected to SDMMC2 sNOR device XSPI NOR sNOR device, connected to XSPIM\_P2 6

Table 8. Supported boot configurations

The boot ROM code evaluates the register bits BOOTSR[0:1] to determine the applied boot configuration. The register bits BOOTSR[0:1] reflect the level of the external boot pins as latched at reset.

XSPI HYPER

#### Allocated pins for BOOTSR[0:1]:

7

- BOOTSR[0]: Boot0 pin (dedicated pin)

- **BOOTSR[1]**: Boot1 pin (nondedicated pin, PA6)

HyperFlash™

Note:

The selected Boot1 pin, PA6, can be overwritten by fuses, BOOTROM\_CONFIG\_10[24:21] (port ID) and BOOTROM\_CONFIG\_10[28:25] (pin ID). The Boot1 pin check has priority over the Boot0 pin check. If the Boot1 pin is not set, the Boot0 pin is checked. If the Boot1 pin is selected but not allowed in the current life cycle, the Boot0 pin is then checked.

The flash boot configuration is checked using fuses in BOOTROM\_CONFIG\_2[8:5], OTP\_WORD11. The boot configuration coding rules are defined in Table 9.

Table 9. Boot configuration coding

| BOOTSR[1:0] | BOOTROM_CONFIG_2[8:5] | Applied boot configuration             |

|-------------|-----------------------|----------------------------------------|

| 0           | 1                     | Boot config. 2                         |

| 0           | 2                     | Boot config. 4                         |

| 0           | 3                     | Boot config. 6                         |

| 0           | 5                     | Boot config. 7                         |

| 0           | 7                     | Boot config. 3                         |

| 0           | 8                     | Boot config. 5                         |

| 0           | 0                     | Boot config. 6 (default configuration) |

| 1           | X                     | Boot config. 1                         |

| 2           | X                     | Boot config. 0                         |

UM3234 - Rev 3 page 10/50

| BOOTSR[1:0] | BOOTROM_CONFIG_2[8:5] | Applied boot configuration |

|-------------|-----------------------|----------------------------|

| 3           | X                     | Boot config. 0             |

The boot ROM code must configure STM32N6 on-chip hardware blocks to enable access to external boot memory or serial links. Table 10 specifies the required on-chip hardware blocks for the supported external boot memory or serial link categories.

Table 10. Hardware blocks required per boot category

| Boot category                | Required hardware blocks        |

|------------------------------|---------------------------------|

| Serial boot                  | USB OTG1, USART1, USART2, UART4 |

| SD1                          | SDMMC1                          |

| eMMC1                        | SDMMC1                          |

| SD2                          | SDMMC2                          |

| eMMC2                        | SDMMC2                          |

| XSPI NOR                     | XSPIM_P2, XSPI1                 |

| XSPI HyperFlash <sup>™</sup> | XSPIM_P2, XSPI1                 |

#### 3.2.8 Usage of hardware timers

The boot ROM code supports timeout and timestamp functions. To enable these features, the boot ROM code configures the TIMER2 hardware block function. The timer module base is set to 1 MHz using the hardware timer prescaler.

#### 3.3 Execution of special boot branches

#### 3.3.1 Dev boot execution

The dev boot mode is executed only in the CLOSED\_UNLOCKED life cycle.

In this scenario, the boot ROM code protects its assets, reopens the debug secure and nonsecure, and then goes into an endless loop. The dev boot mode is selected using the Boot1 pin.

#### 3.3.2 Blocking failure execution

The blocking failure scenario occurs during boot ROM code execution if an error happens (for example, exception, invalid scenario, invalid parameters). In this scenario, the boot ROM code:

- Clears and locks sensitive data

- Clears the download area

- Locks the debug

- Switches all GPIO to secure

- Sends UART status traces using the PG10 BootFailed pin (status values are described in Section 3.11.2)

- Sets the PG10 LED on

As described below, the PG10 (AF11) is used as the BootFailed pin. This pin is multiplexed to UART5\_TX to send UART status traces.

#### 3.4 Boot ROM memory device setup

#### 3.4.1 SDMMC hardware block configuration for SD device

To access an SD card device as a boot memory device attached to the STM32N6 MCU, the boot ROM code configures the SDMMC1 or SDMMC2 hardware blocks. Both SDMMC controller instances have the same configuration settings.

UM3234 - Rev 3 page 11/50

The selection of the SD card device as a boot memory device is done by the applied boot configuration. The SDMMC host controller hardware block is configured for data transfer from the SD card device according to Table 11 before starting the actual boot operation. The SD boot operation implemented in the boot ROM code is described in the following sections. Registers and register fields not explicitly mentioned are not relevant for SD boot operation and can retain their default settings.

Register Register field Applied configuration setting 0x0: Rising edge, SDMMC\_CK dephasing for data and **NEGEDGE** command Default 1-bit wide bus mode: SDMMC D0 used (does not **WIDBUS** support DDR) **PWRSAV** 0x0: SDMMC\_CK clock is always enabled HWFC\_EN 0x0: Hardware flow control is disabled **BUSSPEED** 0x0: DS, HS speed mode selected SDMMC CLKCR 0x84 for SD card identification mode 0x2 for SD card transfer mode: Clock divide factor = sdmmc\_ker\_ck / (2\*SDMMC\_CK) with **CLKDIV** sdmmc\_ker\_ck = 64 MHz sdmmc ck = 177 kHz for SD card identification or = 16 MHz for SD card transfer mode 0x1: Voltage transceiver I/Os driven as output when the **DIRPOL** direction signal is high SDMMC POWER

Table 11. SDMMC settings for SD card identification mode

In addition to configuring the actual SDMMC hardware block, the boot ROM code also carries out the I/O settings, the power domain settings, and the clock settings dedicated to the SDMMC hardware clock.

0x3: Power on, the card is clocked

#### 3.4.2 Configuration settings of SD device

The SD card is addressed by sector. The boot ROM code is forcing the sector size to 512 bytes.

#### 3.4.3 SDMMC hardware block configuration for eMMC device

**PWRCTRL**

To access an eMMC device as a boot memory device attached to the STM32N6 MCU, the boot ROM code configures the SDMMC1 or SDMMC2 hardware blocks. Both SDMMC controller instances have the same configuration settings.

The selection of the eMMC device as a boot memory device is done by the applied boot configuration described in Section 3.2.7: Boot ROM configuration determination. The SDMMC host controller hardware block is configured for data transfer from the eMMC device according to Table 12 before starting the actual boot operation. The SD boot operation implemented in the boot ROM code is described in Section 3.5.1: Access image on SD card device. Registers and register fields not explicitly mentioned are not relevant for SD boot operation and can retain their default settings.

UM3234 - Rev 3 page 12/50

Table 12. SDMMC settings for eMMC boot mode

| Register    | Register field | Applied configuration setting                                                                                               |

|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|

|             | NEGEDGE        | 0x0: Rising edge, SDMMC_CK dephasing for data and command                                                                   |

|             | WIDBUS         | Default 1-bit wide bus mode: SDMMC_D0 used (does not support DDR)                                                           |

|             | PWRSAV         | 0x0: SDMMC_CK clock is always enabled                                                                                       |

|             | HWFC_EN        | 0x0: Hardware flow control is disabled                                                                                      |

| SDMMC_CLKCR | BUSSPEED       | 0x0: DS, HS speed mode selected                                                                                             |

|             | CLKDIV         | 0x2  Clock divide factor = sdmmc_ker_ck / (2*SDMMC_CK) with  sdmmc_ker_ck = 64 MHz sdmmc_ck = 16 MHz for eMMC transfer mode |

| CDMMC DOWED | DIRPOL         | 0x0: Voltage transceiver I/Os driven as output when the direction signal is low                                             |

| SDMMC_POWER | PWRCTRL        | 0x3: Power on, the eMMC is clocked                                                                                          |

In addition to configuring the actual SDMMC hardware block, the boot ROM code also carries out the I/O settings (see Section 3.12.3), the power domain settings (see Section 3.12.2), and the clock settings dedicated to the SDMMC hardware clock (see Section 3.12.1).

#### 3.4.4 Configuration settings of eMMC device

For the implemented eMMC boot mode, the boot-related configuration settings on an eMMC device, as shown in Table 13, are expected to be in place.

Table 13. Required boot settings on eMMC device

| eMMC register | Register field        | Applied configuration setting                                |

|---------------|-----------------------|--------------------------------------------------------------|

| EXT_CSD[179]  | BOOT_PARTITION_ENABLE | Boot partition 1 enabled for boot                            |

| EXT_CSD       | BOOT_BUS_WIDTH        | EMMC1: x1 bus width in boot operation mode (default setting) |

#### 3.4.5 XSPI / XSPIM configuration for serial NOR device

To access a serial NOR device as a boot memory device attached to the STM32N6 MCU, the boot ROM code configures the XSPI1 controller and the XSPIM controller to use the XSPIM\_P2 dedicated port for the Flash device.

The selection of the serial NOR device as a boot memory device is done by the applied boot configuration. The XSPI1 controller hardware block is configured for data transfer from the NOR device according to Table 14 before starting the actual boot operation. The serial NOR boot operation implemented in the boot ROM code is described in the Section 3.4.6. Registers and register fields not explicitly mentioned are not relevant for serial NOR boot operation and can retain their default settings.

Table 14. XSPI1/XSPIM settings for sNOR device

| Register   | Register field | Applied configuration setting                                             |

|------------|----------------|---------------------------------------------------------------------------|

| XSPI1_DCR2 | Prescaler      | 0x1: fclock = fkernel_clock / 2                                           |

| XSPI1 DCR1 | CSHT           | 0x0: NCS stays high for at least 1 cycle between external device commands |

| ASPII_DCRI | DEVSIZE        | 0x1F: set to maximum size of external device 4 GB                         |

|            | IMODE          | 0x1: instruction on a single line                                         |

| XSPI1 CCR  | ADMODE         | 0x1: address on a single line                                             |

| ASPII_CCK  | ADSIZE         | 0x2: 24-bit address                                                       |

|            | DMODE          | 0x1: data on a single line                                                |

UM3234 - Rev 3 page 13/50

| Register  | Register field | Applied configuration setting                                           |

|-----------|----------------|-------------------------------------------------------------------------|

| XSPI1_TCR | DCYC           | 0x8: 8 CLK cycles of dummy phase                                        |

| XSPI1_IR  | INSTRUCTION    | 0xB: NOR instruction. Instruction to be sent to the external SPI device |

| XSPI1_DLR | DL             | Number of data to be retrieved in indirect mode                         |

| XSPI1_CR  | FMODE          | 0x1: Indirect-read mode                                                 |

| XSPI1_AR  | ADDRESS        | Address to be sent to the external device                               |

| XSPI1_DR  | DATA           | 32-bit word: Data to be received from the external SPI device           |

| XSPI1_FCR | CTCF           | Clear transfer complete (TCF) flag in XSPI1_SR register                 |

| VCDIM CD  | MUXEN          | 0x0: No multiplexing                                                    |

| XSPIM_CR  | MODE           | 0x1: if MUXEN = 0, swapped mode => XSPI1 connected to XSPIM_P2          |

In addition to configuring the actual XSPI1 / XSPIM hardware blocks, the boot ROM code also carries out the I/O settings, the power domain settings, and the clock settings dedicated to the XSPI1 / XSPIM hardware clocks.

#### 3.4.6 Configuration settings of serial NOR device

There are no specific boot ROM settings to apply to the serial NOR device.

# 3.4.7 XSPI / XSPIM configuration for HyperFlash<sup>™</sup> device

To access a HyperFlash<sup>™</sup> device as a boot memory device attached to the STM32N6 MCU, the boot ROM code configures the XSPI1 controller and the XSPIM controller to use the XSPIM\_P2 dedicated port for the flash device.

The selection of the HyperFlash<sup>™</sup> device as a boot memory device is done by the applied boot configuration. The XSPI1 controller hardware block is configured for data transfer from the HyperFlash<sup>™</sup> device according to Table 13 before starting the actual boot operation. The HyperFlash<sup>™</sup> boot operation implemented in the boot ROM code is described the following sections. Registers and register fields not explicitly mentioned are not relevant for HyperFlash<sup>™</sup> boot operation and can retain their default settings.

Table 15. XSPI1/XSPIM settings for HyperFlash<sup>™</sup> device

| Register                                   | Register field | Applied configuration setting                                                 |  |

|--------------------------------------------|----------------|-------------------------------------------------------------------------------|--|

| XSPI1_DCR2                                 | Prescaler      | 0x1: fclock = fkernel_clock / 2                                               |  |

|                                            | CSHT           | 0x7: NCS stays high for at least 8 cycles between external device commands    |  |

| XSPI1_DCR1                                 | DEVSIZE        | 0x1F: set to maximum size of external device 4 GB                             |  |

|                                            | MTYP           | 0x4: Hyper-Bus memory mode                                                    |  |

| Venia III.ch                               | TACC           | 0x10: Access time, 16 clock cycles                                            |  |

| XSPI1_HLCR                                 | TRWR           | 0x10: Read write recovery time, 16 clock cycles                               |  |

|                                            | DQSE           | 0x1: DQS enabled                                                              |  |

|                                            | ADMODE         | 0x4: Address on eight lines                                                   |  |

| XSPI1 CCR                                  | ADSIZE         | 0x3: 32-bit address                                                           |  |

| ASPII_CCR                                  | DMODE          | 0x4: Data on eight lines                                                      |  |

|                                            | DDTR           | 0x1: Data double transfer rate (DTR) enabled for data phase                   |  |

|                                            | ADDTR          | 0x1: Data double transfer rate (DTR) enabled for address phase                |  |

| XSPI1_TCR                                  | DHQC           | 0x1: 1/4 cycle hold                                                           |  |

| XSPI1_IR INSTRUCTION 0x0: Hyper-bus instru |                | 0x0: Hyper-bus instruction. Instruction to be sent to the external SPI device |  |

| XSPI1_DLR                                  | DL             | Number of data to be retrieved in indirect mode                               |  |

| XSPI1_CR FMODE 0x1: Indirect-rea           |                | 0x1: Indirect-read mode                                                       |  |

UM3234 - Rev 3 page 14/50

| Register  | Register field | Applied configuration setting                                  |  |  |

|-----------|----------------|----------------------------------------------------------------|--|--|

| XSPI1_AR  | ADDRESS        | Address to be sent to the external device                      |  |  |

| XSPI1_DR  | DATA           | 32-bit word: data to be received from the external SPI device  |  |  |

| XSPI1_FCR | CTCF           | Clear transfer complete (TCF) flag in the XSPI1_SR register    |  |  |

| VCDIM CD  | MUXEN          | 0x0: No multiplexing                                           |  |  |

| XSPIM_CR  | MODE           | 0x1: If MUXEN = 0, swapped mode => XSPI1 connected to XSPIM_P2 |  |  |

In addition to configuring the actual XSPI1 / XSPIM hardware blocks, the boot ROM code also carries out the I/O settings, the power domain settings, and the clock settings dedicated to the XSPI1 / XSPIM hardware clocks.

#### 3.4.8 Configuration settings of HyperFlash<sup>™</sup> device

There are no specific boot ROM settings to apply to the HyperFlash<sup>™</sup> device.

# 3.5 Access image on boot memory device

#### 3.5.1 Access image on SD card device

The boot ROM code accesses a next-stage boot image, FSBL, on an SD card device. Before accessing the SD card, the SDMMC hardware block must be configured.

The SD card does not support the boot operation mode as defined for eMMC devices. Therefore, it is always accessed through the card identification mode and then the data transfer mode based on the protocol defined in the standard specification (see reference SD\_SPEC [2]).

#### Card identification mode

During card identification mode, several commands are sent to follow the standard specification (CMD0, CMD8, ACMD41, CMD55, CMD2, CMD3). The ACMD41 command identifies cards that do not match the power supply range supported by the SDMMC hardware block. The boot ROM code repeatedly issues ACMD41 until a response is provided, allowing the SD card to switch to the Ready state. The boot ROM code then completes the card identification mode by obtaining the new relative card address, switching the SDMMC hardware block to data transfer mode, and placing the SD card device in Standby state.

#### Data transfer mode

In data transfer mode, the boot ROM code searches for FSBLs. It searches for two FSBL images. First, it looks for the GPT magic number in the header. The GPT header is stored in LBA1 (logical block address #1 = 512 bytes). The boot ROM code then checks the GPT table to find FSBL offset addresses in LBA block offset. If GPT is not found, the boot ROM code uses default offsets set to 128@LBA and 640@LBA for FSBL1 and FSBL2, respectively.

The boot ROM code first downloads FSBL1 into the download buffer located in internal RAM, starting at the address DOWNLOAD\_BUFFER\_BASE\_ADDR defined in Table 18, by reading multiple data blocks of 512-byte size using the SDMMC internal DMA. The image is then accessed from the download buffer for further processing by the boot ROM code. Once the complete SD boot image has been loaded into the download buffer, the boot ROM code executes it from there, after performing applicable image analysis and validation tasks.

If there is an issue during FSBL1 processing, the boot ROM code attempts to load FSBL2 into the download buffer and follows the same flow.

# 3.5.2 Access image on eMMC device boot partition

The boot ROM code accesses a next-stage boot image, FSBL, on an eMMC device. Before accessing the eMMC device, the SDMMC hardware block must be configured, and the eMMC card device must be programmed.

The boot operation, as defined for eMMC version 4.51 (see reference JEDEC-EMMC), is applied by the boot ROM code for reading an image from an attached eMMC device. For this boot operation, no commands are sent to the eMMC device. The transfer of boot partition data is initiated by holding the CMD line low for a specified minimum number of clock cycles after power-up or reset of the eMMC device and before any command is sent to the eMMC device.

The boot partition is a multiple of 128 Kbytes and is defined in the EXT\_CSD register on the eMMC device. Once the FSBL is copied from the eMMC card to the internal RAM download buffer using internal DMA, the boot ROM code ends the boot mode and puts the eMMC device in a state to receive new commands.

UM3234 - Rev 3 page 15/50

#### 3.5.3 Access image on serial NOR device

The boot ROM code accesses a next-stage boot image, FSBL, on a serial NOR device. Before accessing the serial NOR device, the XSPI/XSPIM hardware blocks must be configured.

The boot ROM code searches for FSBL1 and FSBL2 in the serial NOR device at offsets 0x0 and 0x40000, respectively. If the boot ROM code detects FSBL1 first, it loads it into the download buffer area at DOWNLOAD\_BUFFER\_BASE\_ADDR, as defined in Table 18, and then executes the secure boot processing. If the secure boot processing fails with FSBL1, the boot ROM code clears the download buffer, and then downloads the FSBL2 image into the download buffer area. The boot ROM code updates the context structure accordingly for the fields: bootPartitionUsedToBoot, bootInterfaceInstance, and bootInterfaceSelected.

The boot ROM code context structure is described in the following sections. If the secure boot processing fails with FSBL2, the download buffer is cleared, and a serial boot is executed.

# 3.5.4 Access image on HyperFlash<sup>™</sup> device

The boot ROM code is accessing a next-stage boot image, FSBL, on a HyperFlash<sup>™</sup> device. Before accessing the HyperFlash<sup>™</sup> device, it is required that the XSPI / XSPIM hardware blocks are configured.

The same boot ROM code processing than serial NOR device is applied to the HyperFlash<sup>™</sup> device as described in the following sections.

## 3.6 Peripheral boot interfaces

#### 3.6.1 Peripheral boot interfaces activation

The boot ROM code activates and configures the interfaces used for DFU boot (download via external link) based on the current boot scenario. This activation of peripheral boot interfaces occurs at an early stage of the normal boot flow. The actual usage of these interfaces - starting with the serial peripheral boot link establishment procedure - happens in two possible stages: either selected by boot pins or after local boot (flash boot) fails, as described in Figure 2.

The following serial interfaces are supported as serial peripheral boot interfaces:

- Three USART interfaces: USART1, USART2, and UART4

- USB 2.0 OTG\_HS 1 instance

Dedicated fuses can disable the usage of each individual serial interface for serial peripheral boot. OTP BOOTROM\_CONFIG\_11[16:9] disables a serial boot source (USART or USB). OTP BOOTROM\_CONFIG\_11[22:20] disables each USART instance.

Note:

If OTP disables both USART and USB boot sources, the system forces UARTs to enable. Similarly, if OTP disables all USART instances, the system forces all USART instances to enable.

#### 3.6.2 Peripheral boot link establishment

The boot ROM code can establish a serial peripheral boot channel on one of the serial boots interfaces activated for the current boot event. Therefore, the boot ROM code polls all activated serial boot interfaces for a certain period. A serial boot channel is established when the link establishment succeeds on a serial boot interface. For USB-based interfaces, the USB enumeration must be completed before entering the serial link establishment phase.

#### 3.6.3 USART configuration

USART1, USART2, and UART4 share the same configuration:

- GPIO mode: Push-pull high speed with pull-up. Both Rx pins are configured as alternate functions.

- Baud rate: Configured by the host. If CubeProgrammer is used as the host, the baud rate is set to 115 200.

- Data width: Nine bits

- Stop bits: One stop bit

- Parity bit: Even

- Hardware flow control: None

- Transfer direction: TX\_RX with 16-oversampling configured

Details on kernel and bus clocks are provided in the following sections.

UM3234 - Rev 3 page 16/50

Note:

If USB is connected, USART is not available during this boot. To use USART boot, disconnect USB and apply a reset.

#### 3.6.4 USB DFU device configuration

The USB DFU device configuration is split into multiple parts:

- USBD\_DFU\_SRAM\_InitVars: The boot ROM code initializes packet descriptors, the SRAM write status, and file operations-related functions.

- USBD\_Desc\_InitVars: The boot ROM code initializes USB descriptors such as device, LangID, and serial

descriptors.

- USBD\_DFU\_InitVars: The boot ROM code initializes USB DFU variables.

- DFU\_Desc\_InitVars: The boot ROM code initializes DFU descriptors such as device, LangID, manufacturer, product, configurations, serial, and interface descriptors.

- USBD\_Init: The boot ROM code initializes the device stack, assigns USBD descriptors, and loads the

class driver. Specifically, in the low-level portion of the device driver, the boot ROM code sets the LL driver

parameters as follows:

- Instance: USB1\_OTG\_HS

- Speed: USB\_OTG\_SPEED\_HIGH

- Number of endpoints: 8

- PHY interface: USB OTG HS EMBEDDED PHY

- Low power: Disabled

- Link power management: Disabled

- Vbus sensing: DisabledBattery charging: Disabled

- SOF: Disabled

- RxFifo and TxFifo sizes: 0x80

#### 3.6.4.1 HSE bypassing

HSE bypass is explained in the RCC section of the reference manual [1].

When the boot ROM code finishes retrieving the type of HSE clock and finds it different from the HSE oscillator mode, it enters the HSE programming sequence. The boot ROM code executes these steps in a specific order:

- 1. Disable HSE

- 2. Get HSERDY flag

- Set the HSE bypass

- 4. Select the external clock type

- 5. Start HSE

#### 3.6.4.2 HSE autodetection

HSE crystal autodetection is explained in the RCC section of the reference manual (RM0486).

The boot ROM code can detect the mode in which the HSE should be used: either analog/digital bypass or oscillator mode. By reading two signal levels (GPIO PH1 inputs), the boot ROM code can detect four scenarios. If the HSE bypass detection disable bit is 0, then the detection bypass is enabled, and three scenarios are possible:

- HSE digital external clock mode: If level1 is low and level2 is low, HSE digital bypass is detected.

- HSE analog external clock mode: If level1 is high and level2 is high, HSE analog bypass is detected.

- HSE oscillator mode: If neither of the previous two modes is detected, no HSE bypass is detected.

If the HSE bypass detection is disabled, the oscillator mode is used.

The boot ROM code sets the USB clock tree after enabling HSE bypass.

#### 3.7 Boot protocol on peripheral interface

#### 3.7.1 Boot protocol overview

The USART and USB serial peripherals protocols are based on the STM32CubeProgrammer tool protocol described in the AN5275 application note.

UM3234 - Rev 3 page 17/50

Note that the above application note is specific to STM32MP1. The STM32N6 specifics and differences are described in the subsequent subchapters starting from Section 3.7.2.

Note: For boot ROM flow, only the protocol details for phase ID: 0x01 (FSBL image) are relevant.

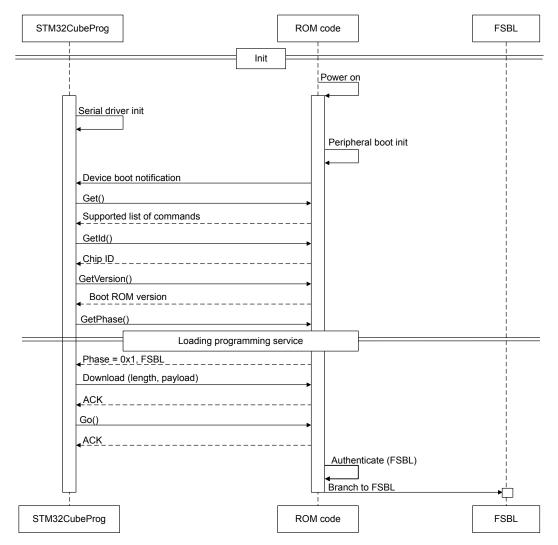

#### 3.7.2 USART FSBL download sequence

The USART boot sequence involves the following steps:

- 1. Initialization (Init): The process begins with the initialization of the programming sequence.

- 2. Loading programming service: The programming service is loaded.

The sequence diagram illustrates the interaction between the following components:

- STM32CubeProg: The programming tool used for the USART boot sequence.

- ROM code: The read-only memory code that interacts with the programming tool.

- FSBL: The first stage bootloader, which is involved in the later stages of the process.

Figure 5. USART boot sequence

#### 3.7.3 USART protocol

The supported commands for the STM32N6 USART protocol are listed in the table below:

UM3234 - Rev 3 page 18/50

17500014

Table 16. USART commands

| Command                 | Code                                                             | Description                                                 |

|-------------------------|------------------------------------------------------------------|-------------------------------------------------------------|

| Get                     | 0x00                                                             | Get a list of available USART commands.                     |

| Get version             | 0x01 Get the version (0x31).                                     |                                                             |

| Get ID                  | 0x02                                                             | Get the device ID (0x0486).                                 |

| Get phase               | 0x03                                                             | Get phase ID (0x01 load FSBL).                              |

| Read partition          | Read partition 0x12 Read data from partition (0xF3): Certificate |                                                             |

| Start (Go)              | 0x21                                                             | Follow the boot ROM flow execution on the downloaded image. |

| Download (Write memory) | 0x31                                                             | Download the image to the download buffer                   |

#### 3.7.4 USB serial protocol

The Boot ROM USB protocol is based on the DFU 1.1 protocol. The key difference is:

• **DFU\_DETACH** is acceptable in the dfuIDLE state (before the execution of FSBL in internal RAM). When this occurs, the USB connection is disconnected, and a new USB enumeration is performed using the FSBL USB stack.

#### 3.7.5 USB DFU STM32N6 enumeration

The USB parameters for the DFU STM32N6 enumeration are listed in the table below:

Table 17. USB DFU STM32N6 enumeration parameters

| Parameter                                                       | Values                                            |  |  |

|-----------------------------------------------------------------|---------------------------------------------------|--|--|

| idVendor                                                        | 0x0483                                            |  |  |

| idProduct 0xDF11                                                |                                                   |  |  |

| iSerial                                                         | String with unique device ID                      |  |  |

| iProduct (HS)                                                   | "DFU in HS mode @Device ID /0x, @Revision ID /0x" |  |  |

| iProduct (FS) "DFU in FS mode @Device ID /0x, @Revision ID /0x" |                                                   |  |  |

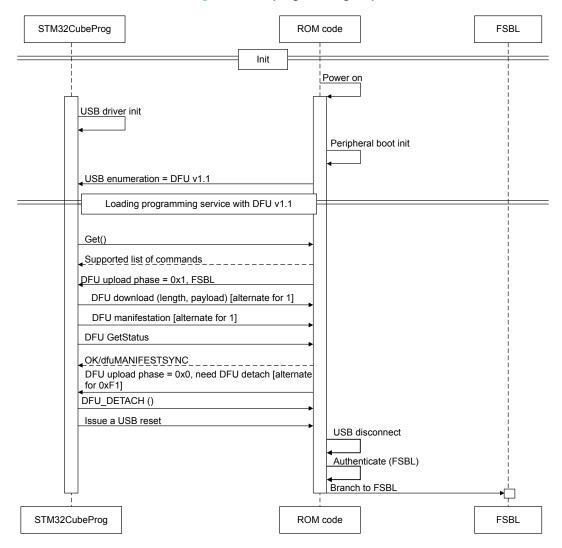

#### 3.7.6 USB programming sequence

The USB programming sequence involves the following steps:

- 1. Initialization (Init): The process begins with the initialization of the programming sequence.

- Loading programming Service with DFU v1.1: The programming service is loaded using the DFU v1.1 protocol.

The sequence diagram illustrates the interaction between the following components:

- **STM32CubeProg**: The programming tool used for the USB programming sequence.

- ROM code: The read-only memory code that interacts with the programming tool.

- FSBL: The first stage bootloader, which is involved in the later stages of the process.

The arrows in the diagram indicate the flow of commands and responses between these components during the programming sequence.

UM3234 - Rev 3 page 19/50

Figure 6. USB programming sequence

#### 3.8 Boot ROM version definition

The boot ROM code version structure information is contained within the boot ROM code function itself as a structure located at the starting address BOOTROMCODE\_VERS\_ADDR, as defined in Table 18. This structure is split into subelements according to the layout specified in Figure 7, with the contents defined in Table 17.

Table 18. Defined boot ROM code version structure elements

| Element          | Value      | Description                          |

|------------------|------------|--------------------------------------|

| ChipVersion      | 0x00008604 | Chip version: 0x486 for STM32N6      |

| CutVersion       | 0x00000200 | Cut version: Cut 2.0                 |

| RommaskVersion   | 0x0000001  | ROM mask version: 1                  |

| Bootrom_version  | 0x00000501 | Boot ROM delivery release: DV5.1     |

| forChipDesignRTL | 0x001F0202 | Chip design RTL version: ASSY 31.2.2 |

| Platform_version | -          | Platform version: not relevant       |

UM3234 - Rev 3 page 20/50

T75067V1

Figure 7. Boot ROM code version structure layout

ChipVersion

|       | MSB |   |             | LSB         |

|-------|-----|---|-------------|-------------|

| Bytes | 3   | 2 | 1           | 0           |

|       | 0   | 0 | ChipV_byte1 | ChipV_byte0 |

CutVersion

|       | MSB |   |               | LSB           |

|-------|-----|---|---------------|---------------|

| Bytes | 3   | 2 | 1             | 0             |

|       | 0   | 0 | Major version | Minor version |

RommaskVersion

|       | MSB |   |   | LSB     |

|-------|-----|---|---|---------|

| Bytes | 3   | 2 | 1 | 0       |

|       | 0   | 0 | 0 | version |

Bootrom\_version

|       | MSB |   |               | LSB           |

|-------|-----|---|---------------|---------------|

| Bytes | 3   | 2 | 1             | 0             |

|       | 0   | 0 | Major version | Minor version |

for Chip Design RTL

|       | MSB |               |                | LSB           |

|-------|-----|---------------|----------------|---------------|

| Bytes | 3   | 2             | 1              | 0             |

|       |     | Major version | Medium version | Minor version |

# 3.9 Address definitions and memory layout of internal RAM

# 3.9.1 Definition of fixed memory addresses and base addresses

The fixed memory addresses used in the boot ROM code are listed in Table 19. The term "base address" is typically used for a fixed memory address when it relates to the start address of a memory area.

Table 19. Absolute memory addresses

| Defined item                | Physical address                                                                                                                                                                                               | Description                                                                                                                   |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| DOWNLOAD_BUFFER_BASE_ADDR   | 0xX4108000 Start address of the download buffer in internal AXI SRA memory, used for copying the FSBL image from an exterior interface (Flash boot or serial boot). X = 2 for nonsecure = 3 for secure access. |                                                                                                                               |

| CONTEXT_BASE_ADDR           | 0xX4100000                                                                                                                                                                                                     | Start address of the context information structure. X = 2 for nonsecure access, X = 3 for secure access.                      |

| BOOTROMCODE_VERS_ADDR       | 0x18001000                                                                                                                                                                                                     | Start address of the boot ROM code version information structure.                                                             |

| TRACE_BUFFER_SEC_BASE_ADDR  | 0x341037F0                                                                                                                                                                                                     | Start address of the SEC trace buffer during the current boot ROM execution.                                                  |

| TRACE_BUFFER_NSEC_BASE_ADDR | 0x241077F0                                                                                                                                                                                                     | Start address of the NSEC trace buffer during the current boot ROM execution.                                                 |

| E1CPVK_COPY_BASE_ADDR       | 0x38004000                                                                                                                                                                                                     | Start address of the E1CPvK copy in the AHB SRAM2 internal RAM area, supported for the CLOSED_LOCKED_UNPROVD life cycle only. |

UM3234 - Rev 3 page 21/50

## 3.9.2 Memory layout of internal RAM

The main internal RAM used by the boot ROM code to handle its own data is located in the internal AXI SRAM2 memory. The following figure shows the layout of this internal RAM for the STM32N6 project.

Figure 8. Boot ROM internal RAM memory layout

\* = size due to RISAF AXI SRAM2 granularity (4 Kbytes)

# JT75069V2

# 3.10 Error and trace logging

Errors and traces are managed by the boot ROM code. To indicate errors, the boot ROM code uses a dedicated GPIO to communicate statuses. A LED can be connected to the BOOTFAILN pin. In case of a blocking failure, this LED is switched on and set to low open drain.

During its execution, the boot ROM code writes binary traces to its memory. These traces are stored in the internal AXI-SRAM2 memory at the addresses <code>TRACE\_BUFFER\_SEC\_BASE\_ADDR</code> and <code>TRACE\_BUFFER\_NSEC\_BASE\_ADDR</code> (as defined in Section 3.9) for secure and nonsecure regions, respectively. There is a fuse bitfield to disable traces, <code>OTP\_WORD16.bit0</code>, detailed in Section 3.11.1.

In case of a blocking failure, the boot ROM code writes a UART log error at 9600 baud to the debug GPIO pin PG10 through UART5\_TX. The following table contains the boot ROM code statuses with their respective values. A specific status sets the corresponding bit to 1 on the uint64 t value.

Table 20. Boot ROM code status secure

| Boot ROM code status                               | Bit number |

|----------------------------------------------------|------------|

| BOOTCORE_STATUS_SEC_BOOT_CONFIG_ANALYZED           | 11         |

| BOOTCORE_STATUS_SEC_ARM_EXCEPTION                  | 12         |

| BOOTCORE_STATUS_SEC_CHIPMODE_CLOSED_UNLOCKED       | 20         |

| BOOTCORE_STATUS_SEC_CHIPMODE_CLOSED_LOCKED_UNPROVD | 21         |

| BOOTCORE_STATUS_SEC_CHIPMODE_CLOSED_LOCKED_PROVD   | 22         |

| BOOTCORE_STATUS_SEC_CHIPMODE_INVALID               | 23         |

| BOOTCORE_STATUS_SEC_NO_BOOT                        | 24         |

| BOOTCORE_STATUS_SEC_NO_BOOT_LOOP                   | 25         |

| BOOTCORE_STATUS_SEC_BLOCKING_FAILURE               | 26         |

| BOOTCORE_STATUS_SEC_SECURE_BOOT                    | 32         |

UM3234 - Rev 3 page 22/50

| Boot ROM code status                    | Bit number |

|-----------------------------------------|------------|

| BOOTCORE_STATUS_SEC_DEV_BOOT            | 33         |

| BOOTCORE_STATUS_SEC_PLL1_LOCKED         | 39         |

| BOOTCORE_STATUS_SEC_SIGNATURE_OK        | 43         |

| BOOTCORE_STATUS_SEC_SIGNATURE_FAIL      | 44         |

| BOOTCORE_STATUS_SEC_WRONG_IMAGE_VERSION | 45         |

| BOOTCORE_STATUS_SEC_CRC_KO              | 53         |

| BOOTCORE_STATUS_SEC_DECRYPT_OK          | 56         |

| BOOTCORE_STATUS_SEC_DECRYPT_KO          | 57         |

| BOOTCORE_STATUS_SEC_IMGVERSION_PRG      | 61         |

| BOOTCORE_STATUS_SEC_IMGVERSION_PRGERR   | 62         |

| BOOTCORE_STATUS_SEC_EXIT_FSBL_DONE      | 63         |

Table 21. Boot ROM code status nonsecure

| Boot ROM code status                      | Bit number |

|-------------------------------------------|------------|

| BOOTCORE_STATUS_NSEC_PLLUSB_LOCKED        | 1          |

| BOOTCORE_STATUS_NSEC_TRACE_IS_INITIALIZED | 2          |

# 3.11 Supported configurations

# 3.11.1 Boot ROM related fuse settings

# OTP words and bits description

The following table provides detailed descriptions of the OTP words and bits used in the boot ROM code.

Table 22. OTP words and bits

| OTP word | OTP bits | Name / description        | Detailed description                                                      |

|----------|----------|---------------------------|---------------------------------------------------------------------------|

| OTP0     | -        | OTP_HW_WORD0              | Virgin check                                                              |

| OTP1     | -        | OTP_HW_WORD1              | OTP security word to close security state                                 |

| OTP2     | -        | OTP_HW_WORD2              | OTP word for reopening (CLOSE->OPEN) via RMA password: RMA bits           |

| OTP3     | -        | OTP_HW_WORD3              | OTP Word for reopening (CLOSE->OPEN) via RMA password: RMA tries bits     |

| OTP4     | -        | OTP_HW_WORD4              | OTP word for TK retries (ECIES), used during ST key provisioning process  |

| OTP5     | -        | ID0                       | -                                                                         |

| OTP6     | -        | ID1                       | -                                                                         |

| OTP7     | -        | ID2                       | -                                                                         |

| OTP8     | -        | RPN_CODING                | -                                                                         |

| OTP9     | -        | FEATURE_DISABLING         | Feature disabling                                                         |

|          | -        | BOOTROM_CONFIG_1          | -                                                                         |

| OTP10    | [26:19]  | rssefw_active_signing_key | Monotonic key index of active signing key used for RSSe_FW authentication |

| OTP11    | -        | BOOTROM_CONFIG_2          | -                                                                         |

| OIPII    | [0]      | no_data_cache             | 0 (enabled): Data cache is used by boot ROM.                              |

UM3234 - Rev 3 page 23/50

| OTP word | OTP bits | Name / description        | Detailed description                                                                            |

|----------|----------|---------------------------|-------------------------------------------------------------------------------------------------|

|          |          |                           | 1 (disabled): Data cache is not used by boot ROM.                                               |

|          | [4]      | 75 57W W                  | 0 (enabled): PLLs for CPU/AXI are enabled for cold boot.                                        |

|          | [1]      | no_cpu_pll                | 1 (disabled): PLLs for CPU/AXI are not enabled for cold boot.                                   |

|          | [2]      | sdmmc1_not_default_af     | 0 (no): SDMMC1 uses a default hard-coded AFmux.                                                 |

|          |          |                           | 1 (yes): SDMMC1 uses AFmux defined in OTP.                                                      |

|          | [3]      | sdmmc2_not_default_af     | 0 (no): SDMMC2 uses the default hard-coded AFmux.                                               |

|          |          |                           | 1 (yes): SDMMC2 uses AFmux defined in OTP.                                                      |

|          |          |                           | 1 (SD card): SD card SDMMC1.                                                                    |

|          |          |                           | 2 (emmc): eMMC SDMMC1. 3 (snor): XSPI NOR.                                                      |

|          |          |                           | 4 reserved.                                                                                     |

|          | [8:5]    | flash boot source         | 5 (hflash): XSPI HyperFlash <sup>™</sup> .                                                      |

|          | [0.5]    | llasti_boot_source        | 6 reserved.                                                                                     |

|          |          |                           | 7 (SD card): SD card SDMMC2.                                                                    |

| OTP11    |          |                           | 8 (emmc): eMMC SDMMC2.                                                                          |

|          |          |                           | Other: invalid.                                                                                 |

|          |          |                           | 0x01 (usb): disable USB boot source.                                                            |

|          |          | boot_source_disable       | 0x02 (uart): disable UART boot source.                                                          |

|          | [16:9]   |                           | 0x04 reserved.                                                                                  |

|          |          |                           | 0x08 reserved.                                                                                  |

|          |          |                           | 0x10 reserved.                                                                                  |

|          | [19:17]  | reserved                  | -                                                                                               |

|          | [22:20]  | uart_instance_disable     | 0b001: disable USART1 instance. 0b010: disable USART2 instance. 0b100: disable USART3 instance. |

|          | [28:26]  | reserved                  | -                                                                                               |

|          |          |                           | Enable the configuration of tampers in the boot ROM before the boot process.                    |

|          | [29]     | tamp_boot_cfg_glob_enable | 0: configuration of tampers is disabled.                                                        |

|          |          |                           | 1: configuration of tampers is enabled.                                                         |

|          | 1001     |                           | HyperFlash <sup>™</sup> is a 3.3V device.                                                       |

|          | [30]     | xspi_3v3                  | 0: not a 3.3V XSPI. 1: It is a 3.3V XSPI.                                                       |

| OTP12    | [31:0]   | BOOTROM_CONFIG_3          | rssefw_version_monotonic_counter                                                                |

|          | -        | BOOTROM_CONFIG_4          | -                                                                                               |

|          |          |                           | 0 (af_nopull_ls): AF; no pull; low speed.                                                       |

|          |          |                           | 1 (af_nopull_ms): AF; no pull; medium speed.                                                    |

| OTD42    |          |                           | 2 (af_nopull_hs): AF; no pull; high speed.<br>3 (af_pullup_ls): AF; pull up; low speed.         |

| OTP13    | [3:0]    | mode0                     | 4 (af_pullup_ms): AF; pull up; medium speed.                                                    |

|          |          |                           | 5 (af_pullup_hs): AF; pull up; high speed.                                                      |

|          |          |                           | 6 (af_pulldown_ls): AF; pull down; low speed.                                                   |

|          |          |                           | 7 (af_pulldown_ms): AF; pull down; medium                                                       |

|          |          |                           | speed.                                                                                          |

UM3234 - Rev 3 page 24/50

| OTP word | OTP bits | Name / description            | Detailed description                                          |

|----------|----------|-------------------------------|---------------------------------------------------------------|

|          |          |                               | 8 (af_pulldown_hs): AF; pull down; high speed.                |

|          |          |                               | 9 (gpio_out_high): GPIO output high.                          |

|          |          |                               | 10 (gpio_out_low): GPIO output low.                           |

|          |          |                               | 11 (gpio_in): GPIO input.                                     |

|          |          |                               | 12 (gpio_open_nopull): GPIO <b>open</b> drain; no pull.       |

|          |          |                               | 13 (gpio_open_pullup): GPIO <b>open</b> drain; pull up.       |

|          |          |                               | 14 (gpio_open_pulldown): GPIO open drain; pull                |

|          |          |                               | down.<br>15 (gpio_analog): GPIO analog mode.                  |

|          | [7:4]    | afmux0                        | Value between 0 and 15.                                       |

|          |          |                               | [0-15]: pin id between 0 and 15 for GPIOA to GPIOG and GPIOP. |

|          | [11:8]   | pin0                          | [0-12]: pin id between 0 and 12 for GPION.                    |

|          | [11.0]   | pino                          | [0-8]: pin id between 0 and 8 for GPIOH and GPIOQ.            |

|          |          |                               | [0-5]: pin id between 0 and 5 for GPIOO.                      |

| OTD40    |          |                               | 0: unused.                                                    |

| OTP13    |          |                               | 1 (PA): Bank A.                                               |

|          |          |                               | 2 (PB): Bank B.                                               |

|          |          |                               | 3 (PC): Bank C.                                               |

|          |          |                               | 4 (PD): Bank D.                                               |