User manual

# Getting started with the STSW-STNRG011GUI GUI for STNRG011/STNRG011A products

# Introduction

This document describes the STSW-STNRG011GUI operations to control the STNRG011/STNRG011A products using the STEVAL-PCC020V2 USB to I²C/UART interface board. If you are using the STEVAL-PCC020V1, buy this new version.

The STEVAL-PCC020V2 is a dedicated USB hardware interface used to connect a Windows®-based PC with the STNRG digital power supply controllers, such as the STNRG01x.

This document explains first the software installation and then the detailed use of the interface with the STSW-STNRG011GUI.

This GUI allows monitoring the digital controller status in real-time. It also allows tuning specific parameters according to the customer's needs.

# 1 GUI features

- Real-time monitoring of the digital controller status

- Access to STNRG011/STNRG011A NVM parameters

- Access to STNRG011/STNRG011A external E<sup>2</sup>PROM for patch upload, calibration, and event history

- Embedded PFC calibration wizard

UM3012 - Rev 1 page 2/37

# 2 Software installation

You have to install the USB driver and the PC GUI before using the STEVAL-PCC020V2 interface board.

# 2.1 Virtual COM port driver installation (SiLabs CP2102)

To use the STEVAL-PCC020V2 interface board, install one of the USB drivers located in the Driver\CP210x VCP Windows CD folder:

- "CP210xCVCPInstaller x86.exe" (for 32-bit OS)

- "CP210xCVCPInstaller\_x64.exe" (for 64-bit OS)

Alternatively, you can find the latest version of the drivers on the SiLabs website.

When the interface board is plugged onto the PC, the driver is automatically installed.

# 2.2 GUI installation

To install the STSW-STNRG011GUI, follow the procedure below.

- Step 1. Launch Setup.msi located in the download folder.

- Step 2. Follow the installation wizard instructions.

By default, the GUI is installed under C:\Program Files (x86)\STMicroelectronics\STNRG011 GUI\. The GUI installer creates an icon in the [Start] menu, under STMicroelectronics\STNRG011.

Figure 1. STSW-STNRG011GUI icon

Note: If a previous version of the software has already been installed, uninstall it through the [Windows

Control Panel Uninstall] option.

Note: Install and save the STSW-STNRG011GUI in a folder with administrator rights for reading and writing.

UM3012 - Rev 1 page 3/37

# **GUI** overview

The STSW-STNRG011GUI is designed for debugging power supply applications.

### It allows:

- reading instantaneous power metering information and PFC operating modes;

- reading and modifying STNRG011/STNRG011A NVM parameters defining the supply behavior (gain, fault management, delays, PFC/LLC parameters, etc.);

- reading event history data (fault history, stored in optional E<sup>2</sup>P);

- programming optional E2P patches;

- accessing internal firmware variables (patch needed).

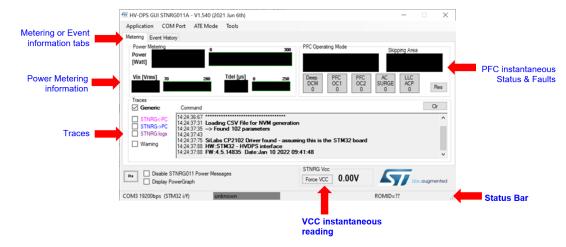

#### 3.1 Startup screen

The GUI is split in the following areas:

- Menu Bar: used to select the operation mode, that is, to communicate with STNRG011/STNRG011A, display logs, access E2P directly, NVM programming, etc.

- Metering or Event tabs: displays the power metering information or event history

- Traces and Status: internal debug traces and status bar that show the STNRG011/STNRG011A current status

Figure 2. STSW-STNRG011GUI startup screen

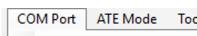

#### 3.2 **Connection management**

At startup, the GUI automatically detects the COM port to be used (the GUI selects the CP2102-based VCP). In the case of multiple CP2102, you have to select manually the right COM port via the COM port menu. You can also open or close the COM port via the menu shown below.

Figure 3. COM port selection

UM3012 - Rev 1 page 4/37

Once the right COM port is selected, the GUI tries to communicate with the interface board microcontroller, as shown below.

Figure 4. Traces during GUI connection

```

14:40:18:52 Loading CSV File for NVM generation

14:40:18:60 -> Found 104 parameters

14:40:18:74

14:40:19:34 SiLabs CP2102 Driver found - assuming this is the STM32 board

14:40:19:43 HW:STM32 - HVDPS interface

14:40:19:44 FW:2.3.4896 Date:Apr 8 2015 15:42:08

14:42:08:17 Waiting BlackBox messages

```

Once the microcontroller has been detected, the GUI displays the associated hardware and firmware version, and the build date.

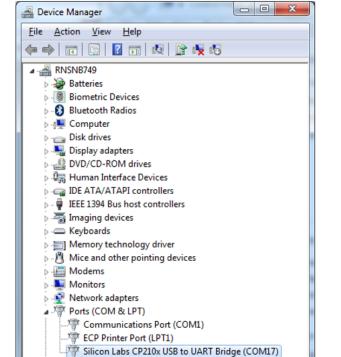

Note: If the GUI does not find a SiLabs-based VCP, an error message appears. Check if the SiLabs VCP is correctly recognized by pressing plus [Pause]. Then, select [Device Manager]>[Silicon Labs CP210x USB to UART Bridge (COM17)], as shown in the following figure.

Figure 5. SiLabs VCP in the [Device Manager]

UM3012 - Rev 1 page 5/37

Processors

Security Devices

Sound, video and game controllers

▶ - ■ Universal Serial Bus controllers

# 3.3 Settings

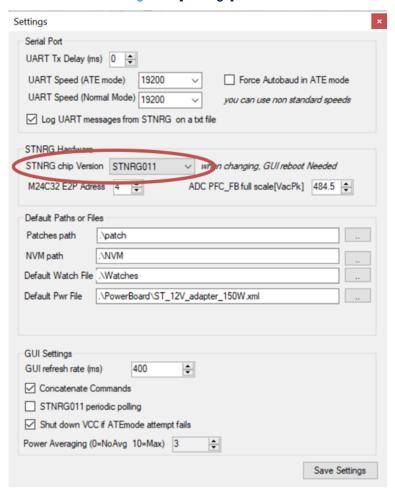

You can access the GUI settings through the [Application]>[Settings] menu.

Figure 6. [Settings] menu

Some settings (for example, the GUI refresh rate or power averaging) can be changed in real-time. In the **[STNRG chip Version]** section, you can choose between STNRG011 and STNRG011A.

Press the [Save Settings] button to save the settings into the config.xml file.

UM3012 - Rev 1 page 6/37

**Table 1. GUI setting parameters**

| Serial port                               |                                                                                                                                                                                                                                                                            |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| UART Tx delay (ms)                        | Optional Tx delay. Keep it at 0 ms.                                                                                                                                                                                                                                        |  |  |

| UART speed (ATE mode)                     | STNRG011/STNRG011A UART speed during the logging phase                                                                                                                                                                                                                     |  |  |

| UART speed (normal mode)                  | STNRG011/STNRG011A UART speed during the ATE mode                                                                                                                                                                                                                          |  |  |

| Forces autobaud in ATE mode               | When entering the ATE mode, it performs the autobaud algorithm. This is supposed not to be necessary, as the STNRG011/STNRG011A internal RC oscillator is trimmed in production to guarantee the correct UART speed                                                        |  |  |

| Log UART messages from STNRG011/STNRG011A | Option to log the UART exchange on a file (uart_trace.txt on the GUI executable directory)                                                                                                                                                                                 |  |  |

|                                           | STNRG011/STNRG011A                                                                                                                                                                                                                                                         |  |  |

| M24C32 E2P address                        | Hardware address of the external E2P. STNRG011/STNRG011A is always assuming 4 (100)                                                                                                                                                                                        |  |  |

| ADC PFC_FB full scale                     | Full-scale equivalent value of the PFC_FB pin, which is the voltage expected at the bulk capacitor when the voltage at the PFC_FB pin is at the ADC full scale (2.5 V). Keep this value, if you are using the standard resistive bridge divider (9 $M\Omega/46.7~k\Omega)$ |  |  |

|                                           | Default paths                                                                                                                                                                                                                                                              |  |  |

| Patches path                              | Default path for the E2P patches                                                                                                                                                                                                                                           |  |  |

| NVM path                                  | Default path for the NVM settings                                                                                                                                                                                                                                          |  |  |

| Default watch files                       | Default path for the watch settings, used to monitor the firmware internal variables                                                                                                                                                                                       |  |  |

| Default power file                        | Calibration file for the power metering                                                                                                                                                                                                                                    |  |  |

|                                           | GUI settings                                                                                                                                                                                                                                                               |  |  |

| GUI refresh rate (1)                      | Delay in ms among each GUI refresh                                                                                                                                                                                                                                         |  |  |

| Concatenate commands (1)                  | Messages sent to the STNRG are concatenated to avoid USB overhead (Write1-Write2Read1-Read2 instead of Write1-Read1-Write2-Read2)                                                                                                                                          |  |  |

| STNRG011/STNRG011A<br>periodic polling    | Periodically polls the STNRG011/STNRG011A status                                                                                                                                                                                                                           |  |  |

| Shut down the VCC if the ATE mode fails   | If enabled, when the device cannot enter the ATE mode, it switches off the VCC supply                                                                                                                                                                                      |  |  |

| Power averaging                           | Averaging filter for real-time power display:  0 = no averaging  10 = maximum averaging                                                                                                                                                                                    |  |  |

<sup>1.</sup> Used only when the [Power Monitor] window is active.

UM3012 - Rev 1 page 7/37

# **GUI normal mode**

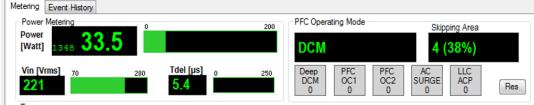

#### 4.1 **Power metering**

During the normal mode, the STNRG011/STNRG011A sends the information used to compute the actual power delivered by the PFC, that is:

- the estimated power computed by the power integration algorithm

- some factors used for power estimation correction:

- V<sub>IN</sub> (mains) voltage

- PFC mode of operations (DCM, valley skipping, TM)

- Time between PFC pulses (DCM mode only)

- Phase angle modulation ratio (at low power only)

- Some flags about temporary PFC faults (deep DCM, PFC\_OCP1, etc.).

PFC Operating Mode 200

Figure 7. GUI metering information panel

Note: If the STNRG011/STNRG011A power messages are disabled, the boxes shown above are empty.

Important: The power metering is not available in the burst mode, to save the MCU power energy, hence, the efficiency at low power).

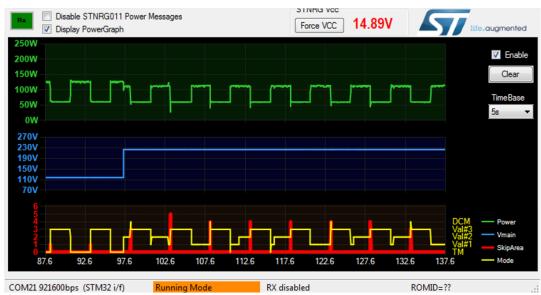

#### 4.2 Power graph report

By checking the [Display PowerGraph] box, the history of the [PowerGraph] event is displayed. It shows the long-term stability of the power supply or the mode changes compared to the load.

Figure 8. GUI [PowerGraph] report

UM3012 - Rev 1 page 8/37

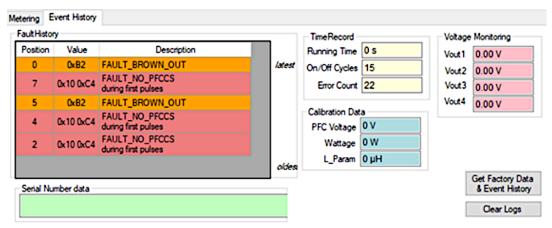

# 4.3 Event history and factory data prerequisite: E<sup>2</sup>P

Event history and factory data are available only if an external E²PROM (M24C32) is connected to the STNRG011/STNRG011A. This allows retrieving some information in case of system failures.

Since the fault history and factory data are sent only at the system power-up, you have to turn the power supply off and on to get the status.

However, if the UART uplink communication is enabled (a patch is needed), it is possible to send a request to the STNRG011/STNRG011A to show immediately the event and fault history by pressing the [Get Factory Data] button.

Another option is to read directly the E<sup>2</sup>P content.

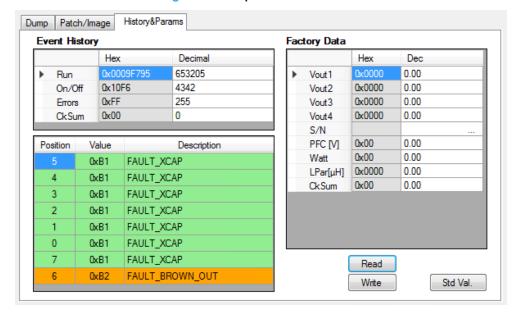

# 4.3.1 Event history

The fault history is stored in the optional external E<sup>2</sup>P.

Carabi Baran

The faults are stored in an eight-position circular buffer; hence, only the last eight faults are stored.

At each power-up, the STNRG011/STNRG011A sends the content of the fault history, which is a sort of black box, to the host.

The GUI displays the faults in a chronological order (the latest at the bottom).

Note: There are two types of faults:

- the standard fault → one position per fault in the circular buffer;

- the fault with debug information → two positions per fault in the circular buffer; this fault provides more firmware information.

| Position | Value     | Description                           |        |

|----------|-----------|---------------------------------------|--------|

| 0        | 0xB1      | FAULT_XCAP                            | latest |

| 7        | 0xB1      | FAULT_XCAP                            |        |

| 6        | 0xB2      | FAULT_BROWN_OUT                       |        |

| 5        | 0xB1      | FAULT_XCAP                            |        |

| 4        | 0xB1      | FAULT_XCAP                            |        |

| 3        | 0x11 0xC1 | FAULT_PFC_UVP<br>AC presence:detected |        |

| 1        | 0xB1      | FAULT_XCAP                            | oldesi |

Figure 9. GUI fault history

The number of faults stored depends on the fault type (between 4 and 8).

For instance, the figure above shows:

- a PFC\_PFC\_UVP with AC presence fault (position 3), which uses two positions in the buffer, while the

previous fault is at position 1;

- two shutdown events (XCAP discharged → positions 4 and 5);

- a BrownOut event ( $V_{AC}$  < 70 Vrms  $\rightarrow$  position 6);

- two shutdown events (positions 7 and 0).

UM3012 - Rev 1 page 9/37

# 4.3.2 Factory data display

Figure 10. GUI factory data panel

Like faults history, the factory data are sent at each STNRG011/STNRG011A power-up.

The table below shows the factory data parameters and lists some fields as examples for a possible user application.

Table 2. GUI E<sup>2</sup>P parameter description

| Voltage monitoring           |                                                                         |  |

|------------------------------|-------------------------------------------------------------------------|--|

| Vout1                        |                                                                         |  |

| Vout2                        | Customer factory field, which is not used by the firmware or the GUI    |  |

| Vout3                        |                                                                         |  |

| Vout4                        |                                                                         |  |

|                              | Calibration data                                                        |  |

| PFC voltage                  | Containing factors, field which is not used by the firmware or the CIII |  |

| Wattage                      | Customer factory field, which is not used by the firmware or the GUI    |  |

| L_Param                      | PFC inductance used by the power computation algorithm                  |  |

|                              | Time record                                                             |  |

| Running time                 | Power supply cumulated active time                                      |  |

| On/off cycles                | Number of power supply restart events                                   |  |

| Error count                  | Number of errors                                                        |  |

|                              | Serial number data                                                      |  |

| Serial number, 20 characters | Customer factory field, which is not used by the firmware or the GUI    |  |

UM3012 - Rev 1 page 10/37

# 5 Power metering calibration

# 5.1 Background

The STNRG011/STNRG011A provides continuous power-metering information to the host about:

- the PFC integrated power in raw format, which is the result of the PID integrator;

- the input voltage;

- the PFC operating mode and skipping area;

- · the PFC fault status.

The instantaneous raw power estimation can be computed as follows:

$$P_{Raw}[W] = PFC_{lsb} \times \left[128 \times \left(\frac{FSR_{Vin}}{256}\right) \times \frac{t_{smed}}{L}\right] \tag{1}$$

### where:

- P<sub>Raw</sub> is the PFC power (not corrected);

- PFC<sub>Isb</sub> is the PFC integrated power in raw format;

- FSR<sub>Vin</sub> is the full-scale ADC voltage reading = 480 V;

- t<sub>smed</sub> is the *smed* event (PFC timer) minimal duration = 1/60 MHz = 16.67 ns;

- L is the PFC inductor value (typically 250 μH on the evaluation board).

The raw power is almost proportional to the actual PFC power.

On the basis of the PFC mode and input voltage, it is possible to correct the raw power to deduce the actual power consumption.

As several parameters have to consider, a very simple approach is to use a calibration method for each PFC operating mode.

The output power is also compensated with the skipping area and input voltage, using the formula below:

$$Pout[W] = (P_{Raw} \times C_{Mode} + C_{Vin}) \times C_{PAM} \times (1 + C_{Tdel})$$

(2)

### where:

- P<sub>Raw</sub> is the raw power;

- C<sub>Mode</sub> is the PFC mode correction factor (typically between 0.7 and 1);

- C<sub>Vin</sub> is the input voltage correction using a second order polynomial (a+b\*Vin+c\*Vin²). However, since we

typically consider only two voltages (EU/US), the second order term is set to 0;

- C<sub>PAM</sub> is the skipping area correction factor (1 for no PAM, 0.26 for the minimum PAM);

- C<sub>Tdel</sub> is the DCM mode correction using a first order equation (a+b\*Tdel).

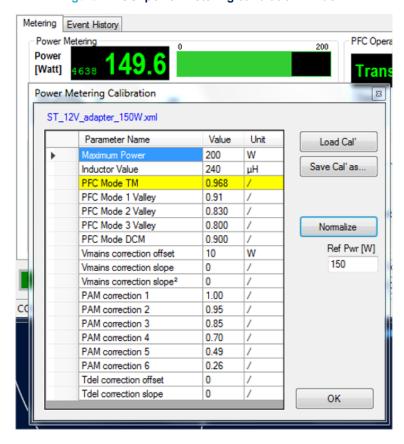

# 5.2 Metering calibration

To display the power metering correction factors described in the previous section, go to the [Application → Power Metering Calibration] menu. The GUI highlights the current PFC operating mode in yellow.

To calibrate the PFC mode parameters, follow the procedure below.

- Step 1. Set a load to make the system enter the transition mode (near nominal power, that is, 150 W).

- Step 2. Enter the associated reference power read on a precision power meter in the [Ref Pwr] box.

UM3012 - Rev 1 page 11/37

# Step 3. Press the [Normalize] button.

The GUI automatically computes and updates the correction factor associated to the current PFC operating mode.

The power displayed in the GUI must be equal to the reference power. This operation has to be repeated for every PFC mode (DCM, *Valley#1/2/3*).

The other parameters (PAM correction, Tdel correction, Vmains) have to be tuned manually.

Figure 11. GUI power metering calibration window

UM3012 - Rev 1 page 12/37

# 6 ATE mode

### 6.1 Normal and ATE mode: differences

The STNRG011/STNRG011A supports two main modes of operation:

- Normal (or running): is the GUI normal operation mode

- ATE: is mainly used to program the STNRG011/STNRG011A NVM section and is based on the ATE protocol

Table 3. Differences between normal and ATE modes

| Mode                      | Running (normal) mode                                                | ATE mode        |

|---------------------------|----------------------------------------------------------------------|-----------------|

| Metering information      | Available through the metering protocol (STNRG011/STNRG011A to host) | Not available   |

| ATE protocol              | No (default)                                                         | Yes             |

| Communication             | STNRG011/STNRG011A →host only (default)                              | Bidirectional   |

| PFC/LLC operations        | Yes                                                                  | No              |

| STNRG011/STNRG011A supply | Self-supplied                                                        | External supply |

| NVM write                 | No                                                                   | Yes             |

Note: It is also possible to enable the ATE protocol in running mode for the bidirectional communication. This requires a specific patch to enable the UART uplink communication.

Note: If the ATE protocol is enabled during the normal mode, the GUI is able to handle simultaneously [Metering information] and [ATE protocol]. However, the bandwidth on the UART link might be impacted. So, it is recommended to disable the metering protocol by checking the [Disable STNRG011 Power messages] box.

Figure 12. GUI: disable STNRG011 power messages

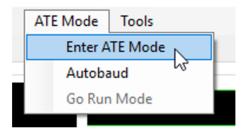

# 6.2 Entering ATE mode

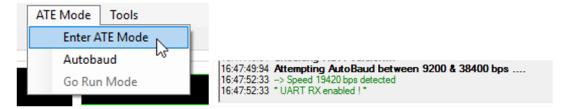

The ATE mode menu is used to set the STNRG011/STNRG011A in ATE mode.

Figure 13. ATE mode menu

The available options are:

- [Enter ATE Mode (Force VCC)]: attempts the ATE mode procedure.

The GUI:

- 1. asserts the SCL pin low (requests to enter the ATE mode);

- 2. switches on the internal VCC generation;

- 3. checks that the ATE mode is effectively working;

- [Auto baud]: is used for internal debug purposes but also to check the UART speed. Basically, it performs the autobaud and computes the optimal UART link speed;

UM3012 - Rev 1 page 13/37

• [Go Run Mode]: switches off the internal VCC generation.

Once the device has successfully entered the ATE mode, the status bar is updated and the ROM ID is displayed (here is 0x0004).

Figure 14. ATE mode status bar

Note:

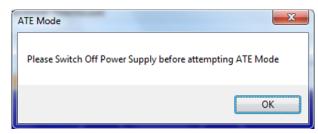

The GUI prevents accessing the ATE mode or forcing VCC when it detects that the STNRG011/STNRG011A is running in the normal mode. The main power supply must be switched off before entering the ATE mode.

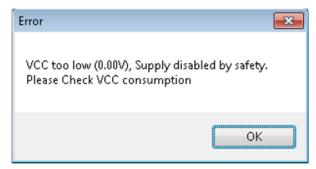

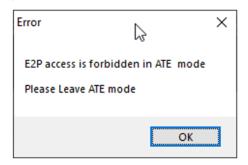

Figure 15. GUI error when trying to enter ATE mode while in normal mode

Note:

Once the VCC is applied (just after the soft-start), the GUI measures the VCC voltage value: if it is below a given threshold (17 V), the GUI assumes an overconsumption and the VCC is automatically disabled.

Figure 16. GUI error when the VCC is applied

# 6.3 Autobaud feature

If the device is not able to enter the ATE mode, it might be due to UART communication issues.

The STNRG011/STNRG011A timing relies on an internal calibrated oscillator, but it does not have the accuracy of an external crystal.

After the ST factory calibration (trimming), the resulting accuracy is about 2.3%. It is enough to ensure the normal UART communication.

However, if the accuracy is outside the UART tolerances, the GUI might not be able to communicate with the STNRG011/STNRG011A and the ATE mode might fail.

To avoid this failure, the GUI has an autobaud function, which tries to communicate with the STNRG011/STNRG011A chip at various speeds.

So, if the ATE mode sequence fails, select the autobaud feature.

If the GUI is able to communicate with the chip, it displays the resulting UART speed and applies it for the ATE mode.

UM3012 - Rev 1 page 14/37

Figure 17. Autobaud menu and results

Note: The computed speed is not updated in the [Application Settings] menu.

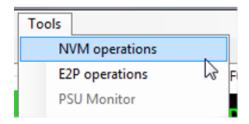

# 6.4 NVM operations

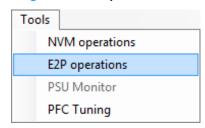

In the ATE mode, NVM operations are accessible via the **Tools** menu.

Figure 18. NVM operation menu

All the power supply customization parameters are stored in the STNRG011/STNRG011A on-chip NVM memory. You can read/write the NVM by:

- 1. using the [NVM r&w] tab, mainly to write the complete NVM without knowing the parameters;

- 2. using the [NVM editor] to edit specific parameters.

Note:

The NVM of STNRG011 and STNRG011A are a bit different. Refer to the related documents about the NVM parameters description.

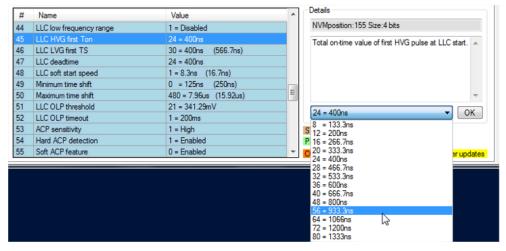

# 6.5 NVM editor

The NVM editor provides an intuitive way of changing the STNRG011/STNRG011A system parameters, which are about 80.

These parameters are stored in the 32-byte NVM on-chip memory.

The GUI maps the NVM parameters to the 32-byte memory.

Danger:

Take care when changing the NVM parameters. Improper settings can lead to the offline converter destruction.

UM3012 - Rev 1 page 15/37

NVM operations Parameters editor Read from IC NVM operations Export NVM to Disk Write to IC # Name Value Detailed NVMposition:64 Size:1 bits Patch upload from EEPROM description of Enable/disable the shutdown feature through LLC\_FB pin. Shutdown is sensed on the LLC\_FB pin if it is put below 125mV. NVM ATE mode 0 = Enabled 0 = Enabled System monitoring parameters List of VAC reading improv 0 = Disabled 0 = Enabled Early Warning feature parameters EW signal in burst mo sort by Non latched faults timer 0 = 546ms **Parameter** 0 = Disabled ∨ OK sections possible values SYSTEM FAULT PFC OC2 detection 0 = Disabled Max number of PFC OC2 PFC HW OVP dete Access to different sections of parameters

Figure 19. NVM editor window

The NVM options are:

- [Read from IC]: reads the NVM content from the chip;

- [Write to IC]: writes the current NVM content to the chip;

- [Import NVM from disk]: reads an NVM file (.INIT format) previously stored;

- [Export NVM to disk]: writes the current NVM on the disk (.INIT format).

Note: Writing the NVM parameters is possible only in the ATE mode.

# 6.5.1 How to change parameters

Step 1. Click on the parameter to edit.

To access quickly the parameters, you can click on the relevant section (system, fault, LLC, PFC, etc.), which displays a detailed description of that parameter.

Step 2. Click on the [Combo] box to choose the value.

For each value, the internal firmware value is also shown.

Figure 20. Parameter change

Step 3. Press [OK] to validate the change.

Once the parameter has been changed and is different from the current NVM, it is highlighted in yellow.

Step 4. Click the [Write to IC] button to program the NVM memory.

UM3012 - Rev 1 page 16/37

# 7 E<sup>2</sup>P operations

Important:

STNRG011/STNRG011A shares the E<sup>2</sup>P interface (SDA/SCL) with the UART interface to minimize pin count. During the normal operation (switching), the optional E<sup>2</sup>P is only accessed at boot and when a fault occurs.

It is possible to access E<sup>2</sup>P in the normal mode, but this might cause conflicts due to simultaneous access by the STNRG011/STNRG011A metering information (UART) and the GUI accessing the E<sup>2</sup>P.

As a consequence, the STNRG011/STNRG011A metering messages must be disabled, but this is only possible if the UART uplink communication is enabled. Otherwise,  $E^2P$  must be accessed while STNRG is disabled (that is, no mains nor an external  $V_{CC}$  are required thanks to the internal  $V_{CC}$  generation in the ATE mode).

Figure 21. E<sup>2</sup>P access in the ATE mode error

E<sup>2</sup>P operations are accessible via the [Tools] menu, as detailed below:

- shut down the mains;

- press the [GUI Force VCC] button to apply the VCC without entering the ATE mode (the SDA is not pulled low);

- go to the [Tools] menu and select [E2P operation].

Figure 22. E<sup>2</sup>P operation menu

# 7.1 E<sup>2</sup>P dump

This feature allows displaying the content of the external E<sup>2</sup>P. It is mainly used for debugging. It also allows changing a memory value by either clicking the address to be changed or by pressing the [**Write**] button in the [**Address**] and [**Value**] boxes.

Table 4. E<sup>2</sup>P mapping

| Area          | Meaning                                                     |

|---------------|-------------------------------------------------------------|

| 0x0000-0x0022 | Serial number and calibration data                          |

| 0x0040-0x0047 | Event history data                                          |

| 0x0048-0x004F | Running time, error counter, and power on/off cycle counter |

| 0x0080-0x0089 | Definition of cold/hot patch addresses                      |

| 0x0090-0x0A80 | Patch area                                                  |

UM3012 - Rev 1 page 17/37

E<sup>2</sup>P Operations Dump Patch/Image History&Params Write Start Adress Write Adress 0x0000 Value 0x0000 Dump ÷ 0A 0C 0E ASCII °•0° -B180 01B0 B001 01E0 F000 à.. ι. ٦ÛB 00A0 00B0 00C0 00D0 00E0 00F0

Figure 23. E<sup>2</sup>P dump tab

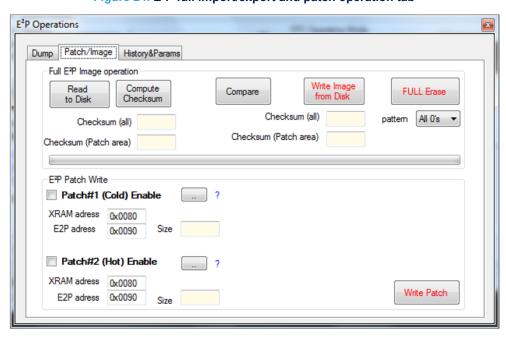

# 7.2 E<sup>2</sup>P patch and image upload/download

This feature allows manipulating the entire E<sup>2</sup>P images and also programming the patch.

# 7.2.1 Full E<sup>2</sup>P image operation box

This tab button allows:

- reading the full E<sup>2</sup>P image and save it to the disk

- computing the E<sup>2</sup>P checksum

- comparing E<sup>2</sup>P to an existing image

- writing the entire E<sup>2</sup>P using an image previously saved on the disk (performing the E<sup>2</sup>P parameters and E<sup>2</sup>P patch programming in a single step)

- erasing the entire E<sup>2</sup>P

Note:

If an E<sup>2</sup>P is connected, the STNRG011/STNRG011A firmware does not support an empty (FF) image. The E<sup>2</sup>P must be cleared using the [All 0s pattern]. Alternatively, a full image can be written (provided by ST).

Both [Erase] and [Write] operations need confirmation to be saved.

# 7.2.2 Patch programming box

There are two different types of patches:

- cold, downloaded from E<sup>2</sup>P to XRAM just before the IC starts switching

- · hot, downloaded after IC has started switching operations

We use only the cold patch in this example.

Note: Usually, you do not have to specify the patch type (hot/cold). Patches are delivered as a full E<sup>2</sup>P image.

Important: Do not change the XRAM and E2P address.

To program a patch, follow the steps below.

Step 1. Click on the [..] button to select the patch to be used.

Note: Only the .bin format is supported.

UM3012 - Rev 1 page 18/37

- Step 2. Tick the associated [Check] box.

- Step 3. Press the [Write Patch] button.

Figure 24. E<sup>2</sup>P full import/export and patch operation tab

UM3012 - Rev 1 page 19/37

# 7.3 E<sup>2</sup>P parameter editor

This feature allows editing the factory data parameters and clearing the event history data.

- Step 1. Press the [Read] button to read the content of the E2PROM.

- **Step 2.** Press the [Write] button to write the displayed values to the E<sup>2</sup>PROM.

- Step 3. Press the [Std Values] button to fill the table with the default values.

If you want to write the values to the E2P, you have to press the [Write] button.

Note: The hex fields are only given for reference: they cannot be edited.

Important: It is recommended to edit these field with the STNRG011/STNRG011A in ATE mode or via a VCC

externally powered.

If the parameters are written while the STNRG011/STNRG011A is running, they are overwritten when STNRG011/STNRG011A is shut down.

When the STNRG011/STNRG011A is powered up, it makes a copy of the event history in its RAM, which changes during the active phase. At shutdown, the RAM content is overwritten in the E<sup>2</sup>P, hence the E<sup>2</sup>P content is overwritten.

Figure 25. E<sup>2</sup>P parameter editor tab

UM3012 - Rev 1 page 20/37

# 8 Additional tools

The GUI embeds some additional tools useful during the power supply integration phase.

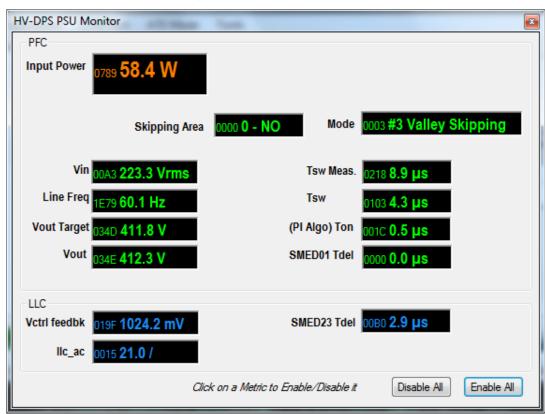

# 8.1 PSU monitor

Note: A specific patch

A specific patch is needed to access this feature. Contact STMicroelectronics sale office for details.

The PSU monitor provides similar information to the power metering, but only on a specific request by the GUI (different from the power metering information sent continuously by STNRG011/STNRG011A).

In this case, the GUI reads the STNRG011/STNRG011A memory directly and additional information can be retrieved.

Figure 26. PSU monitor window

UM3012 - Rev 1 page 21/37

# Table 5. PSU monitor: PFC/LLC features

| PFC                       |                                                                                            |  |

|---------------------------|--------------------------------------------------------------------------------------------|--|

| Input power               | Estimated PFC power corrected by V <sub>IN</sub> /PAM/mode/Tdel parameters                 |  |

| V <sub>IN</sub>           | Mains voltage in RMS value                                                                 |  |

| Line Freq                 | Mains frequency                                                                            |  |

| V <sub>OUT</sub> target   | PFC output voltage (target)                                                                |  |

| V <sub>OUT</sub>          | PFC output voltage (measured)                                                              |  |

| Tsw measurement           | PFC switching period measured at the input line peak                                       |  |

| Tsw                       | PFC switching period estimated in DCM for T <sub>off</sub> and T <sub>on</sub> calculation |  |

| (PI Algo) T <sub>on</sub> | Ton added computed by the power integration algorithm                                      |  |

| Smed01 T <sub>del</sub>   | Duration between PFC pulsed (DCM mode only)                                                |  |

| Skipping area             | PWM applied to PFC during a semi-cycle at low power                                        |  |

| Mode                      | PFC mode of operation                                                                      |  |

| LLC                       |                                                                                            |  |

| Vctrl feedback            | Output voltage of the error amplifier after opto-coupler, used for the LLC feedback loop   |  |

| Ilc_ac                    | LLC anti-capacitive mode indicator                                                         |  |

| SMED23 Tdel               | Value of the LLC time shift                                                                |  |

UM3012 - Rev 1 page 22/37

# 9 PFC calibration

The STNRG GUI can calibrate the PFC parameters thanks to the embedded wizard, which features:

- PFC parameter semiautomated calibration

- THD improver manual tuning

- Possibility to change manually some parameters to test the overall behavior

- Graphical representation of the mode switch

- PFC parameters are updated in the RAM; when the calibration results are satisfactory, you can store the

parameters in the NVM for permanent use

- Manual or automated working mode

Note:

Use the automated mode (a GPIB adapter is required). The embedded driver only supports the Chroma equipment. The SCPI commands issued are very generic, so it should work using other tools from other manufacturers (for example, Agilent/Keysight) but this is not guaranteed.

Otherwise, it is possible to use the manual mode, which is semiautomated. In this case, the GUI detects some events and tries to minimize the user's actions on the tools.

# 9.1 Principle

The calibration scope is to manage correctly:

- the PFC mode change (DCM, valley skipping, TM)

- the skipping area threshold (also called phase angle modulation)

- · the THD improver parameters

The PFC supports five different modes: DCM (low power), 3/2/1 valley skipping, and TM (high power).

The mode change is based on the estimated output power and the switching period.

Parameter name Typical value Description PFC THD improver base Base current of the THD improver (ReCOT functionality on PFC CS pin) 5 (10 mV) PFC THD improver gain 0 (no gain) Gain of the THD improver ramp (ReCOT functionality on PFC\_CS pin) 2176 PFC Min Pin Vskip Minimum PFC power to force a mode switch to DCM Maximum PFC power to force a mode switch towards TM (offset with respect to 2560 PFC Max Pin Vskip (delta) PFC Min Pin Vskip) Correction factor to minimize discontinuities while switching among different PFC PFC delta Pin Vskip 352 PFC power threshold to switch from DCM to valley skipping mode. It also sets PFC maximum DCM power 3072 the PFC on-time during DCM. Above this threshold, the system goes into valley skipping PFC Min Tsw Vskip 448 (134 kHz) Minimum PFC switching period (max. frequency) to force a mode switch to DCM PFC Max Tsw Vskip 608 (87 kHz) Maximum PFC switching period (min. frequency) to force a mode switch to TM Skipping area threshold 1536 PFC power threshold for the skipping area

Table 6. PFC parameters to be calibrated

Note:

The PFC calibration has to be performed for a given design (based on the component choice, supply output power, etc.). It is not necessary to perform the calibration for each unit created.

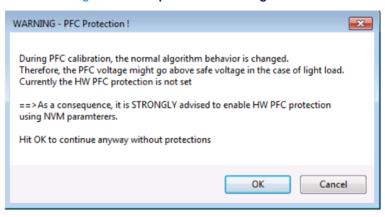

# 9.2 PFC protection

During the PFC calibration, the normal algorithm behavior is changed. In particular, the PFC mode change algorithms can be disabled to adjust some parameters.

Danger:

Consequently, the PFC bulk voltage can rise above the normal voltage at light load, leading to component (for example, bulk capacitors, MOS) damage and even destruction.

UM3012 - Rev 1 page 23/37

To prevent any damage, the GUI performs a preliminary safety check by reading the NVM content and checking if the PFC hardware protection is set. If not, a warning is displayed (as shown in the figure below), inviting the user to update the NVM accordingly.

Important: You can override the warning, but it is under your own responsibility.

Figure 27. PFC protection warning window

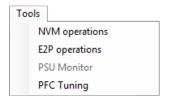

# 9.3 Step by step calibration example

To start calibration, go to the [Tools] menu and select [PFC tuning]. The following window pops up.

Figure 28. PFC tuning menu

Note:

To perform the calibration, the GUI has to communicate with the STNRG011/STNRG011A. Since the UART communication is disabled by default in the running mode, a special procedure (similar to the ATE mode) is applied to enable the UART communication, which requires switching the power supply on/off, as prompted by the GUI.

As previously mentioned, during the tuning operation phases, the GUI modifies the RAM parameters but writes nothing in the NVM (so, changes are not persistent).

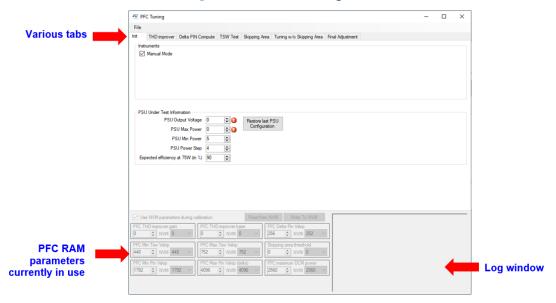

# 9.3.1 Tuning calibration tabs

The following picture shows the PFC tuning main window with tabs that represent the various steps to follow during the calibration.

UM3012 - Rev 1 page 24/37

Figure 29. Main PFC tuning tab

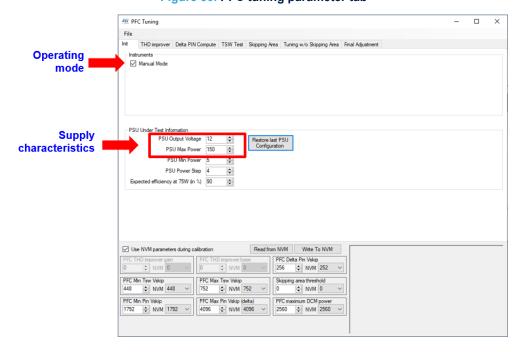

# 9.3.2 Mode of operation

You have to choose the operating mode (manual or not) and the power supply characteristics.

Figure 30. PFC tuning parameter tab

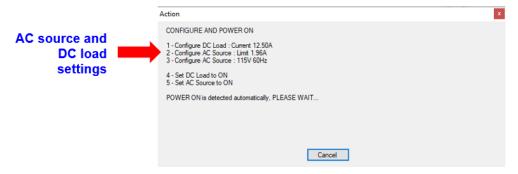

If manual mode is selected, you have to change manually the AC source voltage and DC load current: a window pops up each time an action is necessary.

The STNRG011/STNRG011A is able to detect when the AC source is switched on/off, which limits the interactions.

UM3012 - Rev 1 page 25/37

Figure 31. Manual mode: AC source voltage and DC load current selection

See Figure 32 for NVM options.

As the NVM storage space is limited, some PFC parameters have to be uploaded with a lower resolution than the NVM values. To ensure that the calibration reflects the real mode of operation, the calibrated values can be rounded to the closest one ticking the [Use NVM parameters] check box.

The [Read NVM] button transfers the content of the chip NVM memory to the GUI. This is useful to revert to the original calibration stored in the NVM, if the current calibration is not satisfactory.

The [Write NVM] button is used to write the current calibration in the chip NVM memory.

Figure 32. NVM parameters: RAM and NVM values

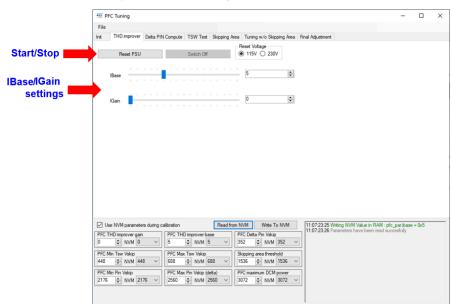

# 9.3.3 Step 1: THD improver

The first step is to calibrate the THD improver since the parameters directly affect the output power reported.

This feature helps to improve the AC current total harmonic distortion (THD) and the power factor (PF) value.

After pressing the [Reset PSU] button, follow the instructions.

Once the PSU starts, you can tune the IBase and IGain settings.

There is only one possible setting, so you have to try various loads and AC voltages to find the best trade-off across all the operation modes.

Figure 33. PFC tuning: THD improver tab

UM3012 - Rev 1 page 26/37

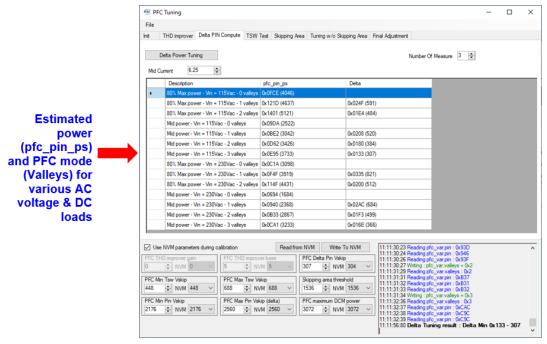

# 9.3.4 Step 2: delta pin calibration

The second step is to calibrate the delta pin correction factor when changing from one mode to the other. To compute the delta pin calibration, the GUI:

- disables the PFC mode change on the basis of the frequency and power values

- forces the PFC mode and records the associated estimated power

- repeats the operation for 2x load current and 2x AC input voltage

- · computes the delta pin correction factor

Figure 34. PFC tuning: delta pin calibration

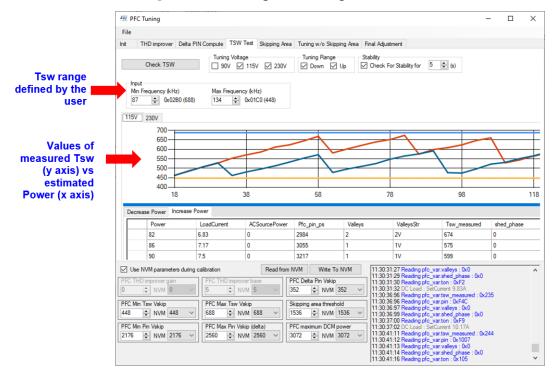

# 9.3.5 Step 3: TSW test

After computing the delta pin, the third step is to determine the mode changes based on the PFC frequency. You have to select manually the minimum/maximum bounds for the PFC frequency.

During the normal operations, if the PFC actual frequency crosses this boundary, a mode change is required. To check the [**TSW range**], in the GUI:

- PFC mode change is enabled on the basis of the PFC frequency (the mode change based on the estimated power is disabled)

- the output power is swept across the operating range

- the switching frequency is monitored; check that the mode change is stable (that is, the IC does not jump continuously from one mode to another because it crosses always a frequency limit during the mode change), adjusting the limits if needed.

Note: If you select the manual mode, the GUI asks to ramp-up and down the DC load smoothly.

UM3012 - Rev 1 page 27/37

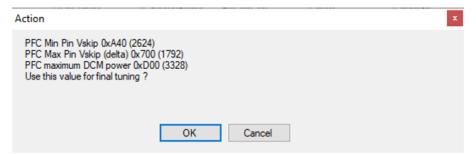

Figure 35. PFC tuning: determining TSW limits

Finally, the GUI computes the PFC parameters.

Figure 36. PFC tuning: PFC min./max. pin and DCM power

UM3012 - Rev 1 page 28/37

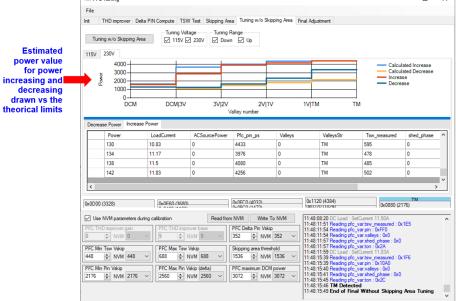

# 9.3.6 Step 4: skipping area threshold

The fourth step consists in setting the skipping area power threshold. Below this threshold, the system applies the power skipping, that is, it shuts down the PFC operation before or after the peak of the AC cycle, like PWM.

This improves the overall efficiency but obviously degrades the THD/PF figures. For this reason, it has to be performed at low power.

The threshold is up to the customer.

To determine the skipping area threshold, the GUI:

- enables the PFC mode change (both the PFC frequency and estimated power-based)

- sets the DC load to match the desired power

- measures the estimated power at various AC voltages

The threshold is the average of the measured values.

Figure 37. PFC tuning: determining the skipping area threshold

UM3012 - Rev 1 page 29/37

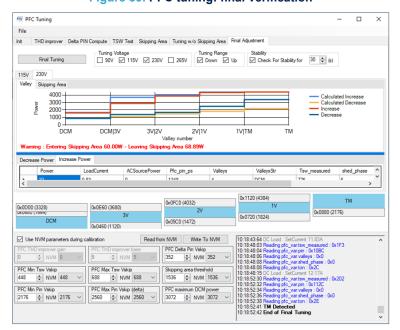

#### 9.3.7 Step 5: final verification

Once all the steps have been performed, the GUI simply checks the supply behavior.

To perform the final verification, the GUI:

- enables the PFC mode change (both the PFC frequency and estimated power-based) as the normal mode

- disables the skipping area mode (the focus is on the mode changes)

- sweeps the DC load across all the operating modes and checks if it is among the limits

Figure 38. PFC tuning: final verification without the skipping area tab

Figure 39. PFC tuning: final verification

UM3012 - Rev 1 page 30/37

# 9.4 PFC parameter update

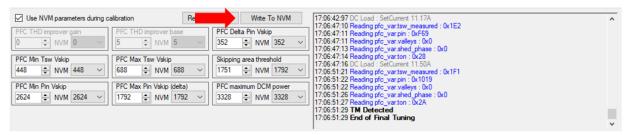

Once you are satisfied with the PFC calibration performance, you can update the NVM to make the parameters permanent, by simply clicking on the [Write to NVM] button.

Figure 40. PFC tuning: writing the NVM values

UM3012 - Rev 1 page 31/37

# **Revision history**

Table 7. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 19-Apr-2022 | 1        | Initial release. |

UM3012 - Rev 1 page 32/37

# **Contents**

| 1 | GUI                                                               | I features                                           |    |  |  |  |  |

|---|-------------------------------------------------------------------|------------------------------------------------------|----|--|--|--|--|

| 2 | Soft                                                              | tware installation                                   |    |  |  |  |  |

|   | 2.1                                                               | Virtual COM port driver installation (SiLabs CP2102) |    |  |  |  |  |

|   | 2.2                                                               | GUI installation                                     |    |  |  |  |  |

| 3 | GUI overview                                                      |                                                      |    |  |  |  |  |

|   | 3.1                                                               | Startup screen                                       | 4  |  |  |  |  |

|   | 3.2                                                               | Connection management                                | 4  |  |  |  |  |

|   | 3.3                                                               | Settings6                                            |    |  |  |  |  |

| 4 | GUI                                                               | I normal mode                                        | 8  |  |  |  |  |

|   | 4.1                                                               | Power metering                                       |    |  |  |  |  |

|   | 4.2                                                               | Power graph report                                   |    |  |  |  |  |

|   | 4.3 Event history and factory data prerequisite: E <sup>2</sup> P |                                                      |    |  |  |  |  |

|   |                                                                   | <b>4.3.1</b> Event history                           |    |  |  |  |  |

|   |                                                                   | 4.3.2 Factory data display                           |    |  |  |  |  |

| 5 | Power metering calibration                                        |                                                      |    |  |  |  |  |

|   | 5.1                                                               | Background                                           |    |  |  |  |  |

|   | 5.2                                                               | Metering calibration                                 |    |  |  |  |  |

| 6 | ATE mode1                                                         |                                                      |    |  |  |  |  |

|   | 6.1                                                               | Normal and ATE mode: differences                     |    |  |  |  |  |

|   | 6.2                                                               | Entering ATE mode                                    |    |  |  |  |  |

|   | 6.3                                                               | Autobaud feature14                                   |    |  |  |  |  |

|   | 6.4                                                               | NVM operations                                       |    |  |  |  |  |

|   | 6.5                                                               | NVM editor                                           |    |  |  |  |  |

|   |                                                                   | 6.5.1 How to change parameters                       | 16 |  |  |  |  |

| 7 | $E^2P$                                                            | operations                                           |    |  |  |  |  |

|   | 7.1                                                               | E²P dump                                             |    |  |  |  |  |

|   | 7.2                                                               | E²P patch and image upload/download                  |    |  |  |  |  |

|   |                                                                   | 7.2.1 Full E <sup>2</sup> P image operation box      | 18 |  |  |  |  |

|   |                                                                   | 7.2.2 Patch programming box                          | 18 |  |  |  |  |

|   | 7.3                                                               | E <sup>2</sup> P parameter editor                    |    |  |  |  |  |

| 8 | Add                                                               | ditional tools                                       |    |  |  |  |  |

|   | 8.1                                                               | PSU monitor                                          |    |  |  |  |  |

| 9 | PFC                                                               | C calibration                                        | 23 |  |  |  |  |

|   | 9.1                                                               | Principle                                            |    |  |  |  |  |

|                                      | 9.2     | PFC pro  | tection                         | . 23 |

|--------------------------------------|---------|----------|---------------------------------|------|

| 9.3 Step by step calibration example |         | Step by  | step calibration example        | . 24 |

|                                      |         | 9.3.1    | Tuning calibration tabs         | . 24 |

|                                      |         | 9.3.2    | Mode of operation               | . 25 |

|                                      |         | 9.3.3    | Step 1: THD improver            | . 26 |

|                                      |         | 9.3.4    | Step 2: delta pin calibration   | . 27 |

|                                      |         | 9.3.5    | Step 3: TSW test                | . 27 |

|                                      |         | 9.3.6    | Step 4: skipping area threshold | . 29 |

|                                      |         | 9.3.7    | Step 5: final verification      | . 30 |

|                                      | 9.4     | PFC par  | rameter update                  | . 31 |

| Rev                                  | ision h | istory . |                                 | .32  |

| List                                 | of tab  | les      |                                 | .35  |

| List                                 | of figu | ıres     |                                 | .36  |

# **List of tables**

| Table 1. | GUI setting parameters                     | . 7 |

|----------|--------------------------------------------|-----|

| Table 2. | GUI E <sup>2</sup> P parameter description | 10  |

| Table 3. | Differences between normal and ATE modes   | 13  |

| Table 4. | E <sup>2</sup> P mapping                   | 17  |

| Table 5. | PSU monitor: PFC/LLC features              | 22  |

| Table 6. | PFC parameters to be calibrated            | 23  |

| Table 7. | Document revision history                  | 32  |

UM3012 - Rev 1

# **List of figures**

| Figure 1.  | STSW-STNRG011GUI icon                                        | . 3 |

|------------|--------------------------------------------------------------|-----|

| Figure 2.  | STSW-STNRG011GUI startup screen                              | . 4 |

| Figure 3.  | COM port selection                                           | . 4 |

| Figure 4.  | Traces during GUI connection                                 | . 5 |

| Figure 5.  | SiLabs VCP in the [Device Manager]                           |     |

| Figure 6.  | [Settings] menu                                              |     |

| Figure 7.  | GUI metering information panel                               |     |

| Figure 8.  | GUI [PowerGraph] report                                      |     |

| Figure 9.  | GUI fault history                                            | . 9 |

| Figure 10. | GUI factory data panel                                       | 10  |

| Figure 11. | GUI power metering calibration window                        | 12  |

| Figure 12. | GUI: disable STNRG011 power messages                         | 13  |

| Figure 13. | ATE mode menu                                                | 13  |

| Figure 14. | ATE mode status bar                                          |     |

| Figure 15. | GUI error when trying to enter ATE mode while in normal mode | 14  |

| Figure 16. | GUI error when the VCC is applied                            |     |

| Figure 17. | Autobaud menu and results                                    | 15  |

| Figure 18. | NVM operation menu                                           | 15  |

| Figure 19. | NVM editor window                                            | 16  |

| Figure 20. | Parameter change                                             | 16  |

| Figure 21. | E <sup>2</sup> P access in the ATE mode error                | 17  |

| Figure 22. | E <sup>2</sup> P operation menu                              | 17  |

| Figure 23. | E²P dump tab                                                 |     |

| Figure 24. | E <sup>2</sup> P full import/export and patch operation tab  | 19  |

| Figure 25. | E <sup>2</sup> P parameter editor tab                        | 20  |

| Figure 26. | PSU monitor window                                           | 21  |

| Figure 27. | PFC protection warning window                                | 24  |

| Figure 28. | PFC tuning menu                                              | 24  |

| Figure 29. | Main PFC tuning tab                                          | 25  |

| Figure 30. | PFC tuning parameter tab                                     | 25  |

| Figure 31. | Manual mode: AC source voltage and DC load current selection |     |

| Figure 32. | NVM parameters: RAM and NVM values                           |     |

| Figure 33. | PFC tuning: THD improver tab                                 |     |

| Figure 34. | PFC tuning: delta pin calibration                            | 27  |

| Figure 35. | PFC tuning: determining TSW limits                           | 28  |

| Figure 36. | PFC tuning: PFC min./max. pin and DCM power                  | 28  |

| Figure 37. | PFC tuning: determining the skipping area threshold          |     |

| Figure 38. | PFC tuning: final verification without the skipping area tab |     |

| Figure 39. | PFC tuning: final verification                               |     |

| Figure 40. | PFC tuning: writing the NVM values                           | 31  |

### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics - All rights reserved

UM3012 - Rev 1 page 37/37