User manual

# Firmware for STM32F334xx microcontroller on STEVAL-DPSLLCK1 LLC full bridge converter with SR

#### Introduction

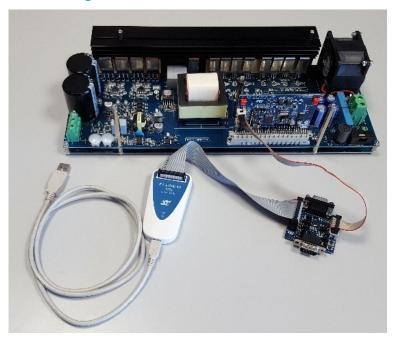

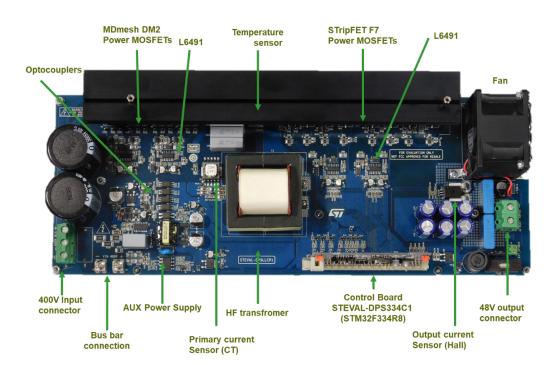

The STSW-DPSLLCK1 application firmware package for the STEVAL-DPSLLCK1 3 kW converter reference design helps developers evaluate and customize digital power design of LLC resonant converters and assess the performance of the STM32F334xx microcontroller in combination with featured power and analog components.

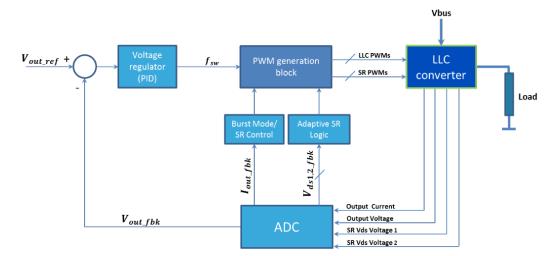

The firmware example implements the control algorithm and required protection functions for constant voltage mode operation. The STM32F334xx microcontroller with high resolution timer drives primary side power MOSFETs with 50% duty cycle PWM signals. An appropriate dead time for each leg is included to ensure zero voltage switching and avoid input voltage shoot-through. The PID voltage regulator running at 50 kHz provides the PWM switching period of primary side devices to change the voltage gain of the resonant tank and regulate the output voltage to the desired value.

The resonant tank is designed to always operate in the inductive region and then in soft switching for the entire frequency range. When the board is powered on, a switching period ramp-up at decreased frequency is performed to avoid current spikes. An adaptive synchronous rectification (A-SR) algorithm based on  $V_{DS}$  sensing is used to drive the secondary side power MOSFETs and reduce conduction losses. Burst mode operation is adopted at light loads to reduce losses due to circulating current and increase converter efficiency.

The control firmware also provides fast overcurrent protection, input and output under- and overvoltage protection, and overtemperature protection. An additional PWM signal is used to drive a cooling fan at a speed that depends on output load and heat-sink temperature.

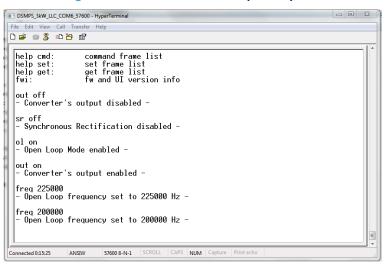

Finally, a basic user UART interface allows control of the main operating parameters of the converter and enable or disable control features such as open loop operation.

IAR embedded workbench for ARM is used to write, compile and debug the source code, but other toolchains can be used.

#### RELATED LINKS -

AN2450: LLC resonant half-bridge converter design guideline

AN2644: An introduction to LLC resonant half-bridge converter

AN4720: Half bridge resonant LLC converters and primary side MOSFET selection

UM2348: Getting started with the STEVAL-DPSLLCK1 evaluation kit for the 3 kW full bridge LLC digital power supply

## 1 Overview

# 1.1 Package content

The DSMPS 3kW - LLC STM32F334x firmware package contains the following folders:

- Documentation with compressed html and latex help files created by Doxygen

- Drivers with HAL, LL, CMSIS and BSP drives

- FullBridge\_LLC\_Project which contains a readme file, source files, linker configuration files (.icf), microcontroller startup file (.s) and IAR Embedded Workbench related files, such as the workspace file (.eww), project file (.ewp) and debugger setting file (.ewd)

Compiled files will be placed inside a folder named as the configuration used in the workspace (DSMPS Control Board STM32F334 by default).

## 1.2 Running FB LLC FW example

To run the DSMPS 3kW - LLC STM32F334x FW example, the workspace file (DSMPS Workspace.eww) should be opened with IAR Embedded Workbench v7.80 or higher.

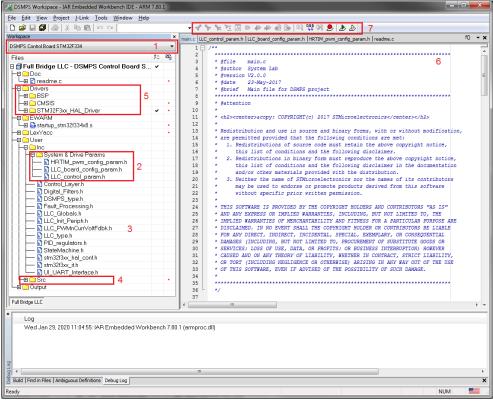

Figure 1. IAR Embedded Workbench window

- 1. Configuration setting

- 2. Main configuration files

- 3. Other included header files

- 4. Source files

- 5. Library files

- 6. Text editor

- 7. Compiling and debugging toolbar

UM2720 - Rev 2 page 2/54

The left side of the image shows the workspace and related files. The System & Drive Params folder contains the main user configuration files to enable or disable certain features.

The default configuration setting is DSMPS Control Board STM32F334, which is specific for the STEVAL-DPS334C1 control board used to run the power application. Other configurations for NUCLEO-F334R8 and 32F3348DISCOVERY boards are only useful for debug purposes as the pin-out and some MCU resources are different.

The firmware can be compiled and flashed using the indicated toolbar. To reprogram the board, you need to configure your preferred debugger tool (e.g., ST-LINK) in the IAR Embedded Workbench option menu by setting the SWD interface and connecting the adapter board.

#### - RELATED LINKS -

See UM2348: Getting started with the STEVAL-DPSLLCK1 evaluation kit for the 3 kW full bridge LLC digital power supply

#### 1.3 STM32Cube firmware

The STSW-DPSLLCK1 example uses STM32Cube HAL (Hardware Abstraction Layer) libraries to configure MCU peripherals. In some parts of the code, STM32Cube LL (Low Level) libraries are used for performance purposes. These LL drivers are built on the standard CMSIS library.

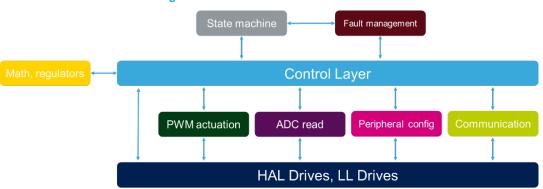

#### 1.4 FB LLC firmware architecture

The FB LLC firmware example includes all the software functions to configure microcontroller peripherals and execute the control algorithm. These functions are divided into different files and can be considered as part of a sub-block.

Basic sub-blocks use HAL and LL drivers in function definitions to modify MCU registers (e.g., PWM actuation, peripheral configuration, etc.). These functions can be easily rewritten or modified by the user for firmware customization. The control layer calls functions of basic sub-blocks to perform the control algorithm.

The state machine and fault management blocks are on top of the control layer.

Figure 2. FB LLC firmware architecture

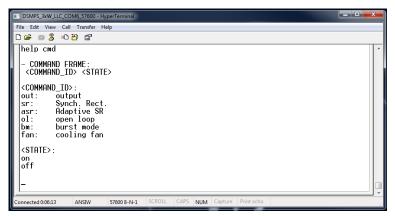

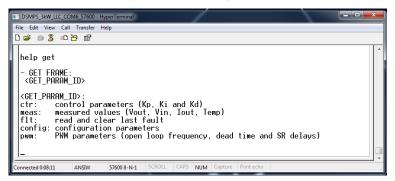

## 1.5 UI communication

The FB LLC firmware example can be executed without any communication interface, and the power conversion begins as soon as an input voltage within the defined range is detected.

A simple UART UI interface is available to enable some real-time functionality such as changing control parameters and detecting and clearing faults.

UM2720 - Rev 2 page 3/54

# 2 STEVAL DPSLLCK1 firmware application

## 2.1 File description

This section lists the most important source files of the FB LLC firmware application example. The same information is available in the readme file.

**LLC\_control\_prm.h**: this file contains the most important definitions the user can change to enable/disable some features and protections, as well as to modify PID default control parameters, task execution frequencies, thresholds used for SR and burst mode, switching frequency range (expressed in Hz), etc. Most of the possible customizations can be made by modifying this file.

**LLC\_board\_config\_param.h**: this file contains definitions of input/output ports, MCU resources and conversion factors of external sensors (Hall sensor, voltage dividers, temperature, etc.). If the solution is customized, this file should be modified accordingly.

**HRTIM\_pwm\_config\_param.h**: this file contains definitions used for HRTIM configuration such as clock frequency, pre-scaler value, maximum, minimum and default dead time value (expressed in ns), polarity of each HRTIM output (according to the driver used in power board), default burst mode duration, etc. All these parameters can be modified by the user. The file also contains the definitions of some macros used to convert time delays in an HRTIM tick number, and they should not be modified.

**DSMPS\_type.h**: contains type definition of variables used for a generic DSMPS control and not strictly related to LLC converter. These types include PID structure, State machine, LED configuration structure, driver pre-charge structure and fault error codes, as well as period and blinking number for LEDs for generic PFC and DC-DC topologies.

**LLC\_type.h**: this file extends type definitions of DSMPS\_type.h file with specific types used for the LLC converter. The DCDC\_MeasureStruct\_t type defines the structure of ADC acquisitions: the variable of this type (named DCDC\_MeasureStruct) is filled with the last ADC measurements for both regular and injected acquisitions. Other important definitions are the enumeration type of SR MOSFET leg (SR\_LEG1 and SR\_LEG2) and DCDC\_ConfigParamStruct\_t type which contains all parameters that can be modified on-the-fly by the user either via debugger or user interface.

**Control\_Layer.c** and **Control\_Layer.h**: contain definitions and prototypes of functions used at high level to enable/disable PWM outputs, enable/disable burst mode, enable/disable SR, execute voltage control loop, set PWM frequency in open loop mode, initialize control parameters, set or check a time delay, etc.

**LLC\_Globals.c** and **LLC\_Globals.h**: contain definitions and declarations of the main variables used for control algorithm and peripheral configuration (Handles). The main variables are: hPWMPeriod (PWM period in HRTIM tick number), hVout\_Reference (output voltage reference in 0 - 4095 range), PID\_Vout\_InitStructure (PID regulator structure with all coefficients, previous error and accumulator), DCDC\_MeasureStruct (which contains last sensed measurements from ADC channels), hPWMDeadTime (value of LLC PWM dead time in HRTIM DT ticks, it is used because dead time can be changed also on-the-fly), SR delays for fixed SR driving, counters used for time scheduling (wait time, start-up time, etc.), boolean variables used for protection enabling and DCDC\_ConfigParamStruct variable (of DCDC\_ConfigParamStruct\_t type), which stores all configuration parameters that can be changed on-the-fly by UART interface.

**PID\_regulators.c** and **PID\_regulators.h**: contain definitions and prototypes of PID regulators (both standard and extended controllers - refer to Section 2.5 PID regulator) and related functions. There are generic PID controllers with anti-windup and saturation features, and functions that can be used to change the proper PID field, such as coefficients, upper limit, lower limit, etc. The DCDC\_PID\_Init() function and its extended version are used to initialize PID structure with default values defined in LLC\_control\_param.h file.

**LLC\_Init\_Periph.c** and **LLC\_Init\_Periph.h**: contain definitions and prototypes of functions used to configure and initialize MCU peripherals like ADC, HRTIM, COMPs, DAC, etc. These functions may be modified for user purposes.

**Digital\_Filters.c** and **Digital\_Filters.h**: contain definitions and prototypes of functions used to perform digital filters. For LLC converter, only a simple low pass filter is used, which implements the formula: yk = y(k-1) - (y(k-1)>n) + (xk>n), where yk is the filter output at discrete time k, xk is the input at the same time, y(k-1) is the previous output and n is a shift value.

UM2720 - Rev 2 page 4/54

**StateMachine.c** and **StateMachine.h**: contain definitions and prototypes of functions used to perform the state machine and its related functions. STM\_StateMachineTask() function executes the state machine, other functions are used to modify the status of the state machine (DSMPS\_State variable) that is accessible only by get/set methods. Other private variables are bConverterEnabled, which identifies if the power conversion can start (its value depends on the default setting or communication commands) and bStartUpComplete flag, which is automatically set when the start-up procedure is completed correctly. In this file, functions related to LED driving (User LED or Fault LED) are also defined.

**LLC\_PWMnCurrVoltFdbk.c** and **LLC\_PWMnCurrVoltFdbk.h**: contain definitions and prototypes of functions used to change PWM switching frequency, to drive SR stage, update burst mode, change dead time, etc. Most of these functions are located in the CCM RAM memory, using #pragma instruction, to speed up their execution as they are called via a high frequency task to update HRTIM registers after control algorithm execution. Functions used to drive the fan with an auxiliary PWM and to get SR MOSFET Vds injected measurements are also present.

**Fault\_Processing.c** and **Fault\_Processing.h**: contain definitions and prototypes of functions used to check protections as well as HRTIM fault interrupt routine used for fast overcurrent protection and AWD interrupt for output overvoltage, if AWD is enabled.

**UI\_UART\_Interface.c** and **UI\_UART\_Interface.h**: contain definitions and prototypes of functions used for user UART communication. These functions include UART configuration, hardware initialization, UART receiving DMA interrupt and complete transfer callback. The scanning (the input stream conversion from characters to meaningful tokens) and the parsing (the interpretation of this tokens and the definition of related rules) are made thanks to lex and yacc files (lexter.l and parser.y) that, once properly compiled, generate lex.yy.c, y.tab.c and y.tab.h files (put inside LexYacc folder), which are recognized by the C program and used for string processing. **stm32f3xx\_hal\_conf.h**: the HAL configuration file. The use of a new HAL module is enabled by modifying this

stm32f3xx\_it.c and stm32f3xx\_it.h: contain definitions and prototypes of interrupt service routines. The interrupts configured relate to the scheduling of the control algorithm, the scheduling of low frequency tasks, SysTick and UI communication.

**stm32f3xx\_hal\_msp.c**: contains function definitions to configure hardware resources. These functions are called by HAL library functions used to configure MCU peripherals.

main.c: contains main() function that represents the starting point of the program. Inside the main(), after HAL initialization, all functions needed to configure the MCU (defined in Init\_Periph.c file) are called, according to the functionalities enabled in LLC\_control\_prm.h file. After peripheral configuration, CTR\_InitEnvironment(), defined in Control\_Layer.c, initializes main control variables, such as PID structure, configuration structure, filtered values, etc. Inside the while(1) loop, FLT\_FaultCheck(), STM\_StateMachineTask() and LED\_Task() functions are called. Interrupt service routines will interrupt this infinite loop when the corresponding event occurs.

## 2.2 Interrupt and tasks

Most control tasks are performed inside specific interrupt service routines, called with a fixed time scheduling or after an external event, and they have different priorities according to their function. The main control loop, synchronous rectification algorithm and frequency start-up are performed inside the TIM6 update interrupt service routine, set by default at 50 kHz. A lower frequency task is scheduled by the TIM16 update event, set at 100 Hz. Inside this interrupt routine, the calculation of low pass digital filter for input voltage and temperature measurements is performed, as well as the regulation of fan speed and the enabling/disabling of SR signals according to the load applied.

All interrupt routines are placed in stm32f3xx\_it.c file, except the HRTIM fault interrupt, which is placed in Fault\_processing.c file.

Task execution frequencies can be changed in LLC control param.c file:

```

/**** Voltage Control loop frequency ****/

```

```

#define VOLTAGE_CONTROL_LOOP_FREQ_HZ((uint32_t)50000)

/**< execution frequency of Vout control loop in Hz */</pre>

```

```

#define VOLTAGE_CONTROL_TIM_PRS ((uint16_t)0)

/**< prescaler of TIM that schedules Vout control loop */</pre>

```

UM2720 - Rev 2 page 5/54

/\*\*\*\* Temperature acquisition and fan control frequency \*\*\*\*/

```

#define LOW_FREQUENCY_TASK_FREQ_HZ ((uint16_t)100)

/**< execution of low frequency task in Hz: fan speed, SR turn-on/off, Vin and Temp

Filtering, update config params */</pre>

```

```

#define LOW_FREQUENCY_TASK_TIM_PRSC ((uint16_t)9999)

/**< prescaler of TIM that schedules execution of low frequency task in Hz: fan, SR enable/

disable, Vin, Temp Filtering and update config params */</pre>

```

Asynchronous tasks can be performed after an overcurrent or overvoltage detection (the last one if AWD is enabled; for further details, refer to Section 2.8 Faults and protections).

Also UI communication related functions are performed asynchronously when a new command is received. Finally, the timings of some slow procedures (start-up, wait time, output undervoltage validation time and LED blinking) are scheduled using some counters decreased inside the Systick interrupt routine (set at 1 ms).

| Task name                                                 | Priority          | Execution frequency                                   | Routine                        | Description                                                                                                                                                                                         |

|-----------------------------------------------------------|-------------------|-------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main control loop                                         | High              | 50 kHz                                                | TIM6 interrupt routine         | Voltage mode: PID regulator to calculate the switching period to control output voltage                                                                                                             |

| Frequency decrease                                        | High              | 50 kHz                                                | TIM6 interrupt routine         | Start-up procedure to decrease switching frequency linearly up to the reference value to avoid overcurrent. It is performed at start-up phase instead of the main control loop.                     |

| Synchronous<br>Rectification and light<br>load burst mode | High              | 50 kHz                                                | TIM6 interrupt routine         | Adapts turn-off PWM edges of SR MOSFETs to the internal diode conduction time. Enables/disables light load burst mode depending on the output current.                                              |

| Fan speed regulation and SR enable/ disable               | Medium            | 100 Hz                                                | TIM16<br>interrupt<br>routine  | SR enabling/disabling is made according to the load current, as well as the fan speed regulation.                                                                                                   |

| Slow protection checks                                    | Low               | -                                                     | Main loop                      | Compare measured values with high and low thresholds and manage state machine accordingly. Fault checked:  Input under/over voltage  Output under/over voltage  Overtemperature  Output overcurrent |

| Fast protection checks                                    | Very high<br>(HW) | Immediately after<br>COMP delay and<br>digital filter | HRTIM Fault interrupt routine  | Fast hardware protection and relative Irq handler. Fault checked: Resonant current overcurrent                                                                                                      |

| Serial communication                                      | Very low          | Asynchronous                                          | DMA interrupt on data received | Manages UART interface to change the main control parameters.                                                                                                                                       |

UM2720 - Rev 2 page 6/54

# 2.3 Control loop

The STSW-DPSLLCK1 firmware example configures the STM32F334 microcontroller on the control board of the STEVAL-DPSLLCK1 kit to drive both primary and secondary side MOSFETs to control the output voltage (Vo), starting from a constant input voltage (Vin).

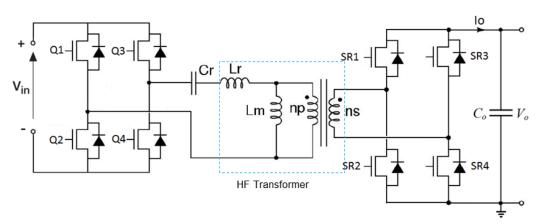

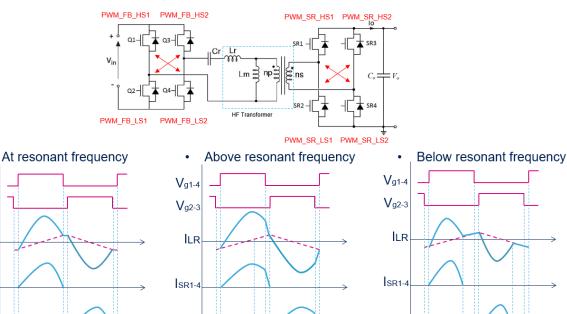

Figure 3. STEVAL-DPSLLCK1 topology

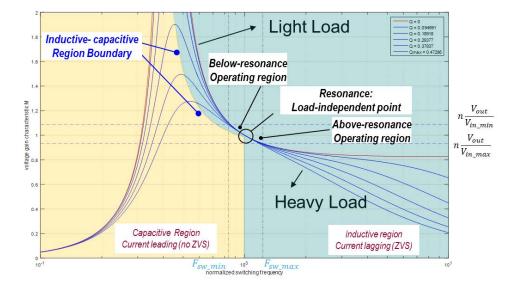

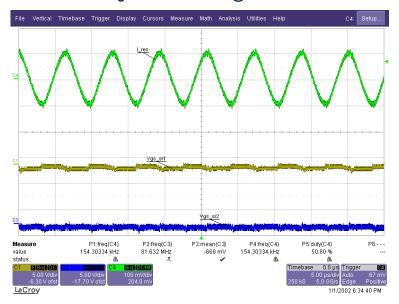

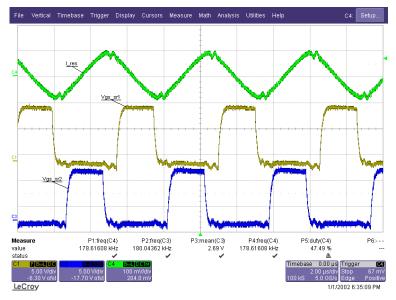

For this purpose, primary side high voltage power MOSFETs (Q1 to Q4) are driven two-by-two (Q1-Q4 and Q2-Q3) with 50% PWM duty cycle and an appropriate dead time. In this way, a square voltage waveform between –Vin and Vin is applied to the resonant tank (composed of Cr, Lr and Lm). According to resonant tank design, modifying the switching frequency can change the voltage gain and regulate the output voltage, making the converter always work in the inductive region and ensure ZVS operation, as shown below.

Figure 4. LLC voltage gain characteristic

UM2720 - Rev 2 page 7/54

Switching frequency is changed according to the feedback control loop, in which the Vout measurement is fed back and compared to the output voltage reference; the voltage error obtained is processed by a standard PID regulator, whose output represents the new switching period for PWM generation block (HRTIM). Control loop algorithm is executed at fixed frequency (50 kHz by default) and ensures a constant output voltage over the entire load range. The user could also modify the firmware to regulate the output current instead of the output voltage (i.e., for battery charger applications) feeding back the output current measurement (sensed by the isolated Hall sensors present in the board), keeping in mind that the PID parameters have to be changed accordingly.

The STM32F334 microcontroller also generates PWM driving signals for secondary side switches performing Synchronous Rectification to reduce conduction losses. Also in this case, power MOSFETs are driven two-by-two (SR1-SR4 and SR2-SR3) to perform the rectification of the transformer output voltage.

The Adaptive SR technique adapts driving signal duration to the conduction time of the power MOSFET body diode thanks to Vds voltage sensing of low side switches. At low load conditions, SR does not provide any benefits (switching losses are comparable or higher than reduction of conduction losses), so it is disabled if output current is lower than 5 A.

An LLC converter requires a small current needed to magnetize the transformer, even if no load is applied. For this reason, at very low load condition, burst mode is activated using a special feature of HRTIM; in this way some PWM pulses, inside a defined burst period, are skipped to reduce conduction losses.

Figure 5. Control loop block diagram

## - RELATED LINKS

AN2450: LLC resonant half-bridge converter design guideline AN2644: An introduction to LLC resonant half-bridge converter

## 2.4 State machine

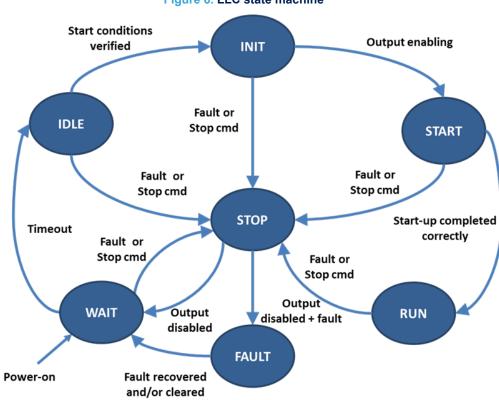

The STSW-DPSLLCK1 firmware package includes a state machine that manages the converter operation control. The tasks executed in the code and the functions that can be called depend on the state machine current state, which changes according to the previous state and if some conditions are verified.

UM2720 - Rev 2 page 8/54

Figure 6. LLC state machine

Table 2. State machine description

| State | Description                                                                                                                                                                                                                                                                                                                                                                      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT  | Persistent state where the application is intended to stay, for a defined wait time, after fault conditions disappear or at power-on. The following state is normally IDLE.                                                                                                                                                                                                      |

| IDLE  | Persistent state; the following state can be INIT if all the required conditions (input voltage and/or external command) are satisfied or STOP if there is a fault condition.                                                                                                                                                                                                    |

| INIT  | Pass-through state: the code is executed only once between IDLE and START states to initialize control variables and enable outputs. The following state is normally START but it can also be STOP if there is a fault condition. The system can remain in this state if the gate driver boot capacitor pre-charge, needed to supply HS power MOSFET by gate driver, is enabled. |

| START | Persistent state where the converter start-up is intended to be executed. The following state is normally RUN as soon as start-up procedure is completed correctly. The following state is STOP if there is a fault condition.                                                                                                                                                   |

| RUN   | Persistent state where the converter is running normally. The following state is STOP if there is a fault condition or a stop command is received.                                                                                                                                                                                                                               |

| STOP  | Pass-through state where PWMs are disabled. The following state is FAULT if a fault stops the converter, WAIT otherwise (external command received).                                                                                                                                                                                                                             |

| FAULT | Persistent state after a fault. The following state is normally WAIT until faults are cleared or recovered (not all faults can be recovered without a system reset).                                                                                                                                                                                                             |

The control board status LED (blue) indicates the state machine state:

- OFF in all the states in which PWMs are disabled

- IDLE when the LED blinks slowly and indefinitely

- INIT and START when the LED blinks quickly

- ON in RUN state

UM2720 - Rev 2 page 9/54

## 2.5 PID regulator

The Proportional, Integral and Derivative (PID) regulator is used to eliminate the error between output voltage and its reference.

The PID regulator output defines the counter overflow value to be set in the HRTIM peripheral (PER register), according to the clock frequency (and then resolution) selected, and it represents the new switching period after the next update event.

In time domain, the PID regulator output is given by the following equation:

$$r(t) = K_p \times \epsilon(t) + K_i \times \int_0^t \epsilon(t) \, dt + K_d \times \frac{d}{dt} \epsilon(t) \tag{1}$$

#### Where:

- r(t) is the regulator output at time t

- ε(t) is error of the system at time t

- K<sub>p</sub> is the proportional coefficient

- K<sub>i</sub> is the integral coefficient

- K<sub>d</sub> is the derivative coefficient

For a digital control loop performed at a fixed frequency (i.e., in discrete time domain), the equation becomes:

$$r\bigg(t_k\bigg) = K_p \times \epsilon\bigg(t_k\bigg) + K_i \times \sum_{j=0}^k \epsilon(t_j) \cdot T_s + K_d \times \frac{\epsilon(t_k) - \epsilon(t_k-1)}{T_s} \tag{2}$$

#### Where:

- r(t<sub>k</sub>) is the regulator output at discrete time t<sub>k</sub>

- ε(t<sub>k</sub>) is the error of the system at discrete time t<sub>k</sub>

- T<sub>s</sub> is the sampling time (control period)

To reduce CPU load, the sampling time is directly part of the integral coefficient, thus avoiding an extra multiplication and division in the previous equation.

As an accumulative term, the integral part is used in the algorithm: increasing the loop time decreases its effect (accumulation is slower and the integral action on the output is delayed). Inversely, decreasing the loop time increases its effect (accumulation is faster and the integral action on the output is increased). Therefore the sampling time (i.e., control frequency) has to be adjusted before changing PID coefficients.

In theory, the higher the sampling rate, the better the regulation. In practice, the following consideration must be made:

- CPU load increases accordingly

- There is no need for a sampling time lower than the refresh rate of external sensors

- PID is a linear regulator, thus for a resonant converter like LLC in which switching frequency is the control

variable, performing the algorithm at variable frequency (e.g., switching frequency or its sub-multiple) could

generate unexpected results, unless updating T<sub>s</sub>, and then K<sub>i</sub> and K<sub>d</sub> at each control loop, needlessly

increasing the CPU load

- Resonant converters can switch at very high frequency (several hundreds of kHz), whereas controlled variables (output DC voltage and DC current) have a relatively slower dynamic, so there is no need to control at switching frequency and the CPU load would in any case be unacceptable

For the above reasons, a 50 kHz control frequency has been chosen for this application for good regulation performance.

UM2720 - Rev 2 page 10/54

The PID regulator function is implemented in PID\_regulators.c file and it has the same structure as the regulator used in STM32 motor control SDK. The output of this regulator is a signed 16-bit variable (int16\_t), so it is in range:  $[-(2^{15}-1); 2^{15}-1]$ , as one of the bits is used to indicate the sign. In the LLC application, the output of the regulator represents the new overflow value for HRTIM counter, which is an unsigned 16-bit variable (uint16\_t) in range  $[0; 2^{16}-1]$ . For this reason, according to the pre-scaler set in HRTIM clock configuration and minimum switching frequency chosen, a signed 16-bit variable might be not enough. For example, if the maximum resolution (HRTIM clock frequency set at 4.608e9 Hz) is adopted, the minimum switching frequency given when HRTIM\_PER is set at its maximum value (0xFFDF = 65503, according to the reference manual) which is around 70.3 kHz, but the standard regulator, whose output can reach  $(2^{15}-1)=32767$  maximum, cannot guarantee this minimum frequency. For this reason and to avoid losing resolution (setting a pre-scaler greater than necessary), an extended version of PID regulator with a 32-bit output is provided in the same source file together with all the related functions.

To enable/disable the extended PID calculation, keeping in mind the maximum output required according to minimum switching frequency and HRTIM clock frequency, the relevant definition in LLC\_control\_param.h file is uncommented (default) or commented accordingly:

```

#define USE EXTENDED PID

```

It is also possible to disable differential term calculation, for both standard and extended PID regulators, commenting the following lines in the PID\_regulators.h file:

```

#define DIFFERENTIAL_TERM_ENABLED

#define DIFFERENTIAL_TERM_ENABLED_EX

```

The definitions of regulator coefficients and their divider (integer calculation has been adopted, divisors should be a power of two to speed-up code execution), are placed in LLC\_control\_param.h file.

```

/*-----/

/******************

#define PID_VOUT_KP_DEFAULT ((int16_t)3000)

/**< default Kp value of PI regulator */

```

```

#define PID_VOUT_KI_DEFAULT ((int16_t)1000)

/**< default Ki value of PI regulator */</pre>

```

```

#define PID_VOUT_KD_DEFAULT ((int16_t)1000)

/**< default Kd value of PI regulator - if used */</pre>

```

```

#define PID_VOUT_INTEGRAL_UPPER_LIMIT (PID_VOUT_UPPER_LIMIT * VOUT_KIDIV2)

/**<upper limit of integral term of PI regulator */

```

```

#define PID_VOUT_INTEGRAL_LOWER_LIMIT (PID_VOUT_LOWER_LIMIT * VOUT_KIDIV2)

/**<lower limit of integral term of PI regulator */</pre>

```

```

#define PID_VOUT_UPPER_LIMIT(HRTIM_MAX_PWM_PERIOD)

/**< output upper limit of PI regulator */</pre>

```

```

#define PID_VOUT_LOWER_LIMIT(HRTIM_MIN_PWM_PERIOD)

/**< output lower limit of PI regulator */

```

```

#define VOUT_KPDIV2 ((uint16_t)(256))

/**< default Kp divider value of PI regulator */

```

UM2720 - Rev 2 page 11/54

```

#define VOUT_KIDIV2 ((uint16_t)(4096))

/**< default Ki divider value of PI regulator */

// Vout PID parameter dividers

#define VOUT_KDDIV2 ((uint16_t)(2048))

/**< default Kd divider value of PI regulator - if used */</pre>

```

Regulator parameters can also be changed via UART interface or acting directly on DCDC\_ConfigParamStruct variable via debugger (and setting the bConfigurationChanged field to TRUE to update the changes).

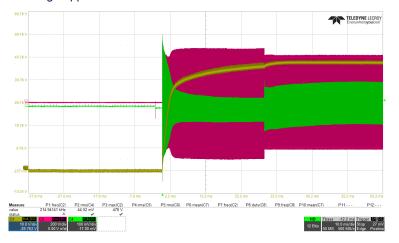

## 2.6 Start-up procedure

One of the most critical processes in the control of LLC converter is the start-up procedure. At converter turn-on, a large current spike due to the discharged magnetizing inductance of the transformer can occur if the procedure is not well controlled. A common practice consists in forcing a low voltage gain at the beginning, that is to turn on devices with a high switching frequency, usually 2 or 2.5 times the resonant frequency, while also ensuring the operation remains in the inductive region.

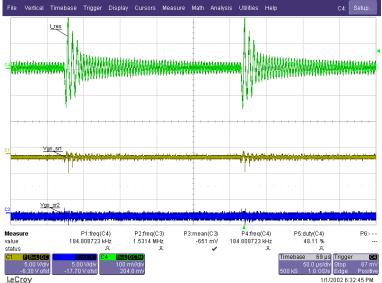

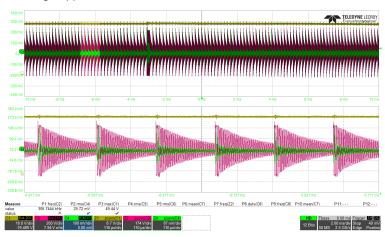

Initially, the control loop is disabled and the switching frequency is set high (380 kHz) and decreased over 500 ms to the minimum value (120 kHz). When the output voltage reaches the desired value of 46 V, the control loop is closed and the switches are driven with the frequency given by PID regulator. To avoid discontinuity when the loop is closed, the integral term of PID regulator is set equal to the corresponding value of last PWM frequency. When the regulation is ongoing, switching frequency can change over a smaller operating range (120 to 250 kHz).

The output threshold at which the control loop is closed is defined in the StateMachine.c file:

```

#define VOUT_MIN_CLOSED_LOOP OUT_VOLT_ADC_VALUE(46)

/**< minimum voltage in [V] to close the control loop during the start-up phase */</pre>

```

Maximum, minimum and start-up frequencies are defined in LLC\_control\_param.h file:

```

#define HRTIM_MAX_PWM_FREQ_START_UP_HZ 380000

/**< maximum frequency in Hz of PWM signals at the beginning of start-up procedure */</pre>

```

```

#define HRTIM_MIN_PWM_FREQ_START_UP_HZ 120000

/**< minimum frequency in Hz of PWM signals at the end of start-up procedure for closed loop operation if the control loop is not closed before */

```

```

#define HRTIM_MAX_PWM_FREQ_HZ 250000

/**< maximum frequency in Hz of PWM signals during closed loop regulation */

```

```

#define HRTIM_MIN_PWM_FREQ_HZ 120000

/**< minimum frequency in Hz of PWM signals during closed loop regulation

- WARNING: if f_min < 140626 Hz, extended PID must be used because period_max > S16_MAX */

```

In the same file, the time duration of start-up procedure is also defined:

```

#define DSMPS_STARTUP_TIME_DURATION_mS((uint16_t)500)

/**< duration in ms of DSMPS_START state*/</pre>

```

If this start-up time is elapsed without reaching the target value (e.g., if there is a short on the output), the start-up fault is triggered and the system is put in safe state.

The start-up procedure can be disabled by commenting the following line in in LLC\_control\_param.h file:

```

#define FREQUENCY_RAMP_UP

/**< if defined a a frequency start-up is performed in START state*/</pre>

```

UM2720 - Rev 2 page 12/54

If defined, frequency start-up is also performed in open loop mode. In this case, the initial switching frequency is always defined by HRTIM\_MAX\_PWM\_FREQ\_START\_UP\_HZ (380 kHz) and scales down to HRTIM\_MAX\_PWM\_FREQ\_HZ (250 kHz), which is both the maximum and default switching frequency in open loop mode. After start-up, it is possible to change open loop switching frequency.

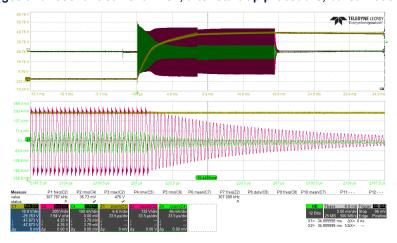

#### 2.7 Burst mode

The STSW-DPSLLCK1 application firmware package implements two different burst modes: the first one is related only to output voltage and is triggered when its value rises above a certain threshold during fast load transients. When this event is detected, PWM outputs are temporarily disabled until output voltage falls down to a second threshold. During the turn-off period, the control loop is disabled to avoid saturation of the accumulator (integral part of PID regulator). The burst mode threshold is set at a value lower than output overvoltage protection value and is defined, together with the re-activation threshold, in the Fault\_Processing.c file:

```

/* Burst mode on bus voltage thresholds */

```

```

#define OUT_VOLTAGE_BURST_MODE_TH_H OUT_VOLT_ADC_VALUE(50)

/**< max voltage for burst mode activation [V] */</pre>

```

```

#define OUT_VOLTAGE_BURST_MODE_TH_L OUT_VOLT_ADC_VALUE(47)

/**< min voltage for burst mode de-activation [V] */</pre>

```

The second burst mode type is the light load burst mode, a common procedure in resonant converters.

The burst mode is implemented through a special feature of the HRTIM, setting burst idle and period duration, both expressed in number of PWM periods (refer to STM32F334 reference manual for further information).

Default light load burst mode parameters are defined in LLC\_control\_param.h file:

```

/*-- Burst Mode control -----*/

```

```

#define BURST_MODE_IDLE_DURATION_RANGE1 36

/**< if defined LIGHT_LOAD_BURST_MODE, BURST_MODE_IDLE_DURATION_RANGE1 + 1

is the number of HRTIM periods that compose the burst idle duration

when the burst mode is active and output current is in range1 */</pre>

```

```

#define BURST_MODE_PERIOD_RANGE1 39

/**< if defined LIGHT_LOAD_BURST_MODE, BURST_MODE_PERIOD_RANGE1 +1 is the

number of HRTIM periods that compose the burst period (idle+ run) when

the burst mode is active and output current is in range 1 */</pre>

```

Default burst idle duration is 36, whereas the default burst period is 39, this means that inside a burst period of 40 PWM cycles, 37 cycles are skipped and only 3 cycles are active (run duration).

Light load burst mode is enabled when output current goes below 0.8 A and disabled when the current goes above 1.3 A. More than one burst mode range can be defined according to output current measurements and desired active pulses, but only the first range is active by default.

Both burst modes are enabled by default, but they can be disabled by commenting the following lines in LLC control param.h file:

```

#define OUT_VOLTAGE_BURST_MODE

/**< if defined PWM signals are stopped if output voltage goes above

defined thresholds and re-enabled with hysteresys */</pre>

```

```

#define LIGHT_LOAD_BURST_MODE

/**< if defined PWM signals are in burst for light loads */</pre>

```

UM2720 - Rev 2 page 13/54

## 2.8 Faults and protections

The STSW-DPSLLCK1 application firmware package includes several protection functions that can be enabled or disabled by the user in LLC control param.h file uncommenting or commenting the corresponding line:

```

#define OVERCURRENT_PROTECTION

#define OUT_OVERCURRENT_PROTECTION

#define OVERTEMPERATURE_PROTECTION

#define INPUT_UNDER_OVER_VOLTAGE_PROTECTION

//#define VOUT_ANALOG_WATCHDOG_ENABLED

#define VOUT_UNDERVOLTAGE_PROTECTION

#define START_UP_FAILED_ENABLED

```

Each fault is identified by an error code defined in the DSMPS\_type.c file. These codes present an "1" in a different bit position: in this way, the fault variable (DCDC\_System\_Fault, defined in the Fault\_Processing.c file) is given by the logic OR operation of codes corresponding to all faults occurred. Some of these faults will be automatically cleared once the fault condition disappears (like input undervoltage), then the fault variable is updated by setting at "0" the corresponding bit. Other faults are not recoverable by choice, even if this setting (recoverable or not) can be modified by commenting the corresponding line in the Fault\_Processing.c file:

```

#define OVER_TEMP_FAULT_NOT_RECOVERABLE

/**< if defined the over-temperature fault is not recoverable (the board must be powered

off) */</pre>

```

```

#define OVER_VOLTAGE_OUT_FAULT_NOT_RECOVERABLE

/**< if defined the output over-voltage fault is not recoverable (the board must be powered

off) */</pre>

```

However, overcurrent and output overcurrent protections are always not recoverable and they require either a system reset to be cleared, or a request by the communication interface.

Once a fault occurred, the system is put in STOP state and then in FAULT state, after disabling outputs, while the last fault occurred is stored in the DCDC\_Last\_System\_Fault variable. The fault can be detected either via UI, reading the variable (during debugging), or by the blinking fault LED (red) on the control board. Only the first detected fault is signalled by LED blinking according to a different number of blinks and a different timing for each type of fault. The blinking sequence is then repeated after a pause given by the following definition in the DSMPS type.h file:

```

#define LED_BLINK_REPETITION_PERIOD_MS 3000

/**< repetition period in ms between a blinking series and the next one */</pre>

```

The fault LED blinks with a 50% duty (ON and OFF) with a duration that can be short or long according to the following definitions:

```

#define LED_BLINK_PERIOD_LONG_MS 500

/**< LED on/off long period in ms */</pre>

```

```

#define LED_BLINK_PERIOD_SHORT_MS 250

/**< LED on/off short period in ms */</pre>

```

By default, slow blinks are related to voltage errors (input and output undervoltage and overvoltage), whereas the fast blinks are related to other errors (overcurrent, overtemperature, etc.).

UM2720 - Rev 2 page 14/54

The following table shows the different blinking configurations for each fault.

Table 3. Fault description

| Error name                                | Code   | Condition                                      | Number of<br>LED Blinks | Blinking<br>speed | Recoverable |

|-------------------------------------------|--------|------------------------------------------------|-------------------------|-------------------|-------------|

| DCDC_NO_ERROR                             | 0x0000 | -                                              | -                       | -                 | -           |

| DCDC_OUT_OVER_VOLT_ERROR                  | 0x0001 | Vout > 56 V                                    | 3                       | slow              | N           |

| DCDC_OUT_UNDER_VOLT_ERROR                 | 0x0002 | Vout < 35 V                                    | 2                       | slow              | N           |

| DCDC_IN_OVER_VOLT_ERROR                   | 0x0004 | Vin > 435 V                                    | 4                       | slow              | Υ           |

| DCDC_IN_UNDER_VOLT_ERROR                  | 0x0008 | Vin < 370 V                                    | 5                       | slow              | Υ           |

| DCDC_OVER_CURRENT_ERROR                   | 0x0010 | Ires > Ires_max                                | 2                       | fast              | N           |

| DCDC_OUT_OVER_CURRENT_ERROR               | 0x0020 | lout > 63 A                                    | 3                       | fast              | N           |

| DCDC_OVER_TEMP_ERROR                      | 0x0040 | T > 55 °C                                      | 4                       | fast              | N           |

| DCDC_STARTUP_FAILED_ERROR                 | 0x0080 | Vout < 47 V && Tramp > 500 ms                  | 6                       | slow              | N           |

| DCDC_PRIMARY_SIDE_ERROR (from PFC if any) | 0x0100 | Error sent by UART communication (not enabled) | 5                       | fast              | Y           |

| DCDC_COMMUNICATION_ERROR                  | 0xE000 | UI UART communication failed (not enabled)     | 6                       | fast              | Y           |

UM2720 - Rev 2 page 15/54

Thresholds and hysteresis for each fault are defined in the Fault\_Processing.c file:

/\* - Fault and burst mode thresholds - for nominal values see LLC\_Control\_Parameters.h file - \*/ /\* Out Voltage thresholds \*/

```

#define OUT VOLTAGE MAX H OUT VOLT ADC VALUE(56)

/**< max voltage for output overvoltage fault detection [V]

- if VOUT_ANALOG_WATCHDOG_ENABLED is not defined, otherwise

the WDG threshold is WDG OUT VOLTAGE MAX in LLC Init Perif.c file ^{\star}/

#define OUT VOLTAGE HYSTERESIS OUT VOLT ADC VALUE(4)

/**< hysteresis for output under/over voltage fault detection [V] */

#define OUT_VOLTAGE_MAX_L (OUT_VOLTAGE_MAX_H - OUT_VOLTAGE_HYSTERESIS)

/**< min voltage for output overvoltage fault cancellation [V] */

#define OUT VOLTAGE MIN L OUT VOLT ADC VALUE (35)

/**< min voltage for output undervoltage fault detection [V] */

#define OUT_VOLTAGE_MIN_H (OUT_VOLTAGE_MIN_L + OUT_VOLTAGE_HYSTERESIS)

/**< max voltage for output undervoltage fault cancellation [V] */

/* Input Voltage thresholds */

#define IN VOLTAGE MAX H IN VOLT ADC VALUE(435)

/**< max voltage for input overvoltage fault detection [V] */

#define IN VOLTAGE_HYSTERESIS IN_VOLT_ADC_VALUE(12)

/**< hysteresis for input under/over voltage fault detection [V] */

#define IN VOLTAGE MAX L (IN VOLTAGE MAX H - IN VOLTAGE HYSTERESIS)

/**< min voltage for input overvoltage fault cancellation [V] */

#define IN VOLTAGE MIN L IN VOLT ADC VALUE(360)

/**< min voltage for input undervoltage fault detection [V] */ \,

#define IN VOLTAGE MIN H (IN VOLTAGE MIN L + IN VOLTAGE HYSTERESIS)

/**< max voltage for input undervoltage fault cancellation [V] */

/* Burst mode on bus voltage thresholds */

#define OUT VOLTAGE BURST MODE TH H OUT VOLT ADC VALUE(50)

/**< max voltage for burst mode activation [V] */

#define OUT_VOLTAGE_BURST_MODE_TH_L OUT_VOLT_ADC_VALUE(47)

/**< min voltage for burst mode de-activation [V] */

/* Temperature thresholds */

#define TEMPERATURE TH H ((uint16 t)55)

/**< max temperature for over-temperature fault detection (higher threshold) [°C] */

#define TEMPERATURE HYSTERESIS ((uint16 t)5)

/**< hysteresis for over-temperature fault detection [°C] */

#define TEMPERATURE TH L (TEMPERATURE TH H - TEMPERATURE HYSTERESIS)

/**< min temperature for over-temperature fault cancellation [°C] */

/* Out current threshold */

#define OUT CURRENT MAX HALL IC AMP2ADC VALUE(62)

```

UM2720 - Rev 2 page 16/54

All fault checks are performed in FLT\_FaultCheck() function, except for fast overcurrent protection and AWD (if enabled), which is called inside the while(1) loop in the main.

Overcurrent protection is a based on resonant current sensed signal. The resonant current is sensed by a current transformer (CT) and then rectified by small signal fast diodes; the signal is sent to the MCU and then compared by an internal comparator to a fixed threshold set on a DAC channel. If the sensed signal rises above the defined threshold, the HRTIM fault is triggered. This means that PWM outputs are automatically put in a safe state by the hardware and HRTIM1\_FLT\_IRQHandler interrupt routine is also called to assert the corresponding fault, put the state machine in STOP state and then in FAULT state. Moreover, the fault event is filtered by a digital filter set in HRTIM\_config() function to prevent false triggers due to commutation noise. The overcurrent threshold, expressed in 12-bit format, is defined in the LLC control param.h file:

```

#define DAC OVERCURRENT COMP THRESHOLD ((uint16 t) 3850)

```

This protection may be triggered when a very large load change is applied.

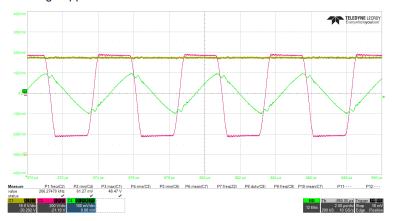

#### 2.9 PWM modulation

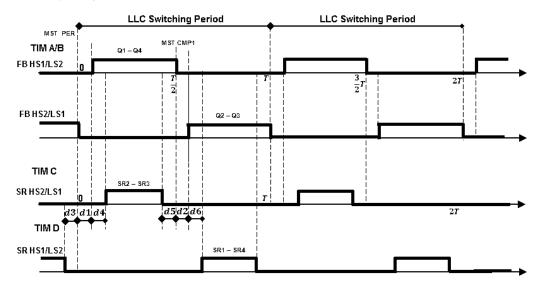

To generate PWM driving signals and trigger ADC acquisitions, the high resolution timer has been used. HRTIM has a modular architecture with several timer units (master timer and Timer A to Timer E) and different external events available; this allows the generation of complex control signals to address most power conversion topologies (for further information, refer to RM0364). To drive both primary side and secondary side switches, different timers have to be synchronized; for this purpose, Timer A and Timer B are used to drive high voltage power MOSFETs, whereas Timer C and Timer D are used to drive SR power MOSFETs and the master timer is used for synchronization and ADC trigger generation.

The primary side switches are driven by a 50% duty cycle and a proper dead time defined in the HRTIM\_pwm\_config\_param.h file, automatically kept constant by the peripheral even if switching frequency changes, unless the user changes it during operation.

The HRTIM half mode, specifically designed for resonant converters, allows the duty cycle to be automatically forced to a half period value when a new period is programmed. By writing HRTIM\_PERxR register, Compare 1 value (HRTIM\_CMP1xR) is automatically updated to the HRTIM\_PERxR/2 value. Even if primary side MOSFETs are logically driven two-by-two (LS1 with HS2 and HS1 with LS2), four HRTIM outputs are used as the gate drivers placed in the power board require an inverted polarity for low side signal; the polarity of each PWM output can be changed in the HRTIM\_pwm\_config\_param.h file:

```

/* -- PWM out polarity */

```

#define HRTIM\_PWM\_FB\_HIGHSIDE\_OUTPOLARITY HRTIM\_OUTPUTPOLARITY\_HIGH

#define HRTIM\_PWM\_FB\_LOWSIDE\_OUTPOLARITY HRTIM\_OUTPUTPOLARITY\_LOW

#define HRTIM\_PWM\_SR\_HIGHSIDE\_OUTPOLARITY HRTIM\_OUTPUTPOLARITY\_HIGH

#define HRTIM PWM SR LOWSIDE OUTPOLARITY HRTIM OUTPUTPOLARITY LOW

In the same way, to drive SR power MOSFETs, four different PWM outputs (defined in the LLC board config param.h file) have been used.

UM2720 - Rev 2 page 17/54

Whereas the driving of high voltage switches requires only the update of the period register, low voltage power MOSFETs are not driven by a 50% duty cycle, then two compare registers (for rising and falling edges) have to be written for each waveform, according to SR control logic. The transformer output voltage is rectified by output stage. Instead of using diodes, the rectification is performed by SR power MOSFETs that are turned on when the corresponding body diode is forward biased, considering also safe delays, as shown in the figure below.

Figure 7. PWM signals timing

- d1: dead time rising FB

- · d2: dead time falling FB

- d3: SR delay falling2

- d4: SR delay rising1

- d5: SR delay falling1

- d6: SR delay rising2

In the above figure, d1 and d2 are the dead times (rising and falling of primary side power MOSFETs. Rising and falling dead times are equal and their default value is defined in HRTIM\_pwm\_config\_param.h

```

/* -- Dead time calculation ------ */

```

```

#define DEAD_TIME_RISING_NS ((uint16_t)600)

/**< initial or default dead time of rising edge in ns */</pre>

```

```

#define DEAD_TIME_FALLING_NS ((uint16_t)600)

/**< initial or default dead time of falling edge in ns */</pre>

```

```

#define DEAD_TIME_MAX_NS ((uint16_t)800)

/**< max dead time for both rising and falling edges in ns */</pre>

```

```

#define DEAD_TIME_MIN_NS ((uint16_t)200)

/**< min dead time for both rising and falling edges in ns */</pre>

```

The same file also defines allowable minimum and maximum values for saturation limits if the dead time is changed during operation (avoiding cross-conduction.

Delays d3 to d6 represent SR safe delays with respect to primary side waveforms: delay rising1, delay rising2, delay falling 1 and delay falling 2. Rising delays are always fixed, falling delays can change if adaptive SR is enabled, otherwise they are also fixed.

Default, minimum and maximum values for SR delays are defined in the LLC control param.h file.

UM2720 - Rev 2 page 18/54

```

/* -- Synchronous Rectification min values -- */

#define SYNCH RECT DELAY RISING1 MIN NS ((int16 t)0)

/**< min delay in ns between FB PWM and SR1 PWM rising edges in ns

- only for adaptive SR and on-fly delay setting */

#define SYNCH RECT DELAY RISING2 MIN NS ((int16 t)0)

/**< min delay in ns between FB PWM and SR2 PWM rising edges in ns

- only for adaptive SR and on-fly delay setting */

#define SYNCH RECT DELAY FALLING1 MIN NS ((int16 t)50)

/**< min delay in ns between FB PWM and SR1 PWM falling edges in ns

- only for an adaptive SR */

#define SYNCH RECT DELAY FALLING2 MIN NS ((int16 t)50)

/**< min delay in ns between FB PWM and SR2 PWM falling edges in ns

- only for an adaptive SR WARNING: Consider that auto-delayed Compare is only valid from the

capture up to the period event (RM pag 633) ^{\star}/

/* -- Synchronous Rectification max values -- */

#define SYNCH_RECT_DELAY_RISING1_MAX_NS ((int16_t)600)

/**< max delay in ns between FB PWM and SR1 PWM rising edges in ns

- only for an adaptive SR */

#define SYNCH RECT DELAY FALLING1 MAX NS ((int16 t)600)

/**< max delay in ns between FB PWM and SR1 PWM rising edges in ns

- only for an adaptive SR */

#define SYNCH RECT DELAY RISING2 MAX NS ((int16 t)600)

/**< max delay in ns between FB PWM and SR2 PWM rising edges in ns

- only for an adaptive SR */

#define SYNCH RECT DELAY FALLING2 MAX NS ((int16 t)600)

/**< max delay in ns between FB PWM and SR2 PWM rising edges in ns

- only for an adaptive SR */

/* -- Synchronous Rectification init values -- */

#define SYNCH RECT DELAY RISING1 INIT NS ((int16 t)(250))

/**< init rising delay for SR1 in ns */

#define SYNCH_RECT_DELAY_FALLING1_INIT_NS SYNCH_RECT_DELAY_FALLING1_MAX_NS

/**< init falling delay for SR1 in ns */

#define SYNCH RECT DELAY RISING2 INIT NS ((int16 t)(250))

/**< init rising delay for SR2 in ns */

#define SYNCH RECT DELAY FALLING2 INIT NS SYNCH RECT DELAY FALLING2 MAX NS

/**< init falling delay for SR2 in ns */

The user should be careful when changing these values to avoid power MOSFET cross-conduction and to avoid

```

If adaptive SR is enabled, SR power MOSFET turn-off can occur either on a HRTIM compare event or on a comparator trigger (with its proper blanking time).

remain permanently ON or OFF.

loosing some SR PWM edges. If a calculated value for a compare register, which depends on both fixed dead time and SR delays, is greater than actual PWM period (given by control loop), the SR power MOSFETs will

UM2720 - Rev 2 page 19/54

|                                     | •                                  | ·                                                               |  |  |

|-------------------------------------|------------------------------------|-----------------------------------------------------------------|--|--|

| Signal                              | Edge                               | Register/Event                                                  |  |  |

| FB HS1/LS2                          | RISING                             | TIMA_PER (TIMB_PER), dead time rising is automatically inserted |  |  |

| 1 B 113 1/L32                       | FALLING                            | TIMA_CMP1 (TIMB_CMP1), automatically written in half mode       |  |  |

| FB HS2/LS1 (complementary waveform) | RISING                             | TIMA_CMP1 (TIMB_CMP1), dead time falling automatically inserted |  |  |

|                                     | FALLING                            | TIMA_PER (TIMB_PER)                                             |  |  |

|                                     | RISING                             | TIMC_CMP2                                                       |  |  |

| SR HS2/LS1                          | FALLING                            | TIMC_CMP1 or COMP2 event (Adaptive SR)                          |  |  |

|                                     | BLANKING TURN-OFF<br>(ADAPTIVE SR) | TIMC_CMP3                                                       |  |  |

|                                     | RISING                             | TIMD_CMP2                                                       |  |  |

| SR HS1/LS2                          | FALLING                            | TIMD_CMP1 or COMP4 event (Adaptive SR)                          |  |  |

|                                     | BLANKING TURN-OFF<br>(ADAPTIVE SR) | TIMD_CMP3                                                       |  |  |

Table 4. Registers and events used for PWM generation

Each register is updated with the values shown in the following table.

Register Value TIMA\_PER (TIMB\_PER) last PWM switching period (Ts) given by control loop TIMC\_CMP2 Dead time rising (d1) + SR delay rising1 (d4) TIMC\_CMP1 Ts/2 - SR delay falling1 (d5) TIMC\_CMP3 TIMC\_CMP2 + blanking window duration TIMD\_CMP2 Ts/2 + dead time falling (d2) + SR delay rising2 (d6) TIMD CMP1 Ts - SR delay falling2 (d3) TIMD\_CMP3 TIMD\_CMP2 + blanking window duration

Table 5. Values for register update

When the control loop provides a new switching period, HRTIM registers have to be updated. To prevent mismatches, the update of used timers is disabled until all registers are written, so they are all active together at next counter roll-over event as pre-load is enabled. Different functions are defined in LLC\_PWMnCurrVoltFdbk.c to update registers used to drive primary side power MOSFETs, secondary side power MOSFETs, or all together.

# 2.10 ADC acquisitions and triggers

Several ADC acquisitions are necessary to perform output regulation and enable protection features. Both ADC1 and ADC2 are used to acquire analog signals: output voltage, input voltage, output current and temperature (voltage across a NTC resistor). These acquisitions are divided into two different regular sequences triggered by the HRTIM master timer (Compare 2 and Compare 3 registers) to avoid commutation noise. Conversion results are then transferred by two DMA channels to DCDC\_MeasureStruct variable, whose type is defined in the LLC\_type.h file. If adaptive SR is enabled, two injected measurements (one for each ADC peripheral) of SR Vds voltages are also performed after a specified delay from SR MOSFETs turn-off. These measurements are used by the adaptive SR algorithm.

ADC trigger delays for both regular and injected conversions are defined in the LLC\_control\_param.h file:

UM2720 - Rev 2 page 20/54

```

/*-- ADC trigger point -----*/

#define ADCx_REGULAR_TRIGGER_POINT_NS ((uint16_t) (1300 + DEAD_TIME_RISING_NS))

/**< ADCx regular aquisition trigger point in ns respect to the beginning of HRTIM period (rollover event) */

#define ADCy_REGULAR_TRIGGER_POINT_NS ((uint16_t) (500 + DEAD_TIME_FALLING_NS))

/**< ADCy regular aquisition trigger point in ns respect to half HRTIM period */

#define ADCx_INJECTED_TRIGGER_POINT_NS ((uint16_t) (250))

/**< ADCx injected aquisition trigger point in ns after PWM SR1 turn-off */

#define ADCy_INJECTED_TRIGGER_POINT_NS ((uint16_t) (250))

/**< ADCy injected aquisition trigger point in ns after PWM SR2 turn-off */</pre>

```

## 2.11 Synchronous rectification

In several power conversion systems, such as AC-DC and DC-DC converters, the output diode (or diodes) rectifier can be replaced by a power MOSFETs, driven by a control logic, to improve the converter efficiency through a technique called synchronous rectification (SR). Thanks to SR, conduction losses are significantly reduced as the output current flows through the power MOSFETs channel instead of the rectification diode; the power loss is then decreased from:

$$P_{loss\_diode} = V_d \cdot I_{out}$$

to:

$$P_{loss\_MOSFET} = R_{ds\_on} \cdot I_{out}^2$$

where  $R_{ds}$  on is very low for SR power MOSFETs.

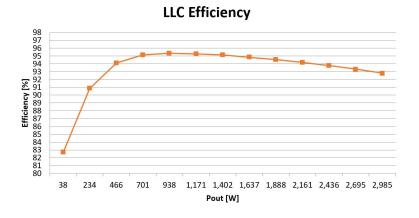

The power converter works even when the SR power MOSFETs are not driven because the rectification is naturally performed by the internal body diode, but suffers worse performance, whereas driving the power MOSFETs when the body diode is forward biased, the system efficiency can increase by 3% - 4%.

A digital implementation of the synchronous rectification allows a reduction in the number of components, introduces more flexibility in control algorithm design and guarantees a higher tolerance to noises.

In LLC topology, the conduction time of SR devices depends on operating frequency and is related to primary side driving signals. If the LLC converter works below the main resonant frequency, but still in the inductive region, SR devices conduct for less than half the PWM period because resonant current reaches magnetizing current before the end of switching semi-period, so conduction time should be adapted.

UM2720 - Rev 2 page 21/54

$V_{g2-3}$

ILR

SR1-4

SR2-3

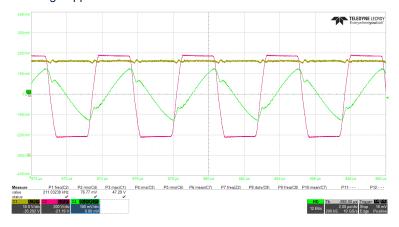

The figure below shows the conduction time of rectification devices according to switching frequency at resonant frequency, above the resonance and below the resonance.

ISR2-3

Figure 8. LLC: Conduction of SR devices

In the STSW-DPSLLCK1 application firmware package, there are two independent signals (managed by TIMC and TIMD, respectively) for each diagonal of the rectification stage, and the SR driving can be either with fixed delays (with respect to primary side signals) or adaptive ones. In the second case, SR rising delays are fixed and set at 250 ns to avoid MOSFETs turning on too early when body diodes can shortly conduct for capacitive currents. However, falling delays can be automatically tuned according to body diode conduction time, which is detected by acquiring the Vds voltage across low side SR MOSFETs.

ISR2-3

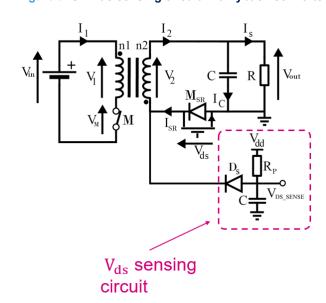

The sensing network consists of a fast Schotthky diode and a pull-up resistor connected to the MCU supply voltage, as shown in the figure below.

Figure 9. SR Vds sensing circuit in a flyback converter

UM2720 - Rev 2 page 22/54

It is important that this sensing network is applied only to low side power MOSFETs, whose source is connected to the microcontroller same ground. When the SR power MOSFET drain voltage is above the MCU supply voltage Vdd, the Schotthky diode is reverse biased and the sensed voltage is pulled up to Vdd. When drain voltage is below Vdd, the Schotthky diode is forward biased and the sensed voltage is equal to this voltage plus the diode voltage drop, generating a positive shift. The current during positive biasing is limited by the pull-up resistor and the diode voltage drop depends on this current. When the body diode is conducting, Vds becomes negative (forward biased diode), but when power MOSFET conducts Vds=Rds on\*I out.

A safe dead time should be inserted before the turn-on and after the turn-off in which body diode conducts.

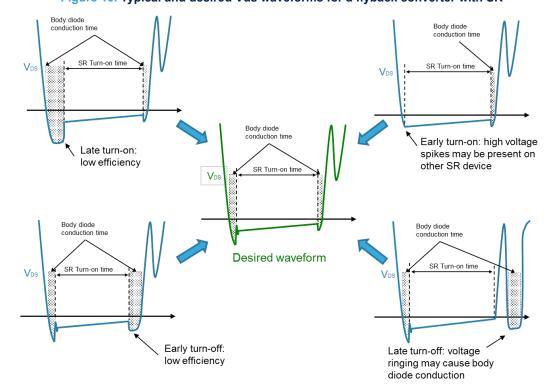

Figure 10. Typical and desired Vds waveforms for a flyback converter with SR

Adaptive SR technique optimizes dead times. If the generated PWM signal is turned-off too early, a positive current causes body diode conduction that lowers converter efficiency, so part of SR benefits are lost. If the PWM is turned-off too late, the power MOSFET is forced to conduct even if the diode is reverse biased, which can damage the power MOSFETs and cause its failure. Moreover, after the power MOSFETs turn-off, a voltage ringing of the Vds can force the body diode to conduct again, impacting efficiency.

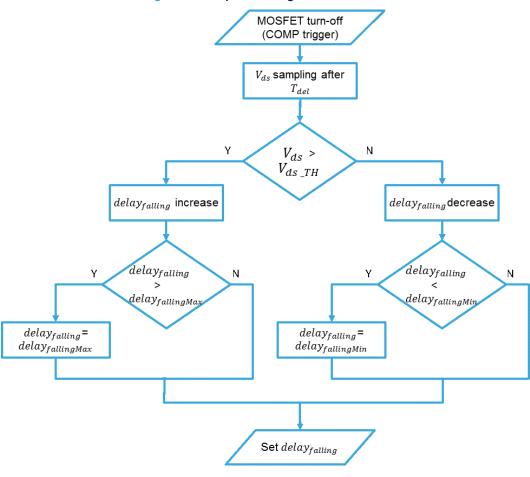

In the firmware package, early or late turn-off of SR MOSFET is detected using injected ADC acquisition after power MOSFET turn-off and the pulse duration is adjusted according to an ST patented adaptive algorithm. The ADC trigger is given by the HRTIM TIMC (and TIMD for the second SR diagonal) and Compare 4 register is set to autodelayed mode from Compare 1 register (which gives the power MOSFETs turn-off). This adds a fixed delay to a compare event or an external event, like the COMP trigger used as a second turn-off mechanism.

The autodelayed mode is a special feature of HRTIM. If the acquired value is below a preset threshold, the power MOSFET body diode is still conducting and the PWM is turned-off too early as the voltage drop on the power MOSFET is equal to the forward voltage of body diode (Figure 10 at the bottom-left). The conduction time can be increased (falling delay decreased) by a fixed quantity.

If the acquired value is above the preset threshold, the power MOSFET is forced to conduct even with a reverse current because the PWM is turned-off too late due to the fact that a small safe interval in which the diode conducts (little notch in Vds waveform) is not present and the Vds rises quickly (Figure 10 at the bottom-right). In this case, the conduction time can be decreased (falling delay increased) by a fixed quantity to turn off the power MOSFET earlier.

The sampling delay from PWM turn-off also provides the time duration of this safe body diode conduction interval. The adaptive algorithm flow chart is shown below, taking into consideration also the saturation limits.

UM2720 - Rev 2 page 23/54

Figure 11. Adaptive SR algorithm flowchart

In practice, to speed reaching the steady state, two couples of thresholds, with different incremental values, are defined in the LLC\_control\_param.h file:

```

/* -- Adaptive SR incremental/decremental values -- */

```

```

#define ADAPTIVE_SYNCH_RECT_INCREMENTAL_DELAY1_NS ((int16_t)2)

/**< incremental falling delay1 for adaptive SR in ns */</pre>

```

```

#define ADAPTIVE_SYNCH_RECT_INCREMENTAL_DELAY2_NS ((int16_t)5)

/**< incremental falling delay2 for adaptive SR in ns */</pre>

```

```

#define ADAPTIVE_SYNCH_RECT_DECREMENTAL_DELAY_NS ((int16_t)2)

/**< decremental falling delay for adaptive SR in ns */</pre>

```

UM2720 - Rev 2 page 24/54

```

/* -- Adaptive SR thresholds values */

#define ADAPTIVE_SYNCH_RECT_INCREMENTAL_VDS1_TH1_mV ((uint16_t)1000)

/**<ADC Vds1 threshold1 in mV to increase/decrease falling delay in adaptive SR ^*/

#define ADAPTIVE_SYNCH_RECT_INCREMENTAL_VDS1 TH2 mV ((uint16 t)1200)

/**< ADC Vds1 threshold2 in mV to increase falling delay in adaptive SR ^{\star}/

#define ADAPTIVE SYNCH RECT INCREMENTAL VDS2 TH1 mV ((uint16 t)750)

/**< ADC Vds2 threshold1 in mV to increase/decrease falling delay in adaptive SR */

#define ADAPTIVE_SYNCH_RECT_INCREMENTAL_VDS2_TH2_mV ((uint16 t)850)

/**< ADC Vds2 threshold2 in mV to increase falling delay in adaptive SR */

The calculation of the new delays is performed in the CTR_AdaptiveSynchRectEdgeCalculation() function called

inside the control loop interrupt routine.

To prevent current inversion, MOSFET turn-off can also be triggered by internal comparators (one for each SR

diagonal) whose thresholds are set in specific DAC channels and defined in the LLC control param.h file:

/*-- Turn-off COMP thresholds for adaptive SR -----*/

#define DAC_SR1_TURN_OFF_COMP_THRESHOLD_mV ((uint16_t) 900)

/**< COMP Vds1 threshold in mV on DAC to shut-down PWM in adaptive SR */

#define DAC SR2 TURN OFF COMP THRESHOLD mV ((uint16 t) 800)

/**< COMP Vds2 threshold in mV on DAC to shut-down PWM in adaptive SR */

To avoid a false trigger of the internal comparator, due to commutation noise at MOSFET turn-on, a blanking

window is inserted to prevent an early turn-off and ensure a minimum on-time. The blanking window duration is

defined in the LLC_control_param.h file:

/*-- Blanking window duration for COMP turn-off in adaptive SR ------*/

```

/\*-- Blanking window duration for COMP turn-off in adaptive SR -----\*/

#define SYNCH RECT TURN OFF BLANKING WINDOW NS ((int16 t)700)

#define SYNCH\_RECT\_TURN\_OFF\_BLANKING\_WINDOW\_NS ((int16\_t)700)

/\*\*< minimum turn-on time for SR1/SR2 signlas for adaptive SR in ns \*/</pre>

UM2720 - Rev 2 page 25/54

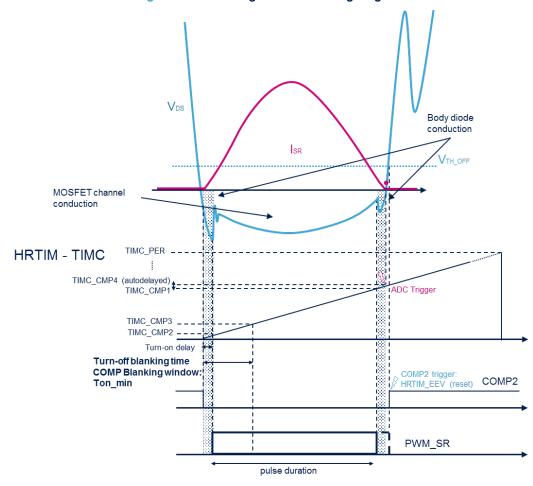

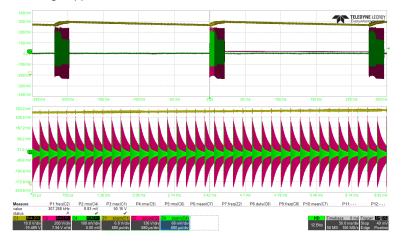

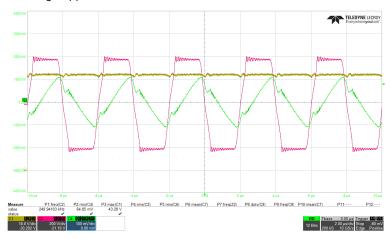

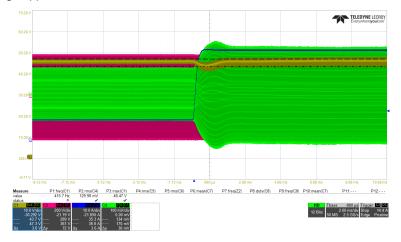

The timing diagram for SR PWM generation for one diagonal is shown in the figure below.

Figure 12. SR PWM generation: timing diagram

The above image shows how pulse generation starts after a delay given by the TIMC\_CMP2 register, then the Vds rings due to MOSFET turn-on, but it is not immediately turned-off by the comparator trigger (threshold in dotted blue line along the top) because the threshold is high and TIMC\_CMP3 ensures a minimum on-time (blanking window). TIMC\_CMP1 gives the MOSFET turn-off, after 250 ns (TIMC\_CMP4 in autodelayed mode from TIMC\_CMP1) the ADC injected acquisition of Vds is triggered (the purple point on top) to perform adaptive SR. In this case, COMP has not been triggered since it is used as a protection system to guarantee MOSFET turn-off.

## – RELATED LINKS -

AN2450: LLC resonant half-bridge converter design guideline AN2644: An introduction to LLC resonant half-bridge converter

## 2.12 Fan driving

The power board cooling fan is supplied by a DC voltage, which, according to the jumper setting and power MOSFET driving, can be the 48 V output voltage, a lower voltage derived from it, or an external voltage.

If J4 jumper is disconnected, an external supply voltage can be directly applied to the fan using J5 connector. Otherwise, if J4 is connected, it is possible to reduce the 48 V applied to the fan by modulating the PWM signal driving the Q13 power MOSFET of the dedicated step-down converter.

The fan rotation speed is proportional to the voltage applied to it and therefore to the duty cycle of the PWM that drives the power MOSFET.

UM2720 - Rev 2 page 26/54

In low frequency tasks, the duty cycle of the PWM used to drive the power MOSFET is adjusted according to the load and the heat-sink temperature: if the temperature is above the higher threshold, the maximum duty cycle is applied, otherwise the duty cycle is proportional to the load.

Temperature and current thresholds, PWM frequency, and minimum and maximum duty cycle values are defined in the LLC\_control\_param.h file:

```

/*-- PWM parameter for FAN control -----*/

#define FAN PWM FREQUENCY 10000

/* PWM Frequency in Hz - min 367 Hz with prescaler = 2 - see FAN TIM Config() */

#define FAN PWM INIT DUTY FAN PWM DUTY LOW SPEED

/**< init duty cycle for fan control */

/**< low speed duty cycle for fan control */

#define FAN PWM DUTY HIGH SPEED ((uint16 t)((97*FAN PWM TIM PERIOD)/100))

/**< high speed duty cycle for fan control */

#define FAN TEMPERATURE THRESHOLD H 43

/**< temperature high threshold (for hysteresis): if temperature is above the threshold, the

fan is driven at high speed, otherwise the speed depends on the load (if FAN PWM DRIVING is

defined) */

#define FAN TEMPERATURE THRESHOLD L 38

/**< temperature low threshold (for hysteresis): if temperature is above the threshold, the

fan is driven at high speed, otherwise the speed depends on the load (if FAN PWM DRIVING is

defined) */

#define FAN HIGH LOAD THRESHOLD HALL IC AMP2ADC VALUE(40)

/**<output current threshold to activate max duty cycle for fan */

#define FAN LOW LOAD THRESHOLD HALL IC AMP2ADC VALUE(6)

/**<output current threshold to activate min duty cycle for fan */

```

## 2.13 Open loop mode and debugging

The STSW-DPSLLCK1 application firmware package can be customized for debugging purposes, both acting at compilation time and when the application is running.

To change the converter default behavior by enabling or disabling certain features, the LLC\_control\_param.h can be modified accordingly.

At board power-up, the default setting for power conversion starts as soon as an input voltage in the correct range is detected after the WAIT state timeout has elapsed, without waiting for a user command (by UI, or debugger). Initially, only low side power MOSFETs are turned-on to pre-charge driver bootstrap capacitors, and the soft-start routine sets the initial switching frequency quite high but it gradually decreases. To disable the start-up features, the following lines can be commented.

```

/* Start-up -----*/

#define START_WITHOUT_COMMAND

/**< if defined the power conversion starts without any command if there is no error,

otherwise a command from UI or debugger is needed */

#define FREQUENCY_RAMP_UP

/**< if defined a frequency start-up is performed in START state */

```

UM2720 - Rev 2 page 27/54

```

#define GATE_DRIVER_BOOTSTRAP_PRECHARGE

/**< if defined the bootstrap capacitors are precharged closing low side switches for a

defined time duration */</pre>

```

Other driving functions, such as synchronous rectification (both adaptive and with fixed delays), fan driving and burst mode, can be removed by commenting the following lines:

/\* Protections and burst modes -----\*/

```

#define OUT_VOLTAGE_BURST_MODE

/**< if defined PWM signals are stopped if output voltage goes above defined thresholds and

re-enabled with hysteresis */</pre>

```

```

#define LIGHT_LOAD_BURST_MODE

/**< if defined PWM signals are in burst for light loads */

/* Additional driving -----*/</pre>

```

```

#define SYNCH_RECTIFICATION

/**< if defined synchronous rectification is enabled to reduce conduction losses

- PWMs depend on hSR_DelayRising1-2 and hSR_DelayFalling1-2 variables */</pre>

```

```

#define ADAPTIVE_SYNCH_RECTIFICATION

**< if defined synchronous rectification is enabled to reduce conduction losses

- PWMs depend on COMP outputs and turn-off is adapted respect to VDS sensing /

- it must be define together with SYNCH_RECTIFICATION */</pre>

```

```

#define FAN_PWM_DRIVING

/**< if defined the FAN is driven by PWM, otherwise the FAN is driven as a GPIO */</pre>

```

These features can alternatively be disabled at the beginning (but can be enabled again by the user according to the following settings:

```

/* initial state of additional driving and burst if defined */

```

```

#define SYNCH_RECTIFICATION_INIT_ENABLED

/**< if defined synchronous rectification is initially enabled, the set can be changed

runtime */</pre>

```

```

#define ADAPTIVE_SYNCH_RECTIFICATION_INIT_ENABLED

/**< if defined adaptive synchronous rectification (with adaptive turn-off) is initially

enabled, the set can be changed runtime */</pre>

```

```

#define LIGHT_LOAD_BURST_MODE_INIT_ENABLED

/**< if defined, together with LIGHT_LOAD_BURST_MODE, burst mode is set for low load

condition */</pre>

```

The open loop mode consists in setting a constant switching frequency without any output regulation. In this case, output undervoltage protection is automatically disabled as the voltage gain, given by resonant tank at the specified switching frequency, may not be enough to ensure an output voltage greater than the protection threshold. The user should be careful about limiting the output voltage (i.e., connecting an electronic load set in voltage mode) even if the output overvoltage protection is kept enabled.

To enable the open loop mode, the corresponding line can be uncommented.

UM2720 - Rev 2 page 28/54

```

/* Debug -----*/

//#define OPEN_LOOP_MODE

/**< if defined SR delays and PWM frequency are initially set via

debugger or communication (operation mode can be changed runtime)

- OPEN LOOP operation, WARNING: output voltage MUST be clamped @48V */

```

The open loop enable setting can be changed, as well as the other configurations, via the debugger through the variable DCDC ConfigParamStruct. This structure variable type is defined in the LLC type.h file:

```

* @brief Configuration Param Struct

typedef struct

bool bConverterEnabled;

bool bOpenLoopEnabled;

bool bSREnabled;

bool bAdaptiveSREnabled;

bool bBurstModeEnabled;

bool bFanPWMDrivingEnabled;

uint32_t wOpenLoopFreq_Hz;

uint16_t hDeadTimeFullBridge ns;

int16 t hFixedSRDelayRising1 ns;

int16 t hFixedSRDelayFalling1 ns;

int16 t hFixedSRDelayRising2 ns;

int16 t hFixedSRDelayFalling2 ns;

int16 t hRegulatorKpGain;

int16 t hRegulatorKiGain;

int16 t hRegulatorKdGain;

bool bConfigurationChanged;

} DCDC ConfigParamStruct t;

```

Each boolean setting can be changed by assigning a TRUE or FALSE value to the corresponding variable.

The open loop switching frequency, expressed in Hz, can also be changed by modifying wOpenLoopFreq\_Hz field in the range ([120000; 250000] Hz). In the same way, dead time and SR fixed delays (expressed in ns and with the limits defined in LLC\_control\_param.h and HRTIM\_pwm\_config\_param.h files) can be modified, as well as regulator gains.

When the configuration is changed, the bConfigurationChanged field has to be set to TRUE to load new values into the low frequency task and become effective.

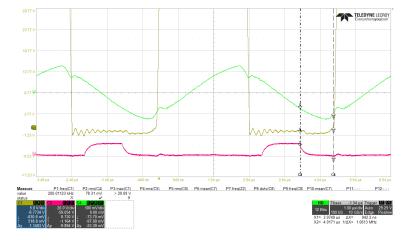

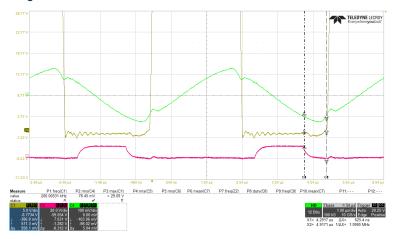

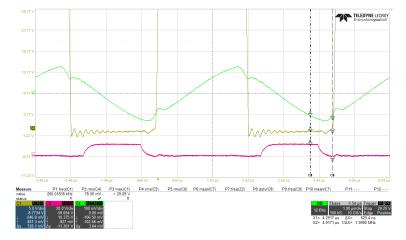

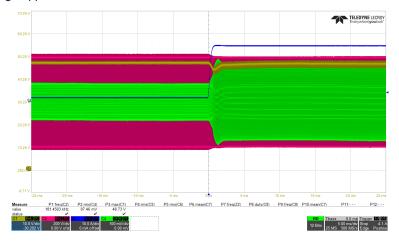

#### Example