Driving SiC MOSFETs with unipolar gate voltage

Theory and experimental data on 1200 V Gen3

## Advancements in SiC MOSFET turn-off driving: From negative bias to 0 V

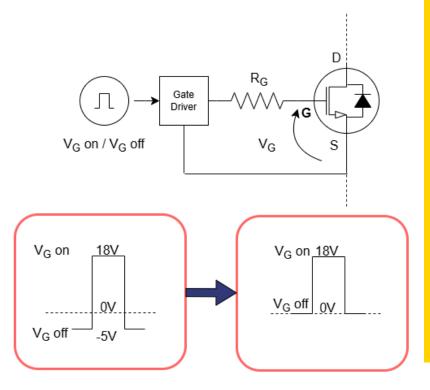

We test the differences between unipolar (Vgs-on, Vgs-off: 18V, 0V) and bipolar (18V, -5V) gate driving strategies on a SiC MOSFET

**SiC MOSFETs** are finding increasing application in high power converters due to better electrical, mechanical, and thermal performances than traditional Si MOSFETs and IGBT.

The most common automotive and industrial power converters are based on simple legs that are combined to form more complex topologies. Historically, a negative bias for driving turn-off of SiC MOSFETs was a standard recommendation for hard-switched half-bridge based topologies.

This is manly to avoid the very famous Miller turn-on effect (known also as parasitic turn-on) and any undesired spurious turn-on events.

**OV turn-off** offers design advantages in terms of simplifying the transition from silicon to SiC, and allowing easier driving circuits that can save space in highly space-constrained applications.

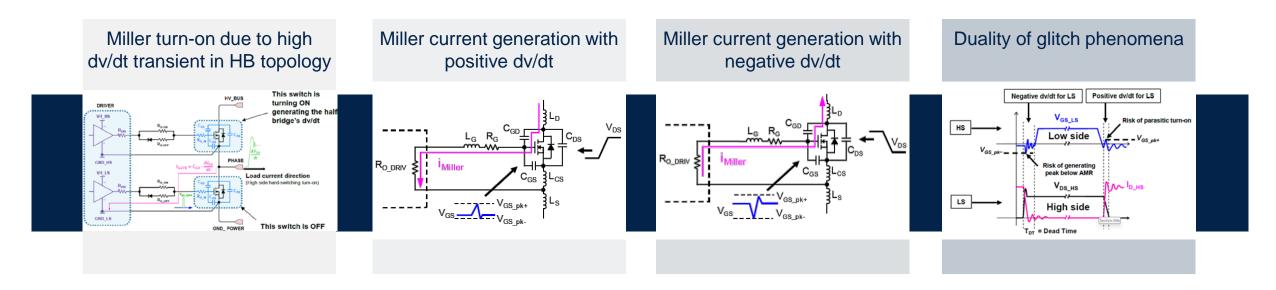

### Miller turn-on effect during transitions

In power converters, minimizing the undesired Miller turn-on effect is crucial for enhancing efficiency and reducing power losses

One effective strategy is to use a negative gate-source voltage Vgs-off during turn-off. This approach helps to mitigate the effects of ringing and overshoot, which can otherwise lead to unintended turn-on due to the Miller effect.

### K elements in Miller turn on phenomenon

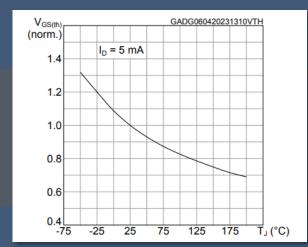

Vgs(th) threshold voltage is the minimum gate-to-source voltage to create a conducting path between MOSFET source & drain terminals

### Normalized gate threshold voltage vs. temperature

| Symbol               | Parameter                       | Test conditions                                      | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------------|------------------------------------------------------|------|------|------|------|

| V <sub>(BR)DSS</sub> | Drain-source breakdown voltage  | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 1 mA         | 1200 |      |      | V    |

| I <sub>DSS</sub>     | Zero gate voltage drain current | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 1200 V      |      |      | 10   | μΑ   |

| I <sub>GSS</sub>     | Gate-body leakage current       | V <sub>DS</sub> = 0 V, V <sub>GS</sub> = -10 to 22 V |      |      | ±100 | nA   |

| V <sub>GS(th)</sub>  | Gate threshold voltage          | $V_{DS} = V_{GS}$ , $I_D = 5$ mA                     | 1.8  | 3.0  | 4.2  | V    |

#### Room temperature testing:

The threshold voltage is tested at room temperature during production to ensure that the devices meet the specified minimum threshold voltage.

#### **Temperature effects:**

Vgs(th) tends to decrease at higher temperatures, although this parameter is not typically measured during production. This behavior must be considered in applications where devices operate at elevated temperatures.

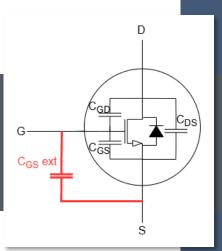

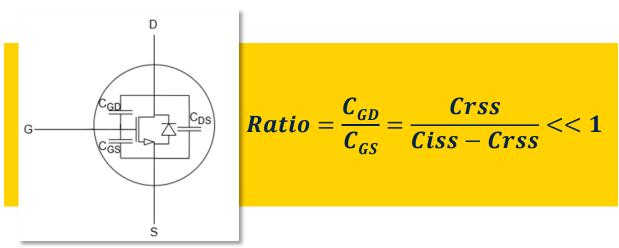

### Why the capacitance ratio is important

### Parasitic capacitance can lead to undesired energy storage and release during switching, causing delays or unwanted oscillations

| Symbol           | Parameter                    | Test conditions                                           | Min. | Тур. | Max. | Unit |

|------------------|------------------------------|-----------------------------------------------------------|------|------|------|------|

| C <sub>iss</sub> | Input capacitance            |                                                           | -    | 1990 | 1-2  | pF   |

| Coss             | Output capacitance           | V <sub>DS</sub> = 800 V, f = 1 MHz, V <sub>GS</sub> = 0 V | H    | 102  |      | pF   |

| C <sub>rss</sub> | Reverse transfer capacitance |                                                           | 2    | 12   | -    | pF   |

A lower capacitance ratio in a device can reduce susceptibility to the false turn-on phenomenon. This means that the device is less likely to experience unintended turn-on events during switching, which can lead to additional power losses.

To improve device performance and reliability, it is crucial to manage parasitic capacitance carefully. This might involve optimizing the device design, selecting appropriate materials, and using external components to dampen unwanted effects.

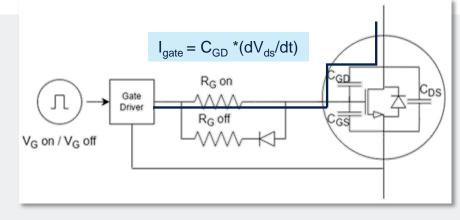

### Miller turn-on mitigation in MOSFETs

### The designer can find a list of the most important key elements which allows optimizing performance

- Gate resistance: select a gate resistance such that the ratio is Rgon/Rgoff ≥ 1.5. This ensures faster turn-off compared to turn-on, reducing the risk of Miller turn-on.

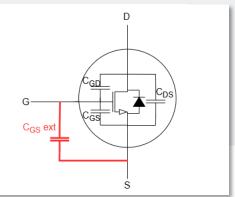

- External capacitance (Cgs-ext): add an external capacitance between the gate and source. A few nF can be enough to improve performance and reduce Vgs spikes.

- Active Miller clamp: use a gate driver with an active Miller clamp to prevent the gate voltage from rising due to the Miller effect during switching.

- PCB layout: optimize the PCB layout to minimize stray inductances, which can exacerbate the Miller effect.

- Miller capacitance ratio: choose MOSFETs with a gate-drain to gate-source capacitance ratio (Cgd/Cgs) as low as possible (much less than 1). This helps reduce the Miller effect.

- Threshold voltage (Vgs(th)): threshold voltage is key and the worst-case condition must be considered for appropriate design robustness.

- **Driving network**: optimize the network according to the design boundary conditions.

### Measurement results V<sub>gsoff</sub> = 0 V

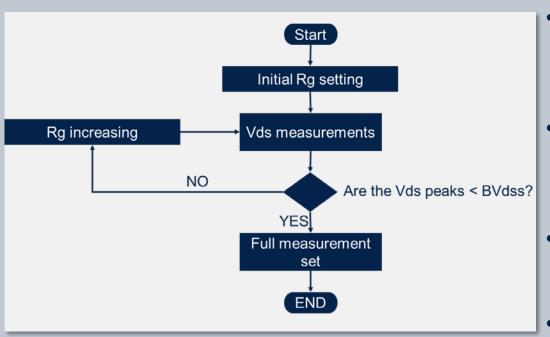

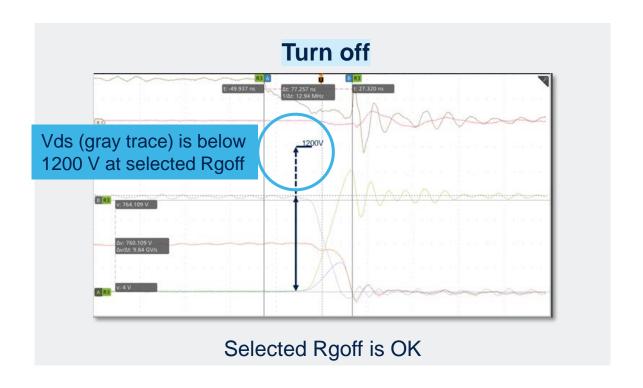

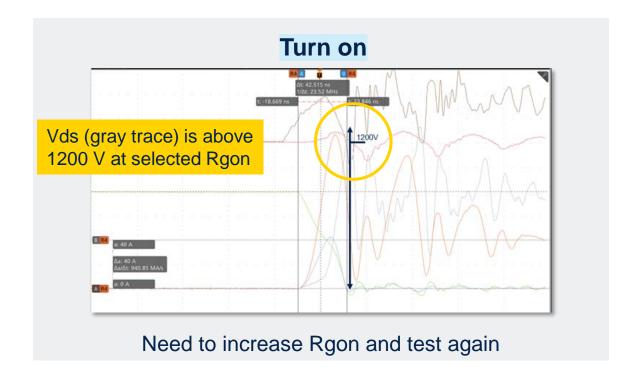

### Driving Rg choice

### Choosing the right gate resistance involves a tradeoff between switching speed and safe operation (Vds spike < Vdss)

- **For Rgoff**, use the lowest value that ensures the Absolute Maximum Rating is not exceeded (with appropriate margin) at Vgs-off = -5V. Then, for 0V OFF, you can simply reduce it to match the speed you would obtains with a negative driving voltage.

- The same sequence on the left can then be used to choose the proper Rgon to mitigate the Vds spike across the complementary switch in the half bridge. In this case, you don't need to tune the Rgon value when moving to unipolar driving.

- Once identified the Rgon and Rgoff which can optimize losses and mitigate the voltage spikes, measurements will be performed at room and high temperatures, to check the behavior.

- Configurations with and without the Active Miller clamp were considered.

### An example of how to select Rg

In these comparisons, a typical and safe switching speed is applied, and the same speed is imposed in all the configurations tested

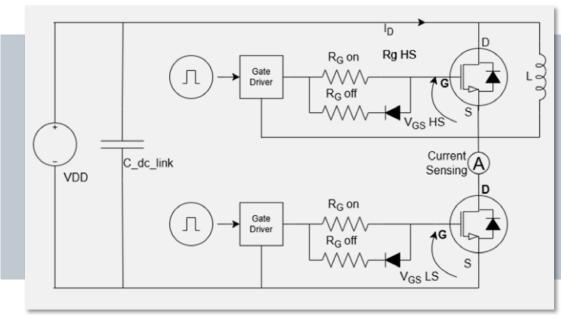

### Double pulse test schematic and test conditions

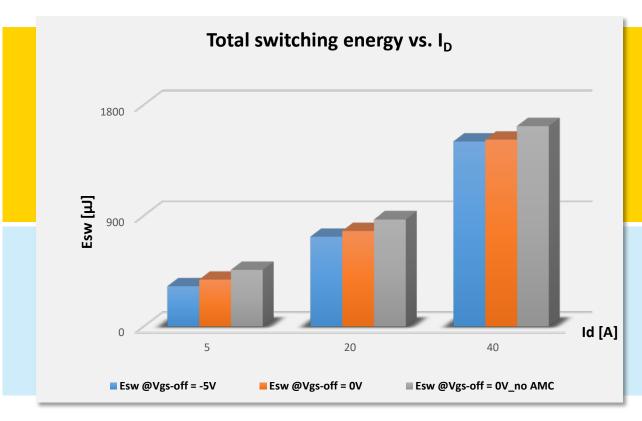

The comparison represents the  $E_{sw}$  vs  $I_D$  using a 1200 V device with 27 m $\Omega_{tvp}$  Gen3 SiC MOSFET as test vehicle

#### Test conditions:

- $T_1 = 150^{\circ}C$

- Turn-on speed: di/dt<sub>ON</sub> ≈ 2 A/ns

- Turn-off speed: dv/dt<sub>OFF</sub> ≈ 35 V/ns

- V<sub>DD</sub> ≈ 800 V

- 0 Vgs-off with and without Active Miller clamp vs negative driving voltage as PoR

- $V_{th} = 2.8 \text{ V}$

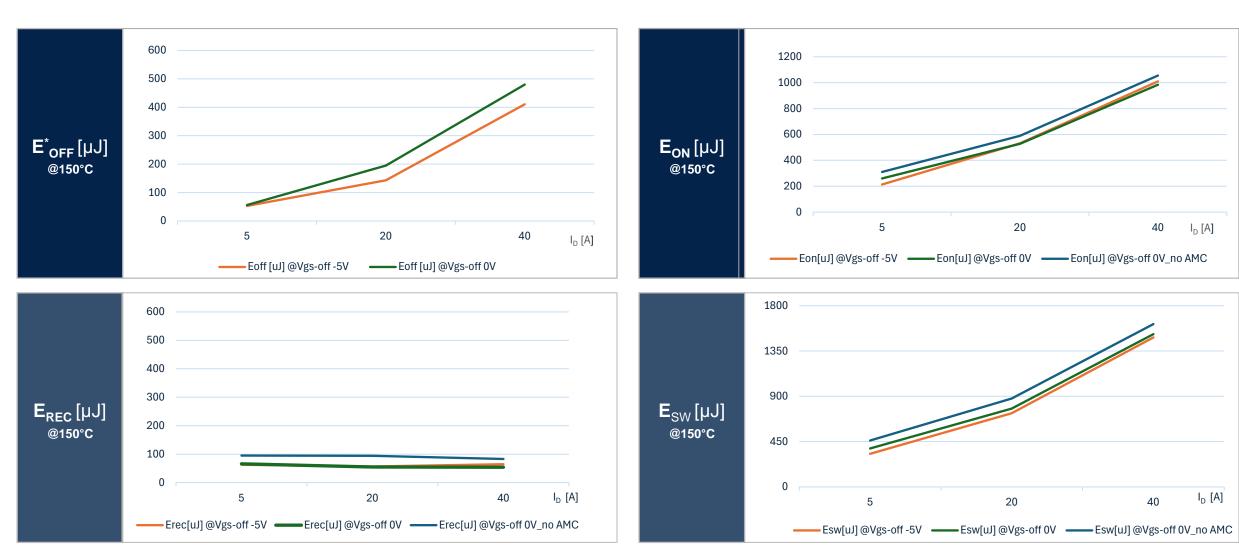

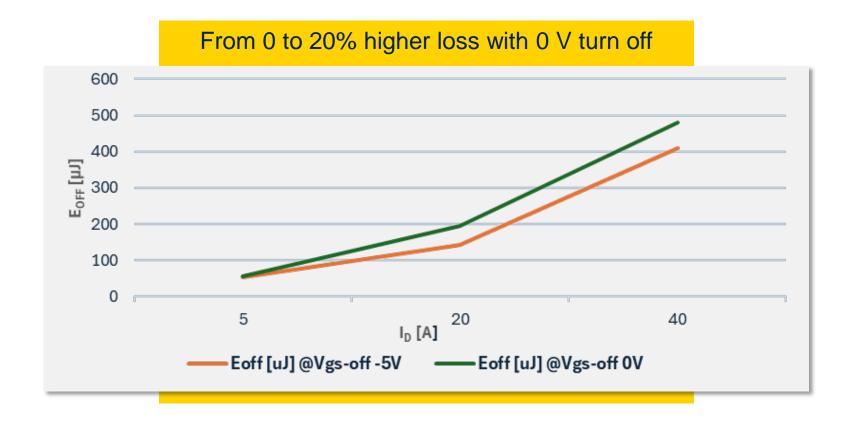

**Eoff** (turn-off speed: dv/dt<sub>OFF</sub> ≈ 35 V/ns)

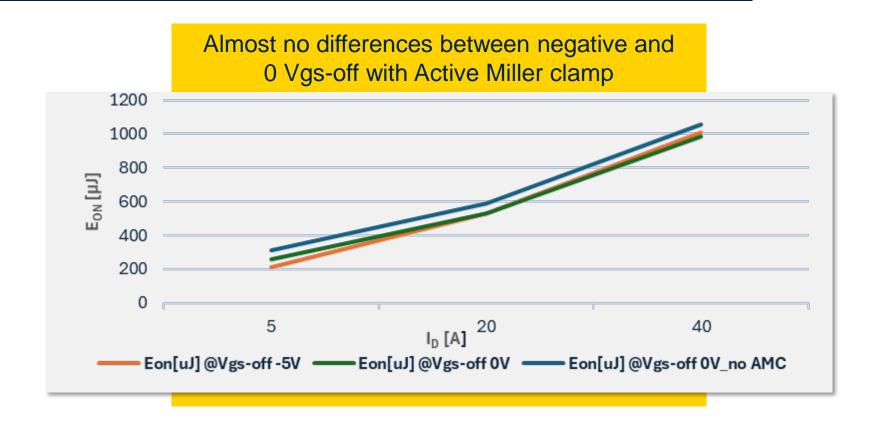

Eon (turn-on speed: di/dt<sub>oN</sub> ≈ 2A/ns)

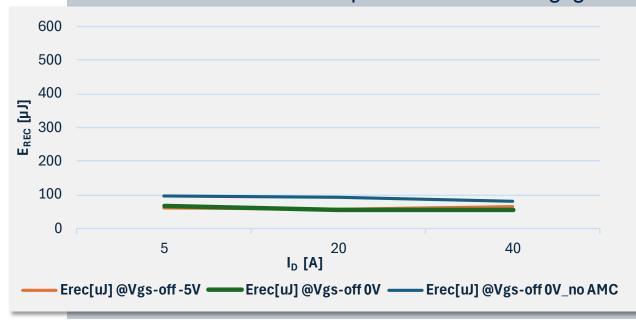

#### Erec (turn-on speed: di/dt<sub>oN</sub> ≈ 2A/ns)

In all the analyzed cases the contribution of Erec is very small in comparison with Eon and Eoff. Even if there are small differences between negative and 0 Vgs-off, their contribution to the overall power losses is negligible

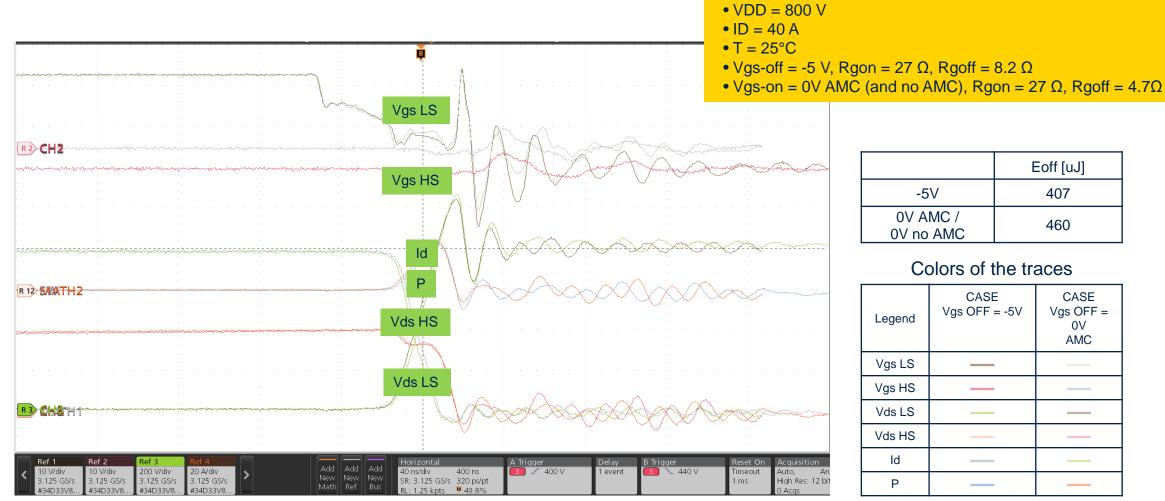

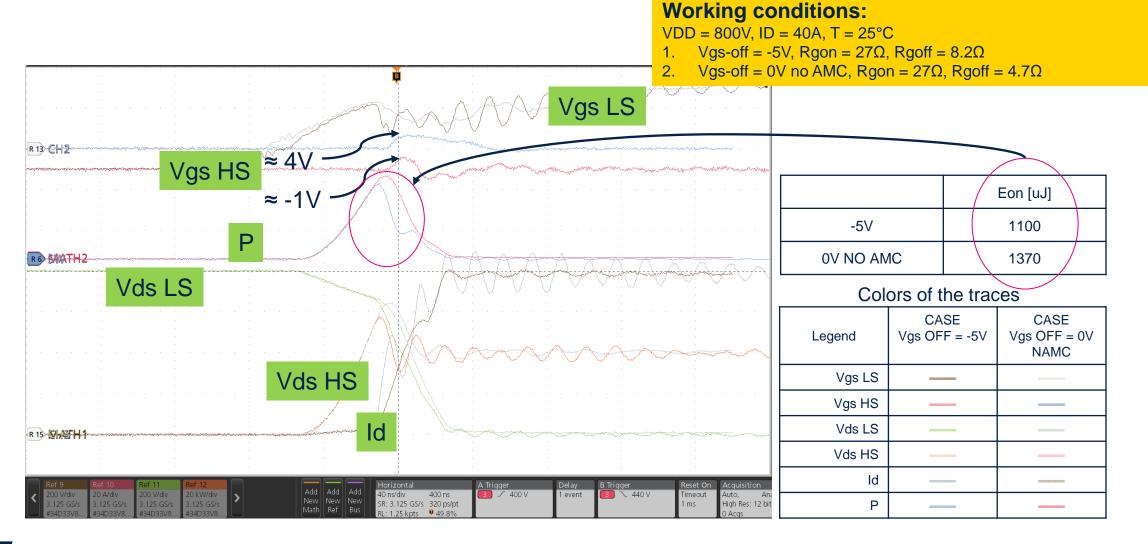

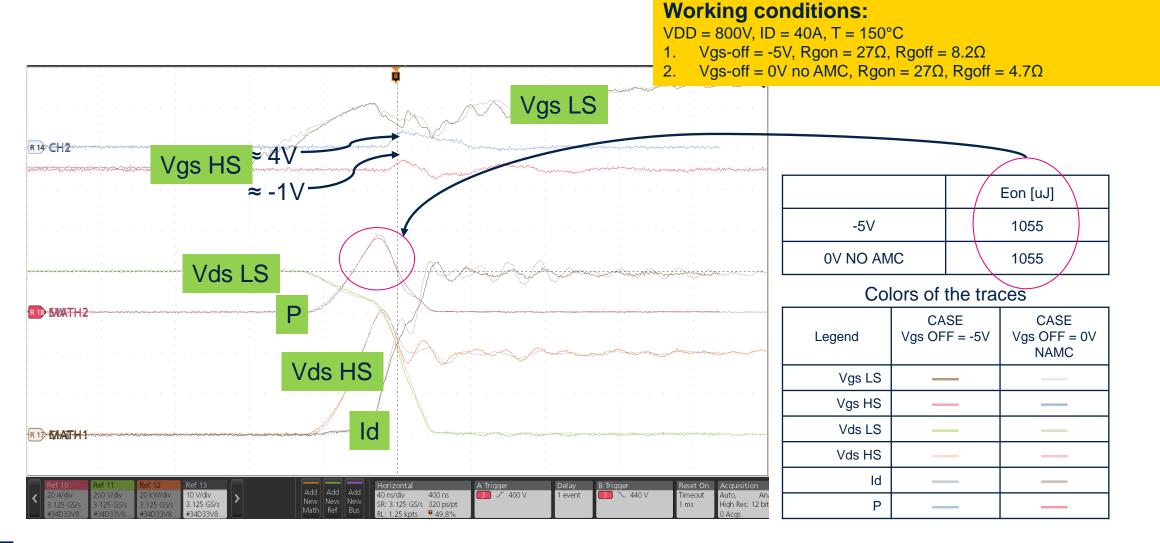

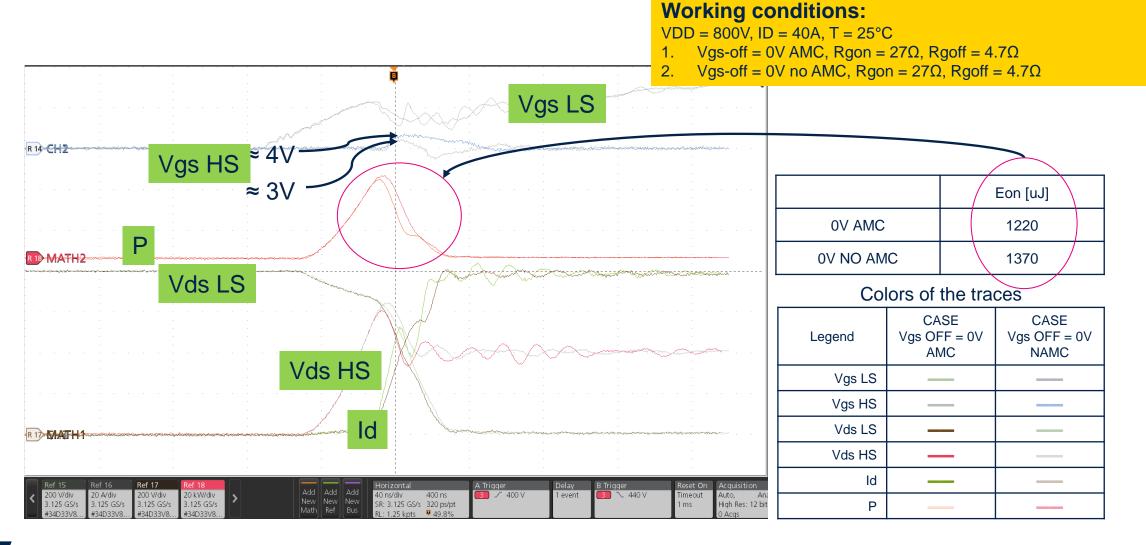

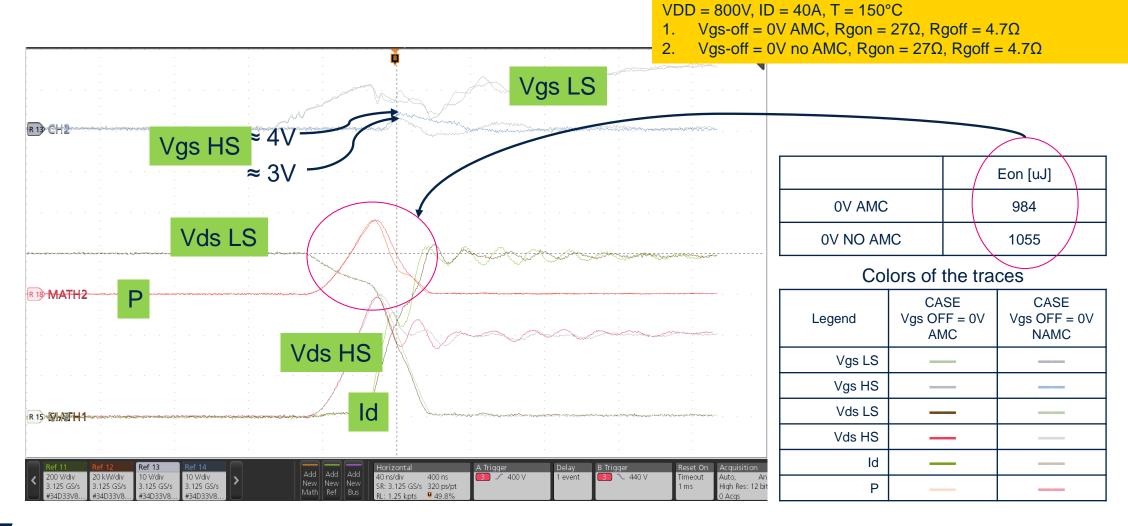

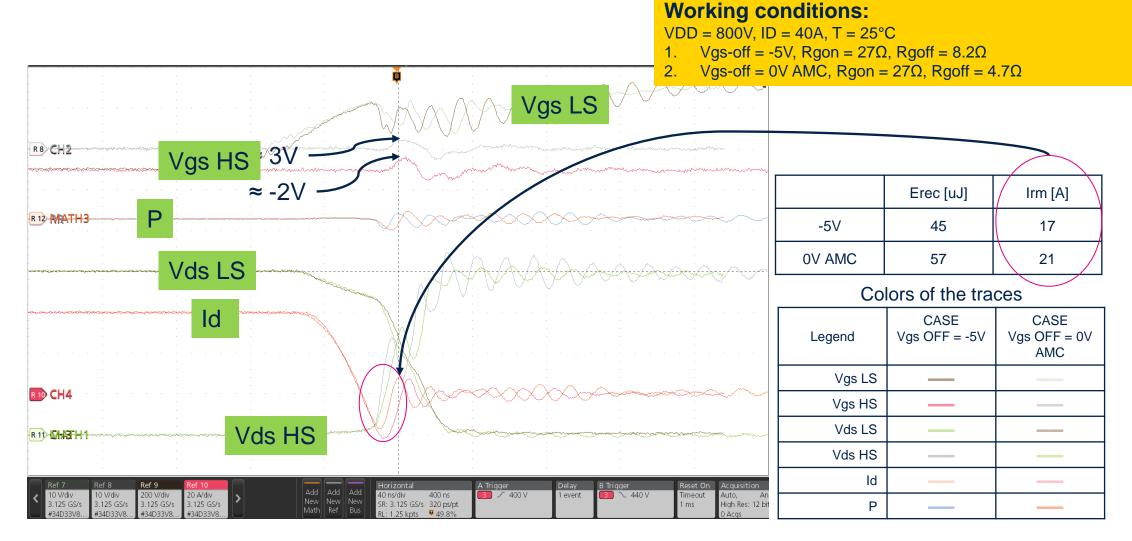

### **Experimental results: waveforms**

**Test conditions:**

| Eoff [uJ] |

|-----------|

407

460

#### Colors of the traces

-5V

OV AMC /

0V no AMC

| Legend | CASE<br>Vgs OFF = -5V | CASE<br>Vgs OFF =<br>0V<br>AMC |

|--------|-----------------------|--------------------------------|

| Vgs LS |                       |                                |

| Vgs HS |                       |                                |

| Vds LS |                       |                                |

| Vds HS |                       | _                              |

| ld     |                       |                                |

| Р      |                       |                                |

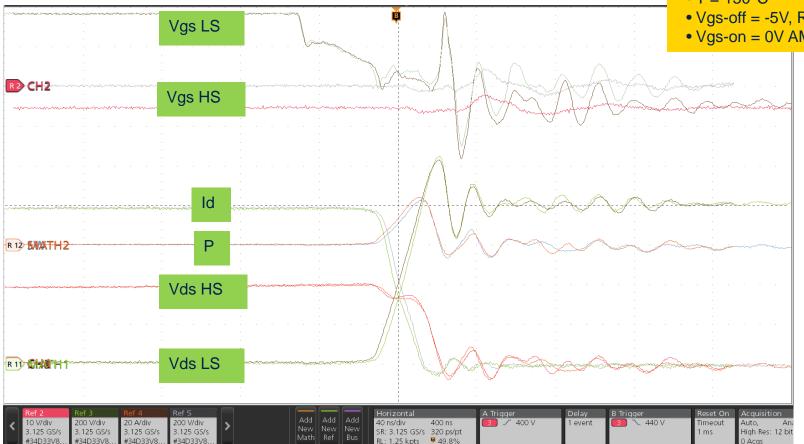

#### **Test conditions:**

- VDD = 800V

- ID = 40A

- T = 150°C

- Vgs-off = -5V, Rgon =  $27\Omega$ , Rgoff =  $8.2\Omega$

- Vgs-on = 0V AMC Rgon =  $27\Omega$ , Rgoff =  $4.7\Omega$

|                       | Eoff [uJ] |

|-----------------------|-----------|

| -5V                   | 410       |

| 0V AMC /<br>0V no AMC | 480       |

#### Colors of the traces

| Legend | CASE<br>Vgs OFF = -5V | CASE<br>Vgs OFF =<br>0V<br>AMC |

|--------|-----------------------|--------------------------------|

| Vgs LS |                       |                                |

| Vgs HS |                       |                                |

| Vds LS |                       |                                |

| Vds HS |                       |                                |

| ld     |                       |                                |

| Р      |                       |                                |

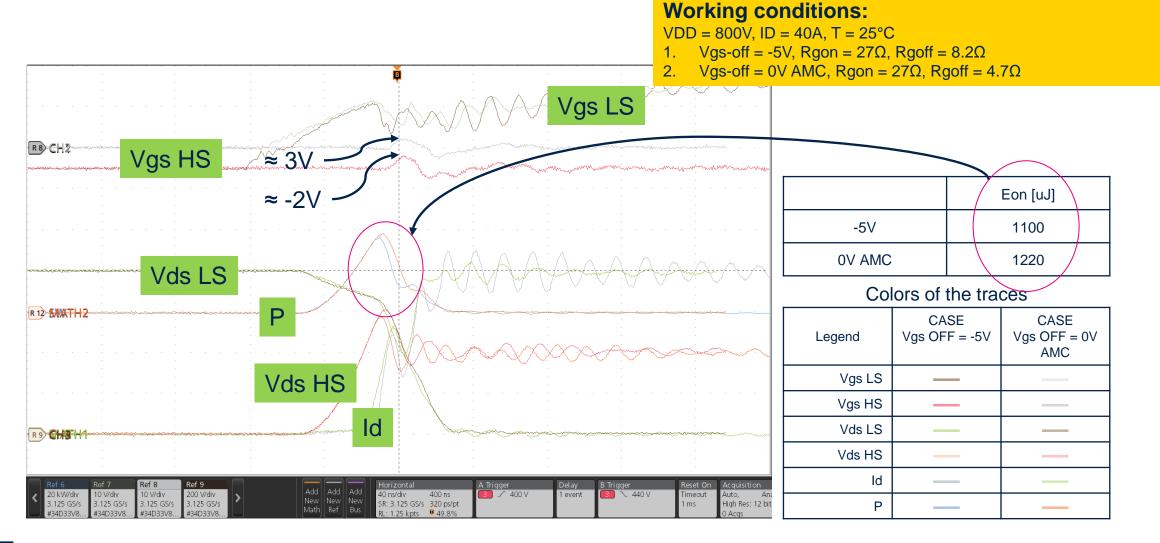

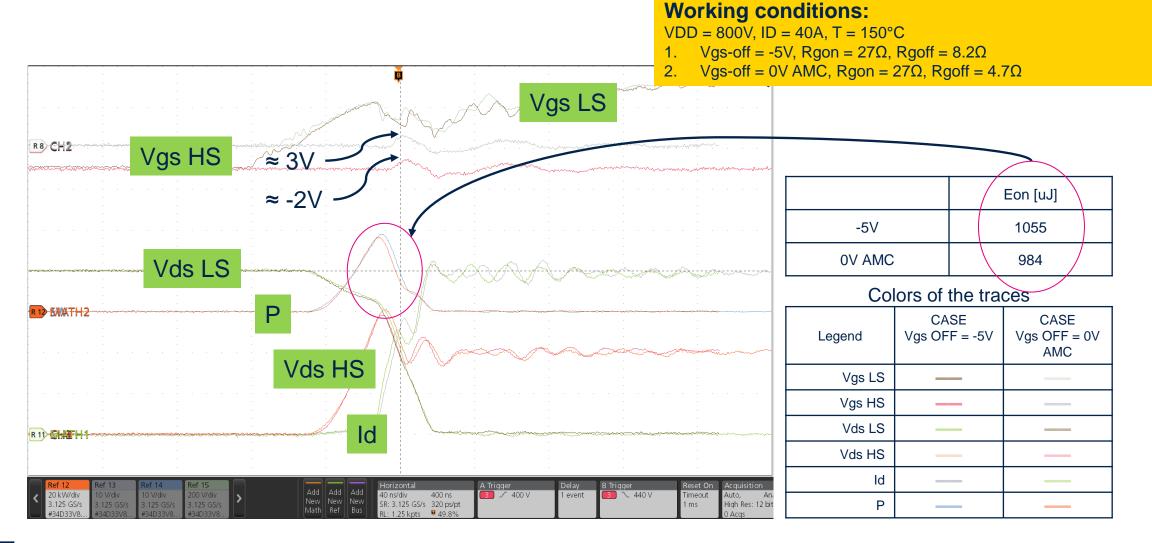

**Working conditions:**

### Reverse recovery waveforms comparison

### **Summary and conclusions**

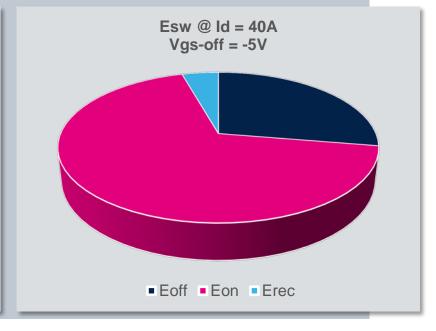

## Energy comparison bipolar vs unipolar driving Summary of test results

#### Experimental data on 1200V; SiC MOSFET Gen3; 27mΩ typ

#### **Test condition:**

- TJ = 150°C,

- Turn-on speed: di/dt<sub>ON</sub> ≈ 2A/ns

- Turn-off speed: dv/dt<sub>OFF</sub> ≈ 35V/ns

- VDD ≈ 800V

- 0 Vgs-off with and without Active Miller clamp vs negative driving voltage as PoR

#### Results:

- In the case investigated (0V Vgs-off and AMC) the gap between unipolar and bipolar driving is negligible especially at high load

- Removing the Active Miller clamp introduces additional switching losses in the range of 5-10%.

### Conclusions

#### Active miller clamp is recommended when applying 0V OFF Vgs

- R<sub>gon</sub> and R<sub>goff</sub> (and in general the driving circuit) can be fine-tuned to optimize the performance, minimizing spikes and switching losses with negative and with zero-volt V<sub>gs-off</sub>.

- The comparison between -5V and 0V shows negligible differences in case of typical threshold voltage (V<sub>TH(typ)</sub>).

- For design robustness, it is suggested to design the system and the driving circuit considering the worst case in terms of V<sub>TH</sub> and temperature, paying attention to the additional amount of energy loss in comparison with the case @ typical V<sub>TH</sub>.

# Our technology starts with You

ST logo is a trademark or a registered trademark of STMicroelectronics International NV or its affiliates in the EU and/or other countries. For additional information about ST trademarks, please refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>.

All other product or service names are the property of their respective owners.