# SR5 E1 line – Register protection overview

### Introduction

The purpose of this document is to give an overview of the register protection mechanism (REG PROT) present in the SR5 E1 line products listed in the following table. It explains how to use the REG PROT feature and provides the necessary information and a reference code to use the register protection mechanism.

**Table 1. Device list**

| Device | Device list      |

|--------|------------------|

| SR5E1  | SR5E1E3, SR5E1E7 |

## 1 Overview

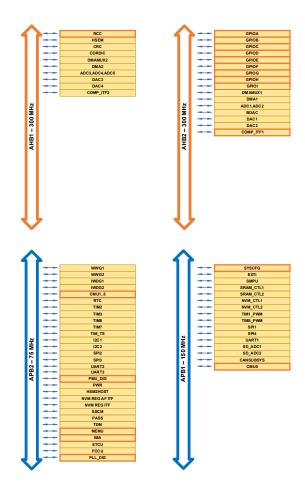

The SR5E1 system architecture presents four peripheral bridges (AHB1, AHB2, APB1, and APB2) that support a hardware mechanism to protect the configuration registers of allocated peripherals on each bridge from unwanted modifications.

The protection mechanism works like a firewall for the write operations, based on the lock status of the register. For this reason, the register protection feature is also referred to as register hardware lock.

Note: The registers are protected with a 32-bit granularity.

The following figure shows the allocation of peripherals available on bridges of the SR5E1 device.

Figure 1. SR5E1: peripheral allocations on bridges

TN1479 - Rev 1 page 2/8

# 2 REG\_PROT

### 2.1 Enabling mechanism

The register protection mechanism (REG PROT) is not enabled by default.

The feature is activated by programming a dedicated device configuration format record (REG\_HWLOCK\_DCF) in the UTEST DCF records area. An enable bit is available for each AHB and APB bridge, giving the possibility to lock APB1, APB2, AHB1, and AHB2 independently.

During the system boot, the device configuration is loaded, and the protection mechanism is actually activated.

Note: The REG\_HWLOCK\_DCF is programmable only once. Therefore, if enabled, the register protection mechanism cannot be disabled.

The enabling of the register protection mechanism on a peripheral bus bridge activates the protection for all the peripherals on the bus, which have the mechanism available. The following table shows the actual protected peripherals on each bridge of the SR5E1 device. Refer to the section "REG\_PROT configuration" of the SR5E1 reference manual (see Reference documents) for the whole list of protected registers for each IP.

| REG_HWLOCK DCF |                                     |                |             |  |  |  |

|----------------|-------------------------------------|----------------|-------------|--|--|--|

| HWLOCK4        | HWLOCK3                             | HWLOCK2        | HWLOCK1     |  |  |  |

| APB Bridge2    | APB Bridge1                         | AHB Bridge2    | AHB Bridge1 |  |  |  |

| SYSCFG<br>CMU0 | CMU15<br>MEMU<br>PMU_DIG<br>PLL_DIG | GPIOx (x = AI) | RCC         |  |  |  |

|                | IMA                                 |                |             |  |  |  |

Table 2. SR5E1: protected peripherals on bridges

## 2.2 Two-step writing mechanism

The register protection mechanism (REG PROT) has the main goal to protect registers from unwanted modification. This means modifications are possible only using a special procedure.

The modification of a protected register consists of a two-step write operation.

- 1. The first write (**WRITE1**), to unlock the register for write, requires providing as data the actual address of the register.

- 2. The second write (WRITE2) is the effective write to the register with the desired data.

Note: As shown in Figure 2. Two-step writing mechanism, the lock of the register is reactivated right after the WRITE2 takes effect.

TN1479 - Rev 1 page 3/8

WRITE1

WDATA = REG\_ADDRESS

Register UNLOCKED

WRITE2

WDATA = REG\_DATA

Figure 2. Two-step writing mechanism

Note:

To unlock the register protection mechanism, the writing of the register address and the writing of the actual data must be done by the same bus master. An erroneous unlock procedure leads to a hard fault error.

### 2.3 Usage example

The example below shows how to configure the REG PROT mechanism on the APB2 bridge and how to modify one register (EXTICR 3 0) of one peripheral (SYSCFG) connected to this bus.

Table 3. Example: SYSCFG.EXTICR\_3\_0 configuration

| SYSCFG register name | Address    | Value                                      |

|----------------------|------------|--------------------------------------------|

| EVILOR 2 0           | 0x42000008 | 0x1 = EXTI0 mux out is PA0 (default value) |

| EXTICR_3_0           |            | 0x2 = EXTI0 mux out is PB0                 |

To configure the register protection mechanism for the APB2 bridge, the user must program the REG HWLOCK DCF as follows:

# • REG\_HWLOCK\_DCF.HWLOCK4 = 0x1,

The write access to the configuration registers of peripherals SYSCFG and CMU0 is already active after the system boot.

To activate the REG PROT mechanism, the user must issue a system reset. Just after the system reset, the SYSCFG and CMU0 peripherals are immediately protected from unwanted modification.

In order to change the value of the register the two-step write mechanism must be used:

#### WRITE1:

```

/* Register locked: register address required as data. */

SYSCFG.EXTICR_3_0 = SYSCFG_BASE + 0x08U;

```

TN1479 - Rev 1 page 4/8

#### WRITE2:

```

/* Register unlocked: write access granted. */

SYSCFG.EXTICR_3_0 = 0x2U;

```

The next write in the register to program a different value will lead to a hard fault error.

```

/* Register locked: write access results in an error. */

```

SYSCFG.EXTICR\_3\_0 =  $0 \times 10$ ;

TN1479 - Rev 1 page 5/8

# **Revision history**

Table 4. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 31-Jul-2023 | 1        | Initial release. |

TN1479 - Rev 1 page 6/8

# **Contents**

| 1   | Ove      | Overview                   |     |  |  |  |

|-----|----------|----------------------------|-----|--|--|--|

| 2   | REG_PROT |                            |     |  |  |  |

|     |          | Enabling mechanism         |     |  |  |  |

|     |          | Two-step writing mechanism |     |  |  |  |

|     |          | Usage example              |     |  |  |  |

| Rev | ision    | history                    | . 6 |  |  |  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

TN1479 - Rev 1 page 8/8