## Built-in self-tests for SPC570Sx

## Introduction

The purpose of this document is to describe how to configure and use built-in self-tests (BIST) in SPC570Sx device. Typical usage of the BIST is to detect latent failures before the user code is executed.

There are two different BIST tests available: LBIST (logic BIST) and MBIST (memory BIST).

## 1 Built-In self-tests

The purpose of this document is to describe how to configure and use built-in self-tests (BIST) in SPC570Sx devices. Typical usage of the BIST is to detect latent failures before the user code is executed. There are two different BIST tests available: LBIST (logic BIST) and MBIST (memory BIST).

A peripheral responsible for the BISTs execution is self-test control unit (STCU2). The STCU2 can execute BISTs during the microcontroller reset phase. Configuration of the STCU is performed via DCF records, which are stored at a specific UTEST address in a test Flash area—once time programmable OTP. User is allowed to program new DCF records, but there is no way to erase the test Flash area. Execution of the DCF records is performed by a system status and configuration module (SSCM) during the reset phase.

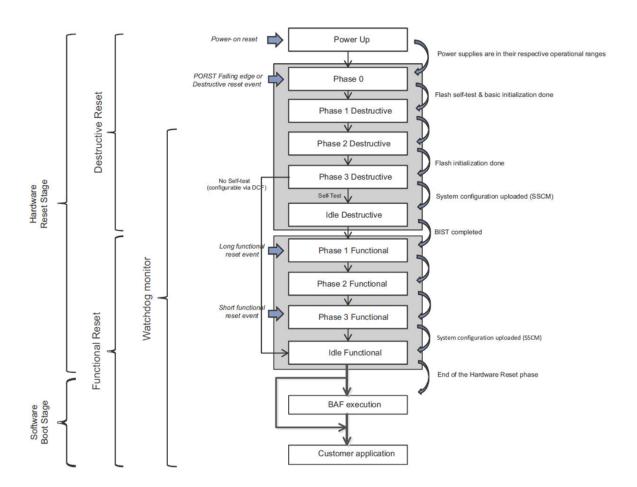

## 1.1 Reset sequence and BIST execution

The hardware reset stage is handled by the RGM module through a state machine. The RGM executes the device initialization through a sequence of phases. At the end of the hardware reset stage, the device starts the software boot stage. The software boot stage is actually the very first code executed by the processor. This code, called BAF, is programmed by ST in a specific Flash location and cannot be modified.

Based on DCF records stored in the user test Flash area, the STCU2 performs BISTs after the destructive reset phase 3.

The destructive reset phase 3 is entered after the reset destructive phase 2 is completed. During this phase, the SSCM module uploads the system configuration and dispatches to the proper clients. During this phase, the CPU reset vector is written into the mode entry (ME) module and the trimming for the analog IPs (such as VR, LVD/HVD, temperature sensor, ADC, I/O, oscillator) are applied. In case no BIST is to be executed, the device can be kept into the phase 3 DEST by keeping the PORST. This can be used for debugging purposes by allowing external test/development equipment to connect through JTAG to the internal debugger.

TN1394 - Rev 1 page 2/24

Figure 1. Reset sequence

TN1394 - Rev 1 page 3/24

$\Delta Y(2) = 0.0V$

X2 0.0s

X1 X2

Agilent Technologies

WED MAR 05 09:32:08 2014

1 000/ 1.000/ 1.000/ 1.000/ 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 100.0 10

Figure 2. PORST pin behavior

#### Probes:

A2 – green PORST signal (pin 44 of eTQFP64 package)

Source

A3 – violet 1.2 V power supply

$\Delta X = 283.00000us$

Mode

Manual

A4 - red 3.3 V power supply

Example of power-on PORST pin behavior is shown in Figure 2. PORST pin behavior.

PORST reset signal is released during the reset phase 0. The figure is valid regardless the BISTs are executed after power-on reset or not executed at all.

X1 -283.000us

$1/\Delta X = 3.5336 kHz$

## 1.2 System status and configuration module (SSCM)

The SSCM module is used during the boot phase to retrieve a set of system and blocks configurations and dispatch them to the proper modules. The SSCM reads device configuration data from the test Flash - it interprets the data as a series of "write" commands for the connected "client" modules.

Note: STCU2 is one of the clients.

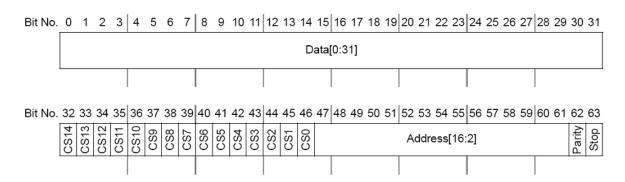

The configuration is stored into an area of the test Flash and organized into a 64-bits record, called DCF (device configuration format). Each DCF contains a client identifier, an address (which identifies the data type within a specific client), and 32-bits data.

The SSCM, during the reset phase 3 reads all the DCF records and dispatches them to the various system modules.

TN1394 - Rev 1 page 4/24

## 1.2.1 DCF record description

The DCF record structure is reported in the figure below and the DCF record description in Table 1. DCF record description.

Figure 3. DCF record structure

Table 1. DCF record description

| Field                  | Description                                                                                                                                                       |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:31<br>Data[0:31]     | 32-bit of data that is to be written to the DCF client                                                                                                            |

| 32:46<br>CSn           | Chip select n.  One chip select is asserted ("1") per DCF record to select the target module for the DCF client.  All other chip selects should be negated ("0"). |

| 47:61<br>Address[16:2] | Address of the DCF client within the selected module (1)                                                                                                          |

| 62<br>Parity           | Parity bit for the DCF record (2)                                                                                                                                 |

| 63<br>Stop             | Stop bit.  This bit indicated the end of the list od DCF records. (3)  0 not the end of the list  1 end of the list                                               |

<sup>1.</sup> Address decoding for DCF clients may not match the standard software address map decoding. Details of DCF client addresses are defined in each module chapter.

TN1394 - Rev 1 page 5/24

<sup>2.</sup> This bit is NOT implemented for DCF client written from UTEST

<sup>3.</sup> The erased state of the Flash memory is 0xFFFF\_FFFF\_FFFF. Therefore the list ends with the first unprogrammed double word. This location can be programmed with a new record to extend the list.

#### 1.2.2 DCF records location

The DCF records are stored in the user test Flash area (UTEST) starting from address 0x00400300 up to 0x00400FFF.

ADDR offset DATA 0x00 0x05AA55AF 0x04 0x00000000 STOP=0 0x08 WDATA[31:0] ADDR[16:2] 0x0CCD[14:0] **PRTY** STOP=0 WDATA[31:0] 0x10 CD[14:0] ADDR[16:2] **PRTY** STOP=0 0x14 8n-1 + 0x0Reserved 8n-1 + 0x4Reserved 1 8n + 0x08n + 0x4

Table 2. Series of DCF records in UTEST Flash memory

#### Caution:

- There must never be an unprogrammed record in the DCF data structure, as it is interpreted as a stop record (bit 63 is set to 1) and subsequent records are ignored. This allows to program the records in several sessions, each time appending new records at the end of the list.

- There is not possible to erase once programmed record. UTEST area is OTP (once time programmable –

not erasable.) But there is the possibility to modify DCF records in some cases (see Section 1.4.7 STCU

setup invalidation).

- It is possible for more than one DCF Record to write to the same DCF client. In this case the later record usually overrides a DCF client value set by a previous record. However, not all DCF clients allow overwriting; this depends on the DCF client implementation.

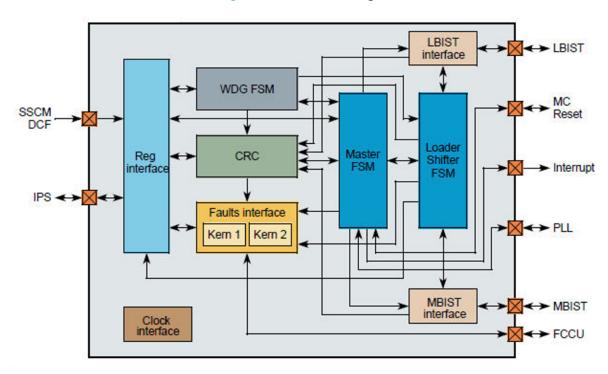

## 1.3 Self test control unit (STCU2)

## 1.3.1 Self-test control unit (STCU2) introduction

Self-test control unit (STCU2) is a comprehensive programmable hardware module that controls the self-test sequence applied both during the off-line and/or on-line conditions. The hardware can manage the logic built-in self-test (LBIST) and the SRAM or ROM built-in self-test (MBIST) blocks of the device. The STCU2 includes the SSCM DCF bus to load the self-test parameters (LBIST or MBIST scheduling activity, LBIST setup, unrecoverable faults (UF) or recoverable faults (RF) management, CRC and MISR expected values, PLL management, and so on) from flash memory during the off-line self-test phase. This interface is only able to write the configuration parameters and start the self-test execution once the STCU2 global reset has been applied. Register access by software is granted by an IPS interface to check the results of the off-line self-test and to load or check the execution of the on-line self-test.

Note: SPC570Sx has implemented off-line self-test only executed during a destructive reset phase.

#### The STCU2 includes:

- A programmable watchdog timer (WDG) to check the LBIST and MBIST self-test operations have completed within the assigned time slot or the STCU2 RUN or BYPASS bits have been programmed before watchdog time-out.

- Direct PLL control during the off-line self-test sequence.

- Two sets of registers to separately collect the LBIST or MBIST results.

TN1394 - Rev 1 page 6/24

To increase the security of this module, a different security key sequence is also required during self-test to unlock write access to the STCU2 registers.

For more details, see Figure 4. STCU2 block diagram.

#### 1.3.2 BIST watchdog

STCU includes two different watchdogs:

- A hard-coded watchdog used to Auto Lock the STCU2 access, forcing a reset condition on the double security key registers.

- A dual function watchdog:

- After a reset event initializes the STCU2, it is used as a hard-coded watchdog time-out.

- During LBIST or MBIST runs, it is used as a programmable Watchdog timer to check the LBIST or MBIST have completed in the designated time slot.

Figure 4. STCU2 block diagram

### 1.3.3 BIST clocking

An internal IRC oscillator 16 MHz or PLL could be used for LBIST tests execution. (LBIST tests execution maximal frequency is 20 MHz, when PLL is used.)

There is possible to enable PLL at up to 80 MHz during MBIST test execution to speed up the testing process.

STCU is able to control the PLL0 during the off-line self-test operations depending on the status of the STCU\_RUN[MBPLLEN]. By this flags, off-line MBIST executed enabling the on-chip PLL control interface selecting the parameters defined into STCU\_PLL\_CFG register (PLLODF, PLLIDF and PLLDF).

Following the formula of PLL0 frequency output:

$$fPLLout = \frac{fVCO}{PLLODF*2}$$

Where:

$$fVCO = fPLLin*(PLLDF*2) = \left(\frac{fRC}{PLLIDF}\right)*\left(PLLDF*2\right)$$

f RC is the frequency of the internal oscillator that is 16 MHz.

Caution: there is necessary to take in account the RC OSC accuracy (typically +-8% see datasheet) for PLL setup not to overcome maximal-allowed clocking frequency.

TN1394 - Rev 1 page 7/24

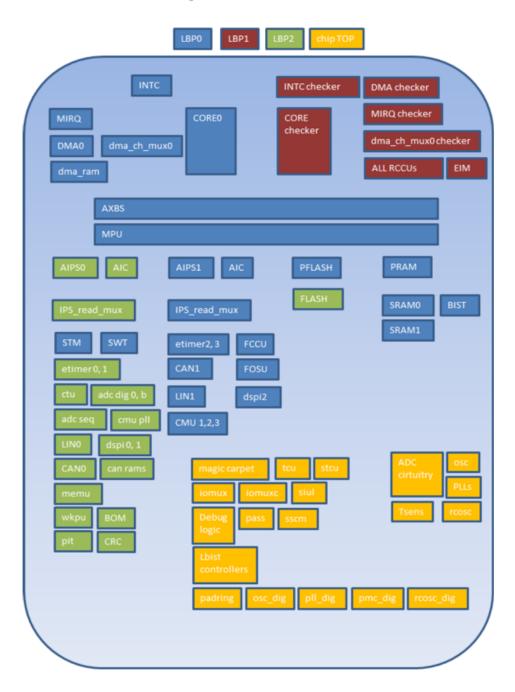

## 1.3.4 STCU LBIST description

The LBIST (logic build in self test) contains 3 partitions (lakes of tests):

Figure 5. LBIST structure

Note: LBIST coverage achieved on monitors is 90% and on each partition is >70% using 2000 patterns.

TN1394 - Rev 1 page 8/24

## 1.3.5 BIST MBIST description

The MBIST (memory build in self test) contains 9 parts:

- MB0 ram\_sram\_1

- MB1 ram\_sram\_0

- MB2 ram\_dma

- MB3 ram\_can\_rxim\_1

- MB4 ram\_can\_rxim\_0

- MB5 ram\_can\_mb\_1

- MB6 ram\_can\_mb\_0

- MB7 ram\_mpflash

- MB8 bam\_rom

## 1.4 BIST setup examples

It is possible to prepare different setup of BIST test. This chapter describes some examples of the following configurations:

- LBIST only

- MBIST only

- LBIST and MBIST

- STCU bypass

## 1.4.1 MBIST example setup

Table 3. MBIST example setup

| Nr. | DCF record        | STCU register | Note                                                                                                                                                                                                                                                                                                      |

|-----|-------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | D3FEA98B 00080008 | STCU_KEY1     | Key 1/2 to unlock STCU access                                                                                                                                                                                                                                                                             |

| 2   | 2C015674 00080008 | STCU_KEY2     | Key 2/2 to unlock STCU access                                                                                                                                                                                                                                                                             |

| 3   | 10000001 0008000C | STCU_CFG      | Pointer set for MBIST0, MBIST reduced algorithm (PMOSEN bit set to '0'), PMOSEN and MBU can be played to choose different algorithms and MBIST coverage, WRP bit set to '0' to allow IPS access.                                                                                                          |

| 4   | 0C02003C 00080010 | STCU_PLL_CFG  | PLL programmed for 40MHz with input frequency as RC(16 MHz+-8%), PLL output freq = (Input_freq*LDF)/(ODF*IDF) = (Input_freq* 0x3C)/(0x0C*02) = 40MHz, according to errata DAN-0043391                                                                                                                     |

| 5   | 0003D090 00080014 | STCU_WDG      | Watchdog timeout setup                                                                                                                                                                                                                                                                                    |

| 6   | 00000000 00080074 | STCU_MBUFML   | Programming '1' to the respective MBIST in this register generates an unrecoverable fault in the case of MBIST failure. If the fault is permanent, then the device will never recover from this programming. So it is safe to program '0' in this register and later STCU status can be read by software. |

| 7   | 00000000 00080028 | STCU_ERR_FM   | Programming '1' to any corresponding bit of this register can make the device unrecoverable if the fault is permanent.                                                                                                                                                                                    |

| 8   | 91000000 00080600 | MBIST_CTRL0   | Next pointer set to MBIST1, CSM BIST set to '1' to indicate parallel running of MBIST0 and MBIST1                                                                                                                                                                                                         |

| 9   | 92000000 00080604 | MBIST_CTRL1   | Next pointer set to MBIST2, CSM BIST set to '1' to indicate parallel running of MBIST1 and MBIST2                                                                                                                                                                                                         |

| 10  | 93000000 00080608 | MBIST_CTRL2   | Next pointer set to MBIST3, CSM BIST set to '1' to indicate parallel running of MBIST2 and MBIST3                                                                                                                                                                                                         |

| 11  | 94000000 0008060C | MBIST_CTRL3   | Next pointer set to MBIST4, CSM BIST set to '1' to indicate parallel running of MBIST3 and MBIST4                                                                                                                                                                                                         |

TN1394 - Rev 1 page 9/24

| Nr. | DCF record        | STCU register | Note                                                                                              |

|-----|-------------------|---------------|---------------------------------------------------------------------------------------------------|

| 12  | 95000000 00080610 | MBIST_CTRL4   | Next pointer set to MBIST5, CSM BIST set to '1' to indicate parallel running of MBIST4 and MBIST5 |

| 13  | 96000000 00080614 | MBIST_CTRL5   | Next pointer set to MBIST6, CSM BIST set to '1' to indicate parallel running of MBIST5 and MBIST6 |

| 14  | 97000000 00080618 | MBIST_CTRL6   | Next pointer set to MBIST7, CSM BIST set to '1' to indicate parallel running of MBIST6 and MBIST7 |

| 15  | 98000000 0008061C | MBIST_CTRL7   | Next pointer set to MBIST8, CSM BIST set to '1' to indicate parallel running of MBIST7 and MBIST8 |

| 16  | 7F000000 00080620 | MBIST_CTRL8   | Next pointer set to null pointer to indicate end of self test                                     |

| 17  | 00000201 00080000 | STCU_RUN      | Self test triggered with MBIST run on PLL frequency                                               |

## 1.4.2 MBIST evaluation

The MBIST test result is available in STCU registers for evaluation in user application.

ERR\_STAT register content to be equal to zero as global no error status.

STCU\_MBEx registers contain bit field with finished MBISTs. Content shall match with executed MBISTs based on DCF records. STCU\_MBSx contain bit field with finished MBISTs without error. Content of corresponding registers to be equal STCU\_MBEx = STCU\_MBSx.

Table 4. MBIST results

```

STCU_ERR_STAT = 0x0

STCU_MBEL = 0x1FF

STCU_MBSL = 0x1FF

STCU_MBEM = 0x0

STCU_MBSM = 0x0

STCU_MBSH = 0x0

STCU_MBSH = 0x0

```

## 1.4.3 LBIST example setup

Table 5. LBIST example setup

| Nr. | DCF record        | STCU register | Note                                                                                                                                                                                                                                                                                                      |

|-----|-------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | D3FEA98B 00080008 | STCU_KEY1     | Key 1/2 to unlock STCU access                                                                                                                                                                                                                                                                             |

| 2   | 2C015674 00080008 | STCU_KEY2     | Key 2/2 to unlock STCU access                                                                                                                                                                                                                                                                             |

| 3   | 005A0001 0008000C | STCU_CFG      | Pointer set for LBIST partition0, WRP bit set to '0' to allow IPS access. Refer to STCU doc for more details.                                                                                                                                                                                             |

| 4   | 18020037 00080010 | STCU_PLL_CFG  | PLL programmed for 18.3MHz with input frequency as RC(16 MHz+-8%), PLL output freq = (Input_freq*LDF)/ (ODF*IDF) = (Input_freq* 0x37)/(0x18*0x02)                                                                                                                                                         |

| 5   | 0001E848 00080014 | STCU_WDG      | Watchdog timeout setup                                                                                                                                                                                                                                                                                    |

| 6   | 00000000 00080040 | STCU_LBUFM    | Programming '1' to the respective LBIST in this register generates an unrecoverable fault in the case of LBIST failure. If the fault is permanent, then the device will never recover from this programming. So it is safe to program '0' in this register and later STCU status can be read by software. |

| 7   | 81001100 00080100 | STCU_LB_CTRL0 | Next pointer to LBIST partition1, parallel mode, CSM bit (31st) can be played with to run                                                                                                                                                                                                                 |

| 8   | 000007D0 00080104 | STCU_LB_PCS0  | Number of patterns -2000 for partition0                                                                                                                                                                                                                                                                   |

TN1394 - Rev 1 page 10/24

| Nr. | DCF record        | STCU register   | Note                                                                                                                 |

|-----|-------------------|-----------------|----------------------------------------------------------------------------------------------------------------------|

| 9   | 9CCC9484 00080110 | STCU_LB_MISREL0 | MISR lower 32 bits for 2000th pattern for partition0. It changes according to the number of patterns to be executed. |

| 10  | 36565224 00080114 | STCU_LB_MISREH0 | MISR upper 32 bits for 2000th pattern for partition0. It changes according to the number of patterns to be executed. |

| 11  | 82001100 00080140 | STCU_LB_CTRL1   | Next pointer to LBIST partition2, parallel mode, CSM bit(31st) can be played with to run                             |

| 12  | 000007D0 00080144 | STCU_LB_PCS1    | Number of patterns: 2000 for partition1                                                                              |

| 13  | CFC6629E 00080150 | STCU_LB_MISREL1 | MISR lower 32 bits for 2000th pattern for partition1. It changes according to the number of patterns to be executed. |

| 14  | 10E9A429 00080154 | STCU_LB_MISREH1 | MISR upper 32 bits for 2000th pattern for partition1. It changes according to the number of patterns to be executed. |

| 15  | 7F001100 00080180 | STCU_LB_CTRL2   | Next pointer to null to indicate end of self-test                                                                    |

| 16  | 000007D0 00080184 | STCU_LB_PCS2    | Number of patterns: 2000 for partition2                                                                              |

| 17  | A582B986 00080190 | STCU_LB_MISREL2 | MISR lower 32 bits for 2000th pattern for partition2. It changes according to the number of patterns to be executed. |

| 18  | D654207A 00080194 | STCU_LB_MISREH2 | MISR upper 32 bits for 2000th pattern for partition2. It changes according to the number of patterns to be executed. |

| 19  | 00000101 00080000 | STCU_RUN        | STCU triggered with LBIST programmed to run on PLL freq.                                                             |

#### 1.4.4 LBIST evaluation

The LBIST test result is available in STCU registers for evaluation in user application.

ERR\_STAT register content to be equal to zero as global no error status.

STCU\_LBE register contains bit field with finished LBISTs. Content shall match with executed LBISTs based on DCF records. STCU\_LBS register contains bit field with finished LBISTs without error. Content of the registers to be equal STCU\_LBE = STCU\_LBS.

Content of corresponding expected STCU\_MISREx and read STCU\_MISRRx register values shall match for all executed LBISTs.

Table 6. LBIST results

```

STCU_LBE = 0x7

STCU_LBS = 0x7

LBIST0

STCU_LB_MISREL0 = 0x9CCC9484

STCU_LB_MISREL0 = 0x9CCC9484

STCU_LB_MISREH0 = 0x36565224

STCU_LB_MISRH0 = 0x36565224

LBIST1

STCU_LB_MISREL1 = 0x0CFC6629E

STCU_LB_MISREL1 = 0x0CFC6629E

STCU_LB_MISREL1 = 0x10E9A429

STCU_LB_MISREH1 = 0x10E9A429

LBIST2

STCU_LB_MISREL2 = 0x0A582B986

```

TN1394 - Rev 1 page 11/24

## 1.4.5 Both LBIST and MBIST example setup

Table 7. LBIST and MBIST example setup

| Nr. | DCF record        | STCU register   | note                                                                                                                                                                                                                                                 |

|-----|-------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | D3FEA98B 00080008 | STCU_KEY1       | Key 1/2 to unlock STCU access                                                                                                                                                                                                                        |

| 2   | 2C015674 00080008 | STCU_KEY2       | Key 2/2 to unlock STCU access                                                                                                                                                                                                                        |

| 3   | 005A0001 0008000C | STCU_CFG        | Pointer set for LBIST partition0, MBIST reduced algo (PMOSEN, MBU bits set to '0'), PMOSEN and MBU can be played with to choose different algo and MBIST coverage, WRP bit set to '0' to allow IPS access, please refer to STCU doc for more details |

| 4   | 0C02003C 00080010 | STCU_PLL_CFG    | PLL programmed for 40MHz with input frequency as RC(16 MHz+-8%), PLL output freq = (Input_freq*LDF)/(ODF*IDF), = (Input_freq* 0x3C)/(0x0C*02) = 40MHz, according to errata DAN-0043391                                                               |

| 5   | 0003D090 00080014 | STCU_WDG        | Watchdog timeout setup                                                                                                                                                                                                                               |

| 6   | 01001100 00080100 | STCU_LB_CTRL0   | Next pointer to LBIST partition1, sequential mode, CSM bit(31st) can be played with to run in serial mode                                                                                                                                            |

| 7   | 000007D0 00080104 | STCU_LB_PCS0    | Number of patterns -2000 for partition0                                                                                                                                                                                                              |

| 8   | 9CCC9484 00080110 | STCU_LB_MISREL0 | MISR lower 32 bits for 2000th pattern for partition0. Will change according to the number of patterns to be executed.                                                                                                                                |

| 9   | 36565224 00080114 | STCU_LB_MISREH0 | MISR upper 32 bits for 2000th pattern for partition0. Will change according to the number of patterns to be executed.                                                                                                                                |

| 10  | 02001100 00080140 | STCU_LB_CTRL1   | Next pointer to LBIST partition2, sequential mode, CSM bit(31st) can be played with to run in serial mode                                                                                                                                            |

| 11  | 000007D0 00080144 | STCU_LB_PCS1    | Number of patterns -2000 for partition1                                                                                                                                                                                                              |

| 12  | CFC6629E 00080150 | STCU_LB_MISREL1 | MISR lower 32 bits for 2000th pattern for partition1. Will change according to the number of patterns to be executed.                                                                                                                                |

| 13  | 10E9A429 00080154 | STCU_LB_MISREH1 | MISR upper 32 bits for 2000th pattern for partition1. Will change according to the number of patterns to be executed.                                                                                                                                |

| 14  | 10001100 00080180 | STCU_LB_CTRL2   | Next pointer to MBIST0 to indicate MBIST run after LBIST                                                                                                                                                                                             |

| 15  | 000007D0 00080184 | STCU_LB_PCS2    | Number of patterns -2000 for partition2                                                                                                                                                                                                              |

| 16  | A582B986 00080190 | STCU_LB_MISREL2 | MISR lower 32 bits for 2000th pattern for partition2. Will change according to the number of patterns to be executed.                                                                                                                                |

| 17  | D654207A 00080194 | STCU_LB_MISREH2 | MISR upper 32 bits for 2000th pattern for partition2. Will change according to the number of patterns to be executed.                                                                                                                                |

| 18  | 91000000 00080600 | MBIST_CTRL0     | Next pointer set to MBIST1, CSM BIST set to '1' to indicate parallel running of MBIST0 and MBIST1                                                                                                                                                    |

| 19  | 92000000 00080604 | MBIST_CTRL1     | Next pointer set to MBIST2, CSM BIST set to '1' to indicate parallel running of MBIST1 and MBIST2                                                                                                                                                    |

| 20  | 93000000 00080608 | MBIST_CTRL2     | Next pointer set to MBIST3, CSM BIST set to '1' to indicate parallel running of MBIST2 and MBIST3                                                                                                                                                    |

| 21  | 94000000 0008060C | MBIST_CTRL3     | Next pointer set to MBIST4, CSM BIST set to '1' to indicate parallel running of MBIST3 and MBIST4                                                                                                                                                    |

| 22  | 95000000 00080610 | MBIST_CTRL4     | Next pointer set to MBIST5, CSM BIST set to '1' to indicate parallel running of MBIST4 and MBIST5                                                                                                                                                    |

| 23  | 96000000 00080614 | MBIST_CTRL5     | Next pointer set to MBIST6, CSM BIST set to '1' to indicate parallel running of MBIST5 and MBIST6                                                                                                                                                    |

| 24  | 97000000 00080618 | MBIST_CTRL6     | Next pointer set to MBIST7, CSM BIST set to '1' to indicate parallel running of MBIST6 and MBIST7                                                                                                                                                    |

TN1394 - Rev 1 page 12/24

| Nr. | DCF record        | STCU register | note                                                                                              |

|-----|-------------------|---------------|---------------------------------------------------------------------------------------------------|

| 25  | 98000000 0008061C | MBIST_CTRL7   | Next pointer set to MBIST7, CSM BIST set to '1' to indicate parallel running of MBIST7 and MBIST8 |

| 26  | 7F000000 00080620 | MBIST_CTRL8   | Next pointer set to null pointer to indicate end of selftest                                      |

| 27  | 00000201 00080000 | STCU_RUN      | Selftest triggered, MBIST run with PLL, LBIST with RC                                             |

### 1.4.6 STCU bypass

By default there is set STCU\_RUN.BYP = 0 after reset. It causes, that during reset phase, the STCU waits (until hardcoded WDG Time-out) for BIST setup and STCU\_RUN.RUN = 1 to execute the BIST tests.

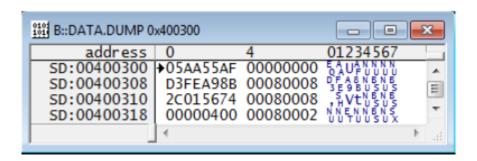

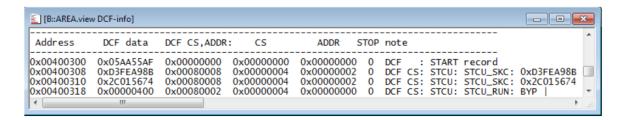

Figure 6. STCU bypass example - memory dump

Figure 7. STCU bypass example - description

Table 8. STCU bypass structure

| Nr. | DCF record        | STCU register    | Note                                                                                                                                                                                                                                                                |

|-----|-------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 05AA55AF 00000000 | DCF start record | DCF start record. The start record must be placed at the beginning of the DCF area in UTEST flash memory to indicate to the device that the following data records must be processed                                                                                |

| 2   | D3FEA98B 00080008 | STCU_KEY1        | Key 1/2 to unlock STCU access                                                                                                                                                                                                                                       |

| 3   | 2C015674 00080008 | STCU_KEY2        | Key 2/2 to unlock STCU access                                                                                                                                                                                                                                       |

| 4   | 00000400 00080000 | STCU_RUN         | 00000400 is the setting of STCU_RUN register. In particular it is set the STCU_RUN[BYP] bit. It means that off-line self-test is completely by-passed and the access to STCU2 is locked until the STCU_SCK register is written according to the request access mode |

#### 1.4.7 STCU setup invalidation

Considering the default configuration shown in the previous paragraph, STCU is bypassed. If the STCU is bypassed it does not accept any extra programming.

TN1394 - Rev 1 page 13/24

Since a final user can't erase the UTEST Flash context, the only possibility to invalidate the bypass STCU configuration consist in altering some STCU Double Words already written in the UTEST. The double words cannot be erased but they can be reprogrammed only in the positions where '1' appear, but ECC to be taken into account. Eight additional bits for every 64-bits are implemented to to have the possibility of single bit correction and double bit detection. See RM for more details.

Moreover, there is the constraint not to introduce ECC errors in the UTest by overwriting its content without care. It is necessary to reprogram both Double Words (@0x00400308 and @0x00400310) in order to invalidate the STCU bypassed and, at the same time, doesn't inject ECC errors.

The new words, which have been specifically chosen not to trigger any ECC error due to the over-write, are: 0xD3FE0889 00000000 and 0x2C015644 00000000.

To recap the re-writing regards the following values:

- 0xD3FE0889 00000000at the address 0x0040 0308 (to overwrite original value: D3FEA98B 0008008)

- 0x2C015644\_00000000 at the address 0x0040\_0310 (to overwrite original value: 2C015674\_0008008)

These values invalid the bypass bit of STCU\_RUN because they are "wrong" keys (due to the ECC error injection it was not possible to find a suitable value to over-write directly the STCU\_RUN value.) and, very important, doesn't trigger any ECC error. With such invalidated DCF records, the STCU doesn't receive any STCU KEY valid sequence and therefore the bypass command does not take effect.

Once the DCF records (writing keys into STCU\_SKC register) were invalidated, all DCF records following the invalid keys are ignored by the STCU. It allows user to prepare and write a new set of DCF records at the end of the original DCF record area – starting with correct keys.

Note:

The STCU setup invalidation can be used not only for bypass skipping, but also to replace current DCF records with new ones or let them invalid only. Thanks to invalidating the last key1 and key2, it is possible proceed with a new STCU setup by adding new set of DCF record staring with valid keys.

**WARNING**: if ECC errors are injected in the UTEST sector, for example by re-writing the same location with not specifically defined data, there is the risk that the sample can't exit the boot phase. In this case the sample becomes useless.

Code below is an exception of a Lauterbach script used for debugging the off-line self-test. It describes how to overwrite the two STCU keys related to the default configuration of the UTest.

TN1394 - Rev 1 page 14/24

Table 9. STCU setup invalidation Lauterbach script excerpt

```

;Lock0 ->TSLock enable UTEST memory

PER.S ANC:0xffFE0010 %LONG 0x3fffffff

;SET_DCF_STCU_STCU_SCK 0xD3FE0889 - key1 overwrite

GOSUB program word 0x00400308 0xD3FE08890000000

;00 - SET DCF STCU STCU SCK 0x2C015644 - key2 overwrite

GOSUB program_word 0x00400310 0x2C01564400000000

;Lock0 ->TSUnLock enable UTEST memory

; PER.S ANC: 0xffFE0010 %LONG 0x0xBffFfFff;

program_word:

entry &address &data

;MCR->PGM =1 enable program memory

PER.S ANC:0xFFFE0000 %LONG 0x610

D.S EA: (&address) %BE %QUAD (&data)

;MCR->EHV=1 program memory

PER.S ANC: 0xFFFE0000 %LONG 0x611

;MCR->EHV=0 program memory

PER.S ANC:0xFFFE0000 %LONG 0x610

;MCR->PGM =0

PER.S ANC:0xfffE0000 %LONG 0x600

RETURN

```

## 1.5 BIST relevant errata

A few errata items are relevant to BIST for SPC570Sx devices.

Device identification for SPC570Sx cut 2.1:

- JTAG\_ID = 0x110A\_2041

- MIDR1 register: MAJOR\_MASK[3:0]: 4'b0001, MINOR\_MASK[3:0]: 4'b0001

Table 10. BIST relevant errata items

| ID          | Module | Title                                                            | Description                                                                                                                                                                                                                   |

|-------------|--------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PS1566      | LBIST  | LBIST: ADC is not converting correctly after LBIST RUN.          | When BIST runs the reset value of some TEST registers are getting changed. Due to this ADC values (for both ADC_0 and ADC_B) are lower than the expected value.                                                               |

|             |        |                                                                  | In device's RM, STCU_PLL_CFG (PLL configuration) value is wrongly provided for configuring PLL at 73.3MHz for Offline MBIST run.                                                                                              |

| DAN-0043391 | STCU2  | STCU2: PLL configuration<br>needs to be changed for<br>MBIST run | A too high PLL frequency might lead to the corruption of the logic of Peripheral Clock Divider (AIPS0), which wakes up – after Self Test sequence completion – with a wrong setting (dividing AIPS0 clock by 1 instead of 2). |

|             |        |                                                                  | Recommended value for PLL frequency for Offline MBIST run is 40MHz: maximum allowed value is 60MHz.                                                                                                                           |

|             |        |                                                                  | The issue is present during offline self-test.                                                                                                                                                                                |

| DAN-0045775 | BIST   | BIST: Unexpected ESR0 signal in case of executing FULL BIST      | PAD[47] when configured as ESR0 through DCF, shows different behavior at the end of the functional reset.                                                                                                                     |

|             |        |                                                                  | 1) running the MBIST Only, ESR0 is deasserted at the end of functional reset                                                                                                                                                  |

TN1394 - Rev 1 page 15/24

| ID        | Module | Title                                  | Description                                                                                                                                                                                                                                                                                                                 |

|-----------|--------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |        |                                        | 2) running offline self-test (with LBIST included->FULL BIST), the ESR0 is deasserted at the end of destructive phase (just after BIST execution) and then asserted at the beginning of the next functional reset                                                                                                           |

| ERR008056 | LBIST  | LBIST: Flash must be idle during LBIST | Logic Built-In Self-Test (LBIST) should only be performed on the flash partition while the flash is in the idle state. LBIST operations must not be initiated for the LBIST partition including flash while flash program or erase operations are in progress. This information was not included in the user documentation. |

## 1.5.1 BIST errata PS1566

In case of LBIST is executed, then errata PS15566 workaround to be applied in user SW to avoid improper ADC conversions.

Table 11. Errata PS15566

| ID     | Workaround                                                                                                      |

|--------|-----------------------------------------------------------------------------------------------------------------|

|        | After LBIST run and before ADC initialization, restore RESET value of non-user TEST registers as default by SW. |

|        | Below the listing of the SW statements to execute to restore default configuration:                             |

|        | * ((vuint32_t *) 0xFFE38000) = 0x03020100;                                                                      |

|        | * ((vuint32_t *) 0xFFE38004) = 0x07060504;                                                                      |

|        | * ((vuint32_t *) 0xFFE38008) = 0x0B0A0908;                                                                      |

|        | * ((vuint32_t *) 0xFFE3800C) = 0x0F0E0D0C;                                                                      |

|        | * ((vuint32_t *) 0xFFE38010) = 0x13121110;                                                                      |

|        | * ((vuint32_t *) 0xFFE38014) = 0x17161514;                                                                      |

|        | * ((vuint32_t *) 0xFFE38018) = 0x1B1A1918;                                                                      |

|        | * ((vuint32_t *) 0xFFE3801C) = 0x1F1E1D1C;                                                                      |

|        | * ((vuint32_t *) 0xFFE38020) = 0x23222120;                                                                      |

|        | * ((vuint32_t *) 0xFFE38024) = 0x27262524;                                                                      |

|        | * ((vuint32_t *) 0xFFE38028) = 0x2B2A2928;                                                                      |

|        | * ((vuint32_t *) 0xFFE3802C) = 0x2F2E2D2C;                                                                      |

| PS1566 | * ((vuint32_t *) 0xFFE38030) = 0x33323130;                                                                      |

|        | * ((vuint32_t *) 0xFFE38034) = 0x37363534;                                                                      |

|        | * ((vuint32_t *) 0xFFE38038) = 0x3B3A3938;                                                                      |

|        | * ((vuint32_t *) 0xFFE3803C) = 0x3F3E3D3C;                                                                      |

|        | * ((vuint32_t *) 0xFFE04000) = 0x03020100;                                                                      |

|        | * ((vuint32_t *) 0xFFE04004) = 0x07060504;                                                                      |

|        | * ((vuint32_t *) 0xFFE04008) = 0x0B0A0908;                                                                      |

|        | * ((vuint32_t *) 0xFFE0400C) = 0x0F0E0D0C;                                                                      |

|        | * ((vuint32_t *) 0xFFE04010) = 0x13121110;                                                                      |

|        | * ((vuint32_t *) 0xFFE04014) = 0x17161514;                                                                      |

|        | * ((vuint32_t *) 0xFFE04018) = 0x1B1A1918;                                                                      |

|        | * ((vuint32_t *) 0xFFE0401C) = 0x1F1E1D1C;                                                                      |

|        | * ((vuint32_t *) 0xFFE04020) = 0x23222120;                                                                      |

|        | * ((vuint32_t *) 0xFFE04024) = 0x27262524;                                                                      |

|        | * ((vuint32_t *) 0xFFE04028) = 0x2B2A2928;                                                                      |

TN1394 - Rev 1 page 16/24

| ID | Workaround                                 |  |  |

|----|--------------------------------------------|--|--|

|    | * ((vuint32_t *) 0xFFE0402C) = 0x2F2E2D2C; |  |  |

|    | * ((vuint32_t *) 0xFFE04030) = 0x33323130; |  |  |

|    | * ((vuint32_t *) 0xFFE04034) = 0x37363534; |  |  |

|    | * ((vuint32_t *) 0xFFE04038) = 0x3B3A3938; |  |  |

|    | * ((vuint32_t *) 0xFFE0403C) = 0x3F3E3D3C; |  |  |

## 1.5.2 BIST errata DAN-0043391

Table 12. Errata DAN-0043391

| ID          | Workaround                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAN-0043391 | STCU_PLL_CFG configuration has to be changed from 0x06020038 00080010 to 0x0C02003C 00080010 to configure PLL at 40MHz or lower.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | The duration of MBIST run increases consequently, according to the selected algorithm. Total Offline Self Test sequence contains anyway also LBIST, which is not affected by PLL frequency, since it is run using on-chip RC oscillator.                                                                                                                                                                                                                                                                                                                                                     |

|             | NOTE: Running Offline MBIST at a lower speed with respect to the maximum speed does not affect ASIL D targets for the hardware architectural metrics of the device. From Safety Analysis (FMEDA) point of view, Error Correction Code (ECC) is the primary Safety Mechanism against memory faults: on-field MBIST (Offline or Online) must be run only to prevent accumulation of faults, which would negatively impact diagnostic coverage of the primary safety mechanism (ECC). ECC does not cover multiple bit faults, it just corrects single bit errors and detects double bit errors. |

The errata workaround is already applied in this document and all examples.

#### 1.5.3 BIST errata DAN-0045775

Table 13. Errata DAN-0045775

| ID          | Workaround                                                                                     |

|-------------|------------------------------------------------------------------------------------------------|

| DAN-0045775 | Application has to ignore the spurious ESR0 toggling during case 2 (LBIST included->FULL BIST) |

## 1.5.4 BIST errata ERR008056

Table 14. Errata ERR008056

| ID | Workaround                                                                                                                                                           |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Flash must be in an idle state for LBIST. Ensure that flash is not performing program, erase, or flash user accessible test mode operations when LBIST is initiated. |

## 1.6 BIST performance

Practical measurements are performed with BIST setups mentioned in Section 1.4 BIST setup examples using standard evaluation board and oscilloscope for time measurement. An application is flashed, which sets PA[0] to output mode (causes port pin transition level High -> Low) in the very first startup instructions. Starting point for time measurement here is PORST transition to high (see Figure 2. PORST pin behavior), which is better measurable than power on voltage ramp-up.

TN1394 - Rev 1 page 17/24

Table 15. BIST related practical measurement results

| # | Setup                                           | Time [ms] | Note:                                                                                                |

|---|-------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------|

| 1 | Original                                        | 8.3       | no added DCF records (see<br>Figure 8. Original device measurement<br>result – no added DCF records) |

| 2 | LBIST only (parallel mode)                      | 10.0      | PLL 18.3MHz                                                                                          |

| 3 | MBIST only (parallel mode)                      | 20.5      | PLL 40MHz                                                                                            |

| 4 | LBIST and MBIST (sequential and parallel modes) | 48.4      | RC 16MHz + PLL40MHz                                                                                  |

| 5 | STCU bypass                                     | 0.5       |                                                                                                      |

Figure 8. Original device measurement result – no added DCF records

#### Probes:

A1 – yellow PA[0] port pin (pin 2 of eTQFP64 package)

A2 – green PORST signal (pin 44 of eTQFP64 package)

A3 – violet 1.2 V power supply

A4 - red 3.3 V power supply

TN1394 - Rev 1 page 18/24

## 2 Conclusion

Flash.

The document describes how to configure and use built-in self-tests (BIST) in SPC570Sx device. Typical usage of the BIST is to detect latent failures before the user code is executed. Two different BISTs can be used: LBIST (logic BIST) and MBIST (memory BIST). There are available only off-line BISTs, which can be executed after power-on reset, if the BISTs have been configured properly in advance in UTEST Flash by DCF records. It shows how to modify BISTs setup practically even the DCF records are already stored in nonerasable UTEST

It provides three typical BIST configurations together with practical performance measurements.

TN1394 - Rev 1 page 19/24

# **Revision history**

Table 16. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 05-May-2022 | 1        | Initial release. |

TN1394 - Rev 1 page 20/24

## **Contents**

| 1    | Built                                   | -In self | tests                                       | 2  |

|------|-----------------------------------------|----------|---------------------------------------------|----|

|      | 1.1                                     | Reset    | sequence and BIST execution                 | 2  |

|      | 1.2                                     | System   | n status and configuration module (SSCM)    | 4  |

|      |                                         | 1.2.1    | DCF record description                      | 5  |

|      |                                         | 1.2.2    | DCF records location                        | 6  |

|      | 1.3                                     | Self tes | st control unit (STCU2)                     | 6  |

|      |                                         | 1.3.1    | Self test control unit (STCU2) introduction | 6  |

|      |                                         | 1.3.2    | BIST watchdog                               | 7  |

|      |                                         | 1.3.3    | BIST clocking                               | 7  |

|      |                                         | 1.3.4    | STCU LBIST description                      | 8  |

|      |                                         | 1.3.5    | BIST MBIST description                      | 9  |

|      | 1.4                                     | BIST s   | etup examples                               | 9  |

|      |                                         | 1.4.1    | MBIST example setup                         | 9  |

|      |                                         | 1.4.2    | MBIST evaluation                            | 10 |

|      |                                         | 1.4.3    | LBIST example setup                         | 10 |

|      |                                         | 1.4.4    | LBIST evaluation                            | 11 |

|      |                                         | 1.4.5    | Both LBIST and MBIST example setup          | 12 |

|      |                                         | 1.4.6    | STCU bypass                                 | 13 |

|      |                                         | 1.4.7    | STCU setup invalidation                     | 13 |

|      | 1.5                                     | BIST re  | elevant errata                              | 15 |

|      |                                         | 1.5.1    | BIST errata PS1566                          | 16 |

|      |                                         | 1.5.2    | BIST errata DAN-0043391                     | 17 |

|      |                                         | 1.5.3    | BIST errata DAN-0045775                     | 17 |

|      |                                         | 1.5.4    | BIST errata ERR008056                       | 17 |

|      | 1.6                                     | BIST p   | performance                                 | 17 |

| 2    | Conc                                    | clusions | s                                           | 19 |

| Rev  | ision l                                 | history  |                                             | 20 |

| Cor  | ntents                                  |          |                                             | 21 |

| List | of tab                                  | oles     |                                             | 22 |

|      |                                         |          |                                             |    |

|      | · - · · · · · · · · · · · · · · · · · · |          |                                             |    |

## **List of tables**

| Table 1.  | DCF record description                            | 5  |

|-----------|---------------------------------------------------|----|

| Table 2.  | Series of DCF records in UTEST Flash memory       | 6  |

| Table 3.  | MBIST example setup                               |    |

| Table 4.  | MBIST results                                     | C  |

| Table 5.  | LBIST example setup                               | C  |

| Table 6.  | LBIST results                                     | 11 |

| Table 7.  | LBIST and MBIST example setup                     | 12 |

| Table 8.  | STCU bypass structure                             | 13 |

| Table 9.  | STCU setup invalidation Lauterbach script excerpt |    |

| Table 10. | BIST relevant errata items                        | 5  |

| Table 11. | Errata PS15566                                    |    |

|           |                                                   |    |

| Table 13. |                                                   |    |

| Table 14. | Errata ERR008056                                  | 7  |

|           | BIST related practical measurement results        |    |

| Table 16. | Document revision history                         | 20 |

# **List of figures**

| Figure 1. | Reset sequence                                            | 3 |

|-----------|-----------------------------------------------------------|---|

| Figure 2. | PORST pin behavior                                        | 4 |

| Figure 3. | DCF record structure                                      | 5 |

| Figure 4. | STCU2 block diagram                                       | 7 |

| Figure 5. | LBIST structure                                           | 8 |

| Figure 6. | STCU bypass example – memory dump                         | 3 |

| Figure 7. | STCU bypass example – description                         | 3 |

| Figure 8. | Original device measurement result – no added DCF records | 8 |

|           |                                                           |   |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics – All rights reserved

TN1394 - Rev 1 page 24/24