## SPC58x Ethernet FIFO access and IMA error injection

### Introduction

This document aims at showing an example of how to program the embedded Ethernet controller available on the spc58x automotive microcontroller (MCU) to access its own internal FIFO by using the slave debug port and, in specific, of how to inject an error through the indirect memory access (IMA) unit checking the error from the memory error management unit (MEMU).

The example code reported in this document has been tested on the SPC584Cx/SPC58ECx MCU.

#### 1 Ethernet controller overview

SPC58x automotive microcontrollers feature a quality-of-service 10/100 Mbit/s Ethernet peripheral that implements the medium access control (MAC) layer plus several internal modules for standard and advanced network features that can be summarized into the following categories:

- MAC core and MAC transaction layer (MTL)

- DMA engine

- · SMA interface

- MAC management counters

- Power management block (PMT)

### 1.1 MAC transaction layer

The MAC transaction layer (MTL) provides the FIFO memory interface to buffer and regulate the packets between the application system memory and the MAC. The MTL block consists of Tx FIFO and Rx FIFO managed by the block and not exposed to the application software. As a result, a software driver cannot access them directly unless for implementing a dedicated procedure as detailed in the next chapter.

Tx DMA

Channel

TSO Engine

Rx DMA

Channel

Channel

MTL Tx FIFO

Controller

MTL Rx FIFO

Controller

MTL CSR

MTL CSR

Figure 1. Controller block diagram for MTL and FIFO

For further details about the Ethernet controller, for instance FIFOs size, programming and configuration, refer to the device reference manual.

### 1.2 Slave mode access

The Ethernet module supports the debug access to the FIFO memory, and the Tx and Rx FIFO queues memory is accessible through the internal slave port as described in the reference manual.

By enabling this mode the user can program the entire selected Tx memory to Tx FIFO queue 0 and the Rx memory to Rx FIFO queue 0.

The FIFO will work in store-and-forward mode, for example the MTL pops out the packet towards the MAC only when the complete packet is stored in the queue.

The offload features such as checksum offload engine and IEEE timestamp should not be enabled with this feature.

The following sections will describe how to write and read data through a slave interface on a FIFO.

TN1332 - Rev 1 page 2/14

#### 1.2.1 Writing to the Tx FIFO

The following code configures and writes a pattern in the Tx FIFO in slave debug mode.

```

/* Configuration */

reg->MTL_DBG_CTL.B.DBGMOD = 1;

reg->MTL_DBG_CTL.B.FDBGEN = 1;

reg->MTL DBG CTL.B.RSTALL = 1;

reg->MTL_DBG_CTL.B.BYTEEN = 3;

reg->MTL DBG CTL.B.PKTSTATE = 0;

/* Write a pattern (fill 4KiB FIFO) */

for (i=0; i < FIFO_ELEMENT_N; i++) {

limit = 10;

/* Complete data word in 64-bit mode. */

for (j = 0; j < 2; j++) {

/* Optionally it could be useful to look at the LOCR bit

for monitoring the FIFO */

/\!\!\!\!\!\!^{\star} To better monitor the FIFO elements, store a pattern ^{\star}/\!\!\!\!

reg->MTL FIFO DEBUG DATA.B.FDBGDATA = FIFO PATTERN+count;

count++;

/* Enable the Writing access to the TX FIFO */

reg->MTL DBG CTL.B.FIFOSEL = 0; // 0 TX FIFO, 3 RX FIFO

reg->MTL DBG CTL.B.FIFORDEN = 0;

reg->MTL_DBG_CTL.B.FIFOWREN = 1;

/* Wait for FIFOBUSY in the status register */

while ((reg->MTL DBG STS.B.FIFOBUSY == 1) && limit)

limit--;

```

#### 1.2.2 Reading from a FIFO

The following code reads from the Rx FIFO and saves the content in the user buffer User\_FIFO\_data.

```

/* READING FROM FIFO IN DEBUG MODE */

reg->MTL DBG CTL.B.DBGMOD = 1;

reg->MTL DBG CTL.B.FDBGEN = 1;

for (i=0; i < FIFO ELEMENT N; i++) {

limit = 10;

for (j = 0; j < 2; j++) {

// 64bit

reg->MTL DBG CTL.B.FIFOSEL = 0; // 0 TX FIFO, 3 RX FIFO

reg->MTL_DBG_CTL.B.FIFORDEN = 1;

reg->MTL DBG CTL.B.FIFOWREN = 0;

while ((reg->MTL_DBG_STS.B.FIFOBUSY == 1) && limit)

limit--;

/* Store the FIFO elements in a user array */

if (limit)

User FIF0 data[count] =

reg->MTL FIFO DEBUG DATA.B.FDBGDATA;

count++;

}

```

TN1332 - Rev 1 page 3/14

#### 2 IMA overview

Indirect memory access (IMA) refers to the activity of accessing any volatile memory for the purpose of reading or modifying data, or both, including ECC check bits.

This capability is mandatory to verify the ECC functionality.

The SPC584Cx/SPC58ECx MCU provides two mechanisms for IMA:

- The built-in CPU E2E\_ECC test capability provides a path for accessing data and ECC check bits from some SRAM arrays.

- An IMA controller module provides registers for selecting, reading and writing memory array including both data and relevant ECC bits.

Despite other peripherals where the application can access the shared memory, in case of the Ethernet controller, where the FIFO cannot be accessed by the software, a dedicated function has been developed to verify this feature.

#### 2.1 Read and write functions

This chapter describes how to perform accesses through the IMA.

#### 2.1.1 IMA read access

In order to perform an IMA read access the user must follow the sequence below:

- Unlock IMA read access

- Based on the memory address to be accessed, write the IMA\_SLCT.ARRAY\_SLCT and IMA\_SLCT.ROW\_SLCT fields

- Set the IMA CTRL.READ bit

- Set IMA\_ENABLE.EN bit to initiate read access. This bit will be self cleared after two clocks.

- · Wait an appropriate number of clocks depending on the speed of the selected memory

- Read data from IMA\_READ\_DATA registers

The following code implements the operations described above.

```

static void IMA Read(unsigned int slct, unsigned int row)

IMA.READ UNLOCK.B.REA KEY = 0xF06AB5BC;

IMA.READ UNLOCK.B.READ KEY = 0 \times 14081B56;

if (IMA.STATUS.B.READ LOCK == 0) {

IMA.SLCT.B.ARRAY SLCT = slct;

IMA.SLCT.B.ROW SLCT = row;

IMA.CTRL.B.READ = 1;

IMA.ENABLE.B.EN = 1;

while (IMA.ENABLE.B.EN);

IMA Read Data Buffer[0] = IMA.READ DATA 0.R;

IMA_Read_Data_Buffer[1] = IMA.READ_DATA_1.R;

IMA Read Data Buffer[2] = IMA.READ DATA 2.R;

IMA Read Data Buffer[3] = IMA.READ DATA 3.R;

IMA Read Data Buffer[4] = IMA.READ DATA 4.R;

IMA.SLCT.B.ARRAY SLCT = 0;

IMA.SLCT.B.ROW SLCT = 0;

IMA.READ UNLOCK.B.READ KEY = 0 \times 000000000;

```

TN1332 - Rev 1 page 4/14

#### 2.1.2 IMA write access

In order to perform an IMA write access the user must follow the sequence below:

- Unlock IMA write access

- Based on the memory address to be accessed, write the IMA\_SLCT.ARRAY\_SLCT and IMA\_SLCT.ROW\_SLCT fields

- Write the data in IMA\_WRITE\_DATA registers

- Clear the IMA\_CTRL.READ bit

- Set IMA ENABLE.EN bit to initiate write access. This bit will be self cleared after two clocks.

- Wait an appropriate number of clocks depending on the speed of the selected memory

- Access by a master (e.g. CPU) to the selected memory location to detect the ECC error

- Check the relevant MEMU register to verify the ECC error is reported

The following code implements the operations described above and it will be invoked by IMA\_Test function to inject an error.

```

static void IMA Write Err(unsigned int slct, unsigned int row,

unsigned int mask_0, unsigned int mask_1,

unsigned int mask 2)

IMA.WRITE_UNLOCK.B.WRITE_KEY = 0x04A43F95;

IMA.WRITE UNLOCK.B.WRITE KEY = 0xE4A9EBF7;

if (IMA.STATUS.B.WRITE LOCK == 0) {

IMA.SLCT.B.ARRAY SLCT = slct;

IMA.SLCT.B.ROW SLCT = row;

IMA Write Data Buffer[0] = IMA Read Data Buffer[0]^mask 0;

IMA_Write_Data_Buffer[1] = IMA_Read_Data_Buffer[1]^mask_1;

IMA Write Data Buffer[2] = IMA Read Data Buffer[2]^mask 2;

IMA_Write_Data_Buffer[3] = IMA_Read_Data_Buffer[3];

IMA Write Data Buffer[4] = IMA Read Data Buffer[4];

IMA.WRITE_DATA_0.R = IMA_Write_Data_Buffer[0];

IMA.WRITE DATA 1.R = IMA Write Data Buffer[1];

IMA.WRITE DATA 2.R = IMA Write Data Buffer[2];

IMA.WRITE_DATA_3.R = IMA_Write_Data_Buffer[3];

IMA.WRITE DATA 4.R = IMA Write Data Buffer[4];

IMA.CTRL.B.READ = 0;

IMA.ENABLE.B.EN = 1;

while (IMA.ENABLE.B.EN) {};

IMA.SLCT.B.ARRAY SLCT = 0;

IMA.SLCT.B.ROW SLCT = 0;

IMA.WRITE UNLOCK.B.WRITE KEY = 0 \times 000000000;

```

TN1332 - Rev 1 page 5/14

### 2.2 Error injection

This section reports the defined commands and the IMA\_Test function invoked in the application.

The FIFO has been filled with a pattern sequence and the IMA\_Test function reads the data from the memory region that maps the internal FIFO and then injects a single-bit error in the 62nd position of the 2nd data word. Note that IMA performs a 64-bit access.

#### Where:

```

#define IMA_ARRAY_ELEMENT 5

unsigned int IMA_Read_Data_Buffer[IMA_ARRAY_ELEMENT];

unsigned int IMA_Write_Data_Buffer[IMA_ARRAY_ELEMENT];

unsigned int Tx_Fifo_data[128];

#define FIFO_PATTERN 0x12345670

#define FIFO_ELEMENT_MAX 64 /* 4KiB*/

#define FIFO_ELEMENT_N 8

#define IMA_ARRAY_ETH_TX_O 29

#define IMA_ARRAY_ETH_TX_E 31

```

The table below reports the ethernet SRAM arrays accessible via IMA, from the device reference manual:

| IMA array select | Block    | Function         | SPC584Cx/SPC58ECx |      |          |

|------------------|----------|------------------|-------------------|------|----------|

|                  |          |                  | Words             | Bits | ECC bits |

| 28               | Ethernet | Ethernet ODD RX  | 512               | 76   | 75-64    |

| 29               |          | Ethernet ODD TX  | 256               | 76   | 75-64    |

| 30               |          | Ethernet EVEN RX | 512               | 76   | 75-64    |

| 31               |          | Ethernet EVEN TX | 256               | 76   | 75-64    |

Table 1. Ethernet IMA array select

TN1332 - Rev 1 page 6/14

### 3 Application

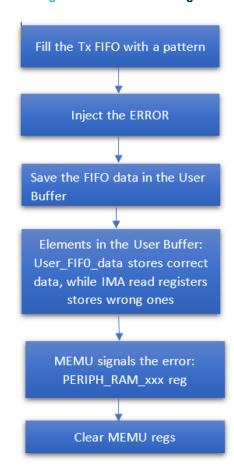

After the Ethernet is successfully initialized, the IMA test can be started. The following diagram shows the flow of the functions explained in the previous chapters.

The Tx FIFO is filled with a known pattern, then the error is injected and the results are visible in the user buffer and in the IMA read registers.

Figure 2. IMA test flow diagram

In case of a single-bit error, i.e. correctable error, in a certain memory location, the error is detected and the data is corrected by the ECC logic before it is provided to the requesting master. As a result, the memory location still holds the corrupted data, as it can be verified by performing a new read operation by the IMA on the same memory location.

Note that a new read access by a master, e.g. the CPU, on the same memory location generates a new single-bit error detection (and the correction of the data provided to the requesting master) with the reporting to the MEMU but in this case the MEMU will drop the error because the address and the syndrome are the same as the error already recorded in the MEMU reporting table. On the contrary, if the valid bit PERIPH\_RAM\_CERR\_STS0.VLD was previously cleared, the error is recorded again.

The following code checks inside the remaining FIFO content.

```

IMA_Read(IMA_ARRAY_ETH_TX_E, 0);

IMA_Read(IMA_ARRAY_ETH_TX_O, 0);

IMA_Read(IMA_ARRAY_ETH_TX_E, 1);

IMA_Read(IMA_ARRAY_ETH_TX_E, 1);

IMA_Read(IMA_ARRAY_ETH_TX_O, 1);

IMA_Read(IMA_ARRAY_ETH_TX_E, 2);

```

TN1332 - Rev 1 page 7/14

### 4 Memory error management unit (MEMU)

The MEMU is responsible for collecting and reporting error events associated with the error correction code (ECC) logic which is also used on peripheral memories.

The MEMU receives an error signal which causes an event to be recorded and the corresponding error flags to be set and reported to the fault collection and control unit (FCCU).

In the example, inserting an error in the 2nd word, the MEMU will report the error after the reading of the first word and the address is the address of the double word.

This behavior is shown in Figure 3 below: error inserted in the 2nd word of the 3rd row of Tx FIFO EVEN (0x12345679) changed in 0x52345679).

After reading the 1st word (data = 0x12345678), MEMU reports the error with address (0x4F0A0000+0x10 where 0x10 is the offset of the 3rd double word).

B::PER, "MEMU" 00 SYS\_RAM\_CERR\_ADDR8 00000000 ERR\_ADD 00000000 SYS\_RAM\_CERR\_STS9 00000000 VLD 00: Entry in table is invalid BAD\_BIT 00 00000000 ERR\_ADD 00000000 SYS\_RAM\_CERR\_ADDR9 SYS\_RAM\_UNCERR\_STS 00000000 00: Entry in table is invalid VLD 00000000 SYS\_RAM\_UNCERR\_ADDR 00000000 ERR\_ADD SYS\_RAM\_OFLWO 00000000 OFLW 00000000 SYS\_RAM\_OFLW1 00000000 OFLW 00000000 00000000 SYS\_RAM\_OFLW2 OFLW 00000000 SYS\_RAM\_OFLW3 00000000 OFLW 00000000 01: Entry in table is valid PERIPH\_RAM\_CERR\_STS0 800000FF VLD BAD\_BIT FF PERIPH\_RAM\_CERR\_ADDR0 4F0A0000 ERR\_ADD 4F0A0000 PERIPH\_RAM\_CERR\_STS1 800000FF 01: Entry in table is valid VLD BAD\_BIT ERR\_ADD PERIPH\_RAM\_CERR\_ADDR1 4F0A0010 4F0A0010 PERIPH\_RAM\_UNCERR\_STS 00000000 VLD 00: Entry in table is invalid PERIPH\_RAM\_UNCERR\_ADDR 00000000 00000000 ERR ADD PERIPH\_RAM\_OFLWO 00000000 00000000 OFLW

Figure 3. MEMU status

The code below checks the Address fields:

TN1332 - Rev 1 page 8/14

## **Appendix A Other information**

## A.1 Acronyms and abbreviations

Table 2. Acronyms and abbreviation table

| Terms | Meaning                      |

|-------|------------------------------|

| DMA   | Direct memory access         |

| FIFO  | First In – First Out         |

| IMA   | Indirect memory address      |

| MAC   | Medium access control        |

| MTL   | MAC transaction layer        |

| MEMU  | Memory error management unit |

## A.2 Reference documents

• SPC58EHx/SPC58NHx 32-bit Power architecture microcontroller reference manual

TN1332 - Rev 1 page 9/14

## **Revision history**

Table 3. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 02-Sep-2020 | 1       | Initial release. |

TN1332 - Rev 1 page 10/14

## **Contents**

| 1   | Ethe         | Ethernet controller overview |                           |    |  |  |

|-----|--------------|------------------------------|---------------------------|----|--|--|

|     | 1.1          | MAC transaction layer        |                           |    |  |  |

|     | 1.2          | Slave r                      | mode access               | 2  |  |  |

|     |              | 1.2.1                        | Writing to the Tx FIFO    | 3  |  |  |

|     |              | 1.2.2                        | Reading from a FIFO       | 3  |  |  |

| 2   | IMA overview |                              |                           | 4  |  |  |

|     | 2.1          | Read a                       | and write functions       | 4  |  |  |

|     |              | 2.1.1                        | IMA read access           | 4  |  |  |

|     |              | 2.1.2                        | IMA write access          | 5  |  |  |

|     | 2.2          | Error ir                     | njection                  | 6  |  |  |

| 3   | Appl         | ication                      |                           | 7  |  |  |

| 4   | Mem          | ory err                      | or management unit (MEMU) | 8  |  |  |

| App | endix        | A Oth                        | ner information           | 9  |  |  |

|     | <b>A.1</b>   | Acrony                       | ms and abbreviations      | 9  |  |  |

|     | <b>A.2</b>   | Refere                       | nce documents             | 9  |  |  |

| Rev | ision        | history                      |                           | 10 |  |  |

## **List of tables**

| Table 1. | Ethernet IMA array select       | 6 |

|----------|---------------------------------|---|

| Table 2. | Acronyms and abbreviation table | ć |

| Table 3. | Document revision history       | C |

TN1332 - Rev 1 page 12/14

# **List of figures**

| Figure 1. | Controller block diagram for MTL and FIFO | 2 |

|-----------|-------------------------------------------|---|

| Figure 2. | IMA test flow diagram                     | 7 |

| Figure 3. | MEMU status                               | 8 |

TN1332 - Rev 1 page 13/14

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2020 STMicroelectronics - All rights reserved

TN1332 - Rev 1 page 14/14