## The BlueNRG-LP radio controller

#### Introduction

The BlueNRG-LP BLE controller is a programmable automate, which can act as a master or a slave node compliant up to the Bluetooth Low Energy 5.2 standard. It is an evolution of the previous architecture (BlueNRG-2) keeping the same functionalities and introducing new features that lose even more the bonding between hardware and CPU.

The BLE controller is a coprocessor intended to perform transmission and reception operations without the direct control of the CPU following the instructions included inside some predefined linked lists in RAM. Then, the task of a dedicated link layer firmware is to fill these lists in advance. This allows the controller to start a transaction directly at low power mode exit while the CPU is still booting.

Typically, a processor interrupt service routine runs at the end of every transmitted or received packet in order to prepare/modify the linked lists in RAM or inform the host about changes. When the ISR execution time is a key point, the controller offers the possibility to check if there is enough time to complete the planned transmission/reception and to check the coherency of the RAM lists preventing the reading of not updated data. Furthermore, the controller reads its configuration in three different consecutive phases giving to the CPU the maximum computation time.

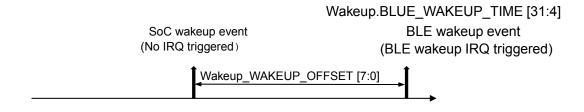

The internal sequence of autonomous actions about the transmission or reception is triggered by a timer event that can either wake up the device from deep sleep or not.

A free running counter driven by the internal or external slow clock is always active during sleep mode and provides the absolute time used as reference to schedule the controller activity. It is located in a programmable wake-up block that is also in charge to execute the request from the radio to go into sleep. The CPU is able to program the wake-up block accessing specific registers through the APB interface of the controller.

The BLE controller embeds the following main components:

- A sequencer, which synchronizes the overall link controller. The sequencer controls all the steps from the beginning (one timer trigger) to the last step (interrupt sent to the CPU).

- · An AHB arbiter block which allows the communication with an SOC.

- A channel incrementer block which implements in hardware the two-channel incrementing algorithm described in Bluetooth core specification 5.2.

- An AES hardware engine which is able to manage simultaneously three processes:

- An "On the fly" data packet payload encryption or decryption.

- An AES 128-bit manual encryption.

- An LE privacy resolution engine which complies with Bluetooth core specification 5.2.

- A transmit block which takes care of the framing of the advertise or data packet. It supports all coded PHY frame format (with S=2 and S=8) and uncoded PHY frame format (1 Mbps and 2 Mbps). It supports data packet length and advertise packet length up to 255 bytes. The transmit block generates 'on the fly' the CRC and the data whitening.

- A receive block which takes care of the data payload de-whitening and the CRC checking for an advertise or data packet. It supports indirectly all coded PHY frame format (with S=2 and S=8) and uncoded PHY frame format (1 Mbps and 2 Mbps). The receive block supports data packet length and advertise packet length up to 255 bytes. It extracts all the header information to ease the sequencer processing.

- An APB main block that manages all the read/write requests coming from the SOC.

- An SN/NESN automatic mechanism, which is automatically disabled when a sequence skip is requested or when no receive buffer in available in RAM.

# 1 Functional description

Three possible timers (wake-up timer, timer1 and timer2) trigger the start of the controller internal sequence. Wake-up timer and timer1 are based on the absolute machine time. Timer2 is only relative to the end of the previous transmitted or received packet. The wake-up timer is the only timer that is always on during the sleep mode, so it is the only one able to wake up the system when the digital power supply is switched off.

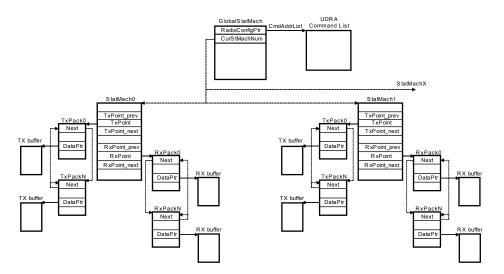

Each time a trigger event is sent to the BLE controller, the sequencer fetches specific tables in RAM to get the required information to know what to configure about the radio and which sequence to start (RX or TX).

There are several types of tables:

- The GlobalStatMach: this table is unique. As the name suggests, it contains valid information for each active link on the device.

- The StatMach: one table for each active link (up to 128 supported by the hardware), called in this context state machine. It contains information such as: the channel, the transmit power and the link to the current action to be performed by the radio, defined by a TxRxPack.

- The TxRxPack: one table for a packet in RX or in TX. There is no predefined number of these tables. They are organized in link lists where each packet points to the next one.

- The DataPack table corresponding to the data buffers pointed by the DataPtr in the TxRxPack. It contains the PDU section of the Bluetooth packet.

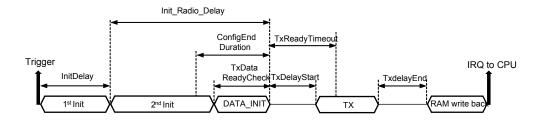

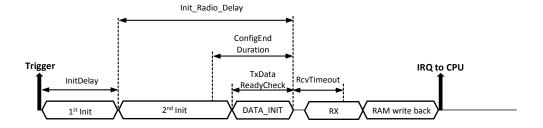

After the BLE controller is triggered by one of the three timers, the following six actions define the usual sequence related to a radio transaction.

- The BLE controller reloads its configuration from retention RAM in order to restore its state (this state might have been modified by the CPU during its interrupt: see action 6 in this list). The link controller reloads its configuration in more separated phases giving more computation time to the CPU.

- 2. The BLE controller requests the radio access. This action occurs in parallel when action 1 is running.

- 3. Data transmission or data reception.

- 4. After the end of all previous actions, the BLE controller writes back its configuration into several tables in RAM and issues an interrupt to the CPU. Depending on internal interrupt enable configuration, the link controller may increase its interrupt (which is connected to the CPU).

- 5. On interrupt detection, the CPU starts an interrupt service routine (ISR) which checks the controller interrupt status register, reads the configuration saved by the controller in RAM and reads the data received PDU in RAM (in case of valid PDU packet reception). The change from one link state machine to another one is defined by a dedicated function of the ISR, which changes the "CurStMachNum" variable value in the GlobStatMach table.

- 6. After all the previous activities have ended, the CPU may ask the wake-up block to send a sleep request to the power manager block (PM) to go into sleep mode.

RM0480 - Rev 2 page 2/80

# 2 Radio resource manager (RRM)

The radio resource manager (RRM) is the block that manages the requests performed by the BLE controller and the CPU to access the radio resources. The requests pass through a semaphore and only one of the two can take control of the radio at a time. The arbitration behaves as follows:

- check the priority value to choose between the BLE controller or the CPU.

- if the same, then the arbiter eliminates the requester that has been served more recently.

The two controllers can request access to the radio resources through a dedicated port:

- Port 0 for the BLE controller

- Port 1 for the CPU (it is a virtual port in this case)

By default, neither the BLE controller nor the CPU has access to the radio. A contributor (BLE or CPU) needs to request a token. The token is requested by software for the CPU. It is done by hardware for the BLE controller each time a timer trig event starts a sequence. Nevertheless, the firmware can release the token granted by the BLE link layer writing inside the CMDREG APB register. Once the requester has the token, its port is granted and it can access the radio resources.

#### 2.1 UDRA

The unified direct register access block allows the software to prepare some commands in a command link list located in the retention RAM. Those commands execute read from and write into the radio registers.

Some interruptions are linked to the UDRA block in the RRM:

- on a command start event

- · on a command end event.

The main goal of this block is to allow the BLE controller to reinitialize the radio registers after a low power mode sequence to start an RF communication while the CPU is still being booted.

#### 2.1.1 UDRA RAM command link list

The mapping in RAM for the commands for each port is the following:

- the RadioConfigPtr field of the GlobalStateMach contains the start address of the command start list

- the command start list is a 32-bit element table containing the first command addresses of each command number of each port (more command lists are available for each port)

- each command of each port contains some read and/or write actions on radio registers.

The RadioConfigPtr value is loaded by the RRM-UDRA automatically when the radio controller reset is released. If the software did not initialize this RAM address supposed to point on the command\_start\_list address before this first automatic load, a "reload pointer" command is available by writing 1 in the UDRA\_CTRL0[0] APB register (this bit is auto-cleared immediately).

Note:

The RadioConfigPtr pointer value loaded and used by the RRM-UDRA block can be read in the UDRA\_RADIO\_CFG\_PTR APB register.

The port mapping has been defined as follows:

- 2 ports (port0=BLE, port1= VP CPU)

- port0 supports 3 command lists

- · port1 supports 4 command lists.

This leads to a command start list table as presented below:

RM0480 - Rev 2 page 3/80

Table 1. Command start list details

| Address in RAM                | Meaning                      | Comments                                                                                                                            |

|-------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| @RadioConfigPtr(value) + 0x00 | port0->command0 base address | Command executed by the BLE controller on wake-up timer trigger event if RadioComListEna bit = 1 in on-going StateMach.             |

| @RadioConfigPtr(value) + 0x04 | port0->command1 base address | Command executed by the BLE controller on Timer1 trigger event if RadioComListEna bit = 1 in on-going StateMach.                    |

| @RadioConfigPtr(value) + 0x08 | port0->command2 base address | Command executed by the BLE controller on Timer2 trigger event if RadioComListEna bit = 1 in on-going StateMach.                    |

| @RadioConfigPtr(value) + 0x0C | port1->command0 base address | VP_CPU: if the software needs to use an RRM-UDRA command to access the radio register instead of a direct access through APB.       |

| @RadioConfigPtr(value) + 0x10 | port1->command1 base address | VP_CPU: if the software needs to use a second RRM-UDRA command to access the radio register instead of a direct access through APB. |

| @RadioConfigPtr(value) + 0x14 | port1->command2 base address | VP_CPU: if the software needs to use a third RRM-UDRA command to access the radio register instead of a direct access through APB.  |

| @RadioConfigPtr(value) + 0x18 | port1->command3 base address | VP_CPU: if the software needs to use a fourth RRM-UDRA command to access the radio register instead of a direct access through APB. |

## 2.1.2 UDRA command format in RAM

The write and read command format are described in the following table. Note that only one radio register address is entered for a write or a read. Then, if the number of data to write/read is more than one, the address is incremented automatically by 1.

Table 2. UDRA command format in RAM

| Byte<br>number | Address in RAM           | Byte value    | Description                                                                                                                      |  |  |  |  |

|----------------|--------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                |                          |               | bit7: 0=write / 1=read                                                                                                           |  |  |  |  |

| 1              | command_base_addr        | 0x            | bit[6:0] = number of data to write or to read.                                                                                   |  |  |  |  |

|                |                          |               | n = number of data for the example in this table.                                                                                |  |  |  |  |

| 2              | command_base_addr+1      | 8-bit address | Address of a Radio register following the 8-bit address mapping.                                                                 |  |  |  |  |

| 3              | command_base_addr+2      | 1st data      | If write command: write first 8-bit data to be written. If read command: location where the first 8-bit read data are available. |  |  |  |  |

|                |                          |               | Optional (depends on number of data to write/read).                                                                              |  |  |  |  |

| 4              | command_base_addr+3      | 2nd data      | If write command: write second 8-bit data to be written.                                                                         |  |  |  |  |

|                |                          |               | If read command: location where the second 8-bit read data are available.                                                        |  |  |  |  |

|                |                          |               |                                                                                                                                  |  |  |  |  |

| n+2            | command_base_addr+(n+1)  | nth data      | Optional (depends on number of data to write/read). If write command: write n <sup>th</sup> 8-bit data to be written.            |  |  |  |  |

|                |                          |               | If read command: location where the n <sup>th</sup> 8-bit read data are available.                                               |  |  |  |  |

|                |                          |               | Optional: possible to chain other commands.                                                                                      |  |  |  |  |

| n+3            | command_base_addr+n+2    | 0x            | bit7: 0=write / 1=readbit                                                                                                        |  |  |  |  |

|                |                          |               | [6:0] = number of data to write or to read.                                                                                      |  |  |  |  |

| n+4            | command_base_addr+n+3    | 8-bit address | Address of a radio register following the 8-bit address mapping (see Table 86. Radio Controller registers list)                  |  |  |  |  |

| n+5            | command base addr+n+4    | 1st data      | If write command: write first 8-bit data to be written.                                                                          |  |  |  |  |

| 1173           | Commanu_base_addi+11+4   | 15t Udta      | If read command: location where the first 8-bit read data are available.                                                         |  |  |  |  |

|                |                          |               |                                                                                                                                  |  |  |  |  |

| last           | command_base_addr+last-1 | 0x00 / 0x80   | MANDATORY.                                                                                                                       |  |  |  |  |

RM0480 - Rev 2 page 4/80

| Byte<br>number | Address in RAM | Byte value | Description                                                                                                                                                                                 |

|----------------|----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                |            | The null command (command with null length) must be added at the end of the command list. This is needed by the state machines of the UDRA to be informed they reached the end of the list. |

#### Basic examples:

- 1) Write AAC0 DIG ENG=0x12 and AAC1 DIG ENG=0x34 (grouped registers) through port1.command0:

- @port1.command0 addr = 0x02; Write 2 data

- @port1.command0 addr+1 = 0x AAC0 DIG ENG ADDR;

- @port1.command0 addr+2 = 0x12; 1st data to write in AAC0 DIG ENG

- @port1.command0\_addr+3 = 0x34; 2nd data to write in AAC1\_DIG\_ENG

- @port1.command0 addr+4 = 0x00; null command

- At the end of command execution, the 2 radio registers have been modified with new value.

- 2) Read of the 4 AFCx\_DIG\_ENG register chained with a write of 0x54 value in RADIO\_FSM\_USER through port1.command1:

- @port1.command1 addr = 0x84; Read 4 data

- @port1.command1\_addr+1 = 0xAFC0\_DIG\_ENG\_ADDR

- @port1.command1 addr+6 = 0x01; Write 1 data

- @port1.command1 addr+7 = 0x RADIO FSM USER ADDR;

- @port1.command0\_addr+8 = 0x54; 1st (and unique) data to write in RADIO\_FSM\_USER register

- @port1.command0 addr+9 = 0x00; null command

Note: @port1.command1\_addr+2 to @port1.command1\_addr+5 contents are written by the RRM-UDRA block with the result of read.

#### At the end of the execution:

- @port1.command1\_addr+2 contains the AFC0\_DIG\_ENG register value

- @port1.command1\_addr+3 contains the AFC1\_DIG\_ENG register value

- @port1.command1\_addr+4 contains the AFC2\_DIG\_ENG register value

- @port1.command1\_addr+5 contains the AFC3\_DIG\_ENG register value

- RADIO FSM USER register has been modified with 0x54

#### 2.2 Direct register access

The direct register access block allows the software to access the radio registers directly through an APB access. The radio registers are mainly used to control the analog part of the radio and the radio FSM. The software has to read/write the RF APB registers located inside the RRM APB register list that points directly to the radio registers. The RF APB registers start at RRM address + 0x100. The radio registers are 8-bit only so the APB register bit field [31:8] part is padded with 0. Then, they can be accessed as 32-bit APB registers (address incremented by 4 between each register) through RRM direct access interface. The radio registers can be also accessed exploiting RRM UDRA command list in RAM as 8-bit registers (address incremented by 1 between each register). An internal arbiter manages the case of concurrent accesses on radio registers by both UDRA (executing a command) and direct register access block (on a CPU read/write APB request). The arbitration is based on round-robin priority mechanism. The software must not write any radio registers through direct APB access if they are also modified through commands in RAM (through UDRA block). In this case, there is a risk of multi drivers in parallel and loss of coherency (no way to know which requester wrote the last).

#### 2.2.1 CPU access to radio resources

Although the CPU can request the use of radio resources through the RRM, in most cases read and write accesses to the radio registers can be done directly through APB inside the RRM APB registers. In this case, reading is not intrusive, it is faster and there is no risk even if a radio transaction is on-going. Writing to radio registers is not supposed to be done during a radio transfer. Writing through RRM commands can be safer in order to avoid changes while a radio transaction is on-going. Nevertheless, if this is done very close to a trig event, it is not possible to know which command is executed first between radio and CPU so which setting is used for the coming transaction.

RM0480 - Rev 2 page 5/80

# 2.3 RRM registers

Table 3. RRM register list

| Address | Nama                | DW | Ponet      | Description                  |

|---------|---------------------|----|------------|------------------------------|

| offset  | Name                | RW | Reset      | Description                  |

| 0x00    | RRM_ID              | R  | 0x00000001 | RRM_ID register              |

| 0x04    | RRM_CTRL            | RW | 0x00000003 | RRM_CTRL register            |

| 0x10    | UDRA_CTRL0          | RW | 0x00000000 | UDRA_CTRL0 register          |

| 0x14    | UDRA_IRQ_ENABLE     | RW | 0x00000000 | UDRA_IRQ_ENABLE register     |

| 0x18    | UDRA_IRQ_STATUS     | RW | 0x00000000 | UDRA_IRQ_STATUS register     |

| 0x1C    | UDRA_RADIO_CFG_PTR  | R  | 0x00000000 | UDRA_RADIO_CFG_PTR register  |

| 0x20    | SEMA_IRQ_ENABLE     | RW | 0x00000000 | SEMA_IRQ_ENABLE register     |

| 0x24    | SEMA_IRQ_STATUS     | R  | 0x00000000 | SEMA_IRQ_STATUS register     |

| 0x28    | BLE_IRQ_ENABLE      | RW | 0x00000000 | BLE_IRQ_ENABLE register      |

| 0x2C    | BLE_IRQ_STATUS      | RW | 0x00000000 | BLE_IRQ_STATUS register      |

| 0x60    | VP_CPU_CMD_BUS      | RW | 0x00000000 | VP_CPU_CMD_BUS register      |

| 0x64    | VP_CPU_SEMA_BUS     | RW | 0x00000000 | VP_CPU_SEMA_BUS register     |

| 0x68    | VP_CPU_IRQ_ENABLE   | RW | 0x00000000 | VP_CPU_IRQ_ENABLE register   |

| 0x6C    | VP_CPU_IRQ_STATUS   | RW | 0x00000000 | VP_CPU_IRQ_STATUS register   |

| 0x100   | AA0_DIG_USR         | RW | 0x000000D6 | AA0_DIG_USR register         |

| 0x104   | AA1_DIG_USR         | RW | 0x000000BE | AA1_DIG_USR register         |

| 0x108   | AA2_DIG_USR         | RW | 0x00000089 | AA2_DIG_USR register         |

| 0x10C   | AA3_DIG_USR         | RW | 0x0000008E | AA3_DIG_USR register         |

| 0x110   | DEM_MOD_DIG_USR     | RW | 0x00000026 | DEM_MOD_DIG_USR register     |

| 0x114   | RADIO_FSM_USR       | RW | 0x00000004 | RADIO_FSM_USR register       |

| 0x118   | PHYCTRL_DIG_USR     | RW | 0x00000000 | PHYCTRL_DIG_USR register     |

| 0x144   | AFC0_DIG_ENG        | RW | 0x00000066 | AFC0_DIG_ENG register        |

| 0x148   | AFC1_DIG_ENG        | RW | 0x00000044 | AFC1_DIG_ENG register        |

| 0x14C   | AFC2_DIG_ENG        | RW | 0x000000FF | AFC2_DIG_ENG register        |

| 0x150   | AFC3_DIG_ENG        | RW | 0x0000007F | AFC3_DIG_ENG register        |

| 0x154   | CR0_DIG_ENG         | RW | 0x00000044 | CR0_DIG_ENG register         |

| 0x168   | CR0_LR              | RW | 0x000000DC | CR0_LR register              |

| 0x16C   | VIT_CONF_DIG_ENG    | RW | 0x00000000 | VIT_CONF_DIG_ENG register    |

| 0x184   | LR_PD_THR_DIG_ENG   | RW | 0x00000050 | LR_PD_THR_DIG_ENG register   |

| 0x188   | LR_RSSI_THR_DIG_ENG | RW | 0x0000001B | LR_RSSI_THR_DIG_ENG register |

| 0x18C   | LR_AAC_THR_DIG_ENG  | RW | 0x00000038 | LR_AAC_THR_DIG_ENG register  |

| 0x1DC   | DTB0_DIG_ENG        | RW | 0x00000000 | DTB0_DIG_ENG register        |

| 0x1F0   | DTB5_DIG_ENG        | RW | 0x00000000 | DTB5_DIG_ENG register        |

| 0x234   | MOD0_DIG_TST        | RW | 0x00000000 | MOD0_DIG_TST register        |

| 0x238   | MOD1_DIG_TST        | RW | 0x00000000 | MOD1_DIG_TST register        |

| 0x23C   | MOD2_DIG_TST        | RW | 0x00000080 | MOD2_DIG_TST register        |

| 0x240   | MOD3_DIG_TST        | RW | 0x00000098 | MOD3_DIG_TST register        |

RM0480 - Rev 2 page 6/80

| Address |                    |    |            |                             |

|---------|--------------------|----|------------|-----------------------------|

| offset  | Name               | RW | Reset      | Description                 |

| 0x248   | RXADC_ANA_USR      | RW | 0x0000001B | RXADC_ANA_USR register      |

| 0x254   | LDO_ANA_ENG        | RW | 0x00000080 | LDO_ANA_ENG register        |

| 0x274   | CBIAS0_ANA_ENG     | RW | 0x00000078 | CBIAS0_ANA_ENG register     |

| 0x278   | CBIAS1_ANA_ENG     | RW | 0x00000007 | CBIAS1_ANA_ENG register     |

| 0x27C   | CBIAS_ANA_TEST     | RW | 0x00000000 | CBIAS_ANA_TEST register     |

| 0x280   | SYNTHCAL0_DIG_OUT  | R  | 0x00000000 | SYNTHCAL0_DIG_OUT register  |

| 0x284   | SYNTHCAL1_DIG_OUT  | R  | 0x00000001 | SYNTHCAL1_DIG_OUT register  |

| 0x288   | SYNTHCAL2_DIG_OUT  | R  | 0x00000040 | SYNTHCAL2_DIG_OUT register  |

| 0x28C   | SYNTHCAL3_DIG_OUT  | R  | 0x00000000 | SYNTHCAL3_DIG_OUT register  |

| 0x290   | SYNTHCAL4_DIG_OUT  | R  | 0x00000018 | SYNTHCAL4_DIG_OUT register  |

| 0x294   | SYNTHCAL5_DIG_OUT  | R  | 0x00000007 | SYNTHCAL5_DIG_OUT register  |

| 0x298   | FSM_STATUS_DIG_OUT | R  | 0x00000000 | FSM_STATUS_DIG_OUT register |

| 0x29C   | IRQ_STATUS_DIG_OUT | R  | 0x00000000 | IRQ_STATUS_DIG_OUT register |

| 0x2A4   | RSSI0_DIG_OUT      | R  | 0x00000008 | RSSI0_DIG_OUT register      |

| 0x2A8   | RSSI1_DIG_OUT      | R  | 0x00000008 | RSSI1_DIG_OUT register      |

| 0x2AC   | AGC_DIG_OUT        | R  | 0x00000000 | AGC_DIG_OUT register        |

| 0x2B0   | DEMOD_DIG_OUT      | R  | 0x00000000 | DEMOD_DIG_OUT register      |

| 0x2B4   | AGC0_ANA_TST       | RW | 0x00000000 | AGC0_ANA_TST register       |

| 0x2B8   | AGC1_ANA_TST       | RW | 0x00000000 | AGC1_ANA_TST register       |

| 0x2BC   | AGC2_ANA_TST       | RW | 0x00000000 | AGC2_ANA_TST register       |

| 0x2C0   | AGC0_DIG_ENG       | RW | 0x0000004A | AGC0_DIG_ENG register       |

| 0x2C4   | AGC1_DIG_ENG       | RW | 0x00000084 | AGC1_DIG_ENG register       |

| 0x2C8   | AGC2_DIG_ENG       | RW | 0x00000006 | AGC2_DIG_ENG register       |

| 0x2CC   | AGC3_DIG_ENG       | RW | 0x0000001A | AGC3_DIG_ENG register       |

| 0x2D0   | AGC4_DIG_ENG       | RW | 0x00000073 | AGC4_DIG_ENG register       |

| 0x2D4   | AGC5_DIG_ENG       | RW | 0x000000F  | AGC5_DIG_ENG register       |

| 0x2D8   | AGC6_DIG_ENG       | RW | 0x00000000 | AGC6_DIG_ENG register       |

| 0x2DC   | AGC7_DIG_ENG       | RW | 0x00000000 | AGC7_DIG_ENG register       |

| 0x2E0   | AGC8_DIG_ENG       | RW | 0x00000000 | AGC8_DIG_ENG register       |

| 0x2E4   | AGC9_DIG_ENG       | RW | 0x00000090 | AGC9_DIG_ENG register       |

| 0x2E8   | AGC10_DIG_ENG      | RW | 0x00000000 | AGC10_DIG_ENG register      |

| 0x2EC   | AGC11_DIG_ENG      | RW | 0x00000010 | AGC11_DIG_ENG register      |

| 0x2F0   | AGC12_DIG_ENG      | RW | 0x00000020 | AGC12_DIG_ENG register      |

| 0x2F4   | AGC13_DIG_ENG      | RW | 0x00000030 | AGC13_DIG_ENG register      |

| 0x2F8   | AGC14_DIG_ENG      | RW | 0x00000038 | AGC14_DIG_ENG register      |

| 0x2FC   | AGC15_DIG_ENG      | RW | 0x00000039 | AGC15_DIG_ENG register      |

| 0x300   | AGC16_DIG_ENG      | RW | 0x0000003A | AGC16_DIG_ENG register      |

| 0x304   | AGC17_DIG_ENG      | RW | 0x0000003B | AGC17_DIG_ENG register      |

| 0x308   | AGC18_DIG_ENG      | RW | 0x0000003C | AGC18_DIG_ENG register      |

| 0x30C   | AGC19_DIG_ENG      | RW | 0x0000003D | AGC19_DIG_ENG register      |

RM0480 - Rev 2 page 7/80

| Address<br>offset | Name               | RW | Reset      | Description                 |

|-------------------|--------------------|----|------------|-----------------------------|

| 0x310             | AGC20_DIG_ENG      | RW | 0x00000080 | AGC20_DIG_ENG register      |

| 0x324             | RXADC_HW_TRIM_OUT  | R  | 0x0000001B | RXADC_HW_TRIM_OUT register  |

| 0x328             | CBIAS0_HW_TRIM_OUT | R  | 0x00000078 | CBIAS0_HW_TRIM_OUT register |

| 0x32C             | CBIAS1_HW_TRIM_OUT | R  | 0x00000008 | CBIAS1_HW_TRIM_OUT register |

| 0x330             | AGC_HW_TRIM_OUT    | R  | 0x00000006 | AGC_HW_TRIM_OUT register    |

## Table 4. RRM\_ID register description

| Bit  | Field name     | Reset | RW | Description                  |

|------|----------------|-------|----|------------------------------|

| 3:0  | IDENTIFICATION | 0x1   | R  | RRM Identification register. |

| 31:4 | RESERVED31_4   | 0x0   | R  | Reserved.                    |

# Table 5. RRM\_CTRL register description

| Bit  | Field name   | Reset | RW | Description                                                                                        |

|------|--------------|-------|----|----------------------------------------------------------------------------------------------------|

| 1:0  | PRIORITY     | 0x3   | RW | Defines the priority between direct register or UDRA for radio register access: - 11: Round-robin. |

| 31:2 | RESERVED31_2 | 0x0   | R  | Reserved.                                                                                          |

## Table 6. UDRA\_CTRL0 register description

| Bit  | Field name      | Reset | RW | Description                                                                             |

|------|-----------------|-------|----|-----------------------------------------------------------------------------------------|

| 0    | RELOAD_RDCFGPTR | 0x0   | RW | Reload the radio configuration pointer from RAM.  This bit is auto-cleared by hardware. |

| 31:1 | RESERVED31_1    | 0x0   | R  | Reserved.                                                                               |

# Table 7. UDRA\_IRQ\_ENABLE register description

| Bit  | Field name             | Reset | RW | Description                                             |

|------|------------------------|-------|----|---------------------------------------------------------|

| 0    | RADIO_CFG_PTR_RELOADED | 0x0   | RW | UDRA interrupt enable (reload radio config pointer).    |

| 1    | CMD_START              | 0x0   | RW | UDRA interrupt enable (command start).                  |

| 2    | CMD_END                | 0x0   | RW | UDRA interrupt enable (command end).                    |

| 3    | CMD_NUMBER_ERROR       | 0x0   | RW | UDRA interrupt enable (error in the number of command). |

| 31:4 | RESERVED31_4           | 0x0   | R  | Reserved.                                               |

RM0480 - Rev 2 page 8/80

# Table 8. UDRA\_IRQ\_STATUS register description

| Bit  | Field name Reset         |        | RW                                     | Description                                             |

|------|--------------------------|--------|----------------------------------------|---------------------------------------------------------|

| 0    | RADIO CFG PTR RELOADED   | 0x0    | RW                                     | UDRA interrupt enable (reload radio config pointer).    |

|      | KADIO_CI O_I IN_NELOADED | 0.00   | IXVV                                   | Write '1' to clear IRQ status bit.                      |

| 1    | CMD START                | 0x0 RW | UDRA interrupt enable (command start). |                                                         |

| '    | GWD_STAICT               | 0.00   | 1744                                   | Write '1' to clear IRQ status bit.                      |

| 2    | CMD END                  | 0x0    | RW                                     | UDRA interrupt enable (command end).                    |

|      | OWD_END                  | UNU    | 1200                                   | Write '1' to clear IRQ status bit.                      |

| 3    | CMD NUMBER ERROR         | 0x0    | RW                                     | UDRA interrupt enable (error in the number of command). |

|      | OMB_NOMBEN_ENTON         | 0.00   | 1.00                                   | Write '1' to clear IRQ status bit.                      |

| 31:4 | RESERVED31_4             | 0x0    | R                                      | Reserved.                                               |

# Table 9. UDRA\_RADIO\_CFG\_PTR register description

| Bit  | Field name           | Reset | RW | Description                                                                                                                  |

|------|----------------------|-------|----|------------------------------------------------------------------------------------------------------------------------------|

|      |                      |       |    | UDRA radio configuration address.  This field contains the value contained by RadioConfigPtr bit field in GlobalStatMach RAM |

| 31:0 | RADIO_CONFIG_ADDRESS | 0x0   | R  | table when the BLE controller exits the reset state.                                                                         |

|      |                      |       |    | This field is updated after a reload configuration pointer command.                                                          |

## Table 10. SEMA\_IRQ\_ENABLE register description

| Bit  | Field name   | Reset | RW | Description                                               |

|------|--------------|-------|----|-----------------------------------------------------------|

| 0    | LOCK         | 0x0   | RW | Semaphore locked (= one port granted) interrupt enable.   |

| 1    | UNLOCK       | 0x0   | RW | Semaphore unlocked (= no port selected) interrupt enable. |

| 31:2 | RESERVED31_2 | 0x0   | R  | Reserved.                                                 |

#### Table 11. SEMA\_IRQ\_STATUS register description

| Bit  | Field name   | Reset | RW | Description                                                                                        |

|------|--------------|-------|----|----------------------------------------------------------------------------------------------------|

| 0    | LOCK         | 0x0   | R  | On read, returns the semaphore locked interrupt status.  Write '1' to clear this IRQ status bit.   |

| 1    | UNLOCK       | 0x0   | R  | On read, returns the semaphore unlocked interrupt status.  Write '1' to clear this IRQ status bit. |

| 31:2 | RESERVED31_2 | 0x0   | R  | Reserved.                                                                                          |

## Table 12. BLE\_IRQ\_ENABLE register description

| Bit  | Field name     | Reset | RW | Description                              |

|------|----------------|-------|----|------------------------------------------|

| 0    | PORT_GRANT     | 0x0   | RW | BLE port grant interrupt enable.         |

| 1    | PORT_RELEASE   | 0x0   | RW | BLE port release interrupt enable.       |

| 2    | PORT_PREEMPT   | 0x0   | RW | BLE port preempt interrupt enable.       |

| 3    | PORT_CMD_START | 0x0   | RW | BLE port command start interrupt enable. |

| 4    | PORT_CMD_END   | 0x0   | RW | BLE port command end interrupt enable.   |

| 31:5 | RESERVED31_5   | 0x0   | R  | Reserved                                 |

RM0480 - Rev 2 page 9/80

Table 13. BLE\_IRQ\_STATUS register description

| Bit  | Field name   | Reset | RW | Description                                                                                                                                                                                                                                                                         |

|------|--------------|-------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |              |       |    | BLE hardware port granted interrupt status.                                                                                                                                                                                                                                         |

|      |              |       |    | - 0: the BLE port request to semaphore is not granted.                                                                                                                                                                                                                              |

| 0    | PORT_GRANT   | 0x0   | RW | - 1: the BLE controller request to take the semaphore is granted: the RF registers access and the radio TX and the radio RX data path are selected for that controller. The port stays granted as long as it requests the token and the semaphore is not preempted by another port. |

|      |              |       |    | Write '1' to clear this IRQ status bit.                                                                                                                                                                                                                                             |

|      |              |       |    | BLE hardware port released interrupt status.                                                                                                                                                                                                                                        |

|      |              |       |    | When read:                                                                                                                                                                                                                                                                          |

| 1    | PORT_RELEASE | 0x0   | RW | - 0: the BLE controller has not been released.                                                                                                                                                                                                                                      |

|      |              |       |    | - 1: the BLE controller has been released by the semaphore.                                                                                                                                                                                                                         |

|      |              |       |    | Write '1' to clear this IRQ status bit.                                                                                                                                                                                                                                             |

|      |              |       |    | BLE hardware port preemption (at semaphore level) interrupt status.                                                                                                                                                                                                                 |

|      |              |       |    | When read:                                                                                                                                                                                                                                                                          |

| 2    | PORT_PREEMPT | 0x0   | RW | - 0: the BLE controller has not been preempted by another controller.                                                                                                                                                                                                               |

|      |              |       |    | - 1: the BLE controller has been preempted and semaphore token was taken by another port.                                                                                                                                                                                           |

|      |              |       |    | Write '1' to clear this IRQ status bit.                                                                                                                                                                                                                                             |

|      |              |       |    | BLE hardware port command start interrupt status.                                                                                                                                                                                                                                   |

|      |              |       |    | When read:                                                                                                                                                                                                                                                                          |

| 3    | CMD_START    | 0x0   | RW | - 0: the BLE port command requested by the BLE controller is not started.                                                                                                                                                                                                           |

|      |              |       |    | - 1: the BLE port command requested by the BLE controller is started.                                                                                                                                                                                                               |

|      |              |       |    | Write '1' to clear this IRQ status bit.                                                                                                                                                                                                                                             |

|      |              |       |    | BLE hardware port command end interrupt status.                                                                                                                                                                                                                                     |

|      |              |       |    | When read:                                                                                                                                                                                                                                                                          |

| 4    | CMD_END      | 0x0   | RW | - 0: the BLE port command requested by the BLE controller is not completed.                                                                                                                                                                                                         |

|      |              |       |    | - 1: the BLE port command requested by the BLE controller is completed.                                                                                                                                                                                                             |

|      |              |       |    | Write '1' to clear this IRQ status bit.                                                                                                                                                                                                                                             |

| 31:5 | RESERVED31_5 | 0x0   | R  | Reserved                                                                                                                                                                                                                                                                            |

Note:

The BLE controller receives the previous information directly by hardware wires and manages the sequence through them. The interrupt mechanism is there in case the CPU needs to monitor the activity between the BLE controller and the RRM block.

Table 14. VP\_CPU\_CMD\_BUS register description

| Bit  | Field name   | Reset | RW | Description                                                                                                                                                                      |

|------|--------------|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0  | COMMAND      | 0x0   | RW | Command number.                                                                                                                                                                  |

| 3    | COMMAND_REQ  | 0x0   | RW | CPU Virtual port command request  - 0: the RRM command request is released.  - 1: request a command to the RRM-UDRA block.  This bit is cleared by HW once the command is ended. |

| 31:4 | RESERVED31_4 | 0x0   | R  | Reserved.                                                                                                                                                                        |

RM0480 - Rev 2 page 10/80

# Table 15. VP\_CPU\_SEMA\_BUS register description

| Bit  | Field name   | Reset | RW | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|------|--------------|-------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0  | TAKE_PRIO    | 0x0   | RW | Semaphore priority value (between 0 and 7) of the take request.  The higher the value, the higher priority is the request.                                                                                                                                                                                                                                                                             |

| 3    | TAKE_REQ     | 0x0   | RW | Semaphore token request  - 0: the CPU virtual port releases the semaphore or does not request to take the RRM semaphore.  - 1: the CPU virtual port requests to take or to keep the RRM semaphore.                                                                                                                                                                                                     |

| 4    | TAKE_PREEMPT | 0x0   | RW | Semaphore token preemption request by the CPU virtual port  - 0: Semaphore take request is not applied with pre-emption. This is the usual use case to request the semaphore.  - 1: Semaphore take request is applied with preemption.  TAKE_PREEMPT=1'b1 should only be used exceptionally when the peripheral cannot wait anymore to get the semaphore due to timing constraint of a radio protocol. |

| 31:5 | RESERVED31_5 | 0x0   | R  | Reserved                                                                                                                                                                                                                                                                                                                                                                                               |

# Table 16. VP\_CPU\_IRQ\_ENABLE register description

| Bit | Field name     | Reset | RW | Description                                      |

|-----|----------------|-------|----|--------------------------------------------------|

| 0   | PORT_GRANT     | 0x0   | RW | CPU virtual port grant interrupt enable.         |

| 1   | PORT_RELEASE   | 0x0   | RW | CPU virtual port release interrupt enable.       |

| 2   | PORT_PREEMPT   | 0x0   | RW | CPU virtual port preempt interrupt enable.       |

| 3   | PORT_CMD_START | 0x0   | RW | CPU virtual port command start interrupt enable. |

| 4   | PORT_CMD_END   | 0x0   | RW | CPU virtual port command end interrupt enable.   |

RM0480 - Rev 2 page 11/80

Table 17. VP\_CPU\_IRQ\_STATUS register description

| Bit | Field name   | Reset | RW     | Description                                                                                                        |

|-----|--------------|-------|--------|--------------------------------------------------------------------------------------------------------------------|

|     |              |       |        | CPU virtual port granted interrupt status.                                                                         |

| 0   | DODT CDANT   | 0x0   | RW     | - 0: the CPU virtual port token request is not granted.                                                            |

| 0   | PORT_GRANT   | UXU   | KVV    | - 1: the CPU virtual port token request is granted by the semaphore:                                               |

|     |              |       |        | Write '1' to clear this IRQ status bit.                                                                            |

|     |              |       |        | CPU virtual port released interrupt status.                                                                        |

|     |              |       |        | - 0: the CPU virtual port has not been released (due to TAKE_REQ=1'b1)                                             |

| 1   | PORT_RELEASE | 0x0   | RW     | - 1: the CPU virtual port has been released by the semaphore due to TAKE_REQ=1'b0 (requested by CPU virtual port). |

|     |              |       |        | Write '1' to clear this IRQ status bit.                                                                            |

|     |              |       |        | CPU virtual port preemption (at semaphore level) interrupt status.                                                 |

|     |              |       |        | When read:                                                                                                         |

| 2   | PORT_PREEMPT | 0x0   | RW     | - 0: the CPU virtual port has not been preempted by another UDRA port.                                             |

|     |              |       |        | - 1: the CPU virtual port has been preempted by another UDRA port.                                                 |

|     |              |       |        | Write '1' to clear this IRQ status bit.                                                                            |

|     |              |       |        | CPU virtual port command start interrupt status.                                                                   |

|     |              |       |        | When read:                                                                                                         |

| 3   | CMD_START    | 0x0   | RW     | - 0: the command requested by the CPU virtual port (port1) is not started.                                         |

|     |              |       |        | - 1: the command requested by the CPU virtual port (port1) is started                                              |

|     |              |       |        | Write '1' to clear this IRQ status bit.                                                                            |

|     |              |       |        | CPU virtual port command end interrupt status.                                                                     |

|     | 4 CMD_END    |       |        | When read:                                                                                                         |

| 4   |              | 0x0   | 0x0 RW | - 0: the command requested by the CPU virtual port (port1) is not completed.                                       |

|     |              |       |        | - 1: the command requested by the CPU virtual port (port1) is completed.                                           |

|     |              |       |        | Write '1' to clear this IRQ status bit.                                                                            |

## 2.3.1 Radio registers (RRM address + 0x100)

They can be accessed through two different mappings:

as 32-bit APB register (address incremented by 4 between each register) through RRM direct access interface as 8-bit register (address incremented by 1 between each register) through RRM UDRA command list in RAM.

Table 18. AA0\_DIG\_USR register description

| Bit  | Field name   | Reset | RW | Description                                                                                                                                                                         |

|------|--------------|-------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | AA_7_0       | 0xD6  | RW | Least significant byte of the BTLE Access Address code.  This register is (over)written by the sequencer during 2 <sup>nd</sup> INIT step with the StatMach.accaddr[7:0] bit field. |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved                                                                                                                                                                            |

RM0480 - Rev 2 page 12/80

# Table 19. AA1\_DIG\_USR register description

| Bit  | Field name   | Reset | RW | Description                                                                                                                                                             |

|------|--------------|-------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | AA_15_8      | 0xBE  | RW | Next byte of the BTLE access address code.  This register is (over)written by the sequencer during 2 <sup>nd</sup> INIT step with the StatMach.accaddr[15:8] bit field. |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved                                                                                                                                                                |

## Table 20. AA2\_DIG\_USR register description

| Bit  | Field name   | Reset | RW | Description                                                                                                                                                             |

|------|--------------|-------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | AA_23_16     | 0x89  | RW | Next byte of the BTLE access address code  This register is (over)written by the sequencer during 2 <sup>nd</sup> INIT step with the StatMach.accaddr[23:16] bit field. |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved                                                                                                                                                                |

# Table 21. AA3\_DIG\_USR register description

| Bit  | Field name   | Reset | RW | Description                                                                                                                                                              |

|------|--------------|-------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | AA_31_24     | 0x89  | RW | Next byte of the BTLE access address code.  This register is (over)written by the sequencer during 2 <sup>nd</sup> INIT step with the StatMach.accaddr[31:24] bit field. |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved                                                                                                                                                                 |

# Table 22. DEM\_MOD\_DIG\_USR register description

| Bit  | Field name   | Reset | RW | Description                                                                                                                                                                                      |

|------|--------------|-------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | SPARE        | 0x0   | RW | Spare                                                                                                                                                                                            |

|      |              |       |    | Index for internal lock-up table in which the synthesizer setup is contained.                                                                                                                    |

|      |              |       |    | Default value is the BLE RF channel 19 -> 2440 MHz.                                                                                                                                              |

|      |              |       |    | For Bluetooth protocol: this bit field is (over)written by the BLE sequencer during the 1 <sup>st</sup> INIT. The value copied here is the output of the channel Incr and hoping hardware block. |

| 7:1  | CHANNEL_NUM  | 0x13  | RW | Example: value to program to select the channel 19:                                                                                                                                              |

|      |              |       |    | CHANNEL_NUM = 19 = 0x13.                                                                                                                                                                         |

|      |              |       |    | Then, 2402 + (channel number * 2) = 2440 MHz for BLE channel 19                                                                                                                                  |

|      |              |       |    | Note: This bit field is used by the SYNTH_IF hardware block to generate the physical frequency on the antenna.                                                                                   |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved                                                                                                                                                                                         |

RM0480 - Rev 2 page 13/80

Table 23. RADIO\_FSM\_USR register description

| Bit  | Field name     | Reset | RW | Description                                                                                                                                      |

|------|----------------|-------|----|--------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                |       |    | Tx mode bit.  For Bluetooth protocol, this bit is (over)written by the BLE sequencer with the StatMach.TxMode bit                                |

| 0    | TXMODE         | 0x0   | RW | during the 1 <sup>st</sup> INIT step.                                                                                                            |

|      |                |       |    | Note: This bit is not used by the hardware.                                                                                                      |

|      |                |       |    | CBP calibration enable bit.                                                                                                                      |

| 1    | EN_CALIB_CBP   | 0x0   | RW | For Bluetooth protocol, this bit is (over)written by the BLE sequencer with the TxRxPack.CalReq bit during the 1 <sup>st</sup> INIT step.        |

|      |                |       |    | Note: This bit is used by the radio FSM as EN_CALIB_SYNTH information.                                                                           |

|      |                |       |    | SYNTH calibration enable bit.                                                                                                                    |

| 2    | EN_CALIB_SYNTH | 0x1   | RW | For Bluetooth protocol, this bit is (over)written by the BLE sequencer with the TxRxPack.CalReq bit during the 1 <sup>st</sup> INIT step.        |

|      |                |       |    | Note: This bit is used by the Radio FSM as EN_CALIB_SYNTH information.                                                                           |

|      |                |       |    | PA power coefficient.                                                                                                                            |

| 7:3  | PA_POWER       | 0x0   | RW | For Bluetooth protocol, this bit is (over)written by the BLE sequencer with the StatMach.PAPower bit field during the 1 <sup>st</sup> INIT step. |

|      |                |       |    | Note: This bit is used by the PA_RAMP hardware block.                                                                                            |

| 31:8 | RESERVED31_8   | 0x0   | R  | Reserved                                                                                                                                         |

# Table 24. PHYCTRL\_DIG\_USR register description

| Bit  | Field name   | Reset | RW | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|--------------|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0  | RXTXPHY      | 0x0   | RW | RXTXPHY selection.  For Bluetooth protocol, this bit field is (over)written by the BLE sequencer during the 1 <sup>st</sup> INIT using the StatMach.RxPhy[2:0] or StatMach.TxPhy[2:0], depending if the transfer is a reception or a transmission.  - 000: uncoded PHY 1 Mb/s  - 001: uncoded PHY 2 Mb/s  - 100: coded PHY S=8 1 Mb/s  - 110: coded PHY S=2 1 Mb/s  Note: This bit field is used by the hardware to inform the digital and analog blocks needing this PHY information. |

| 3:7  | SPARE        | 0x0   | RW | Spare.  Note: this bit field is overwritten by the BLE sequencer during the 1st INIT step with 0b on each bit.                                                                                                                                                                                                                                                                                                                                                                         |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# Table 25. AFC0\_DIG\_ENG register description

| Bit  | Field name      | Reset | RW | Description                                                                        |  |

|------|-----------------|-------|----|------------------------------------------------------------------------------------|--|

| 3:0  | AFC_GAIN_AFTER  | 0x6   | RW | Set the gain of the AFC loop before AA detection to the value2^(-AFC_GAIN_AFTER).  |  |

| 7:4  | AFC_GAIN_BEFORE | 0x6   | RW | Set the gain of the AFC loop before AA detection to the value2^(-AFC_GAIN_BEFORE). |  |

| 31:8 | RESERVED31_8    | 0x0   | R  | Reserved.                                                                          |  |

RM0480 - Rev 2 page 14/80

# Table 26. AFC1\_DIG\_ENG register description

| Bit  | Field name       | Reset | RW | Description                                                                                  |  |

|------|------------------|-------|----|----------------------------------------------------------------------------------------------|--|

| 3:0  | AFC_DELAY_AFTER  | 0x4   | RW | Set the gain of the AFC loop before AA detection to the value AFC_DELAY_AFTER/256.           |  |

| 7:4  | AFC_DELAY_BEFORE | 0x4   | RW | Set the decay factor of the AFC loop before AA detection to the value AFC_DELAY_BEFORE/ 256. |  |

| 31:8 | RESERVED31_8     | 0x0   | R  | Reserved.                                                                                    |  |

# Table 27. AFC2\_DIG\_ENG register description

| Bit  | Field name     | Reset | RW | Description                                            |

|------|----------------|-------|----|--------------------------------------------------------|

| 6:0  | AFC_FREQ_LIMIT | 0x7F  | RW | Max. (absolute value) of frequency correction.         |

| 7    | AFC_ENABLE     | 0x1   | RW | Enable/disable the AFC loop - 0: disabled - 1: enabled |

| 31:8 | RESERVED31_8   | 0x0   | R  | Reserved.                                              |

# Table 28. AFC3\_DIG\_ENG register description

| Bit  | Field name       | Reset | RW | Description                                                                                                                                             |

|------|------------------|-------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | AFC_MINMAX_LIMIT | 0x7F  | RW | Max. difference allowed on the min./max. peak detectors. Values above this limit are interpreted as noise and the current min./max. trackers are reset. |

| 31:8 | RESERVED31_8     | 0x0   | R  | Reserved.                                                                                                                                               |

# Table 29. CR0\_DIG\_ENG register description

| Bit  | Field name     | Reset | RW | Description                                                                                   |

|------|----------------|-------|----|-----------------------------------------------------------------------------------------------|

| 3:0  | CR_GAIN_AFTER  | 0x4   | RW | Set the gain of the clock recovery loop before AA detection to the value 2^(-CR_GAIN_AFTER).  |

| 7:4  | CR_GAIN_BEFORE | 0x4   | RW | Set the gain of the clock recovery loop before AA detection to the value 2^(-CR_GAIN_BEFORE). |

| 31:8 | RESERVED31_8   | 0x0   | R  | Reserved.                                                                                     |

## Table 30. CR0\_LR register description

| Bit  | Field name        | Reset | RW | Description                                                                                   |  |

|------|-------------------|-------|----|-----------------------------------------------------------------------------------------------|--|

| 3:0  | CR_LR_GAIN_AFTER  | 0x6   | RW | Set the gain of the clock recovery loop before AA detection to the value 2^(-CR_GAIN_BEFORE). |  |

| 7:4  | CR_LR_GAIN_BEFORE | 0x6   | RW | Set the gain of the clock recovery loop before AA detection to the value 2^(-CR_GAIN_BEFORE). |  |

| 31:8 | RESERVED31_8      | 0x0   | R  | Reserved.                                                                                     |  |

# Table 31. VIT\_CONF\_DIG\_ENG register description

| Bit  | Field name   | Reset | RW | Description                                                                                                                                                     |

|------|--------------|-------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | VIT_CONF     | 0x0   | RW | Viterbi control register  - VIT_CONF[0] = enable the Viterbi  - VIT_CONF[1] = PD_DETECT_MODE: Preamble detection mode selection (0 = Peak repetition, 1 = RSSI) |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved                                                                                                                                                        |

RM0480 - Rev 2 page 15/80

# Table 32. LR\_PD\_THR\_DIG\_ENG register description

| Bit  | Field name   | Reset | RW | Description                     |

|------|--------------|-------|----|---------------------------------|

| 7:0  | LR_PD_THR    | 0x50  | RW | Preamble detect threshold value |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved.                       |

# Table 33. LR\_RSSI\_THR\_DIG\_ENG register description

| Bit  | Field name   | Reset | RW | Description                   |

|------|--------------|-------|----|-------------------------------|

| 7:0  | LR_RSSI_THR  | 0x1B  | RW | RSSI or peak threshold value. |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved.                     |

# Table 34. LR\_AAC\_THR\_DIG\_ENG register description

| Bit  | Field name   | Reset | RW | Description                          |

|------|--------------|-------|----|--------------------------------------|

| 7:0  | LR_RSSI_THR  | 0x1B  | RW | Address coded correlation threshold. |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved.                            |

# Table 35. DTB0\_DIG\_ENG register description

| Bit  | Field name   | Reset | RW | Description        |

|------|--------------|-------|----|--------------------|

| 0    | DTB_EN       | 0x0   | RW | Enable DTB.        |

| 4:1  | DTB_CFG      | 0x0   | RW | DTB configuration. |

| 7:5  | SPARE        | 0x0   | RW | Spare.             |

| 31:8 | RESERVED31_5 | 0x0   | R  | Reserved.          |

## Table 36. DTB5\_DIG\_ENG register description

| Bit  | Field name       | Reset | RW | Description                                                                                        |

|------|------------------|-------|----|----------------------------------------------------------------------------------------------------|

|      |                  |       |    | It enables the other bits of the register to control the signal in place of the functional design: |

| 0    | RXTX_START_SEL   | 0x0   | RW | 0: the Radio FSM is controlled by the signals generated by the RRM and sequencer                   |

|      |                  |       |    | 1: the Radio FSM is controlled by the bits of this register.                                       |

| 1    | TX_ACTIVE        | 0x0   | RW | Force TX_ACTIVE signal.                                                                            |

| 2    | RX_ACTIVE        | 0x0   | RW | Force RX_ACTIVE signal.                                                                            |

| 3    | INITIALIZE       | 0x0   | RW | Force INITIALIZE signal.                                                                           |

| 4    | PORT_SELECTED_EN | 0x0   | RW | Enable port selection.                                                                             |

| 5    | PORT_SELECTED_0  | 0x0   | RW | Force port_selected[0] signal.                                                                     |

| 7:6  | SPARE            | 0x0   | RW | Spare.                                                                                             |

| 31:8 | RESERVED31_8     | 0x0   | R  | Reserved.                                                                                          |

RM0480 - Rev 2 page 16/80

Table 37. MOD0\_DIG\_TST register description

| Bit  | Field name         | Reset | RW | Description                                                               |

|------|--------------------|-------|----|---------------------------------------------------------------------------|

|      |                    |       |    | Selection                                                                 |

| 0    | MOD_DIG_TEST_SEL   | 0x0   | RW | - 0: forced by modulator (normal mode)                                    |

|      |                    |       |    | - 1: not forced by modulator but by MODx_TST registers values (test mode) |

| 2:1  | SPARE              | 0x0   | RW | Spare                                                                     |

|      |                    |       |    | Bypass modulation                                                         |

| 3    | PMU_NO_MODULTATION | 0x0   | RW | - 0: no bypass                                                            |

|      |                    |       |    | - 1: bypass                                                               |

| 7:4  | KFORCE_3_0         | 0x0   | RW | Fraction part.                                                            |

| 31:8 | RESERVED31_8       | 0x0   | R  | Reserved.                                                                 |

# Table 38. MOD1\_DIG\_TST register description

| Bit  | t | Field name   | Reset | RW | Description    |

|------|---|--------------|-------|----|----------------|

| 7:0  | ) | KFORCE_11_4  | 0x0   | RW | Fraction part. |

| 31:8 | 8 | RESERVED31_8 | 0x0   | R  | Reserved.      |

# Table 39. MOD2\_DIG\_TST register description

| Bit  | Field name   | Reset | RW | Description    |

|------|--------------|-------|----|----------------|

| 7:0  | KFORCE_19_12 | 0x80  | RW | Fraction part. |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved.      |

## Table 40. MOD3\_DIG\_TST register description

| Bit  | Field name   | Reset | RW | Description   |

|------|--------------|-------|----|---------------|

| 2:0  | AFORCE       | 0x0   | RW | Integer part. |

| 7:3  | MFORCE       | 0x13  | RW | Integer part. |

| 31:8 | RESERVED31_8 | 0x0   | R  | Reserved.     |

## Table 41. RXADC\_ANA\_USR register description

| Bit  | Field name                | Reset | RW | Description                                                                        |

|------|---------------------------|-------|----|------------------------------------------------------------------------------------|

| 2:0  | RFD_RXADC_DELAYTRIM_I     | 0x3   | RW | ADC loop delay control bits for I channel.                                         |

| 5:3  | RFD_RXADC_DELAYTRIM_Q     | 0x3   | RW | ADC loop delay control bits for Q channel.                                         |

| 6    | RXADC_DELAYTRIM_I_TST_SEL | 0x0   | RW | When set, RFD_RXADC_DELAYTRIM_I[2:0] bit field is used instead of the HW trimming. |

| 7    | RXADC_DELAYTRIM_Q_TST_SEL | 0x0   | RW | When set, RFD_RXADC_DELAYTRIM_Q[2:0] bit field is used instead of the HW trimming. |

| 31:8 | RESERVED31_8              | 0x0   | R  | Reserved.                                                                          |

RM0480 - Rev 2 page 17/80

Table 42. LDO\_ANA\_ENG register description

| Bit  | Field name             | Reset | RW | Description                                                              |

|------|------------------------|-------|----|--------------------------------------------------------------------------|

| 0    | SPARE                  | 0x0   | RW | Spare.                                                                   |

| 1    | RFD_LDO_TRANSFO_BYPASS | 0x0   | RW | VDD level Bypass mode - 0: Bypass mode disabled - 1: LDO in bypass mode. |

| 2    | RFD_LDO_RXADC_BYPASS   | 0x0   | RW | VDD level Bypass mode - 0: Bypass mode disable - 1: LDO in Bypass mode.  |

| 3    | RFD_LDO_RX_TX_BYPASS   | 0x0   | RW | VDD level Bypass mode - 0: Bypass mode disable - 1: LDO in Bypass mode.  |

| 7:4  | SPARE                  | 0x8   | RW | Spare.                                                                   |

| 31:8 | RESERVED31_8           | 0x0   | R  | Reserved.                                                                |

# Table 43. CBIAS0\_ANA\_ENG register description

| Bit  | Field name           | Reset | RW | Description             |

|------|----------------------|-------|----|-------------------------|

| 3:0  | RFD_CBIAS_IBIAS_TRIM | 0x7   | RW | Ibias current trimming. |