# RM0345 Reference manual

SPC563M64CAL144 calibration adapter board for SPC563M64xx devices

#### Introduction

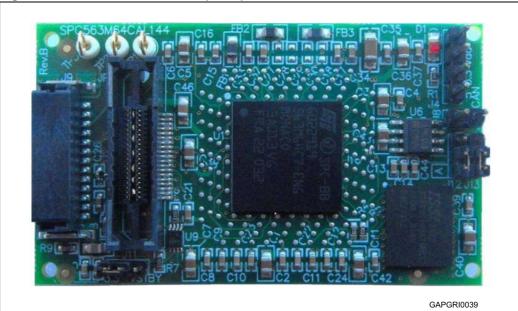

The SPC563M64CAL144 (rev.B) system is designed to enable the use of new enhanced automotive calibration and debug tools on the SPC563M64xx family of automotive microcontrollers.

The SPC563M64CAL144 (rev.B) can be fitted onto the application printed circuit board (PCB) in place of the standard SPC563M64xx family microcontroller in LQFP144 package. SPC563M64CAL144 (rev.B) hardware is designed to support two standardized tool connectors, allowing a variety of calibration and debug hardware to be connected and reused

Figure 1. SPC563M64CAL144 (rev.B)

Table 1. Board summary

| Order code      | On board device | Target footprint |

|-----------------|-----------------|------------------|

| SPC563M64CAL144 | SPC563M64xx     | QFP144           |

September 2013 Doc ID 024080 Rev 3 1/38

Contents RM0345

# **Contents**

| 1        | Calib | oration system overview                            | 6          |

|----------|-------|----------------------------------------------------|------------|

|          | 1.1   | Features overview                                  | 6          |

| 2        | Pow   | er supply                                          | 7          |

| 3        | Rese  | et and configuration signals1                      | 1          |

| 4        | Calib | oration bus interface and External Memory          | 2          |

|          | 4.1   | External memory specification                      | 2          |

|          | 4.2   | SRAM supply and data retention function            | 2          |

|          | 4.3   | Calibration bus interface                          | 4          |

| 5        | Deve  | elopment connector1                                | 5          |

| 6        | Calib | oration connector                                  | 7          |

| 7        | Tool  | IO1                                                | 9          |

| 8        | CAN   | interface                                          | 0          |

| 9        | Calik | oration software compatibility and configuration 2 | 2          |

|          | 9.1   | Calibration bus sw configuration                   |            |

|          |       | 9.1.1 Cal Bus PCR Settings                         |            |

|          |       | 9.1.2 Cal Bus ECCR Settings                        |            |

|          |       | 9.1.3 Cal Bus EBI Settings                         | <u>2</u> 4 |

|          | 9.2   | Example Configuration CODE                         | :7         |

| Appendix | A (   | Calibration base footprints                        | 9          |

| Appendix | В     | Mechanical constrains 3                            | 0          |

| Appendix | CS    | Schematic                                          | 3          |

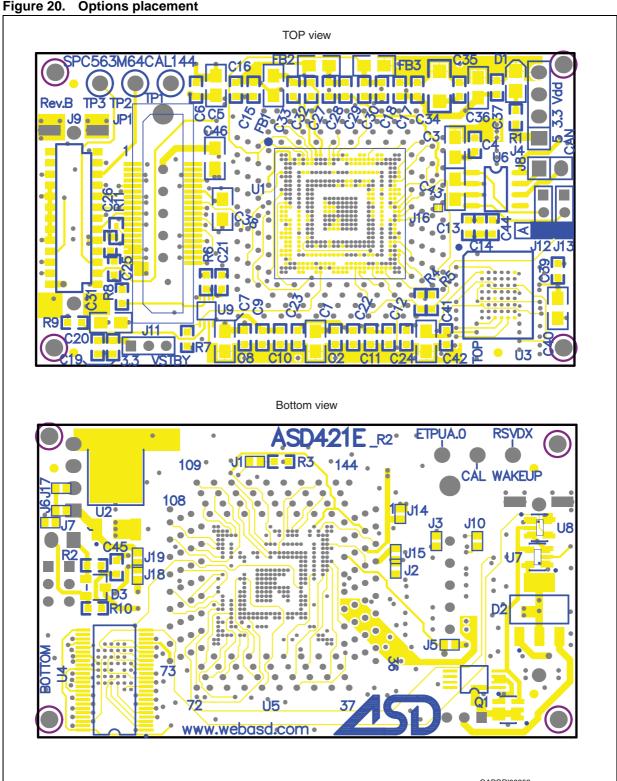

| Appendix | D (   | Options placement                                  | 6          |

| RM0345           | Contents |

|------------------|----------|

|                  |          |

| Revision history | 37       |

List of tables RM0345

# List of tables

| Table 1.  | Board summary                                       | 1  |

|-----------|-----------------------------------------------------|----|

| Table 2.  | J15, J2 and J14 option cut traces                   | 10 |

| Table 3.  | Reset and configuration signals                     |    |

| Table 4.  | J11 configuration of SRAM supply for retention mode | 13 |

| Table 5.  | J3, J5 and J10 option cut traces                    | 15 |

| Table 6.  | Nexus signals on AMP 38 Mictor connector            | 16 |

| Table 7.  | Nexus signals on AMP 38 Mictor connector            | 17 |

| Table 8.  | J12, J13 FlexCAN interface selection                | 20 |

| Table 9.  | J6, J17 and J7 FlexCAN interface selection          | 21 |

| Table 10. | CAN transceiver operating voltage selection         | 21 |

| Table 11. | Calibration bus signals configuration               | 22 |

| Table 12. | EBDF field definition                               | 23 |

| Table 13. | EBI_MCR register setting                            | 24 |

| Table 14. | EBI_CAL_BRx register setting                        | 25 |

| Table 15. | EBI_CAL_BOx register setting                        | 26 |

| Table 16  | Document revision history                           | 37 |

RM0345 List of figures

# List of figures

| Figure 1.  | SPC563M64CAL144 (rev.B)                  | 1    |

|------------|------------------------------------------|------|

| Figure 2.  | Power supply                             |      |

| Figure 3.  | Supply signals from the QFP144 footprint | 8    |

| Figure 4.  | Test points on J4 connector              | 8    |

| Figure 5.  | Supply signals on SPC563M64xx CSP496     | 9    |

| Figure 6.  | SRAM supply circuitry                    | . 13 |

| Figure 7.  | SRAM schematic diagram                   | . 14 |

| Figure 8.  | JP1 development connector                | . 15 |

| Figure 9.  | AMP 38 Mictor                            | . 16 |

| Figure 10. | J9 Calibration connector                 | . 17 |

| Figure 11. | Calibration triggers TOOL_IO             | . 19 |

| Figure 12. | CAN schematic diagram                    | 20   |

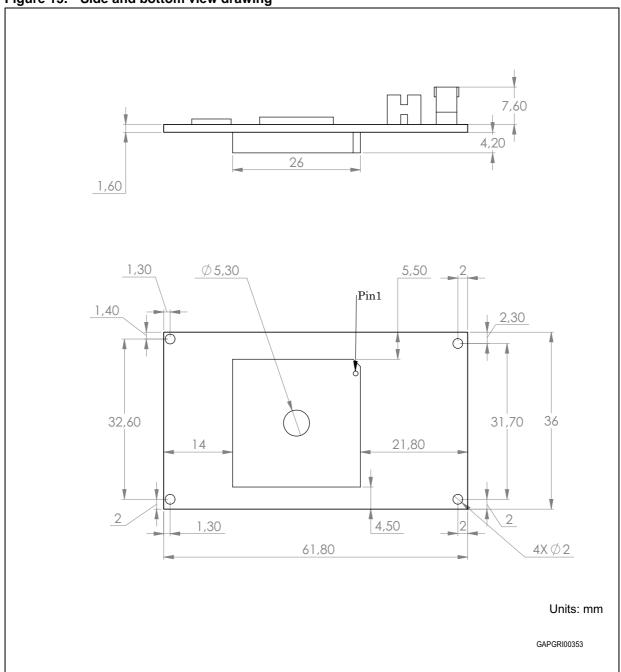

| Figure 13. | TQPACK144SD                              | . 29 |

| Figure 14. | Top and side view drawing                | 30   |

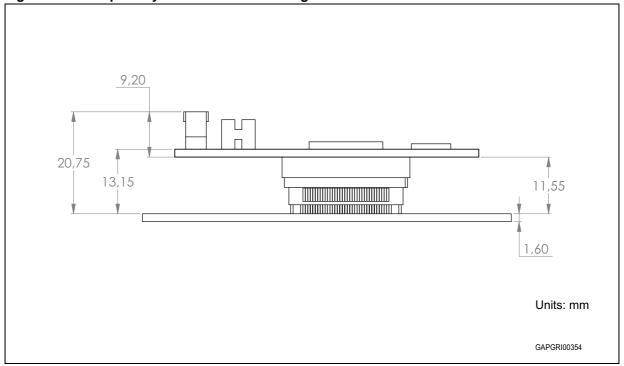

| Figure 15. | Side and bottom view drawing             |      |

| Figure 16. | Complete system side view drawing        | 32   |

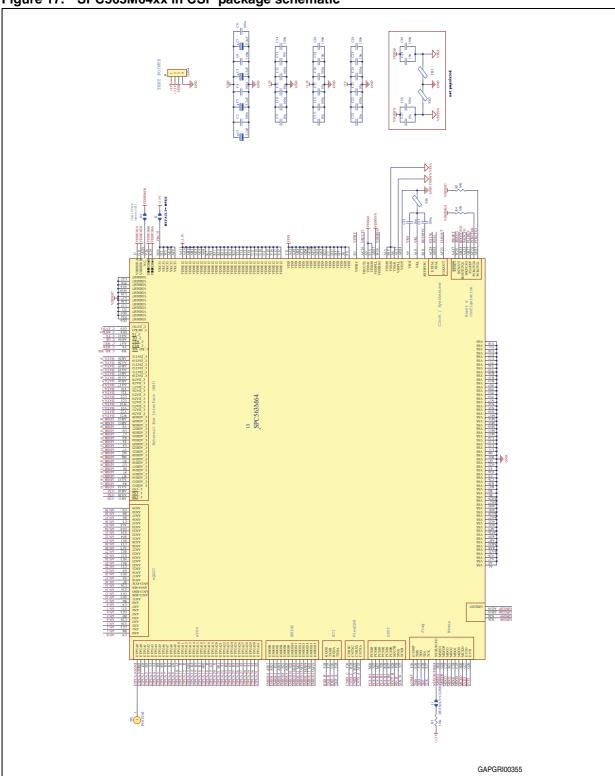

| Figure 17. | SPC563M64xx in CSP package schematic     | . 33 |

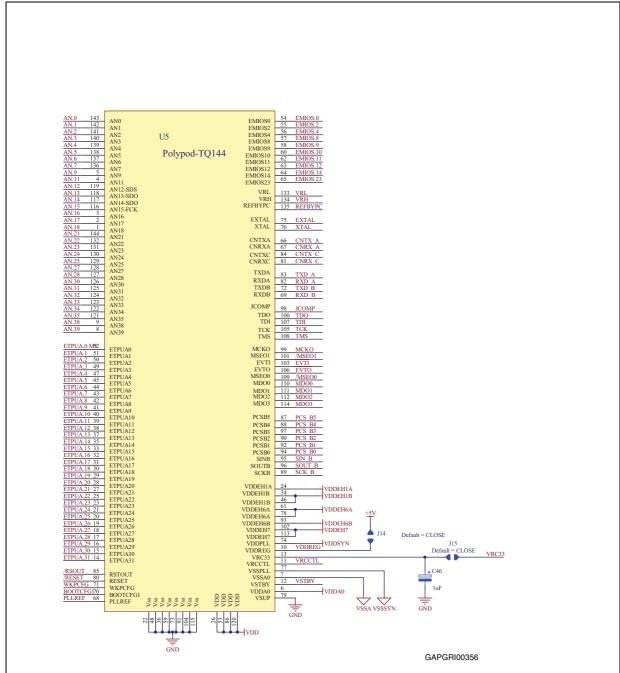

| Figure 18. | Polypod-TQ144 connector schematic        | . 34 |

| Figure 19. | Memory, CAN and connectors schematic     | 35   |

| Figure 20. | Options placement                        | . 36 |

## 1 Calibration system overview

The Calibration Adapter board features 2 Mbytes of SRAM in order to substitute to the SPC563M64xx internal Flash during calibration.

A voltage regulator is also integrated upon the board to generate, from selectable 5 V source, the 3.3 V voltage for the RAM and the calibration bus interface.

Development connector (Mictor AMP38) is providing the interface for the debug and trace tools.

A calibration connector (ERNI 154819) is providing an interface optimized for calibration usage.

A high speed CAN transceiver is connected to the FlexCAN of the mcu device.

The components chosen in the design of this board are automotive qualified to allow system evaluation over the full automotive evaluation range (-40 °C to 125 °C).

#### 1.1 Features overview

calibration systems include these distinctive features:

- Use 100% production silicon, ensuring full hardware and software compatibility between production and calibration systems;

- Support LQFP144 MCU production package allowing calibration systems to be built without requiring modifications to the standard production system housing;

- 2MByte static RAM organized as 1024K words by 16 bits;

- On-board latch providing a 16-bit de-multiplexed bus interface from the SPC563M64xx

16-bit multiplexed calibration interface;

- Support for Nexus-based debug tools even if application PCB does not include Nexus connector;

- Nexus functionality with 12 Message Data Out (MDO) signals;

- Support for full-feature calibration tools, via availability of comprehensive set of device signals available on the connectors;

- ERNI 154819 connector optimized for calibration;

- High speed CAN transceiver with signals protection;

- Allows system calibration without impacting standard MCU I/O resources;

- Allows system calibration regardless of availability of standard MCU external bus;

- Uses tried and tested technology.

RM0345 Power supply

## 2 Power supply

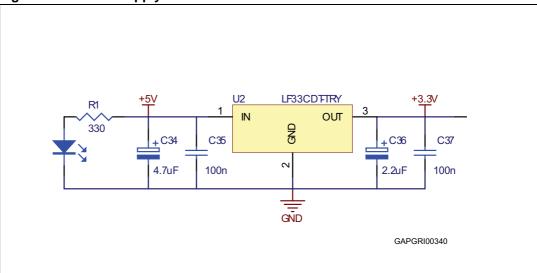

The Calibration boards requires a +5 V to supply the on board CAN transceiver and a +3.3 V to supply the SPC563M64xx calibration bus interface and for the external RAM.

The 3.3 V supply is generated on the SPC563M64CAL144 (rev.B) via the very low drop voltage regulator by using the +5V. A LED (D1) will light when the board is powered.

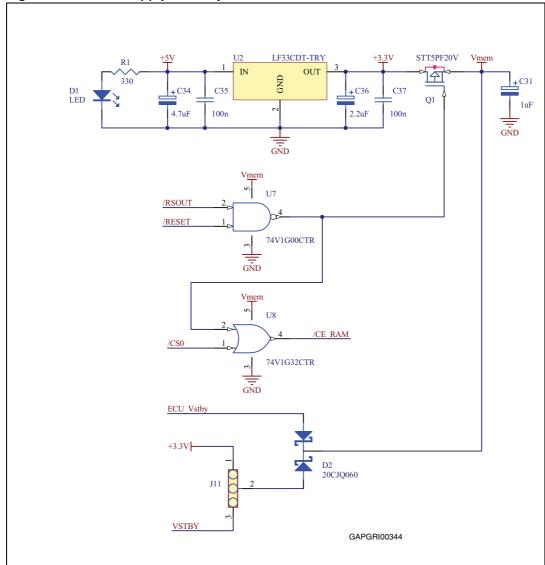

Figure 2. Power supply

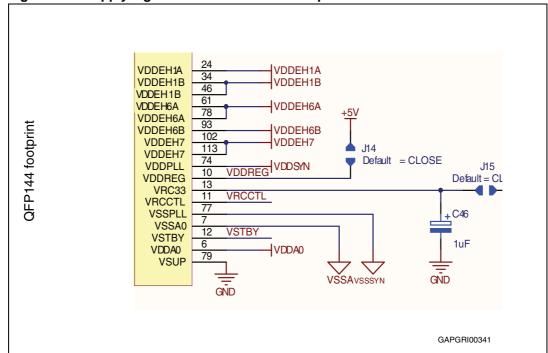

By default the 5V is taken from the target application through the VDDREG supply level (supply input for the internal voltage regulators of the SPC563M64xx). Gauge J14 enables the powering from the application board. *Table 2* shows its option configuration.

In case that no additional power loading could be applied to the application system during calibration, the +5V can be supplied externally via J4 connector (+5V test point, see *Figure 4*) and the gauge J14 (see *Figure 3*) must be open.

Power supply RM0345

Figure 3. Supply signals from the QFP144 footprint

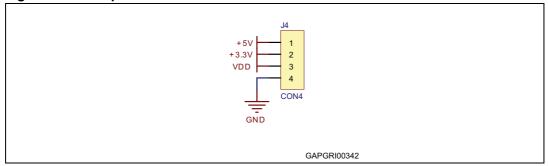

Figure 4. Test points on J4 connector

All power signals and voltage references of the SPC563M64xx QFP144 footprint from the application board are directly connected to the respective calibration device signals.

The VDDE12 supply used to power the dedicated SPC563M64xx calibration bus interface is connected to the upon board +3.3 V voltage regulator.

RM0345 Power supply

| VDBEHT | V

Figure 5. Supply signals on SPC563M64xx CSP496

The VRC33 signal of the CSP496 is connected to its respective signal of the QFP144 target application via the J15 cut trace option.

The VRC33 can be also connected to the on board +3.3V by closing the J2 gauge. In this case the gauge J15 must be open (*Table 2*).

Power supply RM0345

Table 2. J15, J2 and J14 option cut traces<sup>(1)</sup>

| Option name | Function   | Value              | Note                                                                                 |

|-------------|------------|--------------------|--------------------------------------------------------------------------------------|

|             | J15 VRC33  | open               | VRC33 signal is disconnected from the target application board                       |

| 315         |            | close<br>(default) | VRC33 signal is connected to the target application board                            |

| J2          | VRC33      | open<br>(default)  | VRC33 signal is disconnected from the on board +3.3V signal                          |

|             |            | close              | VRC33 signal is connected to the on board +3.3V signal                               |

| J14         | +5V supply | open               | +5V is powered from J4 connector                                                     |

|             |            | close<br>(default) | +5V is powered from target application via VDDREG pin of the QFP144 target footprint |

<sup>1.</sup> Refer to Chapter Appendix D: Options placement for layout Jumper placement

# 3 Reset and configuration signals

Calibration and debug tools may use the reset signals included in the connectors to have visibility of when the SPC563M64xx device has been reset. Debug tools may also require the ability to force device reset.

All signals of the SPC563M64xx QFP144 footprint from the application board are directly connected to the respective calibration device signals. This includes the following signals on the *Table 3*.

Table 3. Reset and configuration signals

| Signal name               | Function                 | Notes                                                                                                                                                                                                                                                                                                          |  |

|---------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reset / Configuration (5) |                          |                                                                                                                                                                                                                                                                                                                |  |

| /RESET                    | External reset input     | The /RESET pin is an active low input. The RESET pin is asserted by an external device during a power-on or external reset. The internal reset signal asserts only if the RESET pin asserts for 10 clock cycles. Assertion of the RESET pin while the device is in reset causes the reset cycle to start over. |  |

| /RSTOUT                   | External reset output    | The RSTOUT pin is an active low output that uses a push/pull configuration. The RSTOUT pin is driven to the low state by the MCU for all internal and external reset sources. There is a delay between initiation of the reset and the assertion of the RSTOUT pin.                                            |  |

| BOOTCFG[1]                | Boot configuration input | The BOOTCFG field holds the value of the BOOTCFG[1] pin that was latched on the last negation of the RSTOUT pin. The BOOTCFG field is used by the BAM program to determine the location of the Reset Configuration Word.                                                                                       |  |

| PLLREF                    | FMPLL Mode Selection     | PLLREF is used to select whether the oscillator operates in xtal mode or external reference mode from reset.  If RSTCFG is 0, External reference clock selected.  If RSTCFG is 1, Xtal oscillator mode is selected                                                                                             |  |

| WKPCFG                    | Weak Pull Configuration  | The signal on the WKPCFG pin determines whether weak pull up or pull down devices are enabled after reset on the eTPU and eMIOS pins.  0: Weak pulldown applied to eTPU and eMIOS pins at reset  1: Weak pullup applied to eTPU and eMIOS pins at reset.                                                       |  |

# 4 Calibration bus interface and External Memory

The SPC563M64xx features a 16-bit de-multiplexed calibration bus interface that is connected to an external 2Mbyte SRAM thanks to an on board latch.

### 4.1 External memory specification

The calibration board provides a SRAM with the following characteristics:

- 2Mbyte static RAMs organized as 1024K words by 16 bits;

- 16-bit data width;

- Fully static operation: no clock or refresh required;

- 3.3V input supply;

- /CE power-down;

- High-speed access time (10ns);

- Full automotive temperature range;

- Lead-free.

When /CE is HIGH (deselected), the device assumes a standby mode at which the power dissipation can be reduced down with CMOS input levels.

### 4.2 SRAM supply and data retention function

The circuitry in *Figure 6* has been implemented on the calibration board to protect the memory and to guarantee that the Working Page is valid after a power fail of the target application by putting the SRAM in standby powered.

The 3.3 V supply of the SRAM (Vmem) is gated by the RESET and RSTOUT signals of the SPC563M64xx.

The memory enable is driven via the SPC563M64xx chip select C\_CS0 "and" the RESETs signals combination.

Figure 6. SRAM supply circuitry

The jumper J11 (see *Figure 6*) allows to select the standby operation of the SRAM.

The standby voltage can be selected between:

- SPC563M64xx Vstby pin: same standby voltage as the internal RAM;

- the 3.3V generated on the calibration board;

- ECU\_Stby supplied by the calibration connector J9 (see Figure 10).

Table 4. J11 configuration of SRAM supply for retention mode

| J11        | SRAM standby supply source                                     |

|------------|----------------------------------------------------------------|

| all open   | ECU_Stby: standby voltage on J9 calibration connector          |

| 1-2 closed | Upon the board +3.3V generated                                 |

| 2-3 closed | VSTBY input pin of the SPC563M64xx from the target application |

#### 4.3 Calibration bus interface

The calibration bus is made up of address bus, data bus, and bus control signals, and is used on the calibration board to access the upon board memory.

The calibration board supports a 16-bit de-mulitplexed calibration bus. This is derived from the multiplexed bus on the SPC563M64xx, where the majority of address lines are derived from the data lines (CAL\_DATA on SPC563M64 device), by using an onboard external latch controlled by the C TS signal. The ALE functionality of this signal indicates to the external latch when to capture the address signals

GAPGRI00345

**SRAM** schematic diagram Figure 7.

The Section 9: Calibration software compatibility and configuration shows the necessary software configuration of the SPC563M64xx calibration interface.

## 5 Development connector

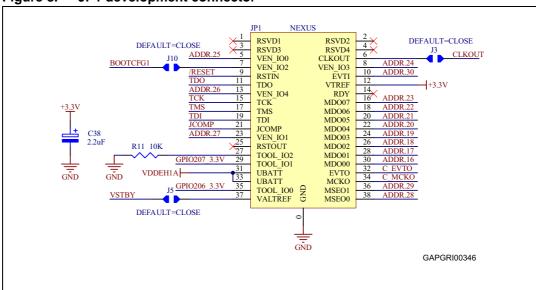

The JTAG signals and Nexus functionality with 12 Message Data Out (MDO) signals are available on the JP1 development connector (Nexus connector).

A hardware control bit in the SPC563M64xx Nexus port controller, is used to control whether the added signals for full width trace port are routed to the MDO[4:11] signals, or the CAL\_MDO[4:11] signals. This control bit is set by the cut trace J1 (default close) on the NEXUSCFG pin of the SPC563M64xx device, as on the calibration board the CAL\_MDO[4:11] signals are routed to the JP1 development connector.

Figure 8. JP1 development connector

The option cut trace J3, J5 and J10 are listed on *Figure 5*.

Table 5. J3, J5 and J10 option cut traces

| option<br>name | Function  | Value                                                   | Note                                                       |

|----------------|-----------|---------------------------------------------------------|------------------------------------------------------------|

|                | J3 CLKOUT | open                                                    | CLKOUT signal is disconnected to the Nexus JP1 connector   |

| 33             |           | close<br>(default)                                      | CLKOUT signal is connected to the Nexus JP1 connector      |

| I. VOTOV       | open      | VSTBY signal is disconnected to the Nexus JP1 connector |                                                            |

| J5             | J5 VSTBY  | close<br>(default)                                      | VSTBY signal is connected to the Nexus JP1 connector       |

| J10            | BOOTCFG1  | open                                                    | BOOTCFG1 signal is disconnected to the Nexus JP1 connector |

|                |           | close<br>(default)                                      | BOOTCFG1 signal is connected to the Nexus JP1 connector    |

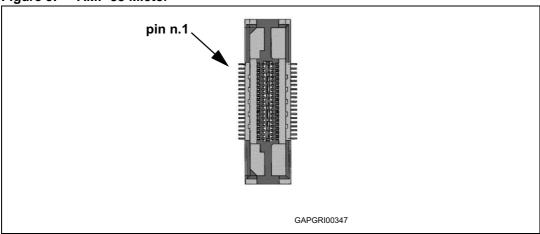

*Figure 6* shows the mapping of the development connector that provides Debug, Nexus trace and calibration signals. The port connector is an AMP 38 pin Mictor style.

Figure 9. AMP 38 Mictor

Table 6. Nexus signals on AMP 38 Mictor connector

|     | ······································ |  |  |

|-----|----------------------------------------|--|--|

| Pin | Description                            |  |  |

| 1   | nc                                     |  |  |

| 3   | nc                                     |  |  |

| 5   | C_MDO9                                 |  |  |

| 7   | BOOTCFG1*                              |  |  |

| 9   | /RESET                                 |  |  |

| 11  | TDO                                    |  |  |

| 13  | C_MDO10                                |  |  |

| 15  | TCK                                    |  |  |

| 17  | TMS                                    |  |  |

| 19  | TDI                                    |  |  |

| 21  | JCOMP                                  |  |  |

| 23  | C_MDO11                                |  |  |

| 25  | nc                                     |  |  |

| 27  | 10K pull down resistor                 |  |  |

| 29  | TOOL_IO1                               |  |  |

| 31  | VDDEH1A                                |  |  |

| 33  | VDDEH1A                                |  |  |

| 35  | TOOL_IO0                               |  |  |

| 37  | VSTBY*                                 |  |  |

| Pin | Descriptio         |

|-----|--------------------|

| 2   | nc                 |

| 4   | nc                 |

| 6   | CLKOUT*            |

| 8   | C_MDO8             |

| 10  | C_ <del>EVTI</del> |

| 12  | +3.3V              |

| 14  | RDY                |

| 16  | C_MDO7             |

| 18  | C_MDO6             |

| 20  | C_MDO5             |

| 22  | C_MDO4             |

| 24  | C_MDO3             |

| 26  | C_MDO2             |

| 28  | C_MDO1             |

| 30  | C_MDO0             |

| 32  | C_EVTO             |

| 34  | C_MCKO             |

| 36  | C_MSEO1            |

| 38  | C_MSEO0            |

<sup>\*)</sup> signal is connected via cut trace option

RM0345 Calibration connector

### 6 Calibration connector

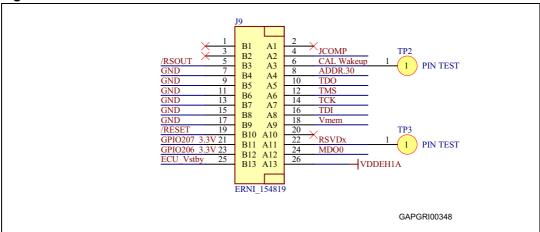

The board is equipped with an ERNI connector to give a more robust solution in terms of physical connectivity for Calibration purpose.

Figure 10. J9 Calibration connector

The *Table 7* shows the mapping of the calibration connector that provides Debug and calibration signals. The port connector is an ERNI 154819 style.

Table 7. Nexus signals on AMP 38 Mictor connector

| Pin | SPC563M64xx routing  | standard function                                    |

|-----|----------------------|------------------------------------------------------|

| B1  | nc                   | nc                                                   |

| B2  | nc                   | nc                                                   |

| ВЗ  | /RSOUT               | /RSOUT                                               |

| B4  | GND                  | GND                                                  |

| B5  | GND                  | GND                                                  |

| В6  | GND                  | GND                                                  |

| B7  | GND                  | GND                                                  |

| B8  | GND                  | GND                                                  |

| В9  | GND                  | GND                                                  |

| B10 | /RESET               | /RESET                                               |

| B11 | GPIO[207]<br>(@3.3V) | GPIO Pins for startup<br>handshake and<br>triggering |

| Pin | SPC563M64xx<br>routing | standard function                                  |

|-----|------------------------|----------------------------------------------------|

| A1  | nc                     | nc                                                 |

| A2  | JCOMP                  | JTAG interface                                     |

| А3  | CAL Wakeup             | 12V output for Wakeup functionality                |

| A4  | C_ <del>EVTI</del>     | JTAG interface                                     |

| A5  | TDO                    | JTAG interface                                     |

| A6  | TMS                    | JTAG interface                                     |

| A7  | TCK                    | JTAG interface                                     |

| A8  | TDI                    | JTAG interface                                     |

| A9  | Vmem                   | VDDSBRAM (Backup<br>Voltage of ECU<br>Standby RAM) |

| A10 | nc                     | nc                                                 |

| A11 | RSVDx                  | reserved Input,<br>connect pin to a solder<br>pad  |

Calibration connector RM0345

Table 7. Nexus signals on AMP 38 Mictor connector (continued)

| Pin | SPC563M64xx routing  | standard function                                         |

|-----|----------------------|-----------------------------------------------------------|

| B12 | GPIO[207]<br>(@3.3V) | GPIO Pins for startup<br>handshake and<br>triggering      |

| B13 | ECU_Vsby             | VDDSBRAM Supply<br>(Backup Voltage of<br>ECU Standby RAM) |

| Pin | SPC563M64xx routing | standard function                                                         |

|-----|---------------------|---------------------------------------------------------------------------|

| A12 | MDO 0               | Detect that the PLL is locked                                             |

| A13 | +5V                 | VDDP Comparator<br>Input (Supply of<br>microcontroller<br>Interface Pins) |

RM0345 Tool IO

### 7 Tool IO

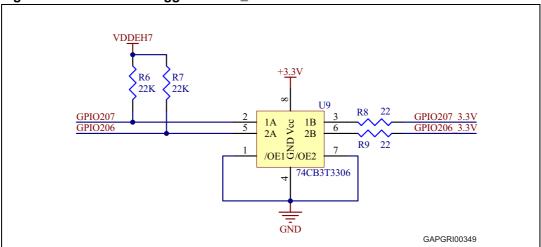

The SPC563M64xx in CSP496 package provides 2 signals, GPIO[206] & GPIO[207], that are not available in the QFP144 standard production package. They can be used by the calibration tools to implement triggers and handshakes. On the calibration board, these signals are available on the JP1 development connector and J9 calibration connector.

By default GPIO[206] & GPIO[207] are powered by VDDEH at 5V. A level shifter (see *Figure 11*) does the translation between the 5v and the 3.3V. This is because the calibration tools operates at 3.3V that is the voltage level of the JTAG and Nexus interfaces.

Figure 11. Calibration triggers TOOL\_IO

CAN interface RM0345

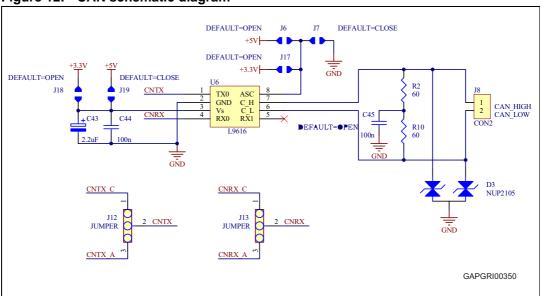

#### 8 CAN interface

The calibration board is equipped with one ST L9616 High-Speed Transceiver. It provides the Controller Area Network (CAN) communication interface through the SPC563M64xx CAN interface for calibration via CAN. This serial communication can reach speeds up to 1Mbps.

Figure 12. CAN schematic diagram

Two jumpers (J12 and J13), allow to select between the two FlexCAN interfaces of the SPC563M64xx mcu.

Table 8. J12, J13 FlexCAN interface selection

| FlexCAN interface | J12 pin configuration TX select | J13 pin configuration<br>RX select |

|-------------------|---------------------------------|------------------------------------|

| FlexCAN A         | 2 - 3                           | 2 - 3                              |

| FlexCAN C         | 2 - 1                           | 2 - 1                              |

The CAN channel is terminated with a 120 ohms resistor. Moreover, a protection circuitry has been designed to protect the CAN transceiver in high-speed and fault tolerant networks from ESD and other harmful transient voltage events (see *Figure 12*).

The L9616 CAN transceiver has an Adjustable Slope Control (ASC) feature that sets the slope speed using its ASC pin. This feature select the modes of operation:

- low speed (CAN baud rate up to 250kBaud)

- high speed (CAN baud rate from 250kBaud to 1000kBaud)

This pin can be put to high or to low by the cut trace options J6, J17 & J7 as described in *Table 9.*

RM0345 CAN interface

Table 9. J6, J17 and J7 FlexCAN interface selection

| J6 (or J17 if 3.3V) | J7     | FlexCAN interface                                               |

|---------------------|--------|-----------------------------------------------------------------|

| closed              | open   | low speed operation (default)<br>(CAN baud rate up to 250kBaud) |

| open                | closed | high speed operation (CAN baud rate from 250kBaud to 1000kBaud) |

The cut trace options J6, J17, J18 and J19 has been put in the design of this board to select the supply of the CAN transceiver between 5 V and 3.3 V. By this option is possible to replace the ST L9616 High-Speed Transceiver mounted on board by default, with a different transceiver that operates at 3.3 V.

Table 10. CAN transceiver operating voltage selection

| CAN Transceiver                         | J6                          | J17                         | J18   | J19   |

|-----------------------------------------|-----------------------------|-----------------------------|-------|-------|

| 5V - ST L9616 High-Speed<br>Transceiver | Adjustable<br>Slope Control | open                        | open  | close |

| 3.3V - CAN transceiver                  | open                        | Adjustable<br>Slope Control | close | open  |

Note: Refer to Section Appendix D: Options placement for layout options placement.

## 9 Calibration software compatibility and configuration

The calibration board uses standard production silicon packaged in the CSP (Chip Scale Package). Therefore, all production silicon features exist and are identical on the calibration board.

The required initialization code may be as simple as the configuration of the EBI and its related pins in the SIU, and it could be integrated into standard application software.

The calibration bus and the SIU can also be configured by an external tool connected to the debug port, removing the need of specific configuration functions in the application software.

#### 9.1 Calibration bus sw configuration

A 16-bit calibration bus is implemented on the board. In multiplexed mode the CAL\_DATA signals will output the address signals during the address phase by using an onboard external latch controlled by the CAL\_TS signal. The CAL\_ALE may be used to drive an external latch when an asynchronous memory is in use.

There are few steps to configure the SPC563M64xx Calibration Bus

- SIU PCR (Pad Configuration Register)

- SIU ECCR (External Clock Control Register)

- External Bus Interface (EBI)

#### 9.1.1 Cal Bus PCR Settings

The SIU PCR registers used to configure the calibration bus are shown in the *Table 11* The table also shows the recommended PA field setting.

Table 11. Calibration bus signals configuration

| signal name   | SPC563M64xx<br>mcu signal name | Function                | P A G (1) | PCR<br>PA<br>field | PCR (3) | Notes |

|---------------|--------------------------------|-------------------------|-----------|--------------------|---------|-------|

|               | Addr                           | ess/Data Bus (4         | 4)        |                    |         |       |

| C_DATA[0:15]  | CAL_DATA[0:15]                 | Calibration data bus    | -         | -                  | 341     |       |

| C_ADDR[12:15] | CAL_ADDR[12:15]                | Calibration address bus | -         | -                  | 340     |       |

| C_ADDR[16:31] | CAL_ADDR[16:31]                | Calibration address bus | -         | -                  | 345     |       |

| C_CS[0]       | CAL_CS[0]                      | Calibration chip select | -         | -                  | 336     |       |

| C_CS[1]       | Not Connected                  |                         |           |                    |         |       |

| C_CS[2]       | CAL_CS[2]                      | Calibration chip select | Р         | 1                  | 220     |       |

|               | CAL_ADDR[10]                   | Calibration address bus | Α         | 0                  | 338     |       |

| signal name | SPC563M64xx<br>mcu signal name | Function                            | PAG® | PCR<br>PA<br>field | PCR (3) | Notes                        |

|-------------|--------------------------------|-------------------------------------|------|--------------------|---------|------------------------------|

| C_CS[3]     | CAL_CS[3]                      | Calibration chip select             | Р    | 1                  | 339     |                              |

| 0_03[3]     | CAL_ADDR[11]                   | Calibration address bus             | Α    | 0                  | 339     |                              |

| C_OE        | CAL_OE                         | Calibration<br>Output enable        | ı    | -                  | 342     |                              |

| C_RD_WR     | CAL_RD_WR                      | Calibration<br>Read/write           | -    | -                  | 342     |                              |

| C_WE[0:1]   | CAL_WE[0:1]                    | Calibration<br>write/byte<br>enable | ,    | -                  | 342     |                              |

| C_TS        | CAL_TS                         | Calibration transfer start          | Р    | 1                  | 343     |                              |

| 0_13        | CAL_ALE                        | Address Latch enable                | Α    | 0                  | 343     |                              |

|             | Clock Synthesizer (1)          |                                     |      |                    |         |                              |

| C_CLKOUT    | CLKOUT                         | System clock output                 | Р    | 01                 | 229     | Clock output signal from MCU |

Table 11. Calibration bus signals configuration (continued)

#### Note:

- 1 The P/A/G column indicates the position a signal occupies in the muxing order for a pin: Primary, Alternate 1, Alternate 2, Alternate 3, or GPIO. Signals are selected by setting the PA field value in the appropriate PCR register in the SIU module. The PA field values are as follows: P 0b0001, A1 0b0010, A2 0b0100, A3 0b1000, or G 0b0000. Depending on the register, the PA field size can vary in length. For PA fields having fewer than four bits, remove the appropriate number of leading zeroes from these values.

- 2 The Pad Configuration Register (PCR) PA field is used by software to select pin function.

- 3 Values in the PCR No. column refer to registers in the System Integration Unit (SIU). The actual register name is "SIU\_PCR" suffixed by the PCR number.

#### 9.1.2 Cal Bus ECCR Settings

The SIU ECCR registers used to control the timing relationship between the system clock and the external clock CLKOUT.

The external bus clock (CLKOUT) divider can be programmed to divide the system clock by one, two or four based on the settings of the EBDF bit field.

Table 12. EBDF field definition

| Register | EBDF field | External Bus Division Factor |

|----------|------------|------------------------------|

| SIU_ECCR | 00         | 1                            |

|          | 01         | 2                            |

|          | 10         | reserved                     |

|          | 11         | 4                            |

#### 9.1.3 Cal Bus EBI Settings

For using the calibration bus with an external memory the user must configure the bus for multiplexed operation. These settings are located in two registers:

- EBI Module Configuration Register (EBI\_MCR)

- EBI Calibration Base Register (EBI\_CAL\_BRx)

- EBI Calibration Option Register (EBI\_CAL\_ORx)

The EBI Module Configuration Register contains bits which configure various attributes associated with EBI operation. In the EBI\_MCR register, the D16\_31, AD\_MUX and DBM fields need to be configured.

Table 13. EBI\_MCR register setting

| bit<br>field | Name                          | Description                                                                                                                                                                       | value |  |

|--------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

| 29           | D16_31 Data Bus 16 31 Select  | The D16_31 bit controls whether the EBI uses the DATA[0:15] or DATA[16:31] signals, when in 16-bit Data Bus Mode (DBM=1) or for chip-select accesses to a 16-bit port (PS=1).     | 0b0   |  |

|              | Data Data 10_01               | 1 = DATA[16:31] signals are used for 16-bit port accesses<br>0 = DATA[0:15] signals are used for 16-bit port accesses                                                             |       |  |

| 30           | AD_MUX<br>Address on Data Bus | The AD_MUX bit controls whether non-chip-select accesses have the address driven on (or sampled from for external master transfers) the data bus in the address phase of a cycle. | 0b1   |  |

| 00           | Multiplexing Mode             | <ul><li>1 = Address on Data Multiplexing Mode is used for non-CS accesses.</li><li>0 = Only Data on data pins for non-CS accesses.</li></ul>                                      |       |  |

| 0.4          | DBM                           | The DBM bit controls whether the EBI is in 32-bit or 16-bit Data Bus Mode.                                                                                                        | 01.4  |  |

| 31           | Data Bus Mode                 | 1 = 16-bit Data Bus Mode is used<br>0 = 32-bit Data Bus Mode is used                                                                                                              | 0b1   |  |

In the EBI\_CAL\_BRx register there are few fields that need to be configured, these are detailed in the *Table 14*.

Table 14. EBI\_CAL\_BRx register setting

| bit<br>field | Name                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | value |

|--------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|              |                                     | These bits are compared to the corresponding unmasked address signals among ADDR[0:16] of the internal address bus to determine if a memory bank controlled by the memory controller is being accessed by an internal bus master                                                                                                                                                                                                                                                                                                                            |       |

| 0-16         | BA<br>Base address                  | Note: An MCU may have some of the upper bits of the BA field tied to a fixed value internally in order to restrict the address range of the EBI for that MCU. Refer to the device-specific documentation to see which bits are tied off, if any, for a particular MCU. Tied-off bits can be read but not written. These bits are ignored by the EBI during the chip-select address comparison. However, the internal bridge of the MCU most likely requires that the chipselect banks be located in memory regions corresponding to the fixed values chosen | 1     |

| 20           | PS<br>Port Size                     | The PS bit determines the data bus width of transactions to this chip-select bank.  Note: In the case where the DBM bit in EBI_MCR is set for 16-bit Data Bus Mode, the PS bit value is ignored and is always treated as a '1' (16-bit port).  1 = 16-bit port                                                                                                                                                                                                                                                                                              | 0b1   |

|              |                                     | 0 = 32-bit port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

|              | AD_MUX                              | The AD_MUX bit controls whether accesses for this chip select have the address driven on the data bus in the address phase of a cycle                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| 24           | Address on Data Bus<br>Multiplexing | <ul> <li>1 = Address on Data Multiplexing Mode is enabled for this chip select.</li> <li>0 = Address on Data Multiplexing Mode is disabled for this chip select.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                 | 0b1   |

|              | WEBS                                | This bit controls the functionality of the WE[0:3]/BE[0:3] signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| 26           | Write Enable / Byte<br>Select       | 1 = The WE[0:3]/BE[0:3] signals function as BE[0:3]<br>0 = The WE[0:3]/BE[0:3] signals function as WE[0:3]                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0b1   |

| 30           | BI<br>Burst Inhibit                 | This bit determines whether or not burst read accesses are allowed for this chipselect bank. The BI bit is ignored (treated as 1) for chip-select accesses with external TA (SETA=1).                                                                                                                                                                                                                                                                                                                                                                       | 0b1   |

|              |                                     | 1 = Disable burst accesses for this bank. This is the default value out of reset (or when SETA=1). 0 = Enable burst accesses for this bank]                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

Table 14. EBI\_CAL\_BRx register setting

| bit<br>field | Name           | Description                                                                                                                                                                                                                                         | value |

|--------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 31           | V<br>Valid bit | The user writes this bit to indicate that the contents of this Base Register and Option Register pair are valid. The appropriate CS signal does not assert unless the corresponding V-bit is set.  1: This bank is valid  0: This bank is not valid | 0b1   |

The EBI Option Registers are used to define the address mask and other attributes for the corresponding chip select. The SCY field of the EBI\_CAL\_BOx register is detailed in the *Table 15*.

Table 15. EBI\_CAL\_BOx register setting

| bit<br>field | Name                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | value |

|--------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 0-16         | AM<br>Address Mask                      | This field allows masking of any corresponding bits in the associated Base Register.  Masking the address independently allows external devices of different size address ranges to be used. Any clear bit masks the corresponding address bit. Any set bit causes the corresponding address bit to be used in comparison with the address pins.  Address mask bits can be set or cleared in any order in the field, allowing a resource to reside in more than one area of the address map. This field can be read or written at any time. | -     |

| 24-27        | SCY<br>Cycle length in clocks           | This field represents the number of wait states (external cycles) inserted after the address phase in the single transfer case, or in the first beat of a burst, when the memory controller handles the external memory access. Values range from 0 to 15 and its depends on the RAM connected on top board.  This is the main parameter for determining the length of the cycle. These bits are ignored when SETA=1.  The total cycle length for the first beat (including the TS cycle) = (2+SCY) external clock cycles.                  | -     |

| 29-30        | BSCY<br>Burst beats length in<br>clocks | This field determines the number of wait states (external cycles) inserted in all burst beats except the first, when the memory controller starts handling the external memory access and thus is using SCY[0:3] to determine the length of the first beat.  These bits are ignored when SETA=1.  The total memory access length for each beat is (1 + BSCY) external clock cycles.  The total cycle length (including the TS cycle) = (2+SCY) + (#beats(h)-1) * (BSCY+1).                                                                  | -     |

26/38 Doc ID 024080 Rev 3

### 9.2 Example Configuration CODE

The following code is used to configure the calibration bus for 16bit de-multiplexed mode.

```

// SIU PCR (Pad Configuration Register) setup

// (Cal BUS bommon drive strength = 20pF, DSC = 0b01)

SIU.PCR[336].R = 0x0040; //CAL CS[0]DSC=20pF (0b01)

SIU.PCR[338].R = 0x0440; //CAL CS[2] (PA=0b1), DSC=20pF (0b01)

SIU.PCR[339].R = 0x0040; //CAL ADDR[11] (PA=0b0), DSC=20pF (0b01)

SIU.PCR[340].R = 0x0040;//CAL ADDR[12..15], DSC=20pF (0b01)

SIU.PCR[345].R = 0x0040; //CAL ADDR[16..30], DSC=20pF (0b01)

SIU.PCR[341].R = 0x0040; //CAL DATA[0..15], DSC=20pF (0b01)

SIU.PCR[342].R = 0x0040;//CAL RD/WR, CAL WE[0-1], CAL OE, DSC=20pF

(0b01)

SIU.PCR[343].R = 0x0040;//CAL ALE, DSC=20pF (0b01)

// SIU ECCR (External Clock Control Register) setup

//-----

SIU.ECCR.R = 0x1000//External Bus Division Factor = 1 (EBDF=0b00)

// EBI Registers setup

// EBI MCR setup for 16-bit bus configuration:

//

// EARP = 01 (Equal priority);

// D16_31 = 0 (DATA[0:15] signals are used for 16-bit port accesses);

// AD_MUX = 1 (Addr on Data Multiplexing Mode is used for non-CS acc.);

// DBM = 0 (32-bit Data Bus Mode is used);

EBI.MCR.R = 0x802;

//----

// EBI Base Register setup for 16-bit bus configuration:

// Base Address = 0x20000000;

// PS = 1 (16-bits port size)

// AD MUX = 1 (Address on Data Multiplexing Mode is enabled for this chip select);

// WEBS = 1 (Use BE function);

// BI = 1 (Disable burst accesses for this bank);

// V = 1 (Valid CS Bank)

EBI.CAL CS[0].BR.R = 0x200008A3;

```

```

//-

// EBI Option Register setup:

//

// Address mask = 0xefe00000;

// Wait state = 0 (set 0 wait states);

EBI.CAL_CS[0].OR.R = 0xffe00000;

```

28/38 Doc ID 024080 Rev 3

# Appendix A Calibration base footprints

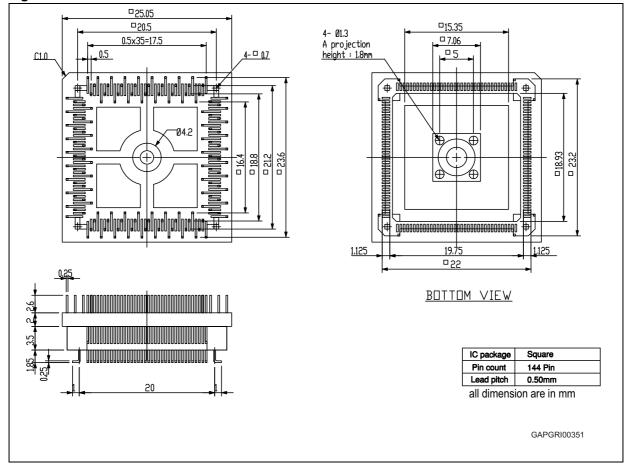

SPC563M64CAL144 (rev.B) calibration board had footprint compatible with QFP144 production package version of SPC563M64xx devices, ensuring that they can be fitted to an application PCB that has been designed to accept standard QFP144 packaged SPC563M64xx devices.

Bases can be supplied with solder footprints, to allow direct and permanent soldered connection to an application PCB, or with pin adapter connectors fitted, allowing connection and removal from an application PCB that is fitted with a compatible receiver socket.

Figure 13. TQPACK144SD

RM0345 **Mechanical constrains**

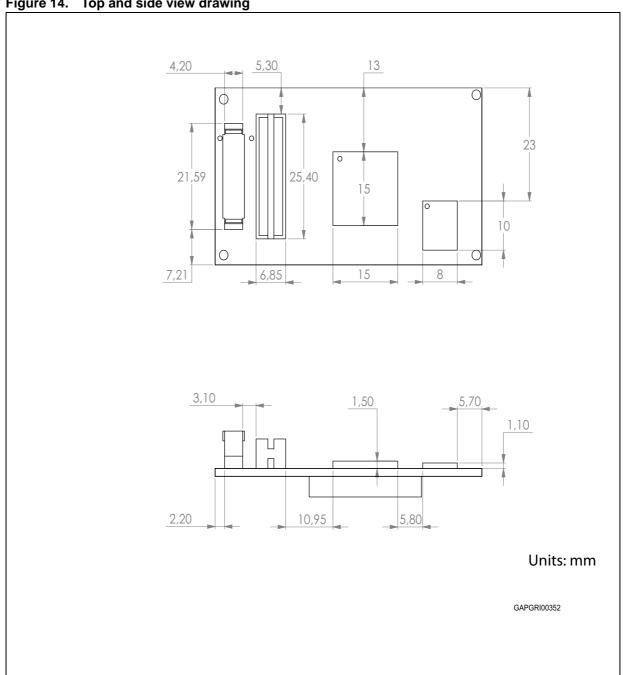

#### **Mechanical constrains Appendix B**

Figure 14. Top and side view drawing

RM0345 Mechanical constrains

Figure 15. Side and bottom view drawing

Mechanical constrains RM0345

Figure 16. Complete system side view drawing

RM0345 Schematic

# Appendix C Schematic

Figure 17. SPC563M64xx in CSP package schematic

Schematic RM0345

Figure 18. Polypod-TQ144 connector schematic

RM0345 Schematic

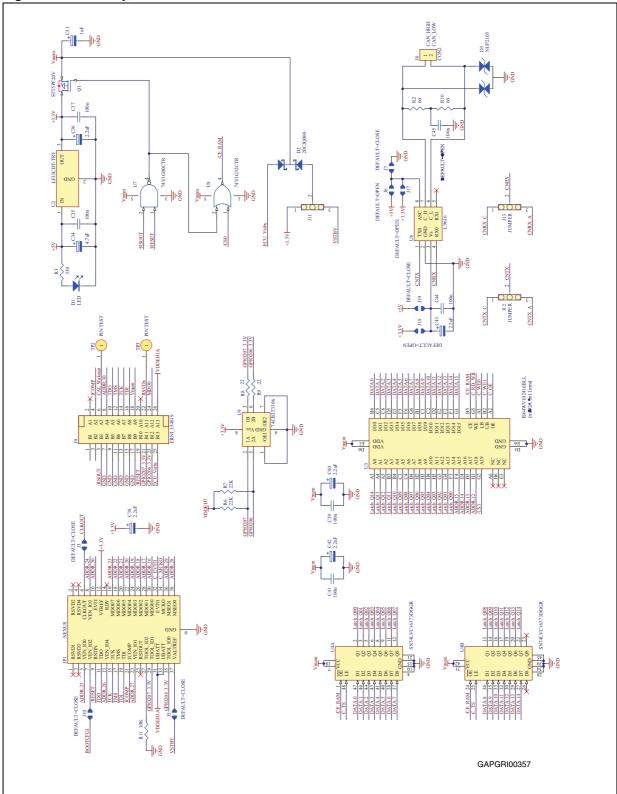

Figure 19. Memory, CAN and connectors schematic

**Options placement** RM0345

# Appendix D Options placement

Figure 20. Options placement

RM0345 Revision history

# **Revision history**

Table 16. Document revision history

| Date        | Revision | Changes             |

|-------------|----------|---------------------|

| 18-Jan-2013 | 1        | Initial release.    |

| 13-Feb-2013 | 2        | Modified Figure 14. |

| 17-Sep-2013 | 3        | Updated Disclaimer. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

38/38 Doc ID 024080 Rev 3