## STM32L4 – 独立型ウォッチドッグ (IWDG)

独立型ウォッチドッグ (IWDG)

Revision 1

Jan - 2016

こんにちは、STM32独立型ウォッチドッグのプレゼンテーションによこそ。こちらでは、問題が発生したときにデバイスをリセットするウォッチドッグとして、または、アプリケーションのタイムアウト管理のためのフリーランニングタイマとして使用することができるこのペリフェラルの主な機能を説明します。

- ・ソフトウェアの障害による誤動作を検出し解決するのに役立ちます:

- ・カウンタが指定されたタイムアウト値に達したときにシステムリセットをトリガ

- ・メインクロックが停止した場合でも、常にアクティブ

- ・アクティブ化して直ぐに無効にすることはできず、リフレッシュされる必要があります

## アプリケーションの利点

- ・メインアプリケーションの外部で完全に独立したプロセス

- ・選択可能なハードウェアまたはソフトウェアスタート

- ・スタンバイまたはストップモードでの選択可能なローパワーフリーズ

独立型ウォッチドッグは、ソフトウェアの障害に起因する誤動作を検出し解決するために使用されます。そのカウンタがタイムアウト値に達したときにリセットシーケンスをトリガします。そのクロックは、独立した32kHzの低速内蔵RC発振器(LSI)であるため、メインクロックが停止してもアクティブのままになります。一度、有効にすると、その状態は、リセットによってのみ無効にすることができます。アプリケーションのための主な利点の1つは、メインクロックから独立して実行する能力です。また、IWDGは、ハードウェアまたはソフトウェアを介し、オプションバイトを使用して設定することもできます。IWDGカウンタは、スタンバイまたはストップモードの間、フリーズさせることができます。

- IWDG の主な機能

- 12bitフリーランニング・ダウンカウンタ

- 独立したRC発振器(LSI)からのクロック駆動

- 条件リセット(ウォッチドッグが起動している場合):

- ダウンカウンタの値が0x000になったとき

- ダウンカウンタが、ウインドウの外で再読み込みされた場合

(ウインドウオプションが有効になっている場合)

IWDGは、12bitフリーランニングダウンカウンタを備えています。これは、32kHzで独立した低速内蔵RC発振器によってクロック駆動されます。IWDGがアクティベートされたとき、ダウンカウンタが0に達するかウインドウの外で再ロードされるとリセットが生成されます。(このオプションが有効になっている場合)

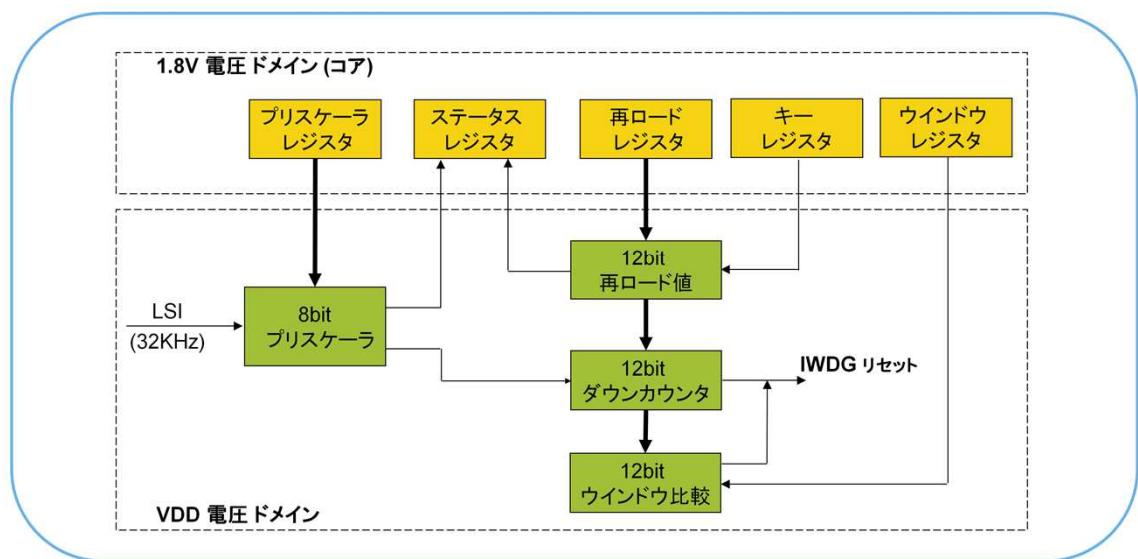

この機能がVDD電圧ドメインにある間、IWDGレジスタは、コア電圧ドメインに位置しています。このアーキテクチャにより、IWDGが、ストップとスタンバイモードで動作を継続できるようになります。8ビットプリスケーラは、LSIの発振器周波数を分周するため使用されます。IWDGが開始されると、12ビットカウンタは、0xFFFFのリセット値からダウンカウントを開始します。IWDGカウンタを更新するには、キー値(0xAAAA)が、カウンタの値をリロードするためのキー寄存器に書き込まれる必要があります。ダウンカウンタが、カウント値の終わり(0x000)に達した場合、システムリセットが発生します。ウィンドウのオプションを有効にすると、カウンタはウィンドウ内でリフレッシュする必要があります。そうしないと、システムリセットが生成されます。

# IWDGのハードウェアスタートの設定

5

- IWDGハードウェアは、オプションバイトを介してイネーブルされます。

- キーレジスタ(IWDG\_KR)は、カウンタが0になる前にウィンドウ内(ウィンドウオプションが有効になっている場合)で、定期的に0x0000 AAAAがソフトウェアによって書き込まれる必要があります。

IWDGハードウェアは、デバイスのオプションバイトで有効になっています。イネーブルにした場合、ウォッチドッグは自動的に電源投入時に起動します。

リセットされないように、キーレジスタは、カウンタが0に到達する前やウィンドウ内(このオプションが選択されている場合には)で、定期的にリフレッシュされる必要があります。

# IWDGのソフトウェアスタートの設定

6

- IWDG\_KRレジスタに0x0000 CCCCを書込むことによってIWDGを有効

- IWDG\_KRレジスタに0x0000 5555を書込むことによってレジスタアクセスを有効

- IWDG\_PRをプログラミングすることによってIWDGプリスケーラを設定

- IWDG\_RLR再ロードレジスタIWDG\_RLRを設定

- レジスタが更新されるのを待ちます(IWDG\_SR=00000000)

- ウィンドウオプションイネーブル: IWDG\_WINRレジスタのウィンドウ値を書き込みます。これは自動的にカウンタ値IWDG\_RLRをリフレッシュします。

- ウィンドウオプションディセーブル: IWDG\_KRレジスタに0x0000 AAAAを書込むことによってカウンタ値をリフレッシュします。

IWDGのソフトウェアスタートは、いくつかのステップで構成されています。

- 最初のステップは、ウォッチドッグを開始する値0x0000 CCCCをキーレジスタを書くことです。

- 次に、キーを解錠するために0x0000 5555を書込むことによってIWDGレジスタの保護を解除します。

- カウンタクロックを供給するプリスケーラ分周器を選択することにより、IWDG\_PRレジスタのIWDGプリスケーラを設定します。

- ウォッチドッグカウンタにロードされる値を定義するために再ロードレジスタ(IWDG\_RLR)に書き込みます。

- 前のレジスタにアクセスした後、レジスタが更新されたことを確認するために、IWDG\_SRビットがリセットされるのを待つ必要があります。

- 二つのオプションが利用可能になります: イネーブルまたはディセーブルIWDGウィンドウオプション。

- ウィンドウオプションを有効にするには、IWDG\_WINRレジスタにウィンドウの値を書き込みます。

- ・それ以外の場合は、ウィンドウのオプションをディセーブルするために、キーレジスタに0x0000 AAAAを書込むことによりカウンタをリフレッシュします。

# IWDGの設定およびリセットフラグ

7

- IWDG タイムベースの設定:

- LSIのクロック(32kHz)からプリスケールされたIWDGタイムベース

- 7つのプリデバイダ:IWDG\_PRレジスタによって選択可能な4~256(12bitウォッチドッグカウンタの再ロード値、RLR[11:0])

- 以下の式を用いてIWDGタイムアウトを設定します:

$$t_{IWDG} (\text{ms}) = t_{LSI} (\text{ms}) \times 4 \times 2^{(IWDG\_PR[2:0])} \times (IWDG\_RLR[11:0] + 1)$$

ここで、 $t_{LSI} (\text{ms}) = 1/32000 = 0.03125$

最小と最大タイムアウト値は、125μs から 32.8sです。

- IWDGリセットソースのチェック:

- IWDGRSTF リセットフラグ(RCC\_CSRレジスタ内)は、IWDGリセットが発生したとき(デバイスのリセット後)、通知します。

IWDGタイムベースは、32kHzのLSIクロックからプリスケールされます。IWDG\_PRプリスケーラレジスタは、4~256までの値で、LSIのクロック周波数を分割することができます。ウォッチドッグカウンタ再ロード値は、IWDG\_RLRレジスタに書き込まれた12ビットの値です。式は、IWDGタイムアウトを決定するのに使用することができます。IWDGの時間は、LSIの周期とそのプリスケーラだけでなく、選択されたウォッチドッグカウンタ再ロード値にももとづいています。パラメータの制限を考えると、IWDGタイムアウト値は、125μsから32.8sまでの間とすることができます。リセットがIWDGペリフェラルによって生成されると、対応するフラグIWDGRSTFが、リセットのソースを知らせるためにRCC\_CSRレジスタに設定されます。

- コアが、DBGモジュール内のDBG\_IWDG\_STOPの構成ビットに応じて休止したとき、IWDGカウンタは停止可能です。

マイクロコントローラがデバッグモード(コア停止)に入ると、DBGモジュール内(MCU APB1 register 1)のDBG\_IWDG\_STOPコンフィギュレーションビットに応じて、IWDGカウンタは正常または停止動作のいずれかを継続します。

# ローパワーモード

9

| モード                            | 説明                                                    |

|--------------------------------|-------------------------------------------------------|

| ラン(Run)                        | アクティブ*.                                               |

| スリープ(Sleep)                    | アクティブ*.                                               |

| ローパワーラン<br>(Low-power run)     | アクティブ*.                                               |

| ローパワースリープ<br>(Low-power sleep) | アクティブ*.                                               |

| ストップ1(Stop 1)                  | アクティブ* またはカウンターフリーズは、FLASH_OPTRレジスタのIWDG_STOPビットに応じて。 |

| ストップ2(Stop 2)                  | アクティブ*またはカウンターフリーズは、FLASH_OPTRレジスタのIWDG_STOPビットに応じて。  |

| スタンバイ(Standby)                 | アクティブ*またはカウンターフリーズは、FLASH_OPTRレジスタのIWDG_STDBYビットに応じて。 |

| シャットダウン(Shutdown)              | パワーダウン.                                               |

\*IWDGがイネーブルの場合

IWDGは、パワーダウンされたシャットダウンモードを除いて、すべての動作モードとローパワーモードでアクティブにすることが可能です。それに、ストップ1、ストップ2モードとスタンバイモードでは、ウォッチドッグカウンタは、FLASH\_OPTRレジスタの対応するビットをプログラムすることによってフリーズさせることができます。