# STM32L4 – I<sup>2</sup>C

インター・インテグレーテッド・サーキット

Revision 1

Jan - 2016

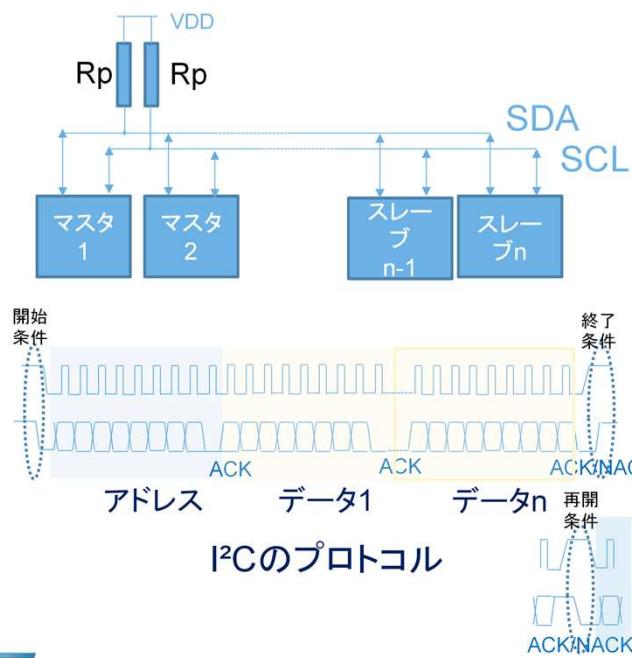

STM32L4の I<sup>2</sup>C [アイ・スクウェア・シー] インタフェースのプレゼンテーションへようこそ。本プレゼンテーションでは、マイコン、センサ、および、シリアルインターフェースメモリなどのデバイスを接続するために広く利用されている本通信インターフェースの主な機能について説明します。

- I<sup>2</sup>Cのインターフェースを提供

- I<sup>2</sup>Cバス仕様およびユーザマニュアル、リビジョン3

- 標準、高速、高速+(1 MHz)

- SMBus 2.0 ハードウェア対応

- PMBus 1.1 互換

### アプリケーションの利点

- 利用が簡単なイベント管理

- 完全にプログラム可能なタイミング値

- 低電力STOPモードで動作可能

I<sup>2</sup>CインターフェースはNXPのI<sup>2</sup>Cバス仕様およびユーザマニュアル、リビジョン3、SMBusシステム管理バス仕様、リビジョン2、および、PMBus電力システム管理プロトコル仕様、リビジョン1.1に準拠しています。

このペリフェラルは非常にシンプルなソフトウェアプログラミングおよび自由度の高いタイミング設定など利用が簡単なインターフェースを提供します。

さらに、I<sup>2</sup>Cペリフェラルは低電力STOPモードで動作可能です。

# 特長

3

- マルチマスタおよびスレーブに対応

- I<sup>2</sup>CのIOピンは以下で電源供給されます:

- VDD、1.71V から 3.6V で機能

- VDDIO2、1.08V から 3.6V で機能

- 高速+モードで20 mA出力の駆動能力

- 全てのI<sup>2</sup>Cバス特有のシーケンス、プロトコル、アビトリレーションおよびタイミング値

- 7および10bitのアドレッシングモード

- 複数 7bitアドレス対応

- クロック・ストレッチ・オプション

I<sup>2</sup>Cペリフェラルはマルチマスタおよびスレーブモードに対応しています。

I<sup>2</sup>CのIOピンはオープンドレインモードに設定する必要があります。

論理ハイレベルは外部プルアップより駆動されます。

I<sup>2</sup>Cのオルタネート機能は1.71Vから3.6Vの範囲のVDDで供給されるIOピンと、1.08Vから3.6Vの範囲のVDDIO2で供給されるIOピンで利用できます。

これにより、STM32L4の主要電源と異なる電圧の外部チップとの通信を可能にします。

代表的な使用例は、センサーハブアプリケーションでのアプリケーションプロセッサとの通信です。

IOピンは高速+モードで要求される20mA出力駆動に対応しています。

ペリフェラルは、全てのI<sup>2</sup>Cバス特有のシーケンス、プロトコル、調停およびタイミング値を制御します。

7および10ビットのアドレッシングモードに対応し、同じアプリ

ケーションで複数の7ビットアドレスに対応することも可能です。ペリフェラルは、スレーブのクロックストレッチに対応可能で、ソフトウェアでスレーブからのクロックストレッチを無効にできます。

- プログラム可能なセットアップおよびホールド時間

- SCLおよびSDAラインにおけるプログラム可能なアナログおよびデジタルノイズフィルタ

- アドレス一致によるSTOPモードからの復帰

- 独立クロックによりシステムクロックから独立した通信ボーレートを設定可能

セットアップおよびホールド時間はソフトウェアによりプログラム可能です。

データおよびクロックラインにおけるアナログおよびデジタルグリッチフィルタはソフトウェアにより設定可能です。

アドレス一致を検出時、ペリフェラルによりマイコンをSTOPモードから復帰させることができます、

ペリフェラルは独立クロックドメインを持つため、システムクロックから独立した通信ボーレートを設定可能です。

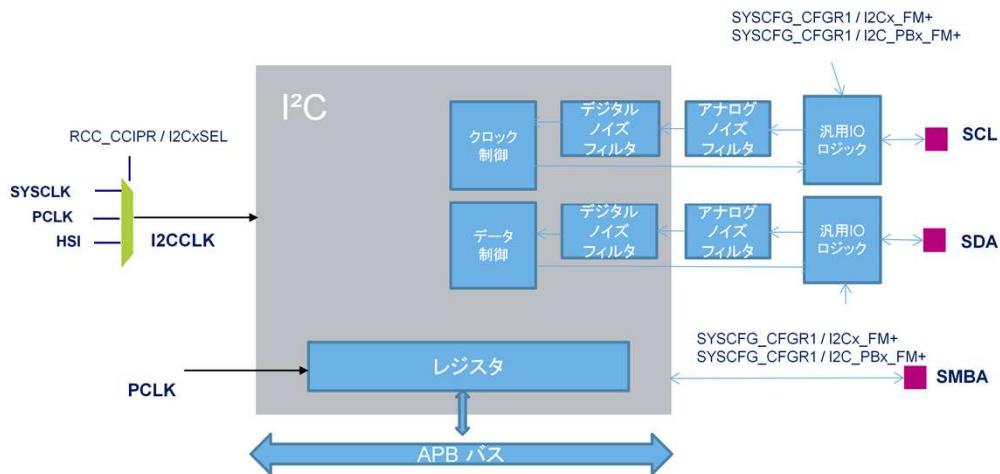

## ブロック図

5

こちらが、I<sup>2</sup>Cのブロック図です。

レジスタはAPBバスを介してアクセスし、ペリフェラルはAPBクロックから独立したI<sup>2</sup>Cクロックからクロック供給されます。

I<sup>2</sup>Cのクロックはシステムクロック、APBクロック、および、高速内蔵16MHz RCオシレータから選択できます。

SCLおよびSDAライン上にアナログおよびデジタルノイズフィルタがあります。

20mAの駆動能力はシステム設定レジスタの制御ビットより有効化できます。

更に、SMBus[“エス”“エム”バスと発音]モードでは、SMBusアラートピンが利用できます。

# I<sup>2</sup>C の SDA および SCL ノイズフィルタ

6

## 柔軟なノイズ・フィルタ

|           | アナログ・ノイズ・フィルタ          | デジタル・ノイズ・フィルタ                             |

|-----------|------------------------|-------------------------------------------|

| フィルタリング能力 | スパイク ≤ 50ns            | プログラム可能(I <sup>2</sup> Cクロック周期換算): 0 から15 |

| メリット      | STOPモードからの復帰が有効の場合利用可能 | フィルタ値をプログラム可能、プロセス、温度、電圧変化から独立            |

| 難点        | プロセス、温度、電圧によって変化       | STOPモードからの復帰が無効の場合利用不可                    |

STM32L4はI<sup>2</sup>Cのデータおよびクロックラインにノイズフィルタを搭載しています。

アナログノイズフィルタは最大50nsのスパイクをフィルタ可能で、ソフトウェアによって有効または無効に設定できます。

デフォルトでは、アナログノイズフィルタは有効です。

アナログノイズフィルタとは別にデジタルノイズフィルタはSDAおよびSCLライン上で有効化可能です。

これらのフィルタは、1から15サイクル分のI<sup>2</sup>Cクロック周期長にプログラム可能で、スパイクを打ち消す事ができます。

デジタルフィルタはI<sup>2</sup>C規格で要求される50nsに対して更なるフィルタ能力を提供します。

デジタルフィルタ値はソフトウェアで固定される一方、アナログフィルタ値はプロセス、温度および電圧によって変化します。

デジタルフィルタは、STOPモードからの復帰機能が有効な場合、ハードウェアで無効化されることにご注意下さい。

この場合、アナログフィルタのみ有効となります。

# I<sup>2</sup>Cのプログラム可能なタイミング

7

## 完全に柔軟なタイミング生成

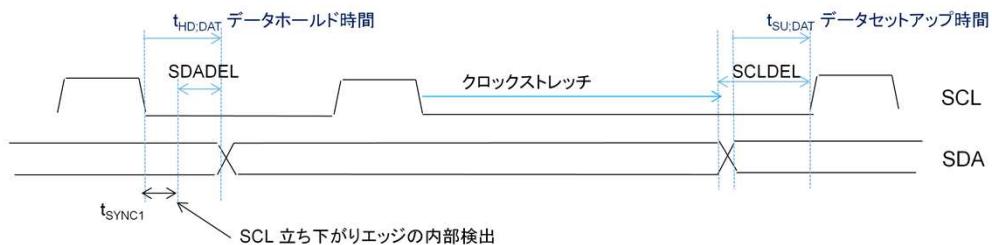

送信時のSDAおよびSCLライン間のセットアップおよびホールド時間はI<sup>2</sup>Cタイミングレジスタ(I2C\_TIMINGR)のPRESC、SDADEL、SCLDELフィールドにてプログラム可能です。

- SDADELはデータホールド時間の生成に使用します。 $t_{SDADEL} = [SDADEL * (PRESC+1) + 1] * t_{I2CCLK}$

- SCLDELはデータセットアップ時間の生成に使用します。 $t_{SCLDEL} = (SCLDEL+1) * (PRESC+1) * t_{I2CCLK}$

I<sup>2</sup>Cのセットアップおよびホールド時間はI<sup>2</sup>Cタイミングレジスタを介してソフトウェアにて設定可能です。

SDADELおよびSCLDELカウンタは送信時に使用され、最小データホールドおよびデータセットアップ時間を保証します。I<sup>2</sup>Cペリフェラルはデータ送信の前にクロックラインにて立ち下がりエッジを検出後、プログラムされたデータホールド時間の間、待機します。

データ送信後、クロックラインはプログラムされたデータセットアップ時間の間、ローにストレッチされます。

全体のデータホールド時間はプログラムされたSDADELカウンタよりも大きくなります。

これは、SCLの立下りエッジが内部で検出されて初めてSDADELの遅延が加えられることに起因します。

内部検出に必要な $t_{SYNC}$ 時間はSCLの立下りエッジ、フィルタによる入力遅延、および、内部でのSCLのI<sup>2</sup>Cとの同期に依存します。

しかしながら、セットアップ時間はこれらの内部遅延の影響を受けません。

# I<sup>2</sup>Cのマスタークロック生成

8

## 完全に柔軟なマスタークロック生成

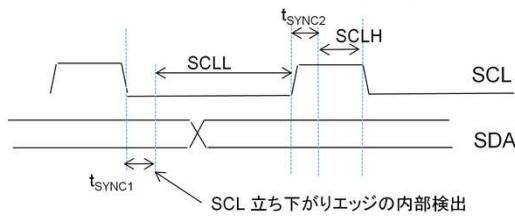

I<sup>2</sup>C\_TIMINGRによりSCLのロー時間およびハイ時間をプログラム可能

- SCL ローカウンタ:  $(SCLL+1) * (PRESC+1) * t_{I2CCLK}$

- SCLの立下りエッジを内部検出後、カウント開始。

- カウント後、SCLは開放されます。

- SCL ハイカウンタ:  $(SCLH+1) * (PRESC+1) * t_{I2CCLK}$

- SCLの立ち上がりエッジを内部検出後、カウント開始。

- カウント後、SCLはローに駆動されます。

- SCL周期 =  $T_{SYNC1} + T_{SYNC2} + [(SCLL+1) + (SCLH+1)] * (PRESC+1) * t_{I2CCLK}$

I<sup>2</sup>Cのマスタークロックのロー時間およびハイ時間はI<sup>2</sup>Cタイミングレジスタにてソフトウェアにより設定可能です。

SCLのローレベルおよびハイレベルカウンタはSCLラインのエッジを検出後に開始します。

この実装により、ペリフェラルはマルチマスター環境におけるマスタークロックの同期機能およびスレーブのクロックストレッチ機能が可能になります。

従って、全体のSCL周期はカウンタの合計よりも大きくなります。

これは、SCLラインのエッジ内部検出により加わる遅延に関係します。

これらの遅延、すなわち、 $t_{SYNC1}$  および  $t_{SYNC2}$  は、SCLの立下りまたは立ち上がりエッジ、フィルタによる入力遅延、および、内部のSCLとI<sup>2</sup>Cクロックの同期による遅延に依存します。

# スレーブアドレッシングモード

9

## 多数のスレーブアドレス

I<sup>2</sup>Cは複数のスレーブアドレスを認識することができます。

2つのアドレスレジスタ:

- I2C\_OAR1: 7または10ビットモード

- I2C\_OAR2: 7ビットモードのみ。OA2MSK[2:0]によりOAR2の0から7 LSBをマスクします

| OA2MSK[2:0] | アドレス一致条件                                   |

|-------------|--------------------------------------------|

| 000         | Address[7:1] = OA[7:1]                     |

| 001         | Address[7:2] = OA[7:2] (ビット1は無視)           |

| 010         | Address[7:3] = OA[7:3] (ビット2:1は無視)         |

| ...         |                                            |

| 111         | I <sup>2</sup> Cの予約済みアドレスを除く全てのアドレスは認識されます |

I<sup>2</sup>Cスレーブは複数のスレーブアドレスを認識することができます。

スレーブアドレスは2つのレジスタにプログラムされます。

自己アドレスレジスタ1へは、7または10ビットアドレスをプログラム可能です。

自己アドレスレジスタ2へは、7ビットアドレスをプログラム可能で、このアドレスの最下位ビットはOA2MSKレジスタを介してマスクし、

複数のスレーブアドレスを認識させることができます。

2つの自己アドレスレジスタは同時に有効にすることが出来ます。

# アドレス一致によるSTOPモードからの復帰

10

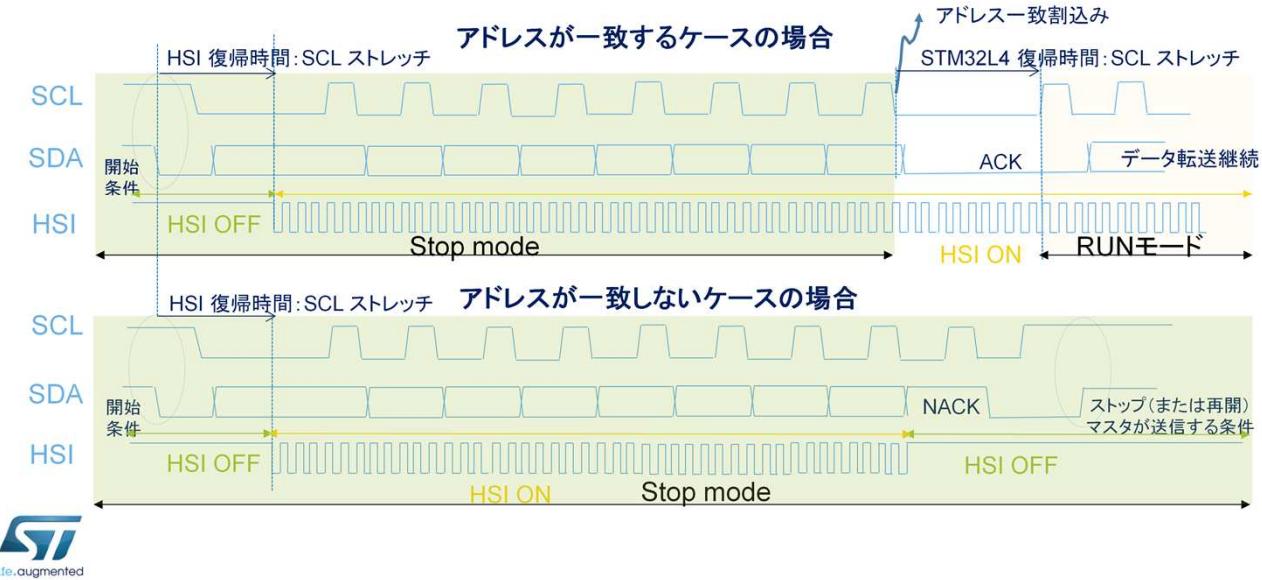

I<sup>2</sup>CCLKクロックがHSIに設定されている場合、I<sup>2</sup>Cは設定されたスレーブアドレスを受信時にマイコンをSTOPモードから復帰させることができます。全てのアドレッシングモードに対応しています。

I<sup>2</sup>Cペリフェラルはアドレス一致時のSTOPモードからの復帰に対応しています。

それを行う為には、I<sup>2</sup>Cペリフェラルのクロックを高速内部16MHzのRCオシレータに設定する必要があります。

STOPモードからの復帰機能が有効な場合、アナログノイズフィルタのみの対応となります。

全てのアドレッシングモードに対応します。

デバイスがSTOPモードの場合、高速内部オシレータは停止します。

開始条件が検出されると、I<sup>2</sup>Cペリフェラルは高速内部オシレータを有効化し、バス上でアドレスを受信するために使用されます。

STOPモードでアドレスを受信後、アドレスがプログラムされたスレーブアドレスと一致した場合、復帰割込みが生成されます。

アドレスが一致しない場合、高速内部オシレータは停止し、割込みは生成されず、デバイスはSTOPモードを維持します。

I<sup>2</sup>Cペリフェラルは開始条件後、高速内部オシレータが開始するまでの間、クロックラインをローにストレッチするためクロックストレッチは有効にする必要があります。

プログラムされたスレーブアドレスと一致したアドレスを受信後、I<sup>2</sup>CペリフェラルはSTM32L4デバイスが復帰するまでの間、クロックラインをローにストレッチします。

# シンプルなマスタモード管理

11

ペイロードが255バイト以下の場合：必要な書き込み回数は1回のみ

- START = 1

- SADD: スレーブアドレス

- RD\_WRN: 転送方向

- NBYTES = N: 転送バイト数

- AUTOEND = 1: N個のデータ後、自動でSTOPを送信

| AUTOEND        | 説明                                                                                                     |

|----------------|--------------------------------------------------------------------------------------------------------|

| 0: ソフトウェア終了モード | NBYTES バイトのデータ転送後、転送終了をソフトウェアで制御：<br>転送完了(TC)フラグがセットされ、有効な場合、割込みが生成されます。<br>再開またはストップ条件をソフトウェアで要求できます。 |

| 1: 自動終了モード     | NBYTES バイトのデータ転送後、ストップ条件が自動で送信されます。                                                                    |

マスタモードでのソフトウェア管理は非常にシンプルです。

書き込み処理1回のみで、255バイト以下のペイロードのマスタ転送を処理することができます。

完全なプロトコルはハードウェアによって管理されます。

マスタモードで転送を開始するには、I<sup>2</sup>C制御レジスタ2に、開始条件、スレーブアドレス、転送方向、転送バイト数、および、転送終了モードを書き込み必要があります。

転送終了モードはAUTOENDビットで設定されます。

このビットがセットされると、プログラムされたバイト数が転送された後、ストップ条件が自動で送信されます。

このビットがセットされていない場合、転送終了はソフトウェアで管理されます。

プログラムされたバイト数が転送された後、転送完了(TC)フラグがセットされ、有効な場合、割込みが生成されます。

その後、開始またはストップ条件がソフトウェアによって繰り返しリクエストされます。

データ転送は割込みまたはDMAにより管理することが出来ま

す。

# 簡単に使えるイベント管理

12

- ペイロードが255バイトより大きい場合: I<sup>2</sup>C\_CR2のRELOADビットをセットする必要があります。

- RELOADビットがセットされている場合、AUTOEND = 0は何の影響もありません。

| RELOAD     | 説明                                                                                             |

|------------|------------------------------------------------------------------------------------------------|

| 0: リロード無し  | NBYTESバイトのデータが転送され、その後、STOPまたはRESTARTが続きます。                                                    |

| 1: リロードモード | NBYTESバイトのデータを転送後、NBYTESがリロードされます: データ転送はレジュームされます<br>転送完了リロード(TCR)フラグがセットされ、有効な場合、割込みが生成されます。 |

ペイロードが255バイトより大きい場合、I<sup>2</sup>C制御レジスタ2にて RELOADビットをセットする必要があります。

その場合、プログラムされたバイト数分の転送後、転送完了リロード(TCR)フラグがセットされます。

TCRビットがセットされている場合、転送されるべき追加のバイト数がプログラムされ、データ転送はレジュームされます。 TCRがセットされている間、I<sup>2</sup>Cクロックはローにストレッチされます。

ペイロードが255バイトより大きい場合、RELOADビットはマスター modeで使用され、スレーブバイト制御が有効の場合、スレーブモードで使用されます。

RELOADビットがセットされていると、AUTOENDビットは何の影響も与えません。

## スレーブモード

13

- デフォルト:I<sup>2</sup>Cスレーブはクロックストレッチを使用。クロックストレッチはソフトウェアで無効にできます。

- 受信:認識制御はスレーブバイト制御(SBC)モードにてRELOAD=1とすることで選択したバイトで行なうことができます

- SBC = 1で、スレーブモード(TxおよびRxモード)のNBYTESカウンタが有効になります。

- SBC = 1は、NOSTRETCH=0時のみ設定可能です。

| SBC        | 説明                                                                                             |

|------------|------------------------------------------------------------------------------------------------|

| 0: リロード無し  | NBYTESバイトのデータが転送され、その後、STOPまたはRESTARTが続きます。                                                    |

| 1: リロードモード | NBYTESバイトのデータを転送後、NBYTESがリロードされます: データ転送はレジュームされます<br>転送完了リロード(TCR)フラグがセットされ、有効な場合、割込みが生成されます。 |

デフォルト時、I<sup>2</sup>Cスレーブはクロックストレッチを使用します。

クロックストレッチ機能はソフトウェアで無効にできます。

受信時、スレーブによる受信バイト認識の動作はスレーブバイト制御モードが選択されていて、RELOADビットがセットされている場合に設定できます。

SBCビットがセットされていると、スレーブモードでバイト数カウントが有効になります。

スレーブバイト制御が有効な場合、クロックストレッチが有効である必要があります。

受信時、スレーブバイト制御が有効でRELOADビットがセットされていて、転送バイト数が1の場合、各受信バイト後に転送完了リロードフラグがセットされ、SCLはストレッチされます。

これは、データ受信後で認識パルス前に行なわれます。

受信バッファノットエンプティフラグもセットされ、データの読み出しが可能となります。

TCRのサブルーチンで、バイト受信後に、認証、または、未認証の情報を送信するためにプログラム可能です。

I<sup>2</sup>Cスレーブ送信モードでは、バイトカウンタを使用しないため、送信時は、SBCビットをクリアする事を推奨します。

SMBusモードでは、スレーブバイト制御モードは送信時にPECバイト(パケットエラーコード)を送信するために使用されます。

## SMBus 2.0 のシームレスな対応

- ARP (アドレス解決プロトコル) : デバイスのデフォルトアドレス、スレーブモードでのアービトリエーション

- ホスト通知プロトコルの対応: ホストアドレス

- アラートの対応: アラートピンおよびアラート応答対応

- タイムアウトおよびバスアイドル検出

- SBCモードにおけるコマンドおよびデータ認識制御

- パケットエラーチェック(PEC)のハードウェア演算

I<sup>2</sup>CペリフェラルはSMBusをハードウェアで対応します。

SMBusのアドレス解決プロトコルはスレーブモードのデバイスのデフォルトアドレスおよびアービトリエーションにより対応可能です。

ホスト通知プロトコルはホストアドレスの対応によって実現可能です。

アラートプロトコルはSMBusアラートピンとアラート応答アドレスにより対応します。

SMBusクロックのロータイムアウトおよびクロックロー累積延長時間をプログラム可能な時間で検出することができます。

バスアイドル条件をプログラム可能な時間で検出することができます。

コマンドおよびデータ認識制御はスレーブバイト制御モードで対応します。

パケットエラーコード(PEC)バイトはハードウェアにより計算されます。

# SMBus: PEC (パケットエラーチェック)

15

- 自動PEC送信/チェック

- NBYTES (データ転送カウンタ)は以下で使用します:

- 受信時、NBYTES-1バイト受信後に、パケットエラーコード(PEC)バイトを自動チェック

- 失敗時の自動NACK送信

- 送信時、NBYTES-1バイト送信後に、パケットエラーコード(PEC)バイトの自動送信

- スレーブバイト制御モード(SBCビット)をスレーブモードにセットし、NBYTESカウンタを有効にする必要があります。

パケットエラーコード(PEC)バイトは送信時、自動で送信され、受信時、自動でチェックされます。

NBYTES値で初期化されるデータ転送カウンタは、受信時、NBYTES-1バイト受信後に自動でPECバイトをチェックするのに使用されます。

受信したPECバイトが計算値と合わない場合、PECバイトの後にNACKが自動で送信されます。

送信時、NBYTES-1バイト後に、内部で計算されたPECバイトは自動で送信されます。

スレーブモードでは、NBYTESカウンタを有効にし、自動PEC受信または送信できるようにするために、スレーブバイト制御モードを有効にする必要があります。

# 割込みおよびDMA

16

| 割込みイベント         | 説明                                                 |

|-----------------|----------------------------------------------------|

| 受信バッファ・ノットエンプティ | 受信バッファが受信データを含み読み出し準備が出来ている場合にセットされます              |

| 送信バッファ割込み状態     | 送信バッファがエンプティで、書き込み準備が出来ている場合にセットされます               |

| ストップ検出          | バス上にストップ条件を検出した場合にセットされます                          |

| 転送完了リロード        | RELOAD=1およびNBYTESバイトのデータが転送された場合にセットされます           |

| 転送完了            | RELOAD=0、AUTOEND=0およびNBYTESバイトのデータが転送された場合にセットされます |

| アドレス一致          | 受信したスレーブアドレスが有効なスレーブアドレスの1つと一致した場合にセットされます         |

| NACK受信          | バイト送信後にNACKを受信した場合にハードウェアによりセットされます                |

- 受信バッファがノットエンプティまたは送信バッファがエンプティの場合、DMA要求を生成することができます

様々なイベントで割込みをトリガできます：

受信バッファノットエンプティフラグは、受信バッファが受信データを含み読み出し準備が出来ている場合にセットされます。

送信バッファ割込み状態は、送信バッファがエンプティで、書き込み準備が出来ている場合にセットされます。

ストップ検出フラグは、バス上にストップ条件を検出した場合にセットされます。

転送完了リロードフラグは、RELOADビットがセットされ、NBYTESバイトのデータが転送された場合にセットされます。

転送完了フラグは、RELOADおよびAUTOENDビットがクリアされ、NBYTESバイトのデータが転送された場合にセットされます。

アドレス一致フラグは、受信したスレーブアドレスが有効なスレーブアドレスの1つと一致した場合にセットされます。

NACK受信フラグは、バイト送信後にNACKを受信した場合にセットされます。

受信バッファノットエンプティフラグ、または、送信エンプティフラグがセットされた場合にDMA要求を生成することができます。

# エラー割込み

17

| 割込みイベント          | 説明                                                                                                |

|------------------|---------------------------------------------------------------------------------------------------|

| バスエラー検出          | 開始およびストップ条件の誤配置を検出した場合にセットされます                                                                    |

| アビトレーション損失       | アビトレーション損失のイベントでセットされます                                                                           |

| オーバーラン／アンダーランエラー | スレーブモードで前のデータの読み出しが完了する前に新しいデータを受信した場合、または、新しいデータが書き込まれていない状態で送信が必要になった場合に、NOSTRETCH=1の状態でセットされます |

| SMBus: PECエラー    | 受信したPECがPECレジスタの内容と一致しない場合にセットされます                                                                |

| SMBus: タイムアウトエラー | タイムアウト、または、延長クロックタイムアウトが発生した場合にセットされます                                                            |

| SMBus: アラートピン検出  | SMBHEN=1(SMBusホスト設定)、ALERTEN=1およびSMBAピンにてSMBALERTイベント(立ち下りエッジ)を検出した場合にセットされます                     |

様々なエラーフラグを生成することができます。

バスエラー検出フラグは、開始およびストップ条件の誤配置を検出した場合にセットされます。

アビトレーション損失フラグは、アビトレーション損失のイベントでセットされます。

オーバーラン/アンダーランエラーフラグは、スレーブモードでクロックストレッチが無効な場合に、オーバーランまたはアンダーランエラーを検出した際にセットされます。

SMBusモードにおいて、PECエラーフラグは、受信したPECが計算されたPECレジスタの内容と一致しない場合にセットされます。

タイムアウトエラーフラグは、タイムアウト、または、延長クロックタイムアウトが検出された場合にセットされます。

アラートピン検出フラグは、SMBusホスト設定時に、アラートが有効でSMBAピンにて立ち下りエッジを検出した場合にセットされます。

# 低電力モード

18

| モード      | Description                                                                                                                                                                     |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RUN      | 有効。                                                                                                                                                                             |

| SLEEP    | 有効。ペリフェラルの割込みによりデバイスをSLEEPモードより復帰。                                                                                                                                              |

| 低電力RUN   | 有効。                                                                                                                                                                             |

| 低電力SLEEP | 有効。ペリフェラルの割込みによりデバイスを低電力SLEEPモードより復帰。                                                                                                                                           |

| STOP1    | アドレス検出は有効。I <sup>2</sup> Cペリフェラルはアドレス一致時に復帰割込みを生成します。                                                                                                                           |

| STOP2    | I <sup>2</sup> C3: アドレス検出は有効。I <sup>2</sup> Cペリフェラルはアドレス一致時に復帰割込みを生成します。<br>I <sup>2</sup> C1, I <sup>2</sup> C2: I <sup>2</sup> Cは無効である必要があります。I <sup>2</sup> Cレジスタの内容は保持されます。 |

| STANDBY  | パワーダウン。STANDBYモードから復帰後、ペリフェラルは再初期化が必要です。                                                                                                                                        |

| SHUTDOWN | パワーダウン。SHUTDOWNモードから復帰後、ペリフェラルは再初期化が必要です。                                                                                                                                       |

RUNモード、低電力RUNモード、SLEEPモード、低電力SLEEPモードでは、I<sup>2</sup>Cペリフェラルは有効です。

I<sup>2</sup>C割込みによりデバイスをSLEEPモードまたは低電力SLEEPモードから復帰します。

STOPモードでは、アドレス検出が有効です。

I<sup>2</sup>Cペリフェラルはアドレス一致のイベントで復帰割込みを生成します。

STANDBYモードおよびSHUTDOWNモードでは、ペリフェラルはパワーダウンの状態となり、STANDBYモードまたはSHUTDOWNモードから復帰後、再初期化が必要となります。

- DBG\_I2Cx\_STOP: コアが停止した際、I2Cx SMBUSのタイムアウトカウンタは停止します。

各I<sup>2</sup>Cペリフェラルにおいて、マイコンのデバッグコンポーネントにデバッグ用にビットが用意されており、コアが停止した際にSMBUSのタイムアウトカウンタを停止することができます。

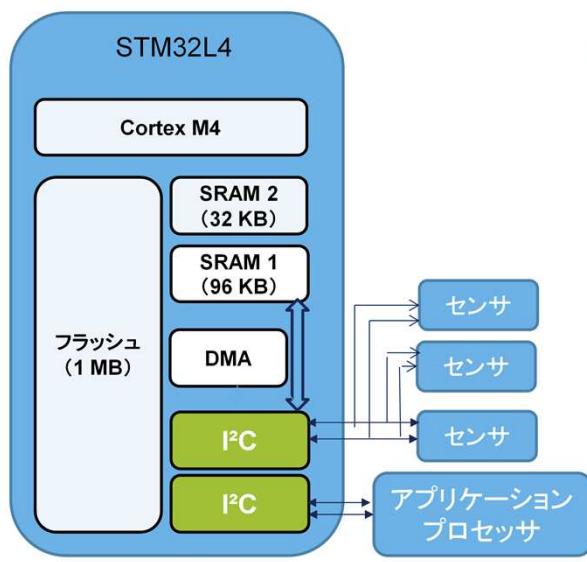

# アプリケーション例

20

## バッチ・アクイジョン・モード(BAM)を使用したセンサーハブ

- I<sup>2</sup>Cマスタが低電力SLEEPモードでセンサと通信

- 必要な通信ペリフェラル+1つのDMA+1つのSRAMのみのクロックが低電力SLEEPモード時に有効になるように設定されます。

- フラッシュメモリはパワーダウンモードに入れ、低電力SLEEPモードでは、フラッシュのクロックはゲーティングにより停止させます。

- I<sup>2</sup>Cクロックは低電力SLEEPモード時でも16MHzで動作可能で、高速モードプラスに必要な1MHzに対応することができるきます。

- I<sup>2</sup>Cスレーブはアプリケーションプロセッサと通信します。

- STM32L4はSTOPモードに入れることができます

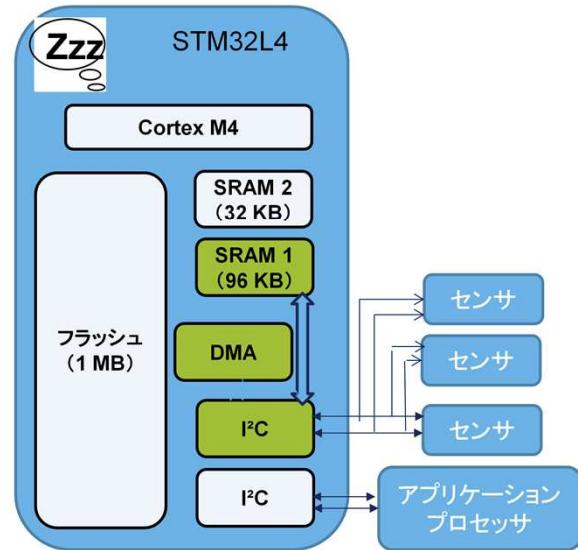

ここで、複数のI<sup>2</sup>Cペリフェラルを必要とするセンサーハブのアプリケーション例を示します。

一つ、または複数のI<sup>2</sup>Cマスタが外部のセンサとのインターフェースに使用されます。

STM32L4デバイスを低電力SLEEPモードに設定し、データ転送中の消費電力を低減することができます。

これを、バッチ・アクイジョン・モードと呼びます。

必要な通信ペリフェラル+1つのDMA+SRAM1またはSRAM2のみを低電力SLEEPモードでクロックが有効になるように設定します。

フラッシュメモリはパワーダウンモードに入れ、低電力SLEEPモードでは、フラッシュのクロックはゲーティングにより停止させます。

I<sup>2</sup>Cクロックは低電力SLEEPモード時でも16MHzで動作可能で、高速モードプラスに必要な1MHzに対応することができるきます。

I<sup>2</sup>Cスレーブはアプリケーションプロセッサとの通信に使用されます。

STM32L4デバイスはSTOPモードに入れ、アプリケーションプロセッサによるアドレスによってのみ復帰させることができます。

# STM32L4の各I<sup>2</sup>Cの機能

21

| I <sup>2</sup> Cの機能                   | I <sup>2</sup> C1 | I <sup>2</sup> C2 | I <sup>2</sup> C3 |

|---------------------------------------|-------------------|-------------------|-------------------|

| 7ビットアドレッシングモード                        | ○                 | ○                 | ○                 |

| 10ビットアドレッシングモード                       | ○                 | ○                 | ○                 |

| 標準モード（最大100kbit/s）                    | ○                 | ○                 | ○                 |

| 高速モード（最大400kbit/s）                    | ○                 | ○                 | ○                 |

| 20mA出力駆動I/O対応<br>高速モードプラス（最大1 Mbit/s） | ○                 | ○                 | ○                 |

| 独立クロック                                | ○                 | ○                 | ○                 |

| SMBus                                 | ○                 | ○                 | ○                 |

| STOP1モードからの復帰                         | ○                 | ○                 | ○                 |

| STOP2モードからの復帰                         |                   |                   | ○                 |

○: 対応

STM32L4デバイスは、これらの機能を持つ3つのI<sup>2</sup>Cペリフェラルを実装しています。

STOP1モードからの復帰は全てのI<sup>2</sup>Cにて対応しています。

STOP2モードからの復帰はI<sup>2</sup>C3のみで対応しています。

詳細は、本ペリフェラルに関するこれらのペリフェラルのトレーニング資料を参照して下さい：

- システム設定コントローラ(SYSCFG)

- リセットおよびクロックコントローラ(RCC)

- 電源制御(PWR)

- 割込み(NVICおよびEXTI)

- ダイレクト・メモリ・アクセス・コントローラ(DMA)

本ペリフェラルに関する詳細情報は、以下のペリフェラルのトレーニング資料をご参照下さい：

- システム設定コントローラ

- リセットおよびクロックコントローラ

- 電源制御

- 割込みコントローラ

- ダイレクト・メモリ・アクセス・コントローラ

詳細に関しては、以下のウェブページをご参照下さい。

- [www.nxp.com](http://www.nxp.com) :

- UM10204 I<sup>2</sup>Cバス仕様およびユーザマニュアル

- [www.sbs-forum.org](http://www.sbs-forum.org)

- システム管理バス（SMBus）仕様

- <http://www.powersig.org/>

- PMBus™ 電力システム管理プロトコル仕様

I<sup>2</sup>Cの詳細に関しては、NXPのウェブサイトより、I<sup>2</sup>Cバスの仕様およびユーザマニュアルをご参照下さい。

SMBus仕様に関しては、スマートバッテリーシステム実装フォーラムをご参照下さい。

PMBus電力システム管理プロトコル仕様に関しては、電力管理バス実装フォーラムをご参照下さい。