# STM32L4 - CRC

巡回冗長検査CRC (Cyclic Redundancy Check)

Revision 1

Dec- 2015

こんにちは。STM32L4の巡回冗長検査CRCペリヘラルのプレゼンテーションへようこそ。

エラー検出コードを生成するために使用されるこのユニットの機能を説明いたします。

- 8、16、32bitデータからCRCコードを得るために使用される

- 完全に構成可能な生成多項式

- プログラム可能なサイズ

- 入出力のデータワードをリバース可能

### アプリケーションの利点

- データの完全性を確認

- ソフトウェアコードサインの生成

- CPUまたはDMAにより容易に使用可能

CRCはCyclic Redundancy Checkの短縮形です。

CRC演算ユニットは、8、16、32bitデータにおいて、コンフィギュレーション可能な生成多項式値とサイズを使ってCRCコードを得るために使用されます。

CRCの基本技術は、データ通信またはストレージの完全性を確認するために用いることが可能です。

CRC演算は、実行期間中にアプリケーションソフトウェアのサインを計算するために使用されます。また、リンク時間に生成された参照サインと比較され、与えられたメモリ内の位置にストアされます

STM32CRCペリヘラルは完全にコンフィギュレーション可能なので、ソフトウェアオーバーヘッドは最小に減らすことができます。

さらに、CPUが他の仕事を実行しているか、またはスリープモードの間、DMAは、データの大きいブロック上のバックツーバックのCRC計算のために使うことができます。

## 鍵となる特徴

3

- 完全プログラム可能な多項式:

- 初期値はCRC-32 (Ethernet) 多項式: 0x04C11DB7

- プログラム可能な多項式のサイズ (7、8、16、32bit)

- プログラム可能な初期値 (デフォルト値 = 0xFFFF\_FFFF)

- 入出力データのいろいろなエンディアン体系

STM32で搭載されているCRCペリフェラルは、7、8、16または32bitのプログラム可能なサイズで、完全にプログラム可能な奇数値多項式を特徴とします。

初期値も、非常に柔軟に実行時にCRCコード生成が可能で、完全にプログラム可能です。

ペリフェラルは、いろいろな通信プロトコルのサポートのために、入出力データのビッグまたはリトルエンディアン・フォーマットをサポートするように構成することができます。

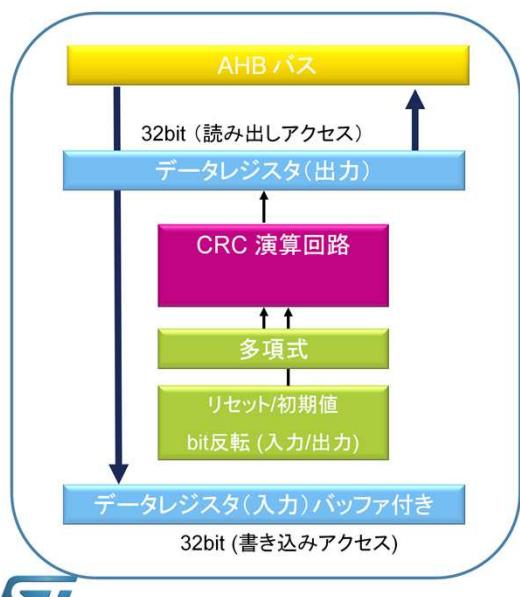

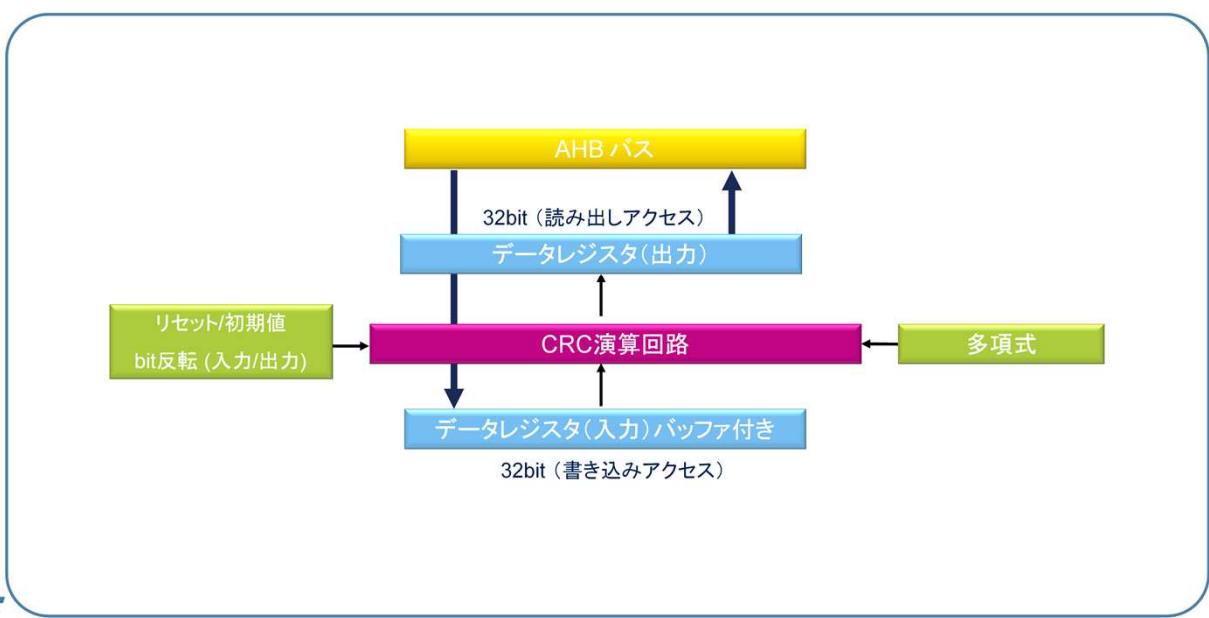

CRC周辺機器は、最適パフォーマンスのためにAHBバス・インターフェースに接続されています。

それには、CPUかDMAによる書き込みと読み出しの両方に使用される一つの32bitレジスタを含みます。

初期値、入出力bit反転と多項式の係数は、新しいCRC値の計算を始める前に、初期化フェーズの間に、ソフトウェアによって構成されます。

CRC演算回路は、次の計算のための初期値になる前のCRC計算の結果を保持します。このように、データブロックの新しいCRC計算を許可します。

# 入力と出力のフォーマット

5

## ソフトウェアのオーバーヘッドを減らす

- 入力データは8、16、32bit単位で入れ替えることが可能。

- 例、入力データ0x1A2B3C4Dに対しCRC演算を適用すると:

- バイト単位で入れ替え: 0x58D43CB2

- ハーフワード単位で入れ替え: 0xD458B23C

- フルワード単位で入れ替え: 0xB23CD458

- 出力データは32bit単位で入れ替えることが可能。

- 出力データの例: 0x11223344:

入出力フォーマットは、ソフトウェアのオーバーヘッドを減らすために、完全に可変です。それにより、アプリケーションで異なるエンティアン仕様を管理することができます。

入力データは、CRC\_CRレジスターのREV\_IN[1:0]bitによって、8bit、16bit、32bit単位で入れ替え、演算することができます。

例えば、入力データ0x1A2B3C4Dに対しCRC演算を適用すると

- バイト単位で入れ替え: 0x58D43CB2

- ハーフワード単位で入れ替え: 0xD458B23C

- フルワード単位で入れ替え: 0xB23CD458

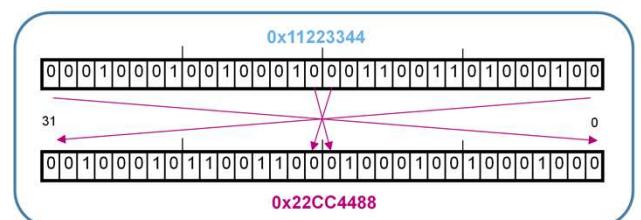

また、出力データも、CRC\_CRレジスターのREV\_OUTbitによって、32bit単位で入れ替えることができます。

操作はbit単位で行われて、例えば入力データ0x11223344は、0x22CC4488に変換されます。

## パフォーマンス

6

- ・単純なファームウェア操作のための1つの入力/出力32bit データレジスタ

- ・入力バッファは、AHBバスをストールさせることなく、連續で書き込み可能

- ・CRCの演算時間は入力データ幅に依存：

- 32bit幅：4 AHB クロックサイクル

- 16bit幅：2 AHB クロックサイクル

- 8bit幅：1 AHB クロックサイクル

- ・CPUがスリープモードのときに、DMAを使って書き込み可能

- 低電力オペレーション(連続的な計算)、そして、時間に厳しいタスクに用にCPUの時間を割くことが可能

CRCデータレジスタは、CRC演算のために発生する数ウェイトステートのための待ち状態が無い2番目のデータを、DMAまたはCPUによって直接書き込める入力バッファを含んでいます。

CRCデータレジスタは、ワード、右揃えハーフワード、右揃えバイトによってアクセスすることができます。

CRCの演算時間は入力データ幅に依存します：

32-bit幅：4 AHB クロックサイクル

16-bit幅：2 AHB クロックサイクル

8-bit幅：1 AHB クロックサイクル

DMAはCRCエンジンに書くために使うことができます。

この為、他のタスクのためにCPUの負荷をなくして、コードまたはデータ保全性を確かめるために、連續の計算のためにDMAは使うことができます。

# 低消費電力モード

7

| モード             | 内 容                                          |

|-----------------|----------------------------------------------|

| Run             | 動作                                           |

| Sleep           | 動作、DMAをCRC演算用に使用可能                           |

| Low-power run   | 動作                                           |

| Low-power sleep | 動作、DMAをCRC演算用に使用可能.                          |

| Stop 1          | 停止。周辺レジスタの内容は保持                              |

| Stop 2          | 停止。周辺レジスタの内容は保持                              |

| Standby         | パワーダウン。CRCペリフェラルは、Standbyモードから退出した後に再初期化が必要  |

| Shutdown        | パワーダウン。CRCペリフェラルは、Shutdownモードから退出した後に再初期化が必要 |

これは、CRCペリフェラルが利用できる電力モードの概要を示します。CRCペリフェラルが動作するために、メインAHBクロックを必要とします。