Quad-SPIメモリ・インターフェース

Revision 1

Dec- 2015

STM32のQuad-SPIメモリ・インターフェースのプレゼンテーションへようこそ。

本プレゼンテーションでは、マイクロコントローラと外部メモリの接続に広く使われているQuad-SPIメモリ・インターフェースの特長について説明します。

# 概要

2

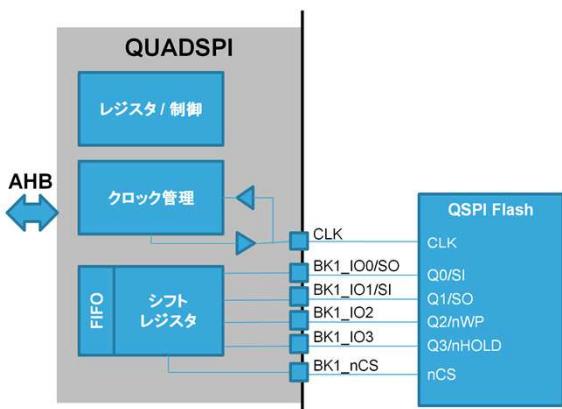

- Quad-SPIメモリ・インターフェースは外部シリアルFlashメモリとの通信インターフェースを提供します

- 自由度の高い設定

- Execute-in-Place (XiP)に対応

- メモリマップ

## アプリケーションの利点

- あらゆるSPI Flashメモリに対応

- 少ないピン数で対応可能

- 既存プロジェクトに容易にメモリ拡張可能

STM32製品に搭載のQuad-SPIメモリ・インターフェースは、マイクロコントローラが外部SPIメモリ、および、Quad-SPIメモリと通信するためのインターフェースを提供します。

本インターフェースは自由度の高い設定が可能で、今日市場に存在するあらゆるシリアルメモリへの接続を容易にします。

アプリケーションは、外部シリアルメモリとの数ピンでの容易な接続を享受できます。

メモリマップ機能により、より多くのメモリ空間が必要になった際、既存プロジェクトに容易に外部メモリを適応させることができます。

- 3つの動作モード

- インダイレクト

- ステータス・ポーリング

- メモリ・マップ

- 最高48MHzの最適化された動作

- シングル・データ・レート(SDR)モード対応

- デュアル・データ・レート(DDR)モード対応

STM32製品に搭載のQuad-SPIメモリインタフェースは、3つの動作モードを提供し、シングル、および、デュアル・データ・レート動作に対応した外部メモリとの通信に最適化されています。

The Quad-SPI memory interface integrated inside STM32 products offers three operating modes and is optimized for communication with external memories with support for single- and dual-data rate operation.

## 柔軟な動作モードによりCPU負荷を低減

- ・ インダイレクト・モード

- ・ 全ての動作はレジスタを通じて実施されます（従来のSPI）

- ・ ステータス・ポーリング・モード

- ・ Flashメモリ・ステータス・レジスタの自動周期的読み出し、および、マッチ時の割り込み生成

- ・ メモリ・マップ・モード

- ・ 外部Flashメモリを内部メモリのように読み出し可能

Quad-SPIメモリ・インターフェースは3つのモードで動作します：

1. インダイレクト・モードでは、従来のSPIインターフェースとして動作し、全ての動作はレジスタを通じて実施されます

2. ステータス・ポーリング・モードでは、Flash・ステータス・レジスタが周期的に読み出され割り込みを生成します

3. メモリ・マップ・モードでは、外部Flashメモリを内部メモリのように読み出し可能です

# フレーム・フォーマット

5

## あらゆるシングル／デュアル／クワッド SPI シリアルFlashメモリと互換

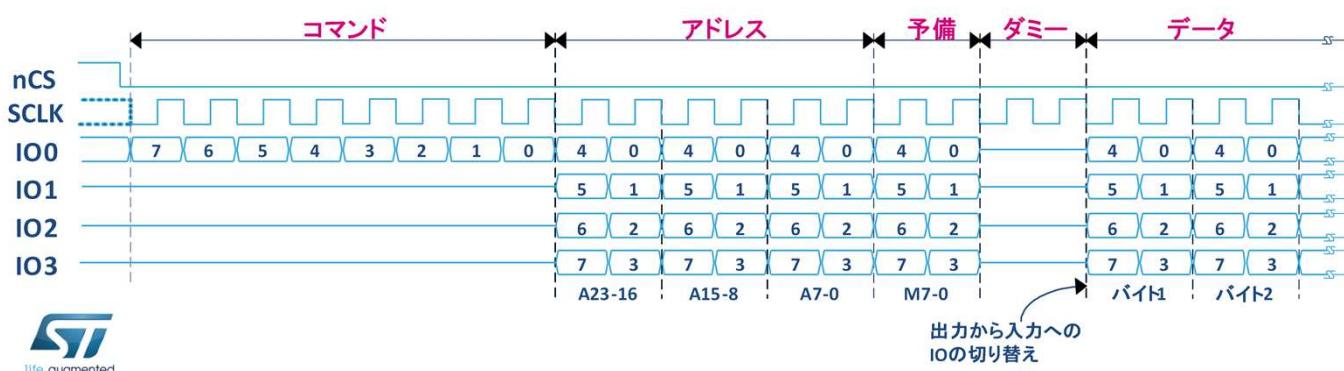

- QSPI のコマンドは最大 5つの 設定可能なフェーズで構成されています

- 各フェーズは有効化または無効化可能

- 各フェースの長さを設定可能

- 各フェースのライン数を設定可能

Quad-SPIメモリインタフェースは、フレームフォーマットの設定に関して高い柔軟性を提供します。

この柔軟性により、あらゆるシリアルFlashメモリへのアドレスが可能になります。

ユーザは、5つの各フェーズを有効化または無効化可能で、各フェースの長さおよび各フェーズで使用されるライン数を設定できます。

# インダイレクト動作モード

6

## 従来のSPIインターフェース

- 従来の通信IPと同じ使い方

- データレジスタの書き込み、または、読み出しによりデータは転送されます

- データ長レジスタにてバイト数を指定します

- データFIFOの管理

- 割り込みフラグ（転送完了フラグ）

- DMA対応

- コマンドの開始

- 命令が必要な場合に命令を書き込んだ時

- 命令およびアドレスが必要な場合にアドレスを書き込んだ時

- データフェーズが必要な場合にデータを書き込んだ時

Quad-SPIメモリインターフェースをインダイレクト動作モードで使用すると、従来のSPIインターフェースのように動作します。

転送データはデータレジスタとFIFOを通ります。

データのやり取りはソフトまたはDMAで行なわれ、その際、Quad-SPIステータスレジスタの割り込みフラグを使用します。各コマンドは、命令コンテキストに応じて、命令、アドレス、または、データを書き込むと開始します。

# ステータス・ポーリング・モード

7

## ソフトウェアのオーバーヘッドを低減

- ステータス・レジスタをポーリングするための特別なモード

- プログラム可能なレジスタ長: 8/16/24/32bit

- 指定したレートで繰り返し読み出し動作

- 応答をマスクし、マッチした場合は割り込みを生成

- プログラム可能なマスク (PSMCR レジスタ)

- マスクされた値はマッチレジスタ(PSMAR)とbit単位で比較されます

- 比較結果の論理積(AND)または論理和(OR)をとることが可能

- マッチを検出すると割り込みが生成されます(マッチ時停止フラグ)

- マッチを検出すると自動的に停止

Quad-SPIインターフェースには、外部Flashメモリのステータスレジスタを自動的にポーリングする特別なモードが搭載されています。

Quad-SPIインターフェースは、また、周期的に外部Flashメモリ内のレジスタを読み出すように設定可能です。

評価対象のbitを選択するために応答データをマスクすることができます。

選択されたbitは、マッチレジスタに格納された要求値と比較されます。

比較結果は、2通りの方法で取り扱われます。

1つは論理積(AND)モードで、全ての選択bitがマッチした場合に割り込みを生成します。

もう1つは論理和(OR)モードで、いずれかの選択bitがマッチした場合に割り込みを生成します。

マッチが発生すると、Quad-SPIインターフェースは自動的に停止します。

# メモリ・マップ・モード

8

- プロジェクトへの容易なメモリ拡張

- 低電力管理

- XiPのためのプリフェッチ

- 外部Flashメモリをウェイとステートを加味して内部メモリのように参照

- 読み出し動作はAHBアクセスにより自動的に発生します

- インダイレクトモードのようにフレームおよびオペコードはIP設定時に定義されます

- 必要に応じて、Quad-SPIバスをストールし、連続読み出しを再開するために、nCSピンはローになり、クロックは停止します

- 低電力のためにnCSピンをハイにリリースするためのタイムアウト・カウンタ

Quad-SPIメモリインターフェースには、メモリ・マップモードというモードがあります。

本モードによるアプリケーションでの主な利点は、内部または外部接続メモリ間でウェイトステート数は異なりますが、読み出しアクセス方法が同じ為、

外部メモリ拡張が容易な点です。

本モードは、読み出し動作時にのみ適しており、低速な外部メモリに対応するためにウェイトステートを含めた上で、外部Flashメモリは内部メモリのように参照することができます。

本モードで対応できるサイズは最大で256Mバイトとなります。プリフェッチバッファはExecution-in-Placeに対応している為、コードを内部RAMへダウンロードしなくとも外部メモリより直接実行できます。

本モードは、また、あるFlashメモリで対応しているSIOO(命令1回のみ送信)モードにも対応しており、コントローラは命令を1回のみ送信し、

後続アクセスの命令フェーズを省略することができます。

# 遅延データのサンプリング

9

- PCBのレイアウトによって信号が遅延した場合に便利です

- サンプリングクロックを1/2クロック・サイクル分シフトすることができます

- SDRモードでのみ対応

- 出力データは1/2システムクロック・サイクル分シフトすることができます

- DDRモードでのみ対応

遅延データのサンプリングにより、PCBレイアウトの最適化の制約による信号の遅延を補正することができます。これにより、アプリケーションにてSDRモード時にデータサンプリング時間を1/2クロックサイクル分シフトすることができます。DDRモードでは、出力データを1/2システムクロックサイクル分シフトすることで、ホールド時間の制限を緩和することができます。

# 割り込みとDMA

10

| 割り込みイベント  | 説明                                                            |

|-----------|---------------------------------------------------------------|

| タイムアウト    | タイムアウトが発生した場合にセットされます。                                        |

| ステータス・マッチ | 自動ポーリングモードで、マスクされた受信データがマッチレジスタの該当bitとマッチした場合にセットされます。        |

| FIFO 閾値   | インダイレクトモードで、FIFOの閾値に達した場合にセットされます。                            |

| 転送完了      | インダイレクトモードでプログラムされたデータ数の転送が完了するか、いずれかのモードで転送が中止された場合にセットされます。 |

| 転送エラー     | インダイレクトモードで、無効なアドレスへアクセスした場合にセットされます。                         |

- DMA要求は、インダイレクトモードでFIFOの閾値に達した場合に生成されます。

Quad-SPI メモリインタフェースは5つの割り込みソースがあります。タイムアウト、自動ポーリングモードでマスクされた受信データがマッチレジスタの該当bitとマッチした場合のステータス・マッチ、FIFO閾値、転送完了および転送エラーです。DMA要求は、インダイレクトモードでFIFOの閾値に達した場合に生成されます。

# 低電力モード

11

| モード      | 説明                                        |

|----------|-------------------------------------------|

| RUN      | 有効。                                       |

| SLEEP    | 有効。ペリフェラルの割り込みによりデバイスをSLEEPモードより復帰。       |

| 低電力RUN   | 有効。                                       |

| 低電力SLEEP | 有効。ペリフェラルの割り込みによりデバイスを低電力SLEEPモードより復帰。    |

| STOP1    | 停止。ペリフェラルレジスタの内容は保持されます。                  |

| STOP2    | 停止。ペリフェラルレジスタの内容は保持されます。                  |

| STANDBY  | パワーダウン。STANDBYモードから復帰後、ペリフェラルは再初期化が必要です。  |

| SHUTDOWN | パワーダウン。SHUTDOWNモードから復帰後、ペリフェラルは再初期化が必要です。 |

Quad-SPI メモリインターフェースは、RUN、SLEEP、低電力RUN、低電力SLEEPモード時に有効です。

Quad-SPI割り込みにより、デバイスをSLEEP、または、低電力SLEEPモードより復帰できます。

STOP1またはSTOP2モードでは、Quad-SPIは停止しますが、そのレジスタの内容は保持されます。

STANDBYまたはSHUTDOWNモードでは、Quad-SPIはパワーダウンの状態となり、復帰後に再初期化が必要になります。

# パフォーマンスと消費電流

12

- データフェッチのパフォーマンス比較

- 10KBのテーブルを外部のQuad-SPI Flash、内蔵Flash、内蔵SRAMから読み出す

- 内蔵Flashメモリからのコード実行

| 条件                                              | 外部QSPI        | 内蔵Flash | 内蔵SRAM |

|-------------------------------------------------|---------------|---------|--------|

| CPU @ 80 MHz – QSPI SDR 4 lanes @ 40 MHz        | 257 µs        | 152 µs  | 88 µs  |

| <b>CPU @ 48 MHz – QSPI DDR 4 lanes @ 48 MHz</b> | <b>214 µs</b> | 227 µs  | 147 µs |

外部 Quad-SPI: マイクロン社製 N25Q256A13EF840E / XiP モード - 内蔵 Flash: ART 有効 - コンパイラー: IAR v7.30.1.7746

- 本ベンチマークにおけるSTM32L4の消費電流(外部Flashメモリを除く)

| 条件                                              | 外部QSPI         | 内蔵Flash  | 内蔵SRAM   |

|-------------------------------------------------|----------------|----------|----------|

| CPU @ 80 MHz – QSPI SDR 4 lanes @ 40 MHz        | 21 mA          | 12.74 mA | 14.11 mA |

| <b>CPU @ 48 MHz – QSPI DDR 4 lanes @ 48 MHz</b> | <b>14.6 mA</b> | 8.79 mA  | 8.64 mA  |

外部 Quad-SPI: マイクロン社製 N25Q256A13EF840E / XiP モード - 内蔵 Flash: ART 有効 - コンパイラー: IAR v7.30.1.7746

外部Flashの消費電流はQuad-SPIFlashデバイスに依存します。

我々の測定では 約 4.7 mA @ 80 MHz/SDR、約 6.1 mA @ 48 MHz/DDR (データ読み出しのベンチマーク、選択したデバイスにおいて)

Quad-SPIメモリインタフェースのパフォーマンスを測定するために、10KBのテーブルを、Quad-SPIFlashメモリ、内蔵Flashメモリ、および、内蔵SRAMから読み出す簡単なベンチマークを使用しています。

コードは内蔵Flashメモリより実行しています。

シングル・データレート・モード(80MHz動作時)では、内蔵Flashメモリは外部Quad-SPIFlashメモリより40%速い結果となっています。

しかし、ダブル・データレート・モード(48MHz動作時)では、Quad-SPIはプリフェッチ機能のおかげで内蔵Flashメモリよりも若干速い結果となっています。

STM32L4の消費電流は、Quad-SPIFlashメモリを使用した場合の方がI/Oをトグルする影響で高くなります。

## エネルギー

13

- データ・フェッチのベンチマークの実行時間と消費電流を組み合わせることで、必要なエネルギー量を定義することができます

| 条件                                            | 外部QSPI<br>(STM32のみ) | 外部QSPI<br>(外部Flash含む) | 内蔵<br>Flash | 内蔵<br>SRAM |

|-----------------------------------------------|---------------------|-----------------------|-------------|------------|

| CPU @ 80 MHz—QSPI SDR 4 lanes @ 40 MHz        | 17.81 µJ            | 21.80 µJ              | 6.38 µJ     | 4.10 µJ    |

| <b>CPU @ 48 MHz—QSPI DDR 4 lanes @ 48 MHz</b> | <b>10.31 µJ</b>     | 14.62 µJ              | 6.58 µJ     | 4.19 µJ    |

外部 Quad-SPI: マイクロン社製 N25Q256A13EF840E / XiP モード - 内蔵 Flash: ART 有効 - コンパイラ: IAR v7.30.1.7746

外部Flashの消費電流はQuad-SPIFlashデバイスに依存します。

我々の測定では 約 4.7 mA @ 80 MHz/SDR、約 6.1 mA @ 48 MHz/DDR (データ読み出しのベンチマーク、選択したデバイスにおいて)

ベンチマークの実行時間と消費電流を組み合わせることで、エネルギー量の全体像を得ることができます。

与えられたタスクのエネルギー消費の点で、DDRモードが最も最適化されたモードということができます。

# Coremarkのスコア

14

- 実行の比較

- Quad-SPIインターフェースはデータ転送に最適化されていますが、外部Quad-SPI Flashメモリからコードを実行することも可能です

| 条件                                       | 外部QSPI       |

|------------------------------------------|--------------|

| CPU @ 80 MHz – QSPI SDR 4 lanes @ 40 MHz | 0.469 CM/MHz |

| CPU @ 48 MHz – QSPI DDR 4 lanes @ 48 MHz | 0.754 CM/MHz |

外部 Quad-SPI: マイクロン社製 N25Q256A13EF840E / XIP モード - 内蔵 Flash: ART 有効 - コンパイラー: IAR v7.30.1.7746

- 消費電流は同じ条件下ではデータフェッチのベンチマークと同等です。

Quad-SPIインターフェースはデータ転送に最適化されていますが、外部Quad-SPI Flashメモリからコードを実行することも可能です

CoreMarkの結果はDDRモードを使用した方がよりよい結果となります。

消費電流は同じ条件下ではデータフェッチのベンチマークと同等です。

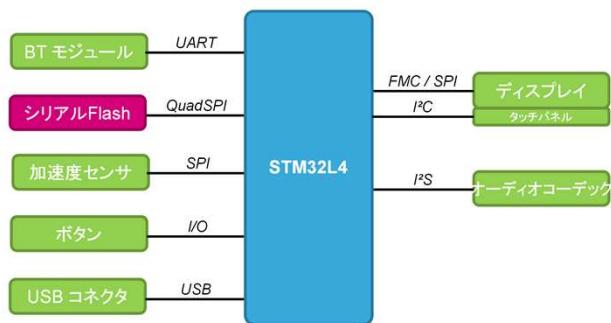

# アプリケーション例

15

- ・コネクティビティとユーザ・インターフェースを含むウェアラブルアプリケーション:

- ・外部Quad-SPIは、ユーザ・インターフェースで必要となるグラフィック(アイコン、フォント等)やオーディオデータを格納しておくことができます

ウェアラブルアプリケーションでは低電力管理機能に加え高品質のユーザインターフェースが要求されます。

これらの要件は、STM32L4のQuad-SPIインターフェースを使って外部Flashメモリに全ての背景画像、高解像度アイコン、または、多言語対応のフォントなどのグラフィックコンテンツを格納しておくことで対応することができます。

さらに、着信音のオーディオデータを外部Flashメモリで提供される広い空間に保存しておくことができます。

このようなデバイスの駆動に少ピン数で対応でき、高効率のシステム実装が実現できます。

- 本ペリフェラルに関する以下のペリフェラルのトレーニング資料も合わせてご参照下さい:

- RCC (Quad-SPIクロック制御、Quad-SPI 有効化／リセット)

- 割り込み (Quad-SPI割り込みマッピング)

- DMA (Quad-SPIデータ転送)

- 汎用入出力 (Quad-SPI入力／出力ピン)

RCC、割り込み、DMA、および、汎用入出力のペリフェラルトレーニングスライドも合わせてご参照下さい。