# STM32L4 - DEBUG

デバッグ・インターフェース

Revision 1

Dec- 2015

STM32のデバッグ・インターフェースのプレゼンテーションへようこそ。

本プレゼンテーションでは、STM32L4デバイスが提供するデバッグ機能について説明します。

# 概要

2

- STM32L4はオンチップのデバッグ機能を提供します

- MCUのプログラミング

- アプリケーションのデバッグ

- コードの分析

## アプリケーションの利点

- 基本デバッグ機能

- 高度な機能(組み込みトレースマクロセル) 異常なコードを素早く特定

- カバレッジおよびプロファイリング機能

STM32製品のデバッグ・インターフェースはMCUの内部リソースへのアクセスを可能にします。

このインターフェースはMCUのプログラム、および、基本的なデバッグ機能を使用したアプリケーションのデバッグに使われます。

基本的なデバッグ機能に加え、アプリケーションの異常な箇所を素早く特定する為に使われるトレース機能や、アプリケーションのテスト、最適化、および、認証で使用されるカバレッジおよびプロファイリングのレポート生成などの利点を享受できます。

# 主な特長

3

## • 基本デバッグ機能

- JTAG、および、シリアル・ワイヤ・デバッグポート

- 柔軟なピン配置

- AHBアクセスポートを介したデバイスのメモリへのプログラミング

- メモリ & ペリフェラルへのアクセス

- 実行制御 —ブレークポイント、ステップ実行

- ペリフェラルの固定

## • 全てのデバッグツールで対応

STM32L4は、全てのハードウェアおよびソフトウェアのデバッグツールで対応する、様々な基本デバッグ機能を提供します。

デバッグのハードウェアは5線の標準JTAGインターフェース、または、2線のシリアル・ワイヤ・デバッグポートを介してSTM32L4とインターフェースします。

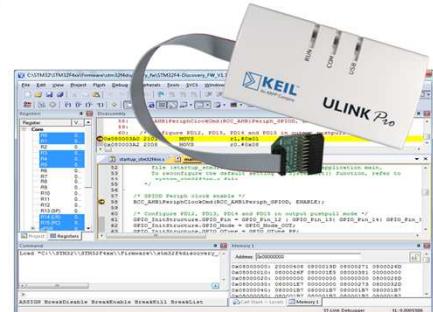

デバッグのツールセットは、AHBアクセスポートへ直接アクセスが可能で、AHBマスタは全ての内部データバスへのアクセス、全てのレジスタおよびメモリへの直接読み出しや書き込み、フラッシュメモリへのプログラミングが可能です。

ユーザは、ブレークポイント、および、コードのステップ実行を使用してアプリケーションの実行を制御できます。

プログラムがブレークポイントに達した場合、タイマなどの内部ペリフェラルは、その時のステートで停止するか、動作を続けることができます。

## • 高度なデバッグ機能

- 特別に対応したデバッグツールやターゲットデバイスが必要です

- データ・ウォッチポイント・トリガ

- 命令トレース・マクロセル

- フラッシュパッチ・ブレークポイント

- トレースポイント・ユニット・インターフェース \*

- 組み込みトレースマクロセル \*

- バウンダリスキャン(JTAGのみ対応)

\* これらの機能は、該当ピンを実装する大型パッケージでのみ対応しています

STM32L4は、より高度なデバッグ機能にも対応しています。これらの機能を使用するためには、デバッグ用のツールセットがその機能に対応している必要があります。また、ハードウェア、および、ソフトウェアのツールに加え、MCU側も、組み込みトレースマクロセル(ETM)やトレースポイント・ユニット(TPUI)に必要な追加ピンが備わっているなど、機能に対応している必要があります。

# フラッシュパッチとブレークポイントユニット

5

## ハードウェアブレークポイントの実装とソフトウェアバグの修正機能

- 複数のハードウェアブレークポイントを実装

- コード領域のコードおよびデータをシステム領域にパッチ

- コードメモリ領域のソフトウェアバグの修正が可能

- ハードウェアブレークポイントとソフトウェアパッチは排他的に使用可能

- 完全な実装オプション

- 2つのリテラルコンパレータ

- 6つの命令コンパレータ

フラッシュパッチとブレークポイントユニットは、アプリケーションのデバッグ用のハードウェアブレークポイント、または、コードメモリ領域におけるソフトウェアバグの修正を可能にします。

完全な実装オプションとして、2つのリテラルコンパレータと6つの命令コンパレータを提供します。

# データ・ウォッチポイント・トリガ

データトレースとシステムのプロファイリングに対応

6

- 全オプションの実装により、4つの設定可能なコンパレータを搭載

- ハードウェア・ウォッチポイント

- ETMへのトリガ

- PCサンプラ

- データ・アドレス・サンプラ

- アプリケーション・プロファイリングに対応

- カウンタは以下の情報をカウントします

- クロック・サイクル

- フォールドされた命令

- ロード・ストア命令

- スリープ・サイクル

- 命令あたりのクロック

- 割り込みオーバヘッド

実装されたデータ・ウォッチポイント・トリガはハードウェア・ウォッチポイント、ETMトリガ、PCサンプラ、または、データアドレスサンプラに設定可能な4つのコンパレータを提供します。本機能は、クロック・サイクル、ロード・ストア命令スリープ・サイクル、命令あたりのクロック、および割り込みオーバヘッドの数をカウントするカウンタを搭載しており、データトレースおよびシステムプロファイリング分析に必要な情報を提供します。

また、アプリケーション・プロファイルのレポートを生成する事も可能です。

## 計装トレース・マクロセル

7

診断用にprintf形式でのデバッグ情報の取得が可能

- トレース情報は様々なトリガにより生成可能

- ITMへの直接書き込みによるソフトウェアトレース

- DWTによるトリガに基くハードウェアトレース

- パケットに付随するタイムスタンプ

- 21bitのタイムスタンプ・カウンタ

計装トレース・マクロセル(ITM)は、診断用にprintf形式でのデバッグ情報の取得を可能にします。

パケットは、ソフトウェアではITMへ直接書き込むことによって、または、ハードウェアではデータ・ウォッチポイント・トリガ(DWT)によるトリガによって生成可能です。また、21bitカウンタによりタイムスタンプを生成することも可能です。

# エンベデッド・トレース・マクロセル

8

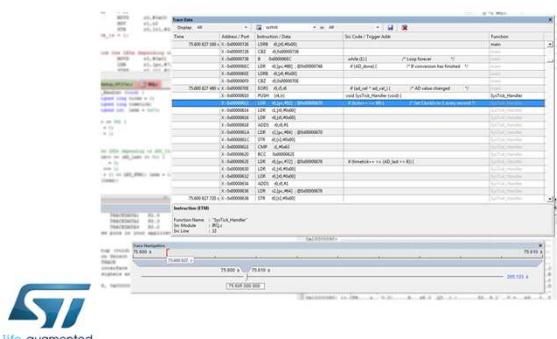

プログラム実行フローの再構成が可能

- DWTまたはITMIによりデータ・トレースが可能

- ETMにより命令トレースが可能

- トレースデータはデバッグツールに保存されるか、PCに送信されます

## アプリケーションの利点

- プログラムフローの再構成により、ファームウェアの異常を素早く特定

- テストおよび認証向けにコードカバレッジおよびプロファイリングのレポートを生成

エンベデッド・トレース・マクロセル(ETM)は、DWTまたはITMIによりデータを、ETMにより命令をトレースすることにより、アプリケーションの実行フローに関する情報を提供します。その後、この情報は、処理の為にデバッガのホストへ送信されます。

この情報により、デバッガは完全に実行フローを再構成することができるようになります。

バグを素早く特定したり、テストおよび認証向けにコードカバレッジおよびプロファイリングのレポートを生成するのに大変便利です。

# トレース・ポート・インターフェース・ユニット

9

オンチップ・トレース・データをフォーマットしITMおよびETMから送信します

- 非同期モード

- 1本の追加ピンが必要

- シリアル・ワイヤ・デバッグ・ポート・モードのみ対応

- 同期モード

- トレースポート幅に応じて2から6本の追加ピンが必要

- より高いデータのスループットが得られます

- リセット後、ピンはトレース用に割り当てられていません

- デバッガのホストでピン設定を行なう必要があります

トレース・ポート・インターフェース・ユニットは、オンチップ・トレース・ユニット、すなわち、ITMおよび、ETMからの情報をフォーマットし、デバッガのホストへ送信します。

本ユニットは、シリアル・ワイヤモードにおいて、1本のピンを通信に使用することで非同期モードに対応します。

また、JTAGおよびシリアル・ワイヤモードにおいて、最大5本のピンを使用することで、同期モードに対応します。

同期モードでは、より高いスループットが得られます。

デバイスのリセット後、これらのピンはトレース用に割り当てられていないため、デバッガのホストがピン設定を行なう必要があります。

## 柔軟なSWJ-DPピン配置

10

### 未使用デバッグピンはアプリケーションで汎用IOとして使用可能

- リセット後、全てのシリアル・ワイヤ JTAGデバッグポート(SWJ-DP)ピンはデバッグ・インターフェースに割り当てられています

- トレース出力は含みません

- デバッグピンはリセット後、内蔵プルアップ/プルダウン抵抗に接続されます

- 幾つかのピンはアプリケーションにより汎用IO機能用に開放することができます

- 代替機能レジスタの再設定が必要

| 利用可能なデバッグポート        | PA13 | PA14 | PA15 | PB3 | PB4 |

|---------------------|------|------|------|-----|-----|

| 全SWJ                | X    | X    | X    | X   | X   |

| 全SWJ(NRSTを除く)       | X    | X    | X    | X   |     |

| JTAG-DP 無効、SW-DP 有効 | X    | X    |      |     |     |

| JTAG-DP 無効、SW-DP 無効 |      |      |      |     |     |

STM32L4は柔軟なデバッグピン配置に対応しています。

リセット後、5本の全てのデバッグピンはデバッグ・インターフェースに割り当てられています。

アプリケーションにより、これらのピンは汎用IOに再設定し、

アプリケーション用にこれらのピンを開放することができます。

また、リセット後、これらのピンが、制御不能なIOレベルを防ぐ為に、内部プルアップ/プルダウン抵抗が有効になっている

点にご注意下さい。

# 低消費電力モード

11

| モード      | I/Oの説明                                    |

|----------|-------------------------------------------|

| RUN      | 有効。                                       |

| SLEEP    | 有効。あらかじめ、デバッガでDBG_SLEEPをセットしておく必要があります。   |

| 低電力RUN   | 有効。                                       |

| 低電力SLEEP | 有効。あらかじめ、デバッガでDBG_SLEEPをセットしておく必要があります。   |

| STOP 1   | 有効。あらかじめ、デバッガでDBG_STOPをセットしておく必要があります。    |

| STOP 2   | 有効。あらかじめ、デバッガでDBG_STOPをセットしておく必要があります。    |

| STANDBY  | 有効。あらかじめ、デバッガでDBG_STANDBYをセットしておく必要があります。 |

デバッグ・インターフェースは低消費電力モードで動作します。

SLEEP、STOP、および、STANDBYモードでは、

DBGMCU\_CRLレジスタの該当するbitを設定することで、低

消費電力モードに入った際にクロックとレギュレータの停止を

回避します。

- 詳細は以下の資料をご参照下さい

- Cortex®-M4 r0p1 テクニカル・リファレンス・マニュアル

- <http://infocenter.arm.com> にて “Cortex®-M4 technical reference manual” を検索

- ARM® デバッグ・インターフェース

- ARM® CoreSight design kit, リビジョン r0p1 – テクニカル・リファレンス・マニュアル

詳細情報に関しては、[infocenter.arm.com](http://infocenter.arm.com)のウェブサイトをご参照下さい。