# STM32L4 – RCC

リセットとクロック制御

Revision 1

- STM32L4のリセットとクロック制御はシステムとペリフェラルのクロックを管理

- 3つの内部発信器

- 2つの外部発信器 (水晶かセラミック振動子)

- 3つのPLL

- 多数のペリフェラルが独立したクロックを持つ

- RCC は色々なシステムとペリフェラルリセットを管理

## アプリケーションの利点

- クロックソースの選択における高い柔軟性は、消費電力と精度の要件を満たすことができる。

- 多くの独立したペリフェラルクロックが通信のボーレートに影響を与えずに消費電力を調整することができ、いくつかのペリフェラルでは低消費電力モードでアクティブを維持する。

- 安全で柔軟なリセット管理

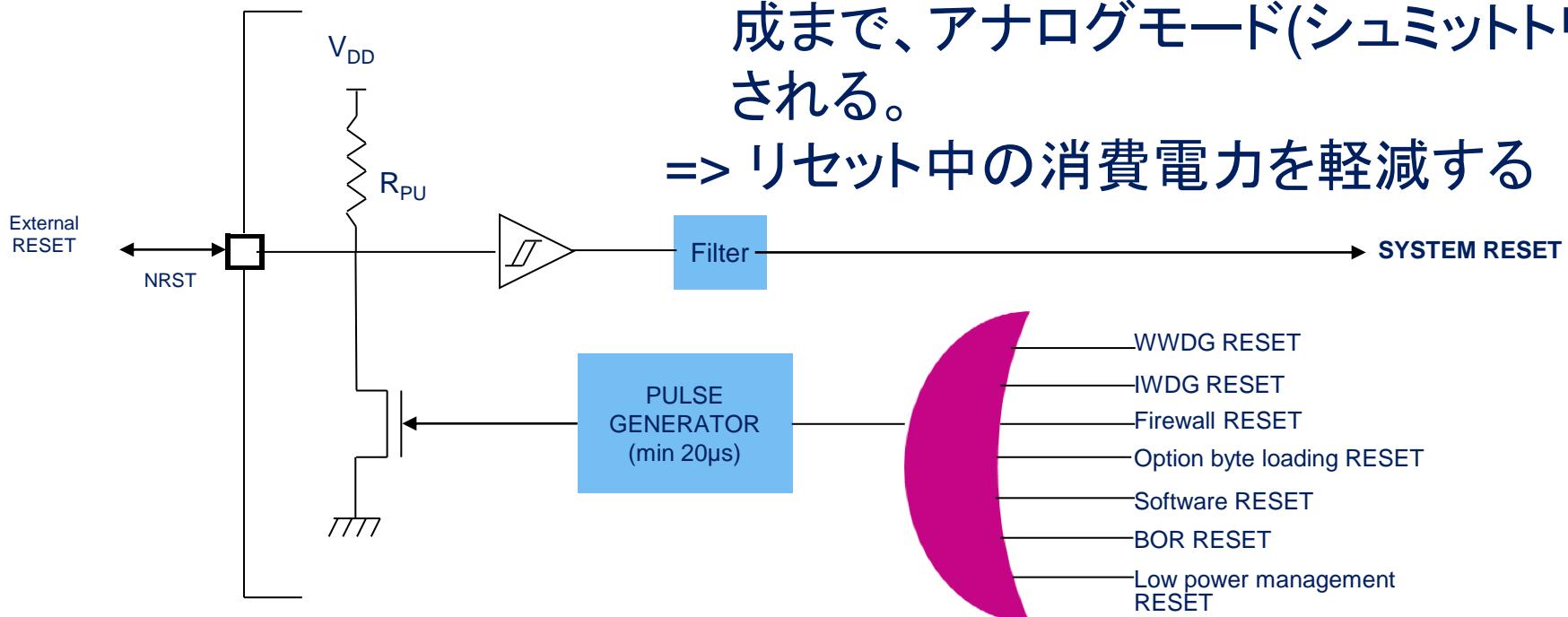

## 外部回路なしで、安全かつ柔軟なリセット管理

- 3つのタイプのリセットを管理:

- システムリセット

- パワーリセット

- バックアップドメインリセット

- ペリフェラルは独立したリセット制御ビットを持つ

## ・システムリセット

- RCCレジスタ、PWRレジスタ、バックアップドメインを除いた、全てのレジスタのリセット

- リセット要因

- NRST ピンが L (外部リセット)

- WWDG イベント

- IWDG イベント

- Firewall イベント

- ソフトウェアリセット (NVIC経由)

- 低消費電力モードでのセキュリティリセット

- オプションバイトロードリセット

- BOR

- RCC\_CSRレジスタにリセット要因のフラグがある

# リセット要因

5

外付け部品は、内部フィルタと電力監視によって、必要ではない

システムリセット要因は、外部コンポーネントをリセットすることが可能

- リセットプルアップは、内部リセット時に無効化

- I/Oは、リセットおよびリセット後ソフトウェアの再構成まで、アナログモード(シミュットリガ無し)で設定される。

- => リセット中の消費電力を軽減する

- パワーリセット

- 要因

- ブラウンアウトリセット(BOR) => バックアップドメインを除く全てのレジスタをリセット

- Standbyから復帰の時 =>  $V_{CORE}$  ドメインの全てのレジスタをリセット

$V_{CORE}$  ドメイン外のレジスタ (RTC, WKUP, IWDG, Standby/Shutdown モード制御)には影響なし

- Shutdownから復帰の時にBORを発生させる.

- バックアップドメインリセット

- RTC レジスタ、バックアップレジスタ、RCC BDCR レジスタのバックアップドメインのリセット

- 要因

- RCC BDCRレジスタのBDRST ビット

- 両方の電源がoffの場合から、VDD または VBAT 電源ON時

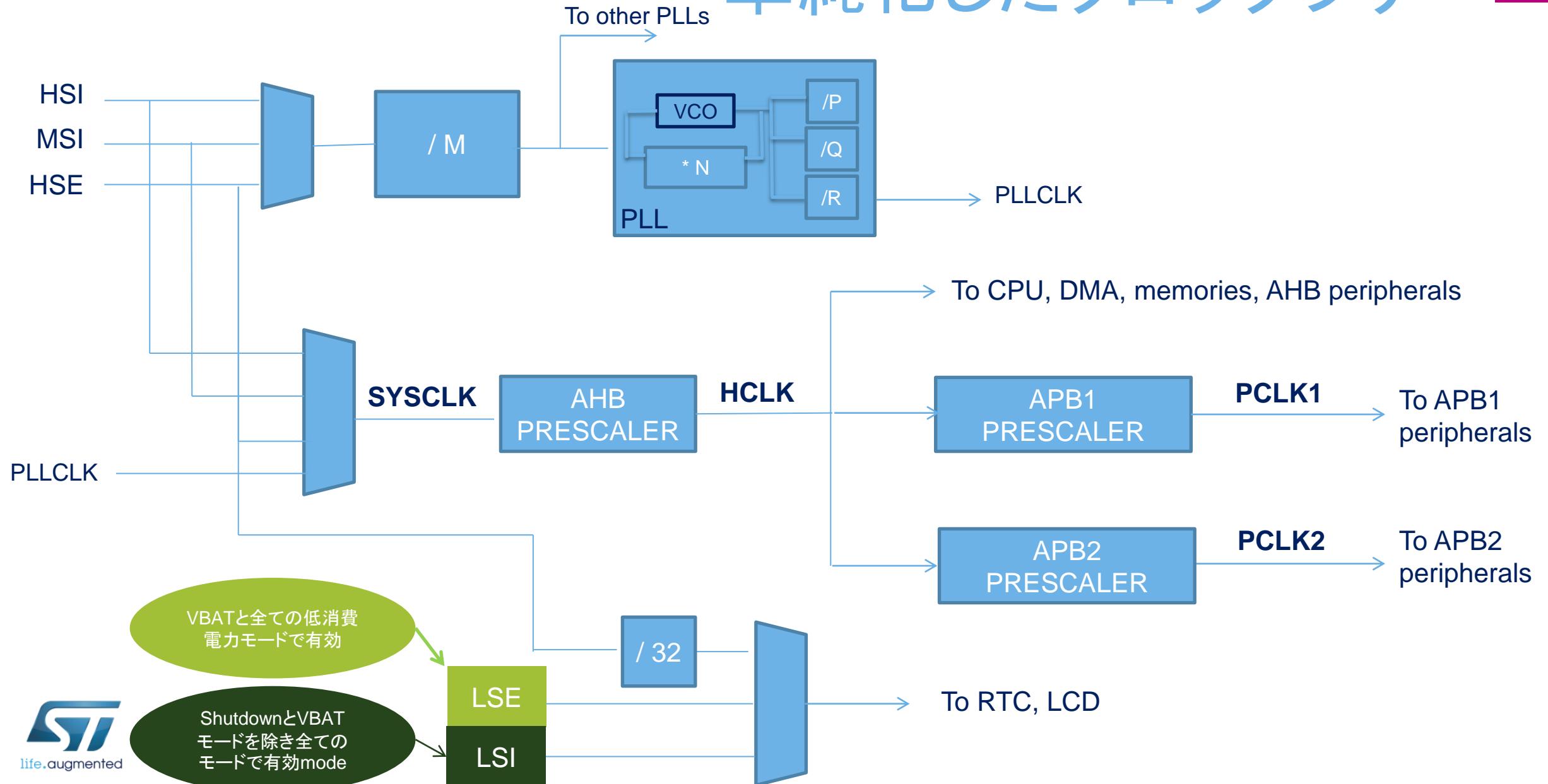

## 低消費電力、精度、およびパフォーマンスのためのクロック・ソースの選択

- 3つの内部クロック Three internal clock sources

- High-speed 内部 16 MHz RC 発信器 (HSI)

- Multi-speed 内部 RC 発信器 (MSI)

- Low-speed 内部 32 kHz RC 発信器 (LSI)

- 2つの外部発信器

- High-speed 外部 4 to 48 MHz 発信器 (HSE) クロックセキュリティシステム付き

- Low-speed 外部 32.768 kHz 発信器 (LSE) クロックセキュリティシステム付き

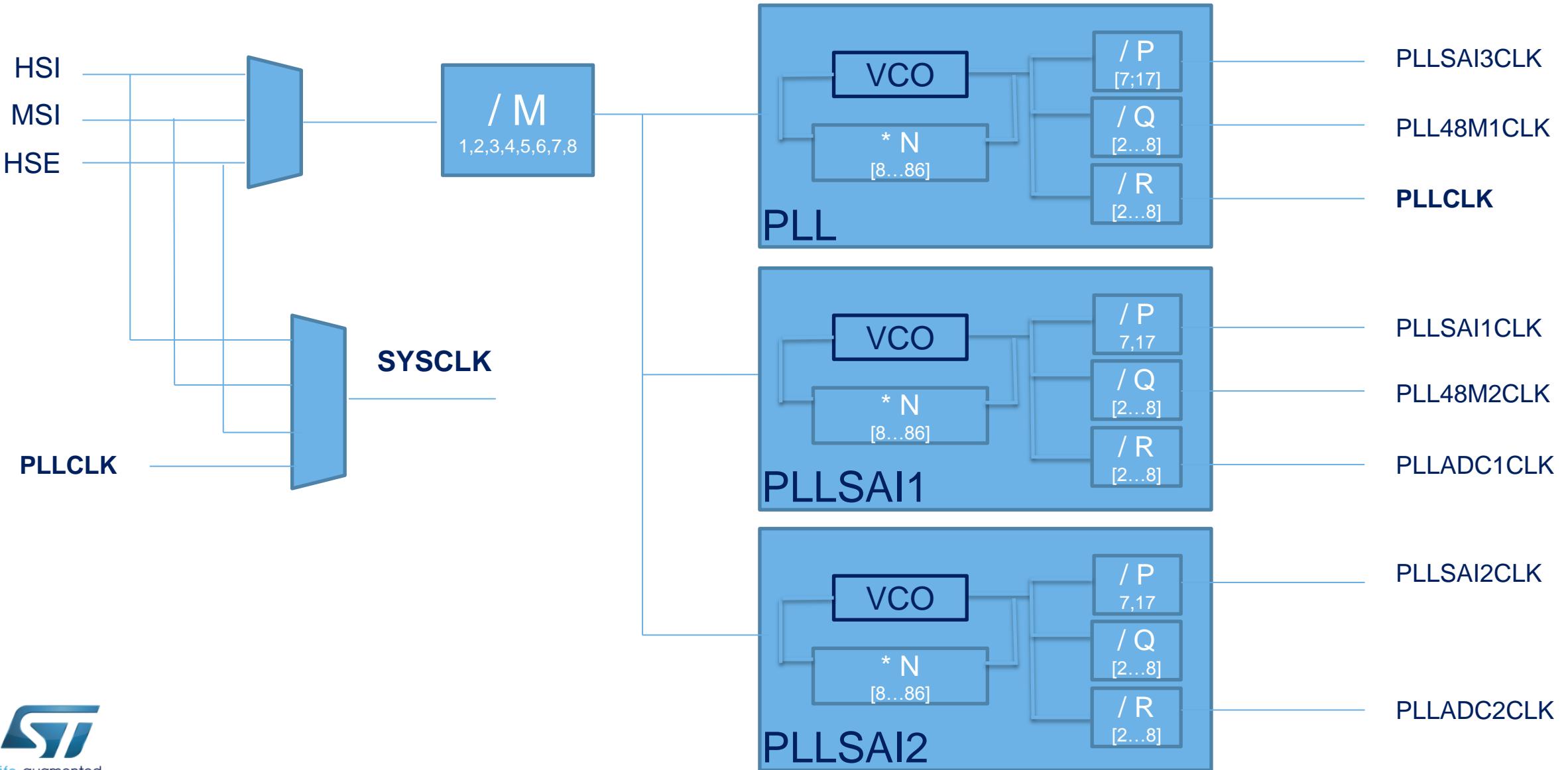

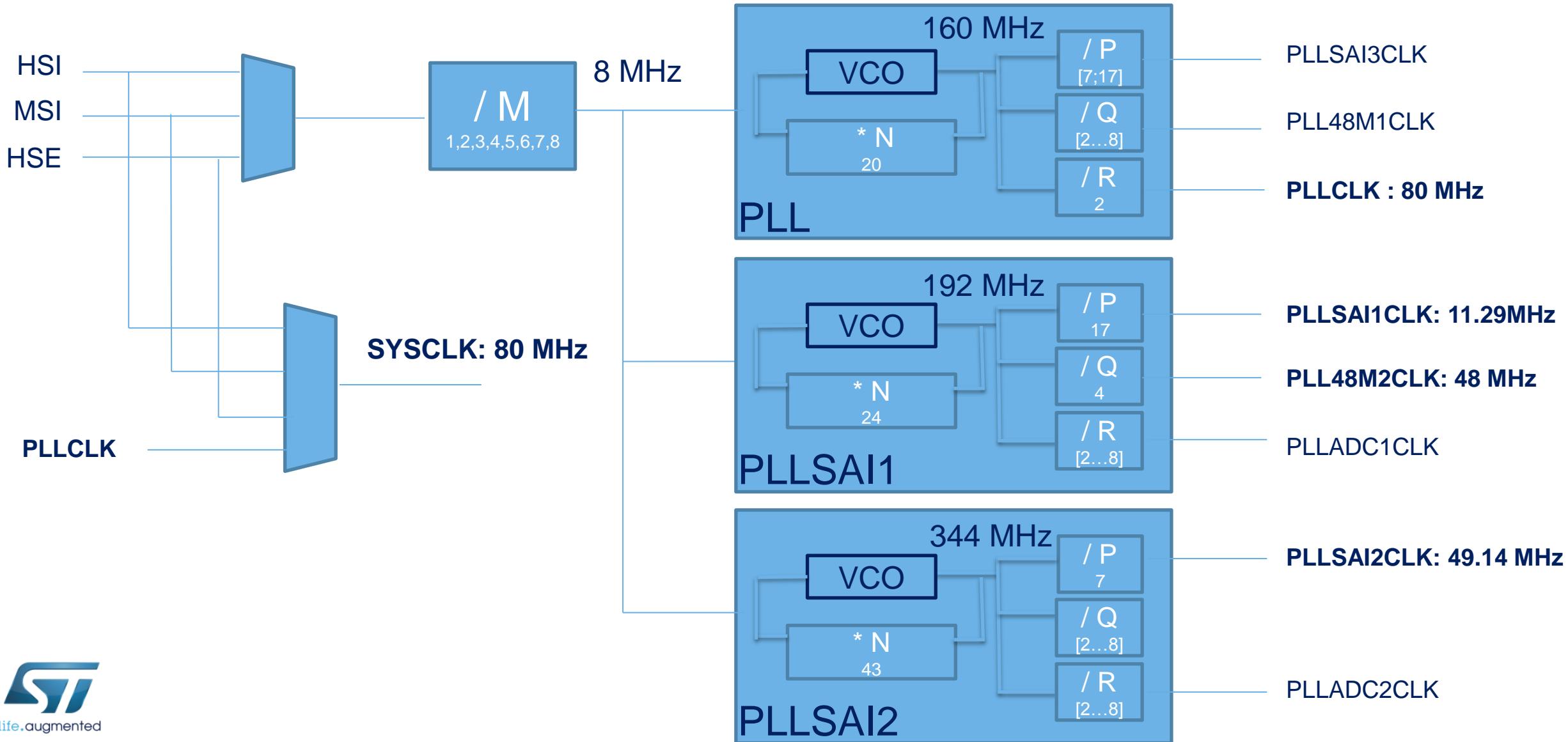

- 3つのPLL, それぞれに3つの独立した出力

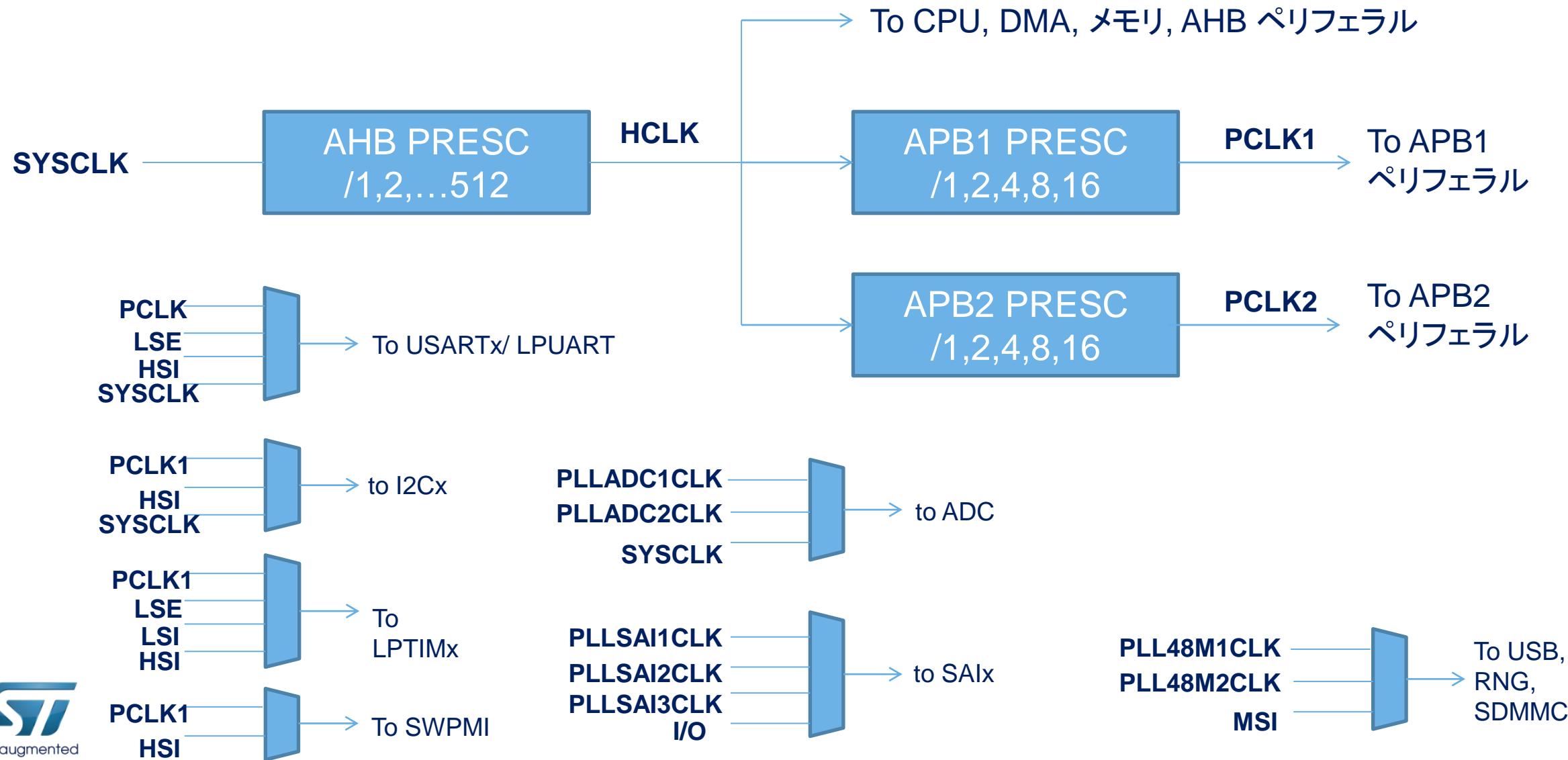

# 単純化したクロックツリー

8

# Multi-Speed 内部 (MSI)クロック

低消費電力のために低い周波数、パフォーマンスのために高い周波数

- MSIクロックはリセット、スタンバイ、シャットダウンモードからの起動時に使用される。

- プログラム可能な周波数:

- RCC\_CRの**MSIRANGE**で12レンジが選択可能: 100 kHz, 200 kHz, 400 kHz, 800 kHz, 1 MHz, 2 MHz, **4 MHz (リセット値)**, 8 MHz, 16 MHz, 24 MHz, 32 MHz, 48 MHz

- Reset、Shutdown後、MSI 周波数は4 MHz

- Standby後: 周波数は1、2、4、8 MHz から選択可能。これはRCC\_CSRの**MSISRANGE**で設定

- MSIRANGEで設定した周波数にスイッチするには、RCC\_CRレジスタの**MSIRGSEL** ビットをセットする必要がある

## USB device 対応のクロックソース

- MSI は以下のように選択できる

- Stop 1、Stop 2 モードからのウェイクアップクロック

- クロックセキュリティシステム(CSS)のバックアップ

- MSI には2つのモードがある:

- ノーマルモード。工場出荷およびユーザのトリミングあり

- **PLLモード (32.768 kHz LSEによる自動キャリブレーション)**

- USB FS デバイス機能とUART 通信のため

# High-Speed 内部 (HSI) クロック

11

1% の誤差および高速なウェイクアップタイム

- **HSI 16 MHz**は工場出荷およびユーザトリミング可能

- HSI は以下のように選択できる

- Stop 1、Stop 2 モードからのウェイクアップクロック

- クロックセキュリティシステム(CSS)のバックアップ

- Stopモードを終了するときに自動的に起動することができる

- I2C、U(S)ART、LPUARTは停止シーケンスからのウェイクアップを検出するために、Stopモード時にHSIを有効にすることが可能。

- HSIは、ペリフェラルウェイクアップシーケンスの検出を除いて、Stopモード時にオフのままである。

# HSI と MSI の特性の違い

12

|             | MSI (100 kHz to 48 MHz)                                                                                        |                                                    | HSI (16 MHz)                     |

|-------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------|

|             | MSI モード (w/o LSE)                                                                                              | PLL モード (w/ 32.768 kHz LSE)                        |                                  |

| 誤差 (typ.)   | Over [0 - 85 C]: +/- 1.55 %                                                                                    | 平均誤差 = LSE 誤差<br>ジッタ < 0.25%                       | Over [0-85 C]: +/- 0.8 %         |

|             | Over [1.62 - 3.6 V]: +0.8/-4.5 %                                                                               |                                                    | Over [1.62 - 3.6 V]: +0.1/-0.2 % |

| 消費電力 (typ.) | 100 kHz : 0.6 µA<br>800 kHz : 1.9 µA<br>1 MHz : 4.7 µA<br>8 MHz : 18.5 µA<br>16 MHz : 62 µA<br>48 MHz : 155 µA |                                                    | 150 µA                           |

| 起動時間 (typ.) | 100 kHz : 10 µs<br>48 MHz : 2.5 µs                                                                             | 最終周波数に対して5%誤差 : 0.5 ms<br>最終周波数に対して1%誤差 : 最大1.5 ms | 1 µs                             |

## 安全なクリスタルのクロック

- **HSE 4-48MHz**

- 外部入力 (バイパスモード) で最大 48 MHz

- 外部水晶およびセラミック振動子 (4 - 48 MHz)

- **クロックセキュリティシステム (CSS)**

- HSEの故障を自動的に検出し

- NMIを生成

- TIM1/TIM8/TIM15/TIM16/TIM17にブレーカ入力 => モータ制御などの重要なアプリケーションを安全な状態にすることが可能

- HISかMSIをバックアップクロックにする => アプリケーションソフトウェアはクリスタルが故障したとしても停止しない

- デフォルトはMSI

# Low-Speed 内部 (LSI) クロック

14

超低消費電力の内部 32 kHz 発信器

Shutdown と VBAT を除く全てのモードで有効

- LSI は RTC, LCD, LPTIMs, IWDG で使用可能

|             | LSI 32 kHz                                                      |

|-------------|-----------------------------------------------------------------|

| 誤差 (typ.)   | Over Temperature:<br>+/- 1.5 %<br><br>Over VDD:<br>+0.1 / -0.2% |

| 消費電力 (typ.) | 110 nA                                                          |

# Low-Speed 外部 (LSE) クロック

32.768 kHz を低消費電力またはハイドライブで設定可能

全てのパワー モード、VBAT モードで動作可能

- LSEは、外部の水晶または共振器、またはバイパスモードで外部クロック源を使用することができる

- LSEにおけるクロックセキュリティシステム:** ShutdownとVBATを除き使用可能。リセット中でも動作

- LSEは RTC, LCD, U(S)ARTs, LPUART, LPTIMs で使用される

| モード                 | 最大のクリスタル gm<br>( $\mu\text{A}/\text{V}$ ) | 消費電力 (nA) |

|---------------------|-------------------------------------------|-----------|

| Ultra-low power     | 0.5                                       | 250       |

| Medium-low driving  | 0.75                                      | 315       |

| Medium-high driving | 1.7                                       | 500       |

| High driving        | 2.7                                       | 630       |

# 3つのPLL クロック

16

## 44.1 kHzと48 kHzオーディオクロックの生成

- HSI/HSE/MSI/PLLから選択

- システムクロック,AHB, APB1, APB2 の最大周波数: 80 MHz

| 電圧レンジ               | SYSCLK   | MSI          | HSI    | HSE      | PLL                       |

|---------------------|----------|--------------|--------|----------|---------------------------|

| Range 1             | 最大80 MHz | 48 MHz range | 16 MHz | 48 MHz   | 80 MHz<br>最大VCO = 344 MHz |

| Range 2             | 最大26 MHz | 24 MHz range | 16 MHz | 26 MHz   | 26 MHz<br>最大VCO = 128 MHz |

| Low-power run/sleep | 最大2 MHz  | 2 MHz range  | 許可     | 分周器つきで許可 | 禁止                        |

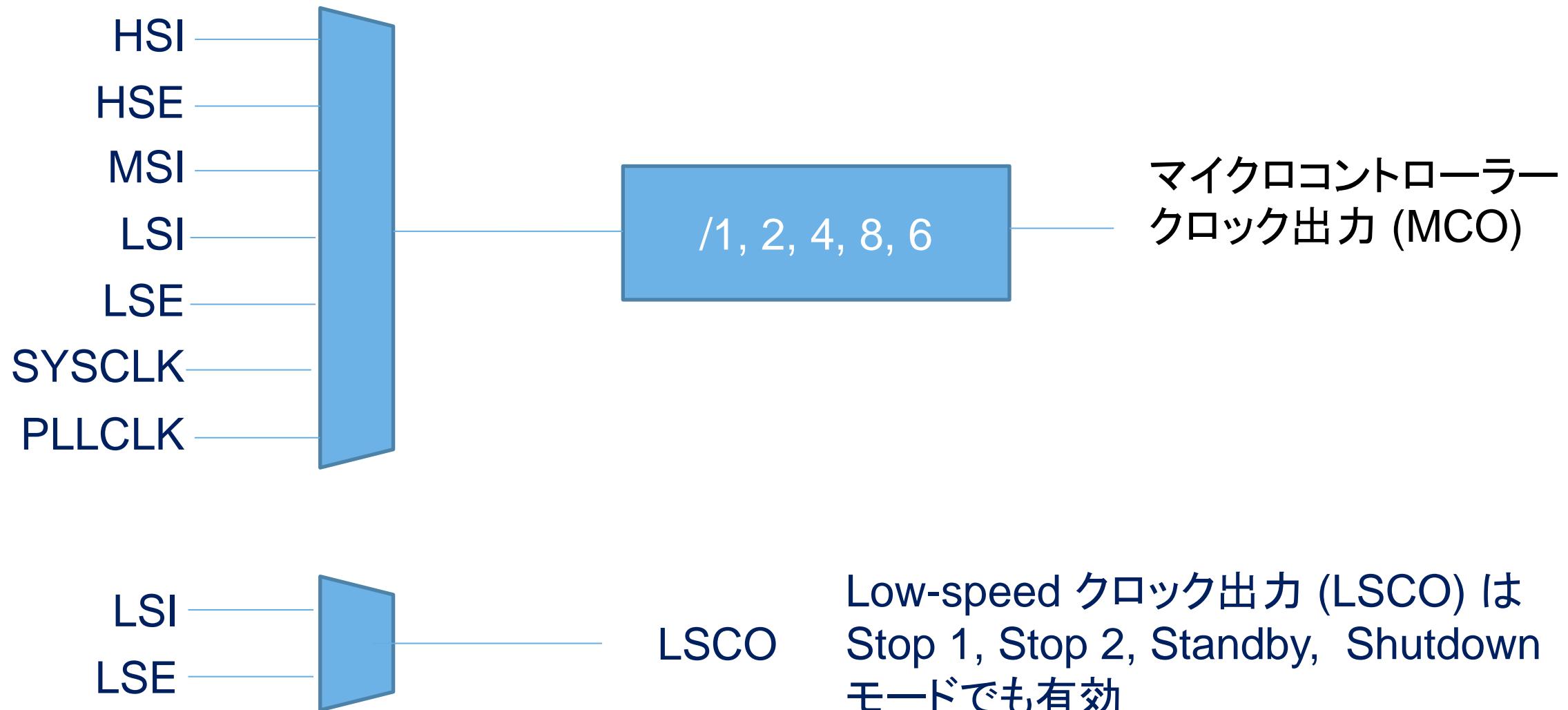

# クロック出力機能

20

## (LP)Runおよび(LP)Sleepのとき動的に消費電力を最適化する

- ペリフェラルクロックイネーブルレジスタ

- ペリフェラルクロックはデフォルトではディセーブル (Flash除く)

- クロックが無効のときはレジスタに読み書きできない

- 注意: SRAM1とSRAM2にはこのビットは無い (Run/LPRun モードで常に有効)

- Sleep、Stopモード時のペリフェラルクロックイネーブルレジスタ

- Sleep, LPSleep, Stop 1/2 モードでペリフェラルクロックの有効無効を設定

- 対応するペリフェラルのクロックが無効のときは、特に意味無し

- バスとカーネルの両方のクロックを制御

- Sleep と Stop モードに影響 (ペリフェラルがStopモード時に独立したクロックを持っているとき)

- 注意: SRAM1 と SRAM2 クロックはデフォルトでは Sleep/LPSleep モードで有効

# 割り込み

22

| 割り込みイベント           | 説明                          |

|--------------------|-----------------------------|

| LSE クロックセキュリティシステム | LSEの問題発生を検知するときにセット         |

| HSE クロックセキュリティシステム | HSEの問題発生を検知するときにセット         |

| PLLSAI2 レディ割り込みフラグ | PLLSAI2 lock で生成されるクロックがレディ |

| PLLSAI1 レディ割り込みフラグ | PLLSAI1 lock で生成されるクロックがレディ |

| PLL レディ割り込みフラグ     | PLL lock のクロックがレディ          |

| HSE レディ            | HSE のクロックがレディ               |

| HSI レディ            | HSI のクロックがレディ               |

| MSI レディ            | MSI のクロックがレディ               |

| LSE レディ            | LSE のクロックがレディ               |

| LSI レディ            | LSI のクロックがレディ               |

- 以下のトレーニングがこのペリフェラルに関係しているので参照してください。

- STM32L4 パワーコントロール (PWR)

- STM32L4 割り込み (NVIC-EXTI)

- 詳細は以下のドキュメントを参照してください

- AN2867 Oscillator design guide for STM8S, STM8A and STM32 microcontrollers

- AN4736 How to calibrate STM32L4 internal RC oscillators