# STM32L4 – SYSCFG

システムコンフィグレーションコントローラ

Revision 1

全てのSTM32L4デバイスは

“システムコンフィグレーションコントローラ”を備えています。

- メモリエリアのリマップ

- GPIO外部割込みの管理

- “連続運転”機能の管理

- SRAM2の保護機能

- FPU割り込み

- ファイアーウォールの有効

- I<sup>2</sup>C高速モード+の設定

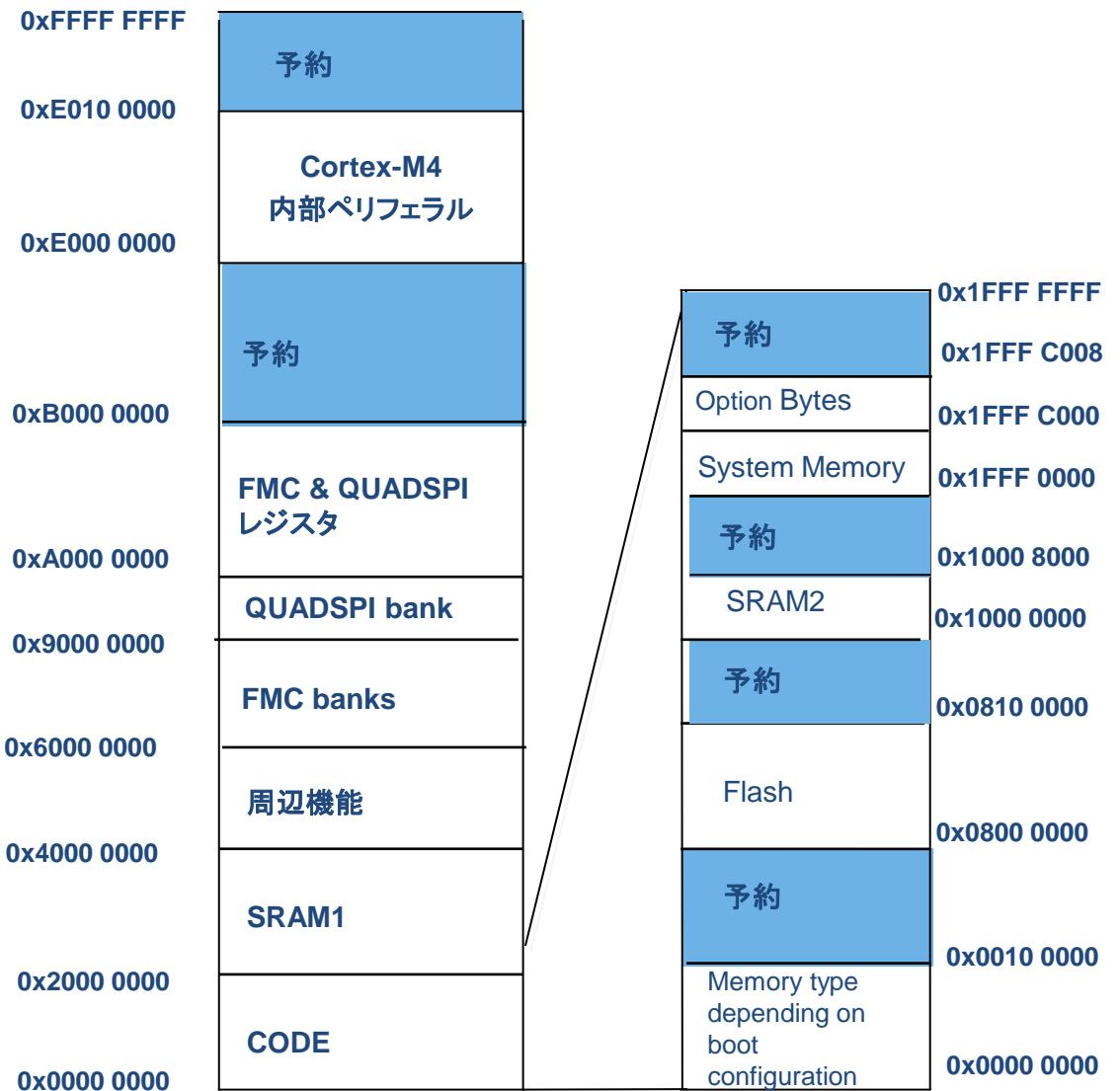

- フラッシュメモリ: 最大1MB、デュアルバンク

- SYSCFG\_MEMRMPでFB\_MODE = 0のとき:

- Bank 1 @ 0x0800 0000 (かつ0x0000 0000)

- Bank 2 @ 0x0808 0000

- SYSCFG\_MEMRMPでFB\_MODE = 1のとき

- Bank 2 @ 0x0800 0000 (かつ0x0000 0000)

- Bank 1 @ 0x0808 0000

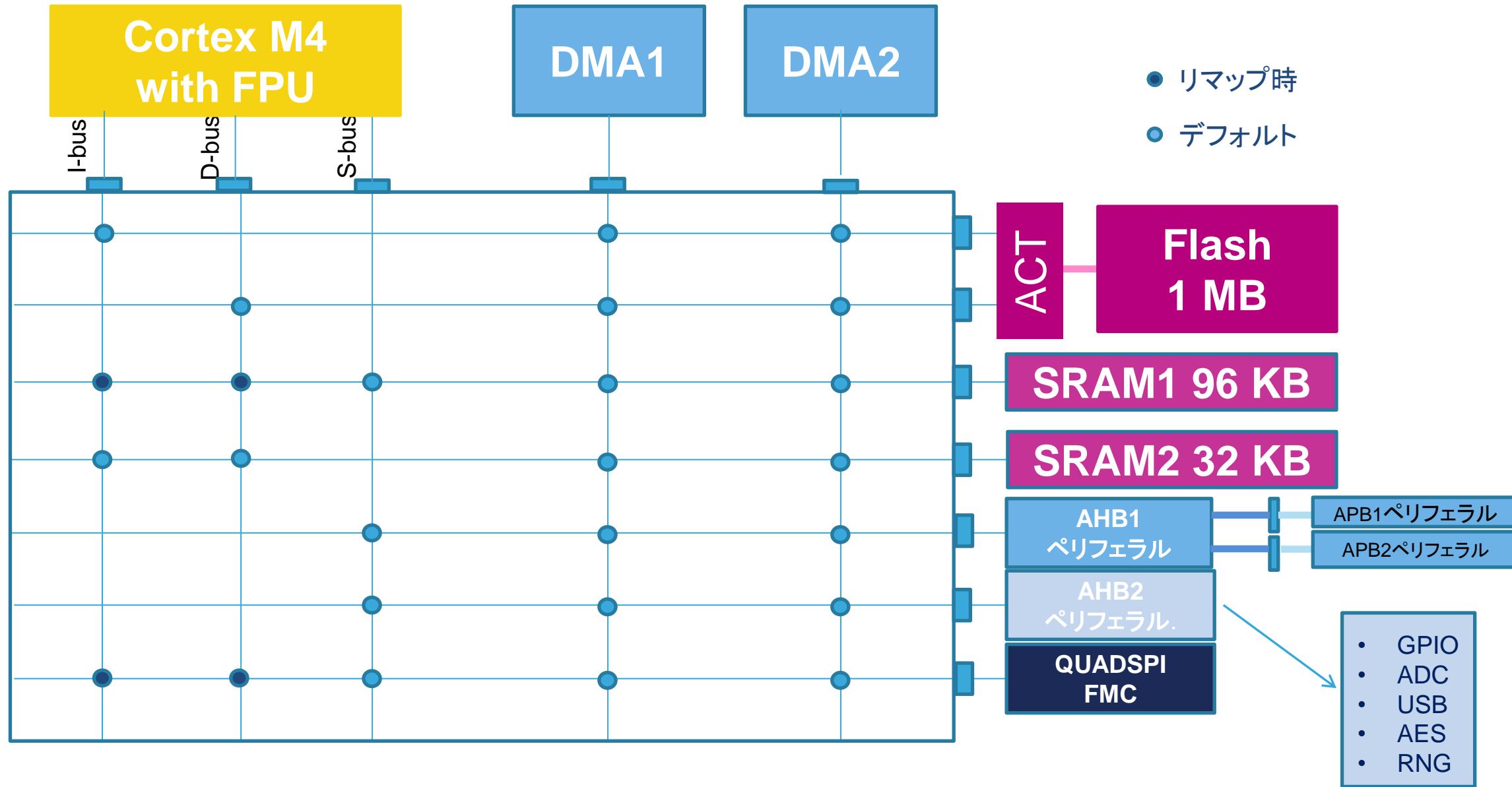

- SRAM: 128KBを2つにわける:

- SRAM1: 96 Kバイト @ 2000 0000

- SRAM2: 32 Kバイト @ 1000 0000

- D-codeとI-codeを通じてのアクセス

## パフォーマンス加速！

- アドレス 0x0000 0000 のリマップオプション

- メイン Flash メモリ

- システム Flash メモリ (Bootloader)

- FMC バンク 1 (NOR/PSRAM モード)

- SRAM1

- QUADSPI

- システムバスの代わりにI-bus/D-busをアクセスすることによってパフォーマンスを改善する

- SYSCFG\_MEMRMPのFB\_MODE

- Flash メモリのバンク 1 & 2 をスワップ

| Bootモード選択            |               | Bootモード              |

|----------------------|---------------|----------------------|

| nBOOT1<br>(オプションビット) | BOOT0<br>(ピン) |                      |

| X                    | 0             | ユーザー Flash メモリ       |

| 1                    | 1             | システムメモリ (bootloader) |

| 0                    | 1             | SRAM1                |

- Boot mode = ユーザー Flash メモリでオプションビット**BFB2 = 0**のとき

- Flash メモリバンク 1からboot

- Boot mode = ユーザー Flash メモリでオプションビット**BFB2 = 1**のとき

- Flash メモリバンク 2からboot(有効なとき)。有効でないときはバンク1から

| プロトコル | I/Oおよびコメント                                                     | コメント                                                                                              |

|-------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| USART | USART1 ピン PA9/PA10<br>USART2 ピン PA2/PA3<br>USART3 ピン PC10/PC11 |                                                                                                   |

| USB   | USB DFU interface ピン PA11/PA12                                 | BootloaderはHSEがあるかどうか調べる: USBクロックをHSEに<br>無い場合、BootloaderはLSEがあるかどうか調べる: USB クロックはLSEで自動トリムされたMSI |

| CAN   | CAN1 ピン PB8/PB9                                                |                                                                                                   |

| SPI   | SPI1 ピン PA4/PA5/PA6/PA7<br>SPI2 ピン PB12/PB13/PB14/PB15         |                                                                                                   |

| I2C   | I2C1 ピン PB6/PB7<br>I2C2 ピン PB10/PB11<br>I2C3 ピン PC0/PC1        | I2Cスレーブアドレスは0x86                                                                                  |

## スタンバイでのパフォーマンス、整合性と安全性(クラスB、SIL)、リテンション

- 32 KBのSRAM2はD-busおよびI-bus経由でアクセスできる:

- リマップ無しで、コード実行は最大のパフォーマンス

- HWパリティチェック: 1ワードにつき4bit

- ユーザーオプションバイトでSRAM2\_PEを有効にする

- パリティエラー時にNMI生成

- オプションでタイマをブレークできる

- オプションでスタンバイ時にリテンション(保持)可能

## セキュア SRAM

- 書き込み保護 – 1KB単位

- **SYSCFG\_SWPR** は書き込み保護レジスタ

- 読み出し・書き込み保護 – RDPによる

- RDPがレベル1から0になったときに消去

- ソフトウェアリセットまたはオプションでハードウェアリセット – システムリセット時

- **SRAM2ER** ビットがセットされていると消去

- ユーザーオプションバイトの**SRAM2\_RST** のときにシステムリセットで消去

## 安全性と堅牢性

### コンフィグレーションレジスタ2内の安全性と堅牢性機能

- SRAM2パリティエラーフラグ

- ECCロックはFlashのECCエラーをTIM1/8/15/16/17のブレーク入力に接続する

- PVDロック はPVD割り込みをTIM1/8/15/16/17ブレーク入力に接続する

- SRAM2パリティエラーをTIM1/8/15/16/17ブレーク入力に接続する

- CLLロックはCortex M4のHard Fault割り込みを TIM1/8/15/16/17ブレーク入力に接続する

=> アプリケーションがクラッシュしたときにアプリケーションが安全な状態になるように

タイマに入力する

# SYSCFGその他の特徴

11

- GPIOx (x=A,...H) とつながる外部割込み (EXTI) の管理

- PA[n] PB[n] .... PH[n] (n=0,...15) のEXTInを選択するための16 個のマルチプレクサ

- コンフィグレーションレジスタ1

- FPU 割り込み有効

- I2C GPIO Fast-mode Plus 20 mA ドライブ有効

- PB6, PB7, PB8, PB9 ハイドライブはI2Cとして使われていないときでも有効にできる

- 電圧ブースター対応の I/O アナログスイッチ

- Firewall 有効

|                            | Flash メモリからの実行                                    |                                                    |         | SRAMからの実行               |                                 |

|----------------------------|---------------------------------------------------|----------------------------------------------------|---------|-------------------------|---------------------------------|

|                            | ART ON<br>I-Cache ON<br>D-Cache ON<br>Prefetch ON | ART ON<br>I-Cache ON<br>D-Cache ON<br>Prefetch OFF | ART OFF | Code & Data<br>in SRAM1 | Code in SRAM2,<br>Data in SRAM1 |

| CoreMark / MHz<br>@ 80 MHz | 3.35                                              | 3.32                                               | 1.55    | 2.37                    | 3.42                            |

- このペリフェラルにリンクされているこれらのトレーニングモジュールを参照:

- リセットおよびクロック制御 (RCC)

- パワーコントローラ(PWR)

- 割り込み (NVIC-EXTI)

- Flash メモリ (Flash)

- システムメモリ保護

- タイマ (TIM)

- I<sup>2</sup>C

- 詳細は以下を参考にしてください:

- AN2606: STM32 microcontroller system memory boot mode

- AN4435: Guidelines for obtaining UL/CSA/IEC 60335 Class B certification in any STM32 application