# STM32H7R3xx STM32H7R7xx STM32H7S3xx STM32H7S7xx

Errata sheet

## STM32H7Rxx/7Sxx device errata

## **Applicability**

This document applies to the part numbers of STM32H7Rxx/7Sxx devices and the device variants as stated in this page. It gives a summary and a description of the device errata, with respect to the device datasheet and reference manual RM0477. Deviation of the real device behavior from the intended device behavior is considered to be a device limitation. Deviation of the description in the reference manual or the datasheet from the intended device behavior is considered to be a documentation erratum. The term "errata" applies both to limitations and documentation errata.

**Table 1. Device summary**

| Reference   | Part numbers                                                                              |

|-------------|-------------------------------------------------------------------------------------------|

| STM32H7R3xx | STM32H7R3A8, STM32H7R3I8, STM32H7R3L8, STM32H7R3N8, STM32H7R3R8, STM32H7R3V8, STM32H7R3Z8 |

| STM32H7R7xx | STM32H7R7A8, STM32H7R7I8, STM32H7R7L8, STM32H7R7Z8                                        |

| STM32H7S3xx | STM32H7S3A8, STM32H7S3I8, STM32H7S3L8, STM32H7S3R8, STM32H7S3V8, STM32H7S3Z8              |

| STM32H7S7xx | STM32H7S7A8, STM32H7S7I8, STM32H7S7L8, STM32H7S7Z8                                        |

Table 2. Device variants

| Reference      | Silicon revision codes        |                       |  |  |

|----------------|-------------------------------|-----------------------|--|--|

| Reference      | Device marking <sup>(1)</sup> | REV_ID <sup>(2)</sup> |  |  |

|                | Y                             | 0x1003                |  |  |

| STM32H7Rxx/Sxx | В                             | 0x2000                |  |  |

|                | B SFSP 2.1.0                  | 0x2000                |  |  |

- 1. Refer to the device datasheet for how to identify this code on different types of package.

- 2. REV\_ID[15:0] bitfield of register.

## Summary of device errata

The following table gives a quick reference to the STM32H7Rxx/7Sxx device limitations and their status:

A = limitation present, workaround available

N = limitation present, no workaround available

P = limitation present, partial workaround available

"-" = limitation absent

Applicability of a workaround may depend on specific conditions of target application. Adoption of a workaround may cause restrictions to target application. Workaround for a limitation is deemed partial if it only reduces the rate of occurrence and/or consequences of the limitation, or if it is fully effective for only a subset of instances on the device or in only a subset of operating modes, of the function concerned.

Table 3. Summary of device limitations

|          |         |                                                                                                        | Status           |                  |                            |  |

|----------|---------|--------------------------------------------------------------------------------------------------------|------------------|------------------|----------------------------|--|

| Function | Section | Limitation                                                                                             |                  | Rev.<br>B        | Rev.<br>B<br>SFSP<br>2.1.0 |  |

|          | 2.1.1   | PLD might perform linefill to address that would generate a MemManage Fault                            | А                | А                | Α                          |  |

| Core     | 2.1.2   | Software programming errors might not be reported for online MBIST access to the ICACHE                | N                | N                | N                          |  |

| Core     | 2.1.3   | ECC error causes data corruption when the data cache error bank registers are locked                   | А                | А                | А                          |  |

|          | 2.1.4   | Store after cache invalidate without intervening barrier might cause inconsistent memory view          | А                | А                | А                          |  |

|          | 2.2.1   | Boundary scan, PC10 and PC11 are not controllable on TFBGA100 package                                  | Р                | Р                | Р                          |  |

|          | 2.2.2   | Only one configuration available using MCE on the FMC interface                                        | N                | N                | N                          |  |

|          | 2.2.3   | Data read might be corrupted on FMC NOR                                                                | Α                | Α                | Α                          |  |

|          | 2.2.4   | Incorrect backup domain reset                                                                          | Р                | Р                | Р                          |  |

|          | 2.2.5   | SRAM1 AHB limitation if the device is not in OPEN state                                                | N <sup>(1)</sup> | -                | -                          |  |

|          | 2.2.6   | LSE crystal oscillator may be disturbed by transitions on PC13                                         | N                | N                | N                          |  |

|          | 2.2.7   | Secure Firmware Install (SFI) is not supported                                                         | N <sup>(1)</sup> | -                | -                          |  |

|          | 2.2.8   | Debug authentication timeout with force download feature                                               | N <sup>(1)</sup> | -                | -                          |  |

| System   | 2.2.9   | RSSLIB: AHB SRAM2 clock is enabled in closed and locked product states                                 | N <sup>(1)</sup> | -                | -                          |  |

| System   | 2.2.10  | Backup domain erased upon reset when STiRoT boot is active and an RTC clock other than LSI is selected | А                | A <sup>(1)</sup> | -                          |  |

|          | 2.2.11  | Tampers are not usable with STiRoT                                                                     | Α                | A <sup>(1)</sup> | -                          |  |

|          | 2.2.12  | RSS Boot fails if a tamper event arises during startup                                                 | Р                | P <sup>(1)</sup> | -                          |  |

|          | 2.2.13  | PRODUCT_STATE different than Open, RSS force its tamper configuration at each boot                     | Α                | A <sup>(1)</sup> | -                          |  |

|          | 2.2.14  | During RSS execution, any error resets the backup registers and device secrets                         | N                | N <sup>(1)</sup> | -                          |  |

|          | 2.2.15  | I/O compensation could alter duty-cycle of high-frequency output signal                                | Α                | А                | Α                          |  |

|          | 2.2.16  | Manual forcing of OTG_FS host or device mode when not possible via ID pin (PM13)                       | Α                | Α                | А                          |  |

ES0596 - Rev 8 page 2/46

|          |         |                                                                                                                                                                |   | Status    |                            |  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------|----------------------------|--|

| Function | Section | Limitation                                                                                                                                                     |   | Rev.<br>B | Rev.<br>B<br>SFSP<br>2.1.0 |  |

|          | 2.3.1   | Dummy read cycles inserted when reading synchronous memories                                                                                                   | N | N         | N                          |  |

|          | 2.3.2   | Wrong data read from a busy NAND memory                                                                                                                        | Α | Α         | Α                          |  |

| FMC      | 2.3.3   | Unsupported read access with unaligned address                                                                                                                 | Р | Р         | Р                          |  |

|          | 2.3.5   | Duty cycle variation on memory clock while accessing PSRAM in continuous clock mode                                                                            | Α | Α         | Α                          |  |

|          | 2.4.1   | Memory-mapped write error response when DQS output is disabled                                                                                                 | Р | Р         | Р                          |  |

|          | 2.4.2   | Deadlock can occur under certain conditions                                                                                                                    | Α | Α         | Α                          |  |

|          | 2.4.3   | Memory wrap instruction not enabled when DQS is disabled                                                                                                       | N | N         | N                          |  |

|          | 2.4.4   | Deadlock or write-data corruption after spurious write to a misaligned address in XSPI_AR register                                                             | N | N         | N                          |  |

|          | 2.4.5   | XSPI deadlock or RAM content corrupted on CSBOUND split during prefetch, when DQS is disabled                                                                  | Α | Α         | Α                          |  |

|          | 2.4.6   | Read-modify-write operation does not clear the MSEL bit                                                                                                        | Α | Α         | Α                          |  |

| XSPI     | 2.4.7   | CALMAX bit not set when the PHY reaches the DLL maximum value                                                                                                  | N | N         | N                          |  |

|          | 2.4.8   | Read data corruption when a wrap transaction is followed by a linear read to the same MSB address                                                              | N | N         | N                          |  |

|          | 2.4.9   | Transactions are limited to 8 Mbytes in OctaRAM <sup>™</sup> memories                                                                                          | N | N         | N                          |  |

|          | 2.4.10  | Variable latency is not supported when a refresh collision occurs during a write access to some OctaRAM <sup>™</sup> memories                                  | Р | Р         | Р                          |  |

|          | 2.4.11  | In automatic status-polling and multiplexed modes, the controller does not request the port if less than two bytes are sent per cycle when XSPI_DLR is cleared | А | А         | Α                          |  |

| XSPIM    | 2.5.1   | Certain quad memories may be reset during arbitration while in single-SPI mode                                                                                 | Α | Α         | Α                          |  |

| SDMMC    | 2.6.1   | Command response and receive data end bits not checked                                                                                                         | N | N         | N                          |  |

|          | 2.7.1   | New context conversion initiated without waiting for trigger when writing new context in ADC_JSQR with JQDIS = 0 and JQM = 0                                   | Α | Α         | Α                          |  |

|          | 2.7.2   | Two consecutive context conversions fail when writing new context in ADC_JSQR just after previous context completion with JQDIS = 0 and JQM = 0                | А | А         | А                          |  |

| ADC      | 2.7.3   | Unexpected regular conversion when two consecutive injected conversions are performed in Dual interleaved mode                                                 | Α | Α         | Α                          |  |

|          | 2.7.4   | ADC_AWDy_OUT reset by non-guarded channels                                                                                                                     | Α | Α         | Α                          |  |

|          | 2.7.5   | Injected data stored in the wrong ADC_JDRx registers                                                                                                           | Α | Α         | Α                          |  |

|          | 2.7.6   | ADC slave data may be shifted in Dual regular simultaneous mode                                                                                                | Α | Α         | Α                          |  |

| ADF      | 2.8.1   | In LFM mode ADF_CCK1 clock cannot be selected for SITFx interfaces                                                                                             | Α | Α         | Α                          |  |

| PSSI     | 2.9.1   | Output mode not usable with both PSSI_RDY and PSSI_DE signals enabled                                                                                          | N | N         | N                          |  |

| GPU2D    | 2.10.1  | Occasional writing miss to frame buffer with slow memories                                                                                                     |   | -         | -                          |  |

| TIM      | 2.11.1  | Unexpected PWM output when using ocref_clr                                                                                                                     | N | N         | N                          |  |

| LPTIM    | 2.12.1  | Device may remain stuck in LPTIM interrupt when entering Stop mode                                                                                             | А | Α         | Α                          |  |

ES0596 - Rev 8 page 3/46

|              |         |                                                                                                                                            | Status    |           |                            |  |

|--------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|----------------------------|--|

| Function     | Section | Limitation                                                                                                                                 | Rev.<br>Y | Rev.<br>B | Rev.<br>B<br>SFSP<br>2.1.0 |  |

| LPTIM .      | 2.12.2  | ARRM and CMPM flags are not set when APB clock is slower than kernel clock                                                                 | Α         | А         | А                          |  |

| LITIM        | 2.12.3  | Interrupt status flag is cleared by hardware upon writing its corresponding bit in LPTIM_DIER register                                     | N         | N         | N                          |  |

| RTC and TAMP | 2.13.1  | Alarm flag may be repeatedly set when the core is stopped in debug                                                                         | N         | N         | N                          |  |

|              | 2.14.1  | Wrong data sampling when data setup time (t <sub>SU;DAT</sub> ) is shorter than one I2C kernel clock period                                | Р         | Р         | Р                          |  |

| I2C          | 2.14.2  | Spurious bus error detection in controller mode                                                                                            | Α         | Α         | Α                          |  |

|              | 2.14.3  | SDA held low upon SMBus timeout expiry in target mode                                                                                      | Α         | Α         | Α                          |  |

|              | 2.15.1  | I3C controller: unexpected read data bytes during a legacy I <sup>2</sup> C read                                                           | Α         | Α         | Α                          |  |

|              | 2.15.2  | I3C controller: SCL clock is not stalled during address ACK/NACK phase following a frame start, when enabled through I3C_TIMINGR2 register | Α         | Α         | А                          |  |

|              | 2.15.3  | I3C controller: unexpected first frame with a 0x7F address when the I3C peripheral is enabled                                              | Α         | А         | А                          |  |

| I3C          | 2.15.4  | I3C controller: no timestamp on IBI acknowledge when timing control is used in Asynchronous mode 0                                         | Α         | А         | А                          |  |

|              | 2.15.5  | I3C target: device returns incorrect value on read RSTACT CCC                                                                              | Α         | Α         | Α                          |  |

|              | 2.15.6  | I3C target: device can report target error 0 before dynamic address assignment                                                             | Α         | А         | А                          |  |

|              | 2.15.7  | I3C target: nonparticipation in dynamic address procedure after NACKed hot-join request                                                    | Α         | А         | А                          |  |

|              | 2.15.8  | I3C target: device fails to resynchronize with Sr or P condition in specific cases                                                         | Α         | А         | А                          |  |

|              | 2.16.1  | Data corruption due to noisy receive line                                                                                                  | -         | Α         | Α                          |  |

| USART        | 2.16.2  | Wrong data received in smartcard mode and 0.5 stop bit configuration                                                                       | Α         | -         | -                          |  |

| USARI        | 2.16.3  | Received data may be corrupted upon clearing the ABREN bit                                                                                 | Α         | Α         | Α                          |  |

|              | 2.16.4  | Noise error flag set while ONEBIT is set                                                                                                   | N         | N         | N                          |  |

| LPUART       | 2.17.1  | Possible LPUART transmitter issue when using low BRR[15:0] value                                                                           | Р         | Р         | Р                          |  |

|              | 2.18.1  | RDY output failure at high serial clock frequency                                                                                          | N         | N         | N                          |  |

| SPI          | 2.18.2  | Truncation of SPI output signals after EOT event                                                                                           | Α         | Α         | Α                          |  |

| 581          | 2.18.3  | TIFRE flag wrongly set in slave PCM long frame mode if FIXCH = 1                                                                           | N         | N         | N                          |  |

|              | 2.18.4  | TIFRE flag never set in slave PCM/I2S mode if FIXCH = 0                                                                                    | N         | N         | N                          |  |

|              | 2.19.1  | Desynchronization under specific condition with edge filtering enabled                                                                     | Α         | Α         | Α                          |  |

| FDCAN        | 2.19.2  | Tx FIFO messages inverted under specific buffer usage and priority setting                                                                 | Α         | А         | А                          |  |

|              | 2.20.1  | Issue during control and status register access interleaved with TxFIFO push in device and host slave mode                                 | Α         | Α         | А                          |  |

| OTG_FS       | 2.20.2  | Potential unexpected transfer on the USB bus instead of a zero-length packet                                                               | А         | А         | А                          |  |

|              | 2.20.3  | False OTG_GINTSTS.CIDSCHG interrupt after reset                                                                                            | Α         | Α         | Α                          |  |

|              | 2.21.1  | Isochronous IN EP disabled when packet fetch is in progress                                                                                | Α         | Α         | Α                          |  |

| OTG_HS       | 2.20.3  | False OTG_GINTSTS.CIDSCHG interrupt after reset                                                                                            | Α         | Α         | Α                          |  |

ES0596 - Rev 8 page 4/46

|          |         | Limitation                                                                                                                        |   | Status    |                            |  |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------|---|-----------|----------------------------|--|

| Function | Section |                                                                                                                                   |   | Rev.<br>B | Rev.<br>B<br>SFSP<br>2.1.0 |  |

| OTG_HS   | 2.21.3  | Potential unexpected transfer on the USB bus instead of a zero-length packet                                                      | Α | Α         | Α                          |  |

|          | 2.21.4  | False detection of chirp-K when a FS device is connected                                                                          | Α | Α         | Α                          |  |

| UCPD     | 2.22.1  | Ordered set with multiple errors in a single K-code is reported as invalid                                                        | N | N         | N                          |  |

|          | 2.23.1  | The MAC does not provide bus access to a higher priority request after a low priority request is serviced                         | N | N         | N                          |  |

|          | 2.23.2  | Rx DMA engine may fail to recover upon a restart following a bus error, with Rx timestamping enabled                              | Α | Α         | Α                          |  |

|          | 2.23.3  | Tx DMA engine fails to recover correctly or corrupts TSO/USO header data on receiving a bus error response from the AHB DMA slave | N | N         | N                          |  |

|          | 2.23.4  | Incorrectly weighted round robin arbitration between Tx and Rx DMA channels to access the common host bus                         | Α | А         | А                          |  |

|          | 2.23.5  | Incorrect L4 inverse filtering results for corrupted packets                                                                      | N | N         | N                          |  |

| ETH      | 2.23.6  | IEEE 1588 Timestamp interrupt status bits are incorrectly cleared on write access to the CSR register with similar offset address | Α | Α         | А                          |  |

|          | 2.23.7  | Bus error along with Start-of-Packet can corrupt the ongoing transmission of MAC generated packets                                | N | N         | N                          |  |

|          | 2.23.8  | Spurious receive watchdog timeout interrupt                                                                                       | Α | Α         | Α                          |  |

|          | 2.23.9  | Incorrect flexible PPS output interval under specific conditions                                                                  | Α | Α         | Α                          |  |

|          | 2.23.10 | Packets dropped in RMII 10 Mbps mode due to fake dribble and CRC error                                                            | Α | Α         | А                          |  |

|          | 2.23.11 | ARP offload function not effective                                                                                                | Α | Α         | Α                          |  |

| CEC      | 2.24.1  | Missed CEC messages in normal receiving mode                                                                                      | Α | Α         | А                          |  |

| CEC      | 2.24.2  | Unexpected TXERR flag during a message transmission                                                                               | Α | Α         | Α                          |  |

<sup>1.</sup> This limitation will be fixed in the next revision

The following table gives a quick reference to the documentation errata.

Table 4. Summary of device documentation errata

| Function | Section | Documentation erratum                                                                       |

|----------|---------|---------------------------------------------------------------------------------------------|

| FMC      | 2.3.4   | CTB1, CTB2, MODE[2:0] write-only bitfields in FMC_SDCMR incorrectly described as readwrite  |

| XSPI     | 2.4.12  | IO states during dummy cycles phase on write transactions are not in a high impedance state |

ES0596 - Rev 8 page 5/46

## 2 Description of device errata

The following sections describe the errata of the applicable devices with Arm<sup>®</sup> core and provide workarounds if available. They are grouped by device functions.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

### **2.1** Core

Reference manual and errata notice for the Arm<sup>®</sup> Cortex<sup>®</sup>-M7 core r1p2 is available from http://infocenter.arm.com.

### 2.1.1 PLD might perform linefill to address that would generate a MemManage Fault

#### **Description**

If the MPU is present and enabled, then it can be programmed so that loads to certain addresses generate a MemManage Fault. This could be because:

- The address is unmapped, that is, it is not in an enabled region and the default memory map is not being used.

- The address cannot be accessed at the current privilege level.

- The address cannot be accessed at any privilege level.

Because of this erratum, a PLD to such an address might incorrectly cause a data cache line-fill.

#### Conditions:

- The data cache is enabled and the MPU is enabled.

- A PLD is executed, and either:

- The PLD is to an address not mapped in the MPU, which requires that:

- The MPU is enabled.

- The default memory map is not being used.

- The default memory map is cacheable at that address.

- The PLD does not hit an enabled MPU region.

- The PLD is to a region that has permission requirements that the PLD does not meet, which requires that:

- The MPU is enabled.

- The default memory map is not being used.

- The region that the PLD hits is cacheable.

- The region that the PLD hits would generate a MemManage fault for a load. This requires either:

- The region cannot be accessed by a read at any privilege level.

- The region only has read access for privileged code and the PLD is unprivileged.

Note that in rare cases, a PLD instruction can be speculatively executed in the shadow of a mispredicted branch. This can even theoretically be a literal value that decodes to a PLD.

Processor execution is not affected by this erratum. The data returned from the line-fill is not directly consumed by the PLD. Any subsequent load to that address can only access the data if it has permission to do so. This erratum does not permit software to access data that it does not have permissions for.

The only implications of this erratum are the access itself that should not have been performed. This might have an impact on memory regions with side-effects on reads or on memory, which never returns a response on the bus.

ES0596 - Rev 8 page 6/46

Accesses to memory that is not mapped in the MPU can be avoided by using MPU region 0 to cover all unmapped memory and make this region execute-never and inaccessible. That is, MPU\_RASR0 must be programmed with:

- The ENABLE bit of the MPU RASR0 register = 0b1; MPU region 0 enable

- The SIZE bit of the MPU\_RASR0 register = 0b11111; MPU region 0 size = 2^32 bytes to cover entire

memory

- The SRD bit of the MPU RASR0 register = 0b0000 0000; All sub-regions enabled

- The XN bit of the MPU RASR0 register = 0b1; Execute-never to prevent instruction fetch

- The AP bit of the MPU\_RASR0 register = 0b000; No read or write access for any privilege level

- The TEX bit of the MPU RASR0 register = 0b000; Attributes = Strongly-ordered

- The C bit of the MPU RASR0 register = 0b0; Attributes = Strongly-ordered

- The B bit of the MPU RASR0 register = 0b0; Attributes = Strongly-ordered

Accesses to memory that is mapped in the MPU, but should not be accessed at the current privilege level can be avoided by making the region noncacheable. That is, MPU\_RASR0 should be programmed with:

- The TEX bit of the MPU RASR0 register = 0b000; Attributes = Strongly-ordered

- The C bit of the MPU RASR0 register = 0b0; Attributes = Strongly-ordered

- The B bit of the MPU RASR0 = 0b0; Attributes = Strongly-ordered

### 2.1.2 Software programming errors might not be reported for online MBIST access to the ICACHE

### **Description**

The online MBIST interface provides access to the cache and TCM RAMs to allow in-field memory testing during normal operation of the processor. Because of this erratum, errors in the software that works with the memory testing might not be indicated on the MBISTERR output signal as intended for ICACHE tests.

Note that this erratum does not affect the detection of faults in the memories under test, but affects only the feature that helps to indicate errors in software used during testing.

There are two online MBIST use cases: software transparent and software assisted.

In the software transparent use case, software running on the processor is not involved in or aware of the memory testing being carried out. See the Cortex<sup>®</sup>-M7 safety manual for more details. In this case, the target memory is automatically locked by the MBIST controller, which causes the processor pipeline to stall if it attempts to access this memory. Testing is carried out using short bursts of accesses, which last for less than 20 clock cycles and do not corrupt the memory contents. For this reason, the memory is locked only for a very short period of time and the gap between bursts is very large.

In the software-assisted use case, the target memory is still locked by the MBIST controller, but the software running on the processor disables the target memory before testing commences. This prevents any software access to this memory during testing. See the Cortex<sup>®</sup>-M7 safety manual for more details. For this reason, software accesses go to another memory instead of the target memory and the pipeline does not stall. This is important because the software-assisted use case is intended to be used for production MBIST algorithms, which take a long time to run. For example, if the ICACHE were disabled then software might still execute using the main memory or the TCMs.

This erratum only affects the software-assisted use case, when the ICACHE RAMs are tested. An error indication is sent back to the MBIST controller if software attempts to access the target memory while it is locked for testing. Because of this erratum, an error is not indicated back to the MBIST controller on the MBISTERR[0] output signal when software performs a lookup to the ICACHE during MBIST testing.

The error indication is correctly asserted for all the other types of ICACHE access during MBIST testing:

- A cache line invalidates because of an ECC error.

- A cache invalidates by MVA.

- A cache invalidates all operation.

- A cache line-fill allocation.

Note that this erratum only affects the MBIST software-assisted use case error indication for the ICACHE and the MBISTERR[0] signal functions correctly for the DCACHE, ITCM, and DTCM.

ES0596 - Rev 8 page 7/46

The following conditions are required to cause this erratum:

- The software intends to use the software assisted online MBIST use case.

- The ICACHE is not disabled by software running on the Cortex<sup>®</sup>-M7 before testing commences.

- The MBIST controller selects an ICACHE memory array for testing, locks the target memory, and testing commences

This erratum could result in an error not being indicated back to the MBIST controller on the MBISTERR[0] output signal when software assisted use case is used and the ICACHE is not disabled by software before testing commences. This could result in the processor unexpectedly stalling for a long period of time during MBIST testing of the ICACHE memories, without there being a clear indication of the cause of the stall. For this reason, the processor might not make progress as expected, because of the software error, during ICACHE testing.

#### Workaround

There is no workaround for this erratum.

#### 2.1.3 ECC error causes data corruption when the data cache error bank registers are locked

#### Description

The data cache contains two error bank registers, DEBR0 and DEBR1. These registers store the locations in the cache that error correcting code (ECC) errors affect and prevent future allocations to those locations.

Software can lock each DEBR, and this prevents the DEBR from being automatically updated when a data cache ECC error is detected.

Because of this erratum, if both DEBR0 and DEBR1 are locked and an ECC error is detected on a cacheable store, then the store data is written onto the bus, but not written into the data cache. This might result in the data cache containing stale data.

#### Conditions:

- DEBR0 and DEBR1 are locked.

- The wanted address has been allocated to the cache.

- A cacheable store to the wanted address looks up in the cache, and an ECC error is found in the cache set that the store addresses.

This erratum can cause data corruption in the data cache.

## Workaround

Software must avoid locking both error bank registers.

## 2.1.4 Store after cache invalidate without intervening barrier might cause inconsistent memory view

## **Description**

If a cache invalidate operation is followed by a write-through store to an address affected by that operation and a line-fill to that address occurs, then the line-fill might allocate to the cache without the data from the store. Subsequently, that store writes to the bus and leaves the cache with stale data.

The following sequence is required for this erratum to occur:

- 1. The address of interest is in the cache.

- One of the following data cache maintenance operations that affects the same cache line as the wanted address is performed.

- DCCIMVAC.

- DCCISW.

- DCIMVAC.

- DCISW.

- 3. A write-through store is performed to the wanted address

- 4. A line-fill to the same cache line of the wanted address occurs for any reason.

There must be no DSB or DMB between the maintenance operation and the store.

ES0596 - Rev 8 page 8/46

If this sequence occurs and certain very specific internal timing conditions are met, then the store data is not merged into the line-fill, but it writes out to the bus. After this has occurred, the line-fill buffer or cache contains stale data.

A subsequent load to the same address of the store might observe stale data in the cache.

#### Workaround

A DMB must be inserted between the cache maintenance operation and the store.

It is expected that all code should already have this DMB or DSB because there is no implicit ordering between cache maintenance operations and stores.

## 2.2 System

#### 2.2.1 Boundary scan, PC10 and PC11 are not controllable on TFBGA100 package

#### **Description**

At board level, when using boundary scan on TFBGA 100 PC10 and PC11 must not be used as they are not controllable, resulting in indeterminate behavior.

#### Workaround

Mask (ignore) the TFBGA 100 PC10 and PC11 signals when performing boundary scan.

## 2.2.2 Only one configuration available using MCE on the FMC interface

#### **Description**

When using the encryption (MCE) on the FMC interface, only one configuration is available. Each memory connected to the FMC interface inherits the MCE region programming.

#### Workaround

None.

#### 2.2.3 Data read might be corrupted on FMC NOR

#### **Description**

Data read might be corrupted when the write FIFO is disabled.

#### Workaround

Enable the write FIFO using FMC\_WRITE\_FIFO\_ENABLE variable in the HAL.

## 2.2.4 Incorrect backup domain reset

#### Description

The backup domain reset may be missed upon a backup domain power-on following a VBAT power-off in VBAT mode, if the VBAT voltage drops during the power-off phase hitting a window, which is a few mV wide before it starts to rise again. This window is located in the range between 100 mV and 700 mV, the exact position depending mainly on the device and on the temperature.

The missed reset results in unpredictable values of the backup domain registers, which may lead to a wrong device behavior, such as driving the LSCO output pin on PA2, raising an unexpected tamper event preventing the access to SRAM2 and PKA, or influencing any of the backup domain functions.

#### Workaround

Apply one of the following measures to avoid an incorrect backup domain reset:

ES0596 - Rev 8 page 9/46

- Before performing a new power-on,let the VBAT supply voltage fall to a level below 100 mV for more than 200 ms.

- If none of the previous workarounds can be applied, and the boot follows a backup domain power-on reset, erase the backup domain by software. In order to discriminate the backup domain power-on reset from a power-on reset, at least one backup register (called, for example, Backup Test Register) must be previously programmed with a BKP\_REG\_VAL value containing 16 bits set and 16 bits cleared. The robustness of this workaround can be significantly improved by using a CRC rather than registers, since the registers are subject to backup domain reset.

The workaround consists in calculating the CRC of the backup domain registers, RCC\_BDCR and RTC/ TAMP registers, excluding the bits modified by hardware. The CRC result can be stored in the backup register, instead of a fixed BKP\_REG\_VAL value. The CRC result needs to be updated for each modification of values covered by the CRC, for example when the CRC peripheral is used.

Insert the following software sequence at the very beginning of the boot code:

- 1. Check if the BORRSTF flag of the RCC RSR register is set (the reset is caused by a power-on).

- 2. If it is set, check that the Backup Test Register content is different from BKP\_REG\_VAL, or that the new CRC calculated value is different from stored results, depending on the chosen workaround implementation.

- 3. If this is the case and if no tamper flag is set (when the tamper detection is enabled), the reset is caused by a backup domain power-on. Then apply the following sequence:

- a. Enable backup domain access by setting the DBP bit of the PWR\_DBPCR register.

- b. Reset the backup domain by applying the following sequence:

- i. Write 0x00010000 to the RCC\_BDCR register, which sets the VSWRST bit and clears the other register bits that may not be cleared.

- ii. In order to make the reset long enough, read the RCC\_BDCR register.

- iii. Write 0x00000000 to the RCC\_BDCR register to clear the VSWRST bit.

- c. Clear the BORRSTF flag by setting the RMVF bit of the RCC\_RSR register.

## 2.2.5 SRAM1 AHB limitation if the device is not in OPEN state

## **Description**

During the RSS processing the SRAM1 AHB is reserved and no longer accessible if the product state is not equal to OPEN. (This limitation only affects products using SFSP version 1.1.0.)

#### Workaround

None.

## 2.2.6 LSE crystal oscillator may be disturbed by transitions on PC13

## **Description**

On LQFP and UFQFPN packages, the LSE crystal oscillator clock frequency can be incorrect when PC13 is toggling as an input or output (for example when used for RTC\_OUT1).

The external clock input (LSE bypass) is not impacted by this limitation.

WLCSP and UFBGA packages are not impacted by this limitation.

#### Workaround

None.

Avoid toggling PC13 when LSE is used on LQFP and UFQFPN packages.

## 2.2.7 Secure Firmware Install (SFI) is not supported

#### **Description**

Secure Firmware Install (SFI) is not supported. (This limitation only affects products using SFSP version 1.1.0.)

ES0596 - Rev 8 page 10/46

None

## 2.2.8 Debug authentication timeout with force download feature

#### **Description**

A timeout is systematically observed when starting the "force download" feature using the STM3CubeProgrammer command-line. (This limitation only affects products using SFSP version 1.1.0.)

#### Workaround

None.

## 2.2.9 RSSLIB: AHB SRAM2 clock is enabled in closed and locked product states

## **Description**

During the RSS execution AHB SRAM2 clock is enabled, and kept enabled after leaving RSS. (This limitation only affects products using SFSP version 1.1.0.)

#### Workaround

None.

## 2.2.10 Backup domain erased upon reset when STiRoT boot is active and an RTC clock other than LSI is selected

## **Description**

Selecting STiRoT boot forces the RTC/TAMP clock source to LSI. If the software application then selects a clock source other than LSI, this results in erasing the backup domain upon reset.

#### Workaround

After the reset, restore the backup domain data and the RTC clock source.

### 2.2.11 Tampers are not usable with STiRoT

#### Description

When the application requires the tamper functionality, STiRoT cannot be used.

#### Workaround

Configure the device to use the proprietary boot entry (OEMiRoT). Taking into account errata: Backup domain erased upon reset when STiRoT boot is active and an RTC clock other than LSI is selected

#### 2.2.12 RSS Boot fails if a tamper event arises during startup

#### **Description**

In PRODUCT\_STATE different than Open, If a tamper event arises during the startup, the execution remains in an infinite loop, failing to jump to the user application code.

#### Workaround

In this situation, the only way to quit the infinite loop and restart the device is to remove all power supplies (also on the VBAT pin), then power the device back on.

ES0596 - Rev 8 page 11/46

## 2.2.13 PRODUCT\_STATE different than Open, RSS force its tamper configuration at each boot

#### **Description**

When PRODUCT\_STATE is Provisioning, Closed or Locked each boot goes through RSS.

RSS activates itamp9 and 15 and sets every activated tamper to confirmed mode.

#### Workaround

The application must set its expected tamper configuration after each boot.

#### 2.2.14 During RSS execution, any error resets the backup registers and device secrets

#### **Description**

When PRODUCT\_STATE is Provisioning, Closed or Locked each boot goes through RSS.

In RSS, any error acts as a tamper by setting BKERASE bit in the TAMP\_CR2 register. The consequence is that the backup registers and device secrets are erased.

Such errors are not expected to occur except in noisy environments.

#### Workaround

None.

## 2.2.15 I/O compensation could alter duty-cycle of high-frequency output signal

#### Description

I/O compensation might create skewed output rise and fall times.

The issue occurs when the I/O compensation is enabled and linked to the PCB the memory and the load seen by the XSPI interface. This issue causes a clock output signal that is outside the recommended duty cycle (for example, 45%-55%).

When using I/O compensation enabled in automatic mode, this issue might also increase the output signal jitter when at low and high temperature.

#### Workaround

Always use the compensation values obtained at boot time, if the calibration is performed at ambient temperature (around 30°C).

If clock rise/fall skew or jitter issues occur, overwrite the SBS\_CCSWVALR register with the compensation boot-time values from btfields XSPI1/2\_PSRC[3:0] and XSPI1/2\_NSRC[3:0] in the SBS\_CCVALR register, modified as follows:

- XSPI1/2\_SW\_PSRC[3:0] becomes XSPI1/2\_PSRC[3:0] boot-time value -2

- XSPI1/2\_SW\_NSRC[3:0] becomes XSPI1/2\_NSRC[3:0] boot-time value +2

#### Then:

- 1. Set bit XSPI1/2\_COMP\_CODESEL=1 in the SBS\_CCCSR register, in order to use the values from the SBS\_CCSWVALR register.

- 2. Enable the compensation cell (XSPI1/2\_COMP\_EN=1 in the SBS\_CCCSR register).

### 2.2.16 Manual forcing of OTG\_FS host or device mode when not possible via ID pin (PM13)

#### Description

When using the USB Full-Speed (FS) Host mode with manual host mode forcing (without ID pin), the internal pull-down resistors on the USB data lines (DP and DM) are disabled (incorrect behavior) if the ID pin is in high state.

When using the USB FS Device mode with manual device mode forcing, the internal pull-down resistors on the USB data lines (DP and DM) are enabled (incorrect behavior) if the ID pin is in low state.

The pulldown resistors are integrated. But they are not automatically set for both cases when ID pin is set high for host mode case and when ID pin is set low for device mode case.

ES0596 - Rev 8 page 12/46

The PM13 pin must be used only in ID mode, for no other functions including GPIO.

The ID pin should be set to a low state for host mode and set to a high state for device mode.

### 2.3 FMC

## 2.3.1 Dummy read cycles inserted when reading synchronous memories

#### Description

When performing a burst read access from a synchronous memory, two dummy read accesses are performed at the end of the burst cycle whatever the type of burst access.

The extra data values read are not used by the FMC and there is no functional failure.

#### Workaround

None.

## 2.3.2 Wrong data read from a busy NAND memory

#### Description

When a read command is issued to the NAND memory, the R/B signal gets activated upon the de-assertion of the chip select. If a read transaction is pending, the NAND controller might not detect the R/B signal (connected to NWAIT) previously asserted and sample a wrong data. This problem occurs only when the MEMSET timing is configured to 0x00 or when ATTHOLD timing is configured to 0x00 or 0x01.

## Workaround

Either configure MEMSET timing to a value greater than 0x00 or ATTHOLD timing to a value greater than 0x01.

## 2.3.3 Unsupported read access with unaligned address

## **Description**

Read access with unaligned address, such as a half-word read access starting at odd address, is not supported.

## Workaround

Compile the software that accesses the fmc region with a compiler option that ensures data alignment, such as – no\_unaligned\_access.

## 2.3.4 CTB1, CTB2, MODE[2:0] write-only bitfields in FMC\_SDCMR incorrectly described as read-write

## Description

The CTB1, CTB2, and MODE[2:0] bitfields in FMC\_SDCMR are write-only, and always read as zero. Some versions of the device reference manual incorrectly indicate that these bitfields are read-write.

This is a documentation error rather than a device limitation.

## Workaround

None.

ES0596 - Rev 8 page 13/46

## 2.3.5 Duty cycle variation on memory clock while accessing PSRAM in continuous clock mode

#### **Description**

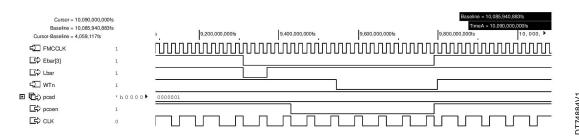

With a clock division of 3 (CLKDIV = 0x02), the FMC continuous clock duty cycle, which is 2/3 high and 1/3 low during read or write transfers, changes to 1/3 high and 2/3 low on the first clock after transfer. The duty cycle change creates a narrow pulse after the data transfer, as illustrated by Figure 1 below.

Figure 1. RTL simulation timing diagram

#### Workaround

The narrow pulse after a data transfer is not expected to cause a timing violation for PSRAM, as CLK may be off and irrelevant after the transfer is complete.

In case PSRAM needs a continuous clock and tCLK<sub>min</sub> is not fullfilled, the clock division must be set to 4 (CLKDIV = 0x03).

## 2.4 XSPI

## 2.4.1 Memory-mapped write error response when DQS output is disabled

## **Description**

If the DQSE control bit of the XSPI\_WCCR register is cleared for memories without DQS pin, it results in an error response for every memory-mapped write request.

#### Workaround

When doing memory-mapped writes, set the DQSE bit of the XSPI\_WCCR register, even for memories that have no DQS pin.

#### 2.4.2 Deadlock can occur under certain conditions

### **Description**

A deadlock can occur when all the following conditions are met:

- The product communicates through an I/O manager in multiplexed mode with an single external memory or an external combo featuring two memories, directly or through a high-speed interface.

- The external memory(ies) is(are) accessed in indirect mode or memory-mapped mode.

The deadlock can happen when the two following conditions occur at the same time:

- The Extended-SPI interface that currently owns the external bus (for example XSPI1) waits for a transfer to

occur with the external memory, to complete its transfer on the internal interconnect matrix bus.

- A data transfer request on the internal interconnect matrix bus arrives to the other Extended-SPI interface (for example XSPI2).

This leads to an ownership conflict where:

- XSPI2 cannot get ownership of the external bus which is currently in use by XSPI1.

- XSPI1 cannot get ownership of the internal interconnect matrix bus which is currently in use by XSPI2.

ES0596 - Rev 8 page 14/46

Apply one of the following measures:

- If any of the features generating automatic transfer split (MAXTRAN, REFRESH, CSBOUND, TIMEOUT) is set, XSPI1 splits its transfer at some point in time, releasing the bus. XSPI2 can then process its data, and when XSPI1 gets ownership back again, it resumes its transfer thanks to its embedded capability to restart at the address following the last address accessed. In this case, the deadlock is resolved. Limitation of the workaround: The automatic resume of the transfer does not work with certain flash memories in write direction only. These memories require an extra "write enable" command before resuming a write transfer. This "write enable" command is not generated by the XSPI.

- The application must ensure that it has sufficient room left in the XSPI internal FIFO for each and every transfer before launching it. The internal interconnect matrix bus activity no longer depends on what happens on external bus side, and the deadlock condition is avoided.

## 2.4.3 Memory wrap instruction not enabled when DQS is disabled

#### Description

Memory wrap instruction (as configured in the XSPI\_WPxxx registers) is not generated when DQS is disabled. The memory wrap instruction is replaced by two regular successive read instructions to ensure the correct data ordering: this split has very limited impact on performance.

#### Workaround

None.

## 2.4.4 Deadlock or write-data corruption after spurious write to a misaligned address in XSPI\_AR register

#### **Description**

Upon writing a misaligned address to XSPI\_AR just before switching to memory-mapped mode (without first triggering the indirect write operation), with the XSPI configured as follows:

- FMODE = 00 in XSPI\_CR (indirect write mode)

- DQSE = 1 in XSPI CCR (DQS active)

then, the XSPI may be deadlocked on the first memory-mapped request or the first memory-mapped write to memory (and any sequential writes after it) may be corrupted.

An address is misaligned if the address is:

- Odd and the XSPI is configured to send two bytes of data to the memory every cycle (octal-DTR mode or dual-quad-DTR mode), or

- Not a multiple of four when the XSPI is configured to send four bytes of data to the memory (16-bit DTR mode or dual-octal DTR mode).

If the XSPI\_AR register is reprogrammed with an aligned address (without triggering the indirect write between the two writes to XSPI register), the data sent to the memory during the indirect write operation are also corrupted.

## Workaround

None.

## 2.4.5 XSPI deadlock or RAM content corrupted on CSBOUND split during prefetch, when DQS is disabled

#### Description

Depending on the XSPI configuration and sequence of operations, XSPI may be deadlocked after an abort or the RAM content corrupted when a REFRESH, TIMEOUT or MAXTRAN event occurs.

ES0596 - Rev 8 page 15/46

When the XSPI is configured as follows:

- 16-bit DTR mode or dual-octal DTR mode enabled

- DQS input disabled (DQSE bit cleared into XSPI CCR register)

and the following sequence occurs:

- 1. The last byte is read from the AMBA interface at an address that is 65-72 bytes before a CSBOUND split.

- 2. There are no more memory-mapped requests (or no more reads from XSPI\_DR register in indirect read mode) for long enough that the prefetch mechanism fills up the FIFO.

then, the issue is encountered if either of the two events occurs:

- An abort is requested before another memory-mapped request is issued.

In such case, XSPI becomes thoroughly deadlocked, and only a reset enables to recover from deadlock.

- No new memory-mapped requests are issued for so long that the command to the memory can be

interrupted (chip select released) due to a REFRESH, TIMEOUT or MAXTRAN event.

In such case, the chip select is not released and the RAM content may get corrupted (for instance if no

refresh is performed).

#### Workaround

Use the DQS output of the memory (by setting the DQSE bit of the XSPI\_CCR register) when using 16-bit memories or octal memories in dual-octal mode.

## 2.4.6 Read-modify-write operation does not clear the MSEL bit

#### **Description**

When the MSEL bit of the XSPI\_CR register is set, it remains set even if the software attempts to clear it by performing a read-modify-write operation.

#### Workaround

To clear the MSEL bit, clear in a single write access bit 7 and bit 30 of the XSPI\_CR register, otherwise, the MSEL bit remains set.

#### 2.4.7 CALMAX bit not set when the PHY reaches the DLL maximum value

## **Description**

The CALMAX bit (bit 31 of the XSPI\_CALFCR register) is expected to be set when the PHY reaches the maximum value of the DLL. However, this bit is wrongly cleared at the end of the calibration phase, meaning that it is always read at 0 when the calibration is complete, even if the maximum value of the calibration has been reached.

#### Workaround

None.

## 2.4.8 Read data corruption when a wrap transaction is followed by a linear read to the same MSB address

#### **Description**

If a wrap transaction is followed by a linear read having the same MSB start address as the wrap (), then the linear read is wrongly considered as a sequential transaction to the previous one, taking back the prefetched data and causing data corruption.

Notice that for a wrap transaction, the prefetch starts after the last address of the wrap window.

ES0596 - Rev 8 page 16/46

As prefetch cannot be disabled, there is no workaround. However, the issue is seldom encountered since wrap operations are mostly initiated by the internal cache to refresh its cacheline. All the other masters must avoid retrieving data by using a linear read access to the same MSB address as the wrap, which has been just completed.

## 2.4.9 Transactions are limited to 8 Mbytes in OctaRAM<sup>™</sup> memories

#### Description

When the controller is configured in Macronix OctaRAM<sup>™</sup> mode, by setting the MTYP[2:0] bitfield of the XSPI\_DCR1 register to 011, only 13 bits of row address are decoded and sent to the memory, meaning that only 8 K of 1-Kbyte blocks can be accessed (8 Mbytes).

#### Workaround

None.

This limitation is not present for PSRAMs or HyperRAM<sup>™</sup> memories.

## 2.4.10 Variable latency is not supported when a refresh collision occurs during a write access to some OctaRAM™ memories

## **Description**

When the memory type (MTYP[2:0] bitfield of the XSPI\_CR register) is configured to 0b011 to target an OctaRAM<sup>™</sup> memory, the host controller does not support the variable latency requested by the external memory if a refresh collision occurs during the write access. For example, some OctaRAM<sup>™</sup> memories, such as ISSI memories, request extra latency cycles for write accesses during refresh collision. In this case, the controller does not sample the DQS input signal during the instruction phase, and cannot detect the extra latency requested by the external memory for the refresh operation. This results in data corruption.

Some OctaRAM<sup>™</sup> memories do not request any additional latency for write access during refresh cycles. It is required only when the refresh occurs during a read access. In this case, no issue can be observed.

#### Workaround

When the application targets an OctaRAM<sup>™</sup> memory that requests extra latency cycles for write access during refresh collision, force the fixed latency mode in the configuration register of the external memory. There is no constraint about read access, since both variable and fixed latency modes are supported.

## 2.4.11 In automatic status-polling and multiplexed modes, the controller does not request the port if less than two bytes are sent per cycle when XSPI\_DLR is cleared

#### **Description**

Due to FIFO RX pointer mismatches, the controller configured in automatic status-polling mode (FMODE[1:0] = 10) may not be able to request the port ownership to serve the status-polling request to the external memory. As a result, the FIFO is wrongly detected full, thus blocking the request from the controller to the I/O manager.

The issue happens in the following conditions:

- The I/O manager is used in multiplexed mode (to connect two controllers sharing the same port).

- The I/O manager is connected to a PHY.

- The controller is configured in automatic status-polling mode.

- Less than two bytes are sent per CLK cycle.

- Data length register (XSPI DLR) is cleared.

ES0596 - Rev 8 page 17/46

Set the XSPI\_DLR to configure the number of bytes to 2 (XSPI\_DLR set to 0x0000 0001), and configure the XSPI polling status mask register (XSPI\_PSMKR) to mask the second dummy byte

## 2.4.12 IO states during dummy cycles phase on write transactions are not in a high impedance state

#### Description

Some reference manual mentions that the controller data IO pins are in high impedance state during the dummy phase in dual-SPI, quadspi, octal mode, and 16-bit mode. This is accurate, but only for read operations. During write transaction, the controller forces the data IO pins as outputs, and sets them to either 0 or 1.

This is a documentation issue rather than a product limitation.

#### Workaround

None.

### 2.5 XSPIM

#### 2.5.1 Certain quad memories may be reset during arbitration while in single-SPI mode

#### **Description**

The XSPI I/O manager allows two XSPIs to be mapped on the same I/Os, in which case the XSPIs arbitrate for use of the multiplexed port. This arbitration introduces a glitch on the data lines when the arbitration passes the ownership of the port from one XSPI to the other.

External quad memories, having their asynchronous RESET pin (when selected by default by the memory) multiplexed with an SO data line and operating in single-SPI mode, may be asynchronously reset due to the glitch on the data line when the ownership of the port is transferred.

This problem typically occurs when the memory defaults to operate in single-bit mode and the application reconfigures the memory in quad mode, while arbitrating and transferring the port ownership.

## Workaround

Ensure that the ownership of the port does not change while an XSPI is configuring its memory to operate in quad mode:

- 1. Configure the first memory to quad mode, while clearing MUXEN of XSPIM\_CR.

- 2. Switch the ownership of the port by inverting the MODE bit value in the XSPIM\_CR register (even if a glitch is present on the corresponding data line, the reset is applied to the memory that is not yet configured)

- 3. Configure the second memory to quad mode, while clearing MUXEN of XSPIM CR.

- 4. Write the MODE bit to the correct value and set the MUXEN bit of the XSPIM\_CR register to come back to the multiplexed mode.

## 2.6 SDMMC

## 2.6.1 Command response and receive data end bits not checked

#### Description

The command response and receive data end bits are not checked by the SDMMC. A reception with only a wrong end bit value is not detected. This does not cause a communication failure since the received command response or data is correct.

#### Workaround

None.

ES0596 - Rev 8 page 18/46

## 2.7 ADC

## 2.7.1 New context conversion initiated without waiting for trigger when writing new context in ADC\_JSQR with JQDIS = 0 and JQM = 0

#### **Description**

Once an injected conversion sequence is complete, the queue is consumed and the context changes according to the new ADC\_JSQR parameters stored in the queue. This new context is applied for the next injected sequence of conversions.

However, the programming of the new context in ADC\_JSQR (change of injected trigger selection and/or trigger polarity) may launch the execution of this context without waiting for the trigger if:

- the gueue of context is enabled (JQDIS cleared to 0 in ADC CFGR), and

- the queue is never empty (JQM cleared to 0 in ADC\_CFGR), and

- the injected conversion sequence is complete and no conversion from previous context is ongoing

#### Workaround

Apply one of the following measures:

- Ignore the first conversion.

- Use a queue of context with JQM = 1.

- Use a queue of context with JQM = 0, only change the conversion sequence but never the trigger selection and the polarity.

## 2.7.2 Two consecutive context conversions fail when writing new context in ADC\_JSQR just after previous context completion with JQDIS = 0 and JQM = 0

#### **Description**

When an injected conversion sequence is complete and the queue is consumed, writing a new context in ADC\_JSQR just after the completion of the previous context and with a length longer that the previous context, may cause both contexts to fail. The two contexts are considered as one single context. As an example, if the first context contains element 1 and the second context elements 2 and 3, the first context is consumed followed by elements 2 and 3 and element 1 is not executed.

This issue may happen if:

- the queue of context is enabled (JQDIS cleared to 0 in ADC\_CFGR), and

- the queue is never empty (JQM cleared to 0 in ADC\_CFGR), and

- the length of the new context is longer than the previous one

### Workaround

If possible, synchronize the writing of the new context with the reception of the new trigger.

## 2.7.3 Unexpected regular conversion when two consecutive injected conversions are performed in Dual interleaved mode

## Description

In Dual ADC mode, an unexpected regular conversion may start at the end of the second injected conversion without a regular trigger being received, if the second injected conversion starts exactly at the same time than the end of the first injected conversion. This issue may happen in the following conditions:

- two consecutive injected conversions performed in Interleaved simultaneous mode (DUAL[4:0] of ADC\_CCR = 0b00011), or

- two consecutive injected conversions from master or slave ADC performed in Interleaved mode (DUAL[4:0]of ADC CCR = 0b00111)

ES0596 - Rev 8 page 19/46

- In Interleaved simultaneous injected mode: make sure the time between two injected conversion triggers is longer than the injected conversion time.

- In Interleaved only mode: perform injected conversions from one single ADC (master or slave), making sure the time between two injected triggers is longer than the injected conversion time.

## 2.7.4 ADC\_AWDy\_OUT reset by non-guarded channels

#### Description

ADC\_AWDy\_OUT is set when a guarded conversion of a regular or injected channel is outside the programmed thresholds. It is reset after the end of the next guarded conversion that is inside the programmed thresholds. However, the ADC\_AWDy\_OUT signal is also reset at the end of conversion of non-guarded channels, both regular and injected.

#### Workaround

When ADC\_AWDy\_OUT is enabled, it is recommended to use only the ADC channels that are guarded by a watchdog.

If ADC\_AWDy\_OUT is used with ADC channels that are not guarded by a watchdog, take only ADC\_AWDy\_OUT rising edge into account.

## 2.7.5 Injected data stored in the wrong ADC\_JDRx registers

#### **Description**

When the AHB clock frequency is higher than the ADC clock frequency after the prescaler is applied (ratio > 10), if a JADSTP command is issued to stop the injected conversion (JADSTP bit set to 1 in ADC\_CR register) at the end of an injected conversion, exactly when the data are available, then the injected data are stored in ADC\_JDR1 register instead of ADC\_JDR2/3/4 registers.

#### Workaround

Before setting JADSTP bit, check that the JEOS flag is set in ADC\_ISR register (end of injected channel sequence).

## 2.7.6 ADC slave data may be shifted in Dual regular simultaneous mode

## **Description**

In Dual regular simultaneous mode, ADC slave data may be shifted when all the following conditions are met:

- A read operation is performed by one DMA channel,

- OVRMOD = 0 in ADC\_CFGR register (Overrrun mode enabled).

#### Workaround

Apply one of the following measures:

- Set OVRMOD = 1 in ADC CFGR. This disables ADC DR register FIFO.

- Use two DMA channels to read data: one for slave and one for master.

ES0596 - Rev 8 page 20/46

## 2.8 ADF

## 2.8.1 In LFM mode ADF\_CCK1 clock cannot be selected for SITFx interfaces

## **Description**

In low-frequency master (LFM) mode, the input clock selectors of the SITFx serial interfaces do not allow selecting the ADF\_CCK1 clock. The STIFx clock selector is controlled through the SCKSRC[1:0] bitfield of the corresponding ADF\_SITFxCR register. The following table shows the expected and the actual behavior of the device:

Table 5. SITFx clock selector operation

| SCKSRC[1:0] | Clock selected |          |  |

|-------------|----------------|----------|--|

| 30N3N0[1.0] | Expected       | Actual   |  |

| 00          | ADF_CCK0       | ADF_CCK0 |  |

| 01          | ADF_CCK1       | ADF_CCK0 |  |

| 1x          | Reserved       | Reserved |  |

As in the LFM mode the ADF\_CCK1 cannot be selected and the ADF\_CKIx is disabled, ADF\_CCK0 is the only applicable clock for the SITFx interfaces.

#### Workaround

Always enable the ADF\_CCK0 clock (by setting the CCK0EN bit of the ADF\_CKGCR register) and select it for the SITFx interfaces, even in applications that only use the ADF\_CCK1 clock output on the I/Os.

Note:

As the ADF\_CCK1 and ADF\_CCK0 clocks originate from the same clock source, the use of ADF\_CCK1 for clocking external microphones and ADF\_CCK0 for clocking the SITFx interfaces does not compromise the performance.

### 2.9 PSSI

## 2.9.1 Output mode not usable with both PSSI\_RDY and PSSI\_DE signals enabled

## **Description**

In output mode, when both the PSSI\_RDY and PSSI\_DE signals are enabled (DERDYCFG[2:0] bitfield set to 011, 100, or 111), the PSSI\_DE signal may fail to indicate data validity.

As a result, output mode cannot be used when both PSSI\_RDY and PSSI\_DE signals are enabled.

#### Workaround

None.

## 2.10 GPU2D

## 2.10.1 Occasional writing miss to frame buffer with slow memories

#### Description

The GPU operating slowly due to slow memories may occasionally fail to write isolated single-pixel data to the frame buffer.

## Workaround

None

ES0596 - Rev 8 page 21/46

## 2.11 TIM

## 2.11.1 Unexpected PWM output when using ocref\_clr

### **Description**

In combined PWM mode 1, asymmetric PWM mode 1, or asymmetric PWM mode 2, using ocref\_clr can cause the tim\_ocxrefc output to be unexpectedly re-enabled or disabled. This behavior depends on the timing of when ocref\_clr is activated and deactivated.

#### Workaround

None.

#### 2.12 LPTIM

## 2.12.1 Device may remain stuck in LPTIM interrupt when entering Stop mode

#### Description

This limitation occurs when disabling the low-power timer (LPTIM).

When the user application clears the ENABLE bit in the LPTIM\_CR register within a small time window around one LPTIM interrupt occurrence, then the LPTIM interrupt signal used to wake up the device from Stop mode may be frozen in active state. Consequently, when trying to enter Stop mode, this limitation prevents the device from entering low-power mode and the firmware remains stuck in the LPTIM interrupt routine.

This limitation applies to all Stop modes and to all instances of the LPTIM. Note that the occurrence of this issue is very low.

#### Workaround

In order to disable a low power timer (LPTIMx) peripheral, do not clear its ENABLE bit in its respective LPTIM\_CR register. Instead, reset the whole LPTIMx peripheral via the RCC controller by setting and resetting its respective LPTIMxRST bit in the relevant RCC register.

## 2.12.2 ARRM and CMPM flags are not set when APB clock is slower than kernel clock

#### **Description**

When LPTIM is configured in one shot mode and APB clock is lower than kernel clock, there is a chance that ARRM and CMPM flags are not set at the end of the counting cycle defined by the repetition value REP[7:0]. This issue can only occur when the repetition counter is configured with an odd repetition value.

## Workaround

To avoid this issue, the following formula must be respected:

{ARR, CMP} ≥ KER CLK / (2\* APB CLK),

where APB\_CLK is the LPTIM APB clock frequency, and KER\_CLK is the LPTIM kernel clock frequency. ARR and CMP are expressed in decimal value.

**Example**: The following example illustrates a configuration where the issue can occur:

- APB clock source (MSI) = 1 MHz, kernel clock source (HSI) = 16 MHz

- The repetition counter is set with REP[7:0] = 0x3 (odd value)

The above example is subject to issues, unless the user respects:

$\{CMP, ARR\} \ge 16 MHz / (2 * 1 MHz)$

→ ARR must be ≥ 8 and CMP must be ≥ 8

Note:

REP set to 0x3 means that effective repetition is REP+1 (= 4) but the user must consider the parity of the value loaded in the LPTIM\_RCR register (=3, odd) to assess the risk of issue.

ES0596 - Rev 8 page 22/46

## 2.12.3 Interrupt status flag is cleared by hardware upon writing its corresponding bit in LPTIM\_DIER register

#### **Description**

When any interrupt bit of the LPTIM\_DIER register is modified, the corresponding flag of the LPTIM\_ISR register is cleared by hardware.

#### Workaround

None.

#### 2.13 RTC and TAMP

## 2.13.1 Alarm flag may be repeatedly set when the core is stopped in debug

#### **Description**

When the core is stopped in debug mode, the clock is supplied to subsecond RTC alarm downcounter even when the device is configured to stop the RTC in debug.

As a consequence, when the subsecond counter is used for alarm condition (the MASKSS[3:0] bitfield of the RTC\_ALRMASSR and/or RTC\_ALRMBSSR register set to a non-zero value) and the alarm condition is met just before entering a breakpoint or printf, the ALRAF and/or ALRBF flag of the RTC\_SR register is repeatedly set by hardware during the breakpoint or printf, which makes any attempt to clear the flag(s) ineffective.

#### Workaround

None.

#### 2.14 I2C

## 2.14.1 Wrong data sampling when data setup time (t<sub>SU:DAT</sub>) is shorter than one I2C kernel clock period

#### Description

The I<sup>2</sup>C-bus specification and user manual specify a minimum data setup time (t<sub>SU:DAT</sub>) as:

- 250 ns in Standard mode

- 100 ns in Fast mode

- 50 ns in Fast mode Plus

The device does not correctly sample the  $I^2C$ -bus SDA line when  $t_{SU;DAT}$  is smaller than one I2C kernel clock ( $I^2C$ -bus peripheral clock) period: the previous SDA value is sampled instead of the current one. This can result in a wrong receipt of target address, data byte, or acknowledge bit.

## Workaround

Increase the I2C kernel clock frequency to get I2C kernel clock period within the transmitter minimum data setup time. Alternatively, increase transmitter's minimum data setup time. If the transmitter setup time minimum value corresponds to the minimum value provided in the I<sup>2</sup>C-bus standard, the minimum I2CCLK frequencies are as follows:

- In Standard mode, if the transmitter minimum setup time is 250 ns, the I2CCLK frequency must be at least

4 MHz

- In Fast mode, if the transmitter minimum setup time is 100 ns, the I2CCLK frequency must be at least

- In Fast-mode Plus, if the transmitter minimum setup time is 50 ns, the I2CCLK frequency must be at least 20 MHz.

ES0596 - Rev 8 page 23/46

## 2.14.2 Spurious bus error detection in controller mode

### **Description**

In controller mode, a bus error can be detected spuriously, with the consequence of setting the BERR flag of the I2C\_SR register and generating bus error interrupt if such interrupt is enabled. Detection of bus error has no effect on the I<sup>2</sup>C-bus transfer in controller mode and any such transfer continues normally.

#### Workaround

If a bus error interrupt is generated in controller mode, the BERR flag must be cleared by software. No other action is required and the ongoing transfer can be handled normally.

#### 2.14.3 SDA held low upon SMBus timeout expiry in target mode

#### Description

For the target mode, the SMBus specification defines  $t_{\text{TIMEOUT}}$  (detect clock low timeout) and  $t_{\text{LOW:SEXT}}$  (cumulative clock low extend time) timeouts. When one of them expires while the I2C peripheral in target mode drives SDA low to acknowledge either its address or a data transmitted by the controller, the device is expected to report such an expiry and release the SDA line.

However, although the device duly reports the timeout expiry, it fails to release SDA. This stalls the I<sup>2</sup>C bus and prevents the controller from generating RESTART or STOP condition.

#### Workaround

When a timeout is reported in target mode (TIMEOUT bit of the I2C ISR register is set), apply this sequence:

- 1. Wait until the frame is expected to end.

- Read the STOPF bit of the I2C\_ISR register. If it is low, reset the I2C kernel by clearing the PE bit of the I2C CR1 register.

- 3. Wait for at least three APB clock cycles before enabling again the I2C peripheral.

## 2.15 I3C

## 2.15.1 I3C controller: unexpected read data bytes during a legacy I<sup>2</sup>C read

#### **Description**

Under specific conditions, unexpected data bytes are read during a legacy I<sup>2</sup>C read transfer.

The issue occurs when all the following conditions are met:

- I3C acts as controller

- a legacy I<sup>2</sup>C read message is generated

- the STALLT bit of I3C\_TIMINGR2 register is set to request the SCL clock to be stalled at low level on the 9th T-bit phase of data bytes (also known as ACK/NACK phase)

- instead of releasing the SDA line, the I<sup>2</sup>C target incorrectly drives SDA low on the 9th T-bit phase of the end of read from the I3C controller