## The BlueNRG-2 device limitations

#### Silicon identification

This errata sheet applies to the following STMicroelectronics BlueNRG-2 devices:

**Table 1. Device identification**

| Order code   | Package  | Identification information of the device <sup>(1)</sup> | Device cut |

|--------------|----------|---------------------------------------------------------|------------|

| BlueNRG-232  | VFQFPN32 | 0x00000100                                              | 1.0        |

| BlueNRG-232  | VFQFPN32 | 0x00000112                                              | 1.2        |

| BlueNRG-232S | VFQFPN32 | 0x00000112                                              | 1.2        |

| BlueNRG-248  | VFQFPN48 | 0x00000112                                              | 1.2        |

| BlueNRG-248S | VFQFPN48 | 0x00000112                                              | 1.2        |

| BlueNRG-234  | WLCSP34  | 0x00000112                                              | 1.2        |

<sup>1.</sup> Value as read from register CKGEN\_SOC - DIE\_ID register (0x4090001C)

Note:

For each device limitation the following information are provided:

- Part number affected: which device and cut is affected from the limitation (the devices and cuts not reported are not affected by the limitation)

- Description: limitation description

- Impact: limitation impact

- Workaround: possible workaround if any

#### 1 Limitations

#### 1.1 Reduced operating voltage range when brown-out reset (BOR) is enabled

Part number affected: the BlueNRG-232 cut 1.0.

Description: when brown-out reset (BOR) is enabled the operating voltage of the device is reduced to 2.1-3.6 V.

**Impact:** brown-out reset (BOR) threshold prevents the device from being safely used below 2.1 V. **Workaround:** the application using brown-out reset (BOR) must restrict operating range to 2.1 V.

#### 1.2 Brown-out reset (BOR) is not enabled by default

Part numbers affected: the BlueNRG-232 cut 1.0.

Description: the device brown-out reset (BOR) is not enabled by default.

Impact: brown-out reset (BOR) activation requires a software action.

**Workaround:** brown-out reset (BOR) can be enabled by the software by setting the BOR\_CONFIG=BOR\_ON preprocessor option in STSW-BLUENRG1-DK (BlueNRG-1, BlueNRG-2 software development kit).

#### 1.3 Bit pattern could cause SWD interface not to work

Part numbers affected: the BlueNRG-232 cut 1.0.

**Description:** During debug connection via serial wire debugger (SWD) port, if a specific bit pattern is sent/ received to/from the SWDIO pin, the chip could not answer anymore subsequent SWD requests, thus breaking the connection. The bit pattern represented as 32 bit word is 0x39E6xxxx.

**Impact:** using serial wire debugger (SWD) during development and/or production to program the Flash memory can cause some issues if the Flash memory image contains a particular pattern.

Workaround: none.

#### 1.4 Extended packet length limitation

Part numbers affected: the BlueNRG-232 cut 1.0.

**Description:** the extended packet length for test mode packets does not work. User mode packets are not impacted.

Impact: The extended data length feature cannot be certified.

Workaround: none.

#### 1.5 Aux ADC end of calibration interrupt flag cannot be cleared

Part numbers affected: the BlueNRG-232 cut 1.0.

**Description:** the ADC end of calibration interrupt flag cannot be cleared, so it cannot be used. STATUS register includes end of calibration information in bit 2.

**Impact:** no specific issue, since the interrupt of end of calibration does not have a practical use in the real application scenario.

**Workaround:** since the end of calibration bit cannot be used, keep the interrupt mask bit associated disabled. There is no interest in such bit.

#### 1.6 ADC WDOG status flag / interrupt cannot be cleared

Part numbers affected: the BlueNRG-232 cut 1.0.

**Description:** Aux ADC WDOG status flag / interrupt cannot be cleared.

Impact: Aux ADC WDOG IRQ is not usable.

Workaround: none.

#### 1.7 ADC does not work properly when a 32 MHz system clock is being used

**Part numbers affected:** the BlueNRG-232 cut 1.0, cut 1.2, BlueNRG-232S cut 1.2, BlueNRG-234 cut 1.2, BlueNRG-248 cut 1.2, and the BlueNRG-248S cut 1.2.

ES0436 - Rev 4 page 2/7

Description: ADC IP does not work properly with a system clock at 32 MHz.

Impact: ADC cannot be used with a system clock at 32 MHz.

**Workaround:** the application, using a 32 MHz quartz and accessing ADC, should configure system clock to 16 MHz.

#### 1.8 ADC SNR degradation

Part numbers affected: the BlueNRG-232 cut 1.0.

Description: ADC SNR may be randomly degraded depending on ADC clock generator start-up.

Impact: SNR degradation is in the range of 6 dB, therefore the effective number of bit of the ADC is reduced by 1 bit

Workaround: in case of static signal, multiple acquisitions and averaging allow ADC accuracy to be recovered.

#### 1.9 ADC unwanted aliased signal after the decimation filter

Part numbers affected: the BlueNRG-232 cut 1.0, cut 1.2, BlueNRG-232S cut 1.2, BlueNRG-234 cut 1.2, BlueNRG-248 cut 1.2, and the BlueNRG-248S cut 1.2.

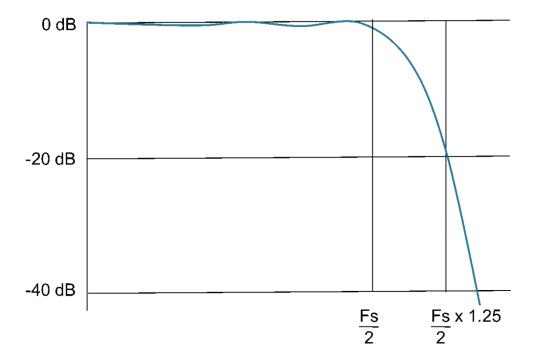

**Description:** the bandwidth of the anti-aliasing filter is slightly broader with respect to the signal bandwidth, potentially thus generating unwanted aliased signal after the decimation filter.

**Impact:** When a pure sine wave, generated in the [Fs/2; 1.25\*Fs/2] range, is being sampled, user can notice an attenuated aliased sine wave in the [0.75\*Fs/2; Fs/2] range.

Figure 1. Interpolation filter frequency response

In case of waveform acquisition, especially when audio speech and music is caught, no further degradation has been identified.

F<sub>s</sub> is the sampling frequency on the output of the downsampling filter, described as ADC data rate in the datasheet.

**Workaround:** by choosing an appropriate oversampling factor (OSR), so that maximum frequency of the sampled signal is lower than Fs/2, aliasing may be avoided.

### 1.10 Incorrect system ROM table detected by the debug connection

Part numbers affected: the BlueNRG-232 cut 1.0.

ES0436 - Rev 4 page 3/7

**Description:** system ROM table address is incorrect and prevents a proper recognition as an ST device when connecting to a debugger.

Impact: the debug connection may work incorrectly and the part is not recognized as an ST device.

Workaround: none.

# 1.11 Unexpected short glitch up to 0 Volt on some DIO during the wakeup of the system

Part numbers affected: the BlueNRG-248 cut 1.2 and the BlueNRG-248S cut 1.2.

**Description**: Depending on sleep mode timing defined, a glitch to 0 Volt could be observed on DIO21, DIO22, DIO23, DIO24, DIO24, DIO25 when system wakeup.

Impact: Any device connected to DIO21, DIO22, DIO23, DIO24, DIO24, DIO25 can be triggered for an unwanted operation.

Workaround: none.

ES0436 - Rev 4 page 4/7

## **Revision history**

Table 2. Document revision history

| Date        | Version | Changes                                                                                              |

|-------------|---------|------------------------------------------------------------------------------------------------------|

| 28-Jun-2018 | 1       | Initial release.                                                                                     |

| 27-Apr-2020 | 2       | Updated Table 1. Device identification.                                                              |

|             |         | Updated Section 1: Limitations with all sub-sections with reference to the involved cuts.            |

| 04-Oct-2021 | 3       | Added Section 1.11: Unexpected short glitch up to 0 Volt on some DIO during the wakeup of the system |

| 27-Jan-2025 | 4       | Added references to new BlueNRG-232S and BlueNRG-248S.                                               |

ES0436 - Rev 4 page 5/7

## **Contents**

| 1   | Limitations |                                                                                  |   |

|-----|-------------|----------------------------------------------------------------------------------|---|

|     | 1.1         | Reduced operating voltage range when brown-out reset (BOR) is enabled            | 2 |

|     | 1.2         | Brown-out reset (BOR) is not enabled by default                                  | 2 |

|     | 1.3         | Bit pattern could cause SWD interface not to work                                | 2 |

|     | 1.4         | Extended packet length limitation                                                | 2 |

|     | 1.5         | Aux ADC end of calibration interrupt flag cannot be cleared                      | 2 |

|     | 1.6         | ADC WDOG status flag / interrupt cannot be cleared                               | 2 |

|     | 1.7         | ADC does not work properly when a 32 MHz system clock is being used              | 2 |

|     | 1.8         | ADC SNR degradation                                                              | 3 |

|     | 1.9         | ADC unwanted aliased signal after the decimation filter                          | 3 |

|     | 1.10        | Incorrect system ROM table detected by the debug connection                      | 3 |

|     | 1.11        | Unexpected short glitch up to 0 Volt on some DIO during the wakeup of the system | 4 |

| Rev | vision      | history                                                                          | 5 |

ES0436 - Rev 4 page 6/7

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

ES0436 - Rev 4 page 7/7