# STM32H742xI/G, STM32H743xI/G STM32H750xB, STM32H753xI

Errata sheet

## STM32H742xI/G, STM32H743xI/G, STM32H750xB, STM32H753xI device errata

## **Applicability**

This document applies to the part numbers of STM32H742xI/G, STM32H743xI/G, STM32H750xB, STM32H753xI devices and the device variants as stated in this page.

It gives a summary and a description of the device errata, with respect to the device datasheet and reference manual RM0433. Deviation of the real device behavior from the intended device behavior is considered to be a device limitation. Deviation of the description in the reference manual or the datasheet from the intended device behavior is considered to be a documentation erratum. The term "errata" applies both to limitations and documentation errata.

**Table 1. Device summary**

| Reference     | Part numbers                                                                                                                                               |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STM32H742xI/G | STM32H742VI, STM32H742ZI, STM32H742II, STM32H742BI, STM32H742XI, STM32H742AI, STM32H742VG, STM32H742ZG, STM32H742IG, STM32H742BG, STM32H742XG, STM32H742AG |

| STM32H743xI/G | STM32H743VI, STM32H743ZI, STM32H743II, STM32H743BI, STM32H743XI, STM32H743AI, STM32H743VG, STM32H743ZG, STM32H743IG, STM32H743BG, STM32H743XG, STM32H743AG |

| STM32H750xB   | STM32H750VB, STM32H750IB, STM32H750XB, STM32H750ZB                                                                                                         |

| STM32H753xI   | STM32H753VI, STM32H753ZI, STM32H753II, STM32H753BI, STM32H753XI, STM32H753AI                                                                               |

Table 2. Device variants

| Reference                                                 | Silicon revision codes        |                       |  |  |  |  |  |  |

|-----------------------------------------------------------|-------------------------------|-----------------------|--|--|--|--|--|--|

| Reference                                                 | Device marking <sup>(1)</sup> | REV_ID <sup>(2)</sup> |  |  |  |  |  |  |

|                                                           | Y, W                          | 0x1003                |  |  |  |  |  |  |

| STM32H742xI/G, STM32H743xI/G,<br>STM32H750xB, STM32H753xI | X                             | 0x2001                |  |  |  |  |  |  |

|                                                           | V                             | 0x2003                |  |  |  |  |  |  |

- 1. Refer to the device datasheet for how to identify this code on different types of package.

- 2. REV ID[15:0] bitfield of DBGMCU IDC register.

## Summary of device errata

The following table gives a quick reference to the STM32H742xI/G, STM32H743xI/G, STM32H750xB, STM32H753xI device limitations and their status:

A = limitation present, workaround available

N = limitation present, no workaround available

P = limitation present, partial workaround available

"-" = limitation absent

Applicability of a workaround may depend on specific conditions of target application. Adoption of a workaround may cause restrictions to target application. Workaround for a limitation is deemed partial if it only reduces the rate of occurrence and/or consequences of the limitation, or if it is fully effective for only a subset of instances on the device or in only a subset of operating modes, of the function concerned.

Table 3. Summary of device limitations

|                |         |                                                                                               | Status    |           |   |  |  |  |

|----------------|---------|-----------------------------------------------------------------------------------------------|-----------|-----------|---|--|--|--|

| Function       | Section | Rev.<br>Y,W                                                                                   | Rev.<br>X | Rev.<br>V |   |  |  |  |

|                | 2.1.1   | Data corruption when using data cache configured in write-through                             | Р         | Р         | Р |  |  |  |

|                | 2.1.2   | PLD might perform linefill to address that would generate a MemManage Fault                   | Α         | Α         | Α |  |  |  |

| Arm 32-bit     | 2.1.3   | Software programming errors might not be reported for online MBIST access to the ICACHE       | N         | N         | N |  |  |  |

| Cortex-M7 core | 2.1.4   | ECC error causes data corruption when the data cache error bank registers are locked          | А         | А         | Α |  |  |  |

|                | 2.1.5   | Store after cache invalidate without intervening barrier might cause inconsistent memory view | А         | А         | Α |  |  |  |

|                | 2.1.6   | Cortex®-M7 FPU interrupt not present on NVIC line 81                                          | N         | N         | N |  |  |  |

|                | 2.2.1   | AXI domain locked when watchdog reset limited to CPU1 or CPU2                                 | Α         | Α         | Α |  |  |  |

|                | 2.2.2   | Timer system breaks do not work                                                               | N         | -         | - |  |  |  |

|                | 2.2.3   | Clock recovery system synchronization with USB SOF does not work                              | Α         | -         | - |  |  |  |

|                | 2.2.4   | SysTick external clock is not HCLK/8                                                          | Α         | -         | - |  |  |  |

|                | 2.2.5   | Option byte loading can be done with the user wait-state configuration                        | Α         | -         | - |  |  |  |

|                | 2.2.6   | Flash memory BusFault address register may not be valid when an ECC double error occurs       | Α         | -         | - |  |  |  |

|                | 2.2.7   | Flash ECC address register may not be updated                                                 | N         | -         | - |  |  |  |

|                | 2.2.8   | PCROP-protected areas in flash memory may be unprotected                                      | Α         | -         | - |  |  |  |

| System         | 2.2.9   | Flash memory bank swapping may impact embedded flash memory interface behavior                | N         | -         | - |  |  |  |

|                | 2.2.10  | Reading from AXI SRAM may lead to data read corruption                                        | Α         | -         | - |  |  |  |

|                | 2.2.11  | Clock switching does not work when an LSE failure is detected by CSS                          | Α         | -         | - |  |  |  |

|                | 2.2.12  | RTC stopped when a system reset occurs while the LSI is used as clock source                  | Α         | -         | - |  |  |  |

|                | 2.2.13  | USB OTG_FS PHY drive limited on DP/DM pins                                                    | N         | -         | - |  |  |  |

|                | 2.2.14  | Unexpected leakage current on I/Os when V <sub>IN</sub> higher that V <sub>DD</sub>           | Α         | -         | - |  |  |  |

|                | 2.2.15  | LSE oscillator driving capability selection bits are swapped                                  | Α         | -         | - |  |  |  |

|                | 2.2.16  | HRTIM internal synchronization does not work                                                  | N         | -         | - |  |  |  |

ES0392 - Rev 15 page 2/73

|            |         |                                                                                                               | Status      |           |          |  |  |

|------------|---------|---------------------------------------------------------------------------------------------------------------|-------------|-----------|----------|--|--|

| Function   | Section | Limitation                                                                                                    | Rev.<br>Y,W | Rev.<br>X | Rev<br>V |  |  |

|            | 2.2.17  | Device stalled when two consecutive level regressions occur without accessing from/to backup SRAM             | -           | А         | Α        |  |  |

|            | 2.2.18  | Invalid flash memory CRC                                                                                      | Р           | -         | -        |  |  |

|            | 2.2.19  | GPIO assigned to DAC cannot be used in output mode when the DAC output is connected to on-chip peripheral     | N           | N         | N        |  |  |

|            | 2.2.20  | Unstable LSI when it clocks RTC or CSS on LSE                                                                 | Р           | Р         | Р        |  |  |

|            | 2.2.21  | 480 MHz maximum CPU frequency not available                                                                   | Р           | Р         | Р        |  |  |

|            | 2.2.22  | VDDLDO is not available on TFBGA100 package                                                                   | N           | N         | N        |  |  |

| System     | 2.2.23  | WWDG not functional when $V_{DD}$ is lower than 2.7 V and VOS0 or VOS1 voltage level is selected              | N           | N         | N        |  |  |

|            | 2.2.24  | A tamper event does not erase the backup RAM when the backup RAM clock is disabled                            | Α           | Α         | Α        |  |  |

|            | 2.2.25  | LSE CSS detection occurs even when the LSE CSS is disabled                                                    | Р           | Р         | Р        |  |  |

|            | 2.2.27  | Ethernet MII mode is not available on packages with PC2_C/PC3_C pins                                          | Α           | Α         | Α        |  |  |

|            | 2.2.28  | HASH input data may be corrupted when DMA is used                                                             | Α           | Α         | Α        |  |  |

|            | 2.2.30  | LSE crystal oscillator may be disturbed by transitions on PC13                                                | N           | N         | N        |  |  |

|            | 2.2.29  | DMA2D swap byte feature is not available                                                                      | N           | -         | -        |  |  |

| MDMA       | 2.3.1   | Non-flagged MDMA write attempts to reserved area                                                              | Α           | Α         | Α        |  |  |

| BDMA       | 2.4.1   | BDMA disable failure and error flag omission upon simultaneous transfer error and global flag clear           | Α           | Α         | Α        |  |  |

|            | 2.5.1   | SOFx not asserted when writing into DMAMUX_CFR register                                                       | N           | N         | N        |  |  |

| DMAMUX     | 2.5.2   | OFx not asserted for trigger event coinciding with last DMAMUX request                                        | N           | N         | N        |  |  |

| DIVIAIVIUX | 2.5.3   | OFx not asserted when writing into DMAMUX_RGCFR register                                                      | N           | N         | N        |  |  |

|            | 2.5.4   | Wrong input DMA request routed upon specific DMAMUX_CxCR register write coinciding with synchronization event | Α           | Α         | Α        |  |  |

|            | 2.6.1   | Dummy read cycles inserted when reading synchronous memories                                                  | N           | N         | N        |  |  |

|            | 2.6.2   | Wrong data read from a busy NAND memory                                                                       | Α           | Α         | Α        |  |  |

| FMC        | 2.6.3   | Spurious clock stoppage with continuous clock feature enabled                                                 | Α           | -         | -        |  |  |

|            | 2.6.4   | Unsupported read access with unaligned address                                                                | Р           | Р         | Р        |  |  |

|            | 2.6.5   | Duty cycle variation on memory clock while accessing PSRAM in continuous clock mode                           | Α           | Α         | Α        |  |  |

|            | 2.7.1   | First nibble of data not written after dummy phase                                                            | Α           | -         | -        |  |  |

|            | 2.7.2   | QUADSPI cannot be used in indirect read mode when only data phase is activated                                | Р           | Р         | Р        |  |  |

| OHADODI    | 2.7.3   | QUADSPI hangs when QUADSPI_CCR is cleared                                                                     | Р           | Р         | Р        |  |  |

| QUADSPI    | 2.7.4   | QUADSPI internal timing criticality                                                                           | Α           | Α         | Α        |  |  |

|            | 2.7.5   | Memory-mapped read of last memory byte fails                                                                  | Р           | Р         | Р        |  |  |

|            | 2.7.6   | QUADSPI memory failure when using HCLK quadspi_ker_ck clock as QUADSPI CLK                                    | Α           | Α         | Α        |  |  |

| SDMMC      | 2.8.1   | Busy signal not detected at resume point when suspend command accepted by the card during busy phase          | Α           | -         | -        |  |  |

| 32         | 2.8.2   | Clock stop reported during read wait sequence                                                                 | Α           | -         | -        |  |  |

ES0392 - Rev 15 page 3/73

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 | Status      |      |           |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-----------|--|--|--|

| Function | Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Limitation                                                                                                                                      | Rev.<br>Y,W | Rev. | Rev.<br>V |  |  |  |

|          | 2.8.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Unwanted overrun detection when an AHB error is reported while all bytes have been received                                                     | А           | -    | -         |  |  |  |

| SDMMC    | 2.8.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Consecutive multiple block transfers have to be separated by eight SDMMC bus clocks when started by setting the DTEN bit                        | Α           | -    | -         |  |  |  |

|          | 2.8.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Data 2 line cannot be used to suspend double-data-rate transfers with read wait mode enabled                                                    | Р           | -    | -         |  |  |  |

|          | 2.8.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Command response and receive data end bits not checked                                                                                          | N           | N    | N         |  |  |  |

| 2.9.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | New context conversion initiated without waiting for trigger when writing new context in ADC_JSQR with JQDIS = 0 and JQM = 0                    | Α           | Α    | Α         |  |  |  |

|          | 2.9.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Two consecutive context conversions fail when writing new context in ADC_JSQR just after previous context completion with JQDIS = 0 and JQM = 0 | Α           | А    | Α         |  |  |  |

|          | 2.9.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Unexpected regular conversion when two consecutive injected conversions are performed in Dual interleaved mode                                  | Α           | А    | Α         |  |  |  |

|          | 2.9.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC_AWDy_OUT reset by non-guarded channels                                                                                                      | Α           | Α    | Α         |  |  |  |

|          | 2.9.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Injected data stored in the wrong ADC_JDRx registers                                                                                            | Α           | Α    | Α         |  |  |  |

| ADC      | 2.9.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC slave data may be shifted in Dual regular simultaneous mode                                                                                 | Α           | Α    | Α         |  |  |  |

|          | 2.9.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Conversion overlap might impact the ADC accuracy                                                                                                | Α           | -    | -         |  |  |  |

|          | 2.9.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC3 resolution limited by LSE activity                                                                                                         | Α           | -    | -         |  |  |  |

|          | 2.9.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC maximum sampling rate when V <sub>DDA</sub> is lower than 2 V                                                                               | Α           | -    | -         |  |  |  |

|          | 2.9.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ADC maximum resolution when V <sub>DDA</sub> is higher than 3.3 V                                                                               | Α           | -    | -         |  |  |  |

|          | 2.9.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | First ADC injected conversion in a sequence may be corrupted                                                                                    | Α           | -    | -         |  |  |  |

| _        | 2.9.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Conversion triggered by context queue register update                                                                                           | Α           | Α    | Α         |  |  |  |

|          | 2.9.13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Updated conversion sequence triggered by context queue update                                                                                   | Α           | Α    | Α         |  |  |  |

| DAG      | 2.10.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Invalid DAC channel analog output if the DAC channel MODE bitfield is programmed before DAC initialization                                      | -           | Α    | Α         |  |  |  |

| DAC      | 2.10.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DMA underrun flag not set when an internal trigger is detected on the clock cycle of the DMA request acknowledge                                | N           | N    | N         |  |  |  |

|          | 2.11.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Overshoot on VREFBUF output                                                                                                                     | Α           | Α    | Α         |  |  |  |

| VREFBUF  | 2.9.5 Injected data stored in the wrong ADC_JDRx registers  2.9.6 ADC slave data may be shifted in Dual regular simultaneous mode  2.9.7 Conversion overlap might impact the ADC accuracy  2.9.8 ADC3 resolution limited by LSE activity  2.9.9 ADC maximum sampling rate when VDDA is lower than 2 V  2.9.10 ADC maximum resolution when VDDA is higher than 3.3 V  2.9.11 First ADC injected conversion in a sequence may be corrupted  2.9.12 Conversion triggered by context queue register update  2.9.13 Updated conversion sequence triggered by context queue update  Invalid DAC channel analog output if the DAC channel MODE bittle is programmed before DAC initialization  DMA underrun flag not set when an internal trigger is detected on to clock cycle of the DMA request acknowledge  2.11.1 Overshoot on VREFBUF output  2.11.2 VREFBUF Hold mode cannot be used  2.11.3 VREFBUF trimming code not automatically initialized after reset  DPAMP 2.12.1 OPAMP high-speed mode must not be used  2.13.1 Device stalled when accessing LTDC registers while pixel clock is disabled  2.15.1 Anticipated burst idle period entry and exit  2.16.1 One-pulse mode trigger not detected in master-slave reset + trigge |                                                                                                                                                 |             | N    | N         |  |  |  |

|          | 2.11.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VREFBUF trimming code not automatically initialized after reset                                                                                 | Α           | -    | -         |  |  |  |

| OPAMP    | 2.12.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OPAMP high-speed mode must not be used                                                                                                          | N           | -    | -         |  |  |  |

| LTDC     | 2.13.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 | Α           | Α    | Α         |  |  |  |

| LIDTIM   | 2.15.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Anticipated burst idle period entry and exit                                                                                                    | N           | N    | N         |  |  |  |

| HKIIW    | 2.15.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Delayed idle protection malfunction when IDLESx = 1                                                                                             | N           | N    | N         |  |  |  |

|          | 2.9.11 First ADC injected conversion in a sequence may be corrupted 2.9.12 Conversion triggered by context queue register update 2.9.13 Updated conversion sequence triggered by context queue update  2.10.1 Invalid DAC channel analog output if the DAC channel MODE bitfilis programmed before DAC initialization  2.10.2 DMA underrun flag not set when an internal trigger is detected on clock cycle of the DMA request acknowledge  2.11.1 Overshoot on VREFBUF output  2.11.2 VREFBUF Hold mode cannot be used  2.11.3 VREFBUF trimming code not automatically initialized after reset  AMP 2.12.1 OPAMP high-speed mode must not be used  2.13.1 Device stalled when accessing LTDC registers while pixel clock is disabled  2.15.1 Anticipated burst idle period entry and exit  2.15.2 Delayed idle protection malfunction when IDLESx = 1  One-pulse mode trigger not detected in master-slave reset + trigger configuration                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |             |      | Р         |  |  |  |

| TIM      | 7 16 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 | N           | N    | N         |  |  |  |

|          | 2.16.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Output compare clear not working with external counter reset                                                                                    | Р           | Р    | Р         |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |             |      |           |  |  |  |

| LPTIM    | 2.17.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Device may remain stuck in LPTIM interrupt when entering Stop mode                                                                              | Α           | Α    | Α         |  |  |  |

|          | 2.17.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Device may remain stuck in LPTIM interrupt when clearing event flag                                                                             | Α           | Α    | Α         |  |  |  |

ES0392 - Rev 15 page 4/73

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                        | Status      |      |           |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------|------|-----------|--|--|--|

| Function | Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Limitation                                                                                                             | Rev.<br>Y,W | Rev. | Rev.<br>V |  |  |  |

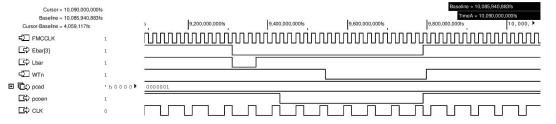

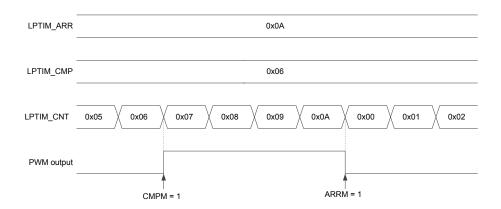

| LPTIM    | 2.17.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LPTIM events and PWM output are delayed by one kernel clock cycle                                                      | Α           | Α    | Α         |  |  |  |

|          | 2.18.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RTC calendar registers are not locked properly                                                                         | Α           | -    | -         |  |  |  |

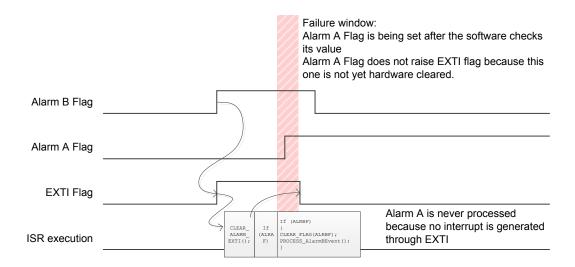

|          | 2.18.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RTC interrupt can be masked by another RTC interrupt                                                                   | Α           | Α    | Α         |  |  |  |

| DTO      | 2.18.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Calendar initialization may fail in case of consecutive INIT mode entry                                                | Α           | Α    | Α         |  |  |  |