Datasheet

## Octal high-side smart power solid-state relay with serial/parallel selectable interface on-chip

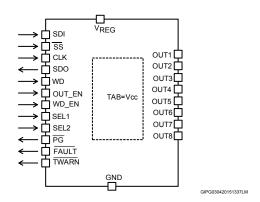

PowerSSO-36 package with exposed pad down (EPD)

# Product status link VNI8200XP VNI8200XP-32

#### **Features**

- Voltage operating range 10.5 V to 36 V

- UVLO with hysteresis

- Output current: 0.7 A or 1.0 A (VNI8200XP or VNI8200XP-32) per channel

- Low supply current in OFF (1 mA) and ON (5.3 mA) state

- 5 V and 3.3 V compatible I/Os

- Selectable interface on logic side SPI or parallel

- 5 MHz SPI (8 or 16-bits) with output enable, daisy chain and MCU freeze detection

- 100 mA DC-DC with integrated boot diode and adjustable output voltage

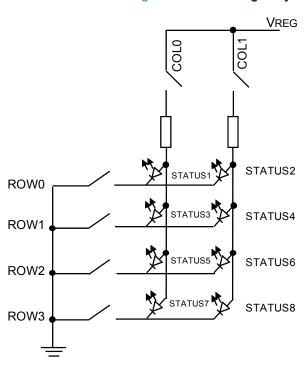

- 4x2 LED matrix for efficient outputs state LEDs driving

- Can drive all type (resistive, capacitive, inductive) of loads

- Per-channel overload and short-circuit protection

- · Per-channel/independent overtemperature protection

- Fast demagnetization of inductive loads (Vout clamp)

- Overvoltage protection (VCC clamping)

- · Loss of GND protection

- Power Good (supply voltage level) diagnostic

- · Common fault open drain output

- IC warning temperature detection

- PowerSSO-36 (10.3 x 10.3 mm) package

- Designed to meet IEC61131-2, IEC61000-4-2, IEC61000-4-4 and IEC61000-4-5

#### **Application**

- Programmable logic control

- · Industrial PC peripheral input/output

- Numerical control machines

#### **Description**

The VNI8200XP and VNI8200XP-32 are monolithic 8-channel drivers, designed in STMicroelectronics™ VIPower™ technology, intended to drive any kind of load with one side connected to ground. Both ICs operates from 10.5 V to 36 V and feature a very low supply current, parallel or 4-wires SPI control interface, 4x2 LED matrix and a micropower step-down switching regulator with peak current control loop mode.

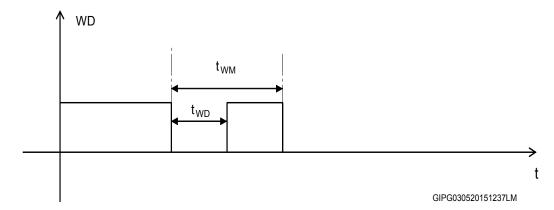

The SPI interface (enabled by SEL2 pin = H) can work up to 5 MHz in 8-bits (SEL1 = L), or 16-bits (SEL1 = H) with parity check and extended diagnostic (DC-DC operation, Case over-temperature, SPI Communication Fail, Power Good) information. In SPI mode the daisy chain is allowed, both the OUT\_EN signal and the MCU freeze detection by whatchdog are available. If enabled (WD\_EN voltage above 25% of VREG), the watchdog circuitry generates an internal reset on expiry of the internal watchdog timer. The watchdog timer reset can be achieved by applying a negative pulse on the WD pin. The whatchdog timer can be programmed by the set voltage on WD\_EN pin.

The internal LED matrix driver circuitry (4 rows, 2 columns) allows the efficient driving of the 8 LEDs reporting the on/off status of each of the 8 outputs. The VREG pin supplies both the logic output buffers and LED matrix. The 100 mA output current capability of the integrated step-down (featuring overload and short-circuit conditions) can be used to supply both the VREG pin and other application components (for example digital isolators or optocouplers).

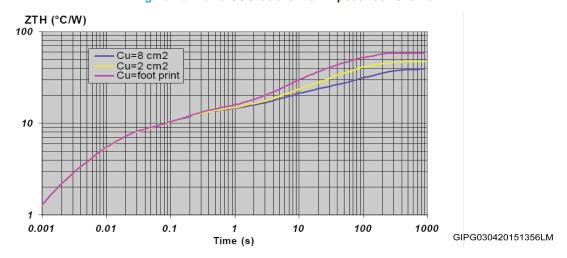

Active per-channel current limitation (0.7 A and 1.0 A for VNI8200XP and VNI8200XP-32, respectively), combined with channel-independent thermal shutdown, protect the circuitry against overload and short circuit. Built-in thermal shutdown protects each channel from over-temperature and overload: each overheated channel automatically turns OFF after its junction temperature triggers the protection threshold ( $T_{CRD}$ ). The channel turns back ON if its junction temperature decreases lower than restart threshold ( $T_{CRD}$ ). An additional case temperature sensor protects the whole chip against over-temperature: if the case temperature triggers the  $T_{CSD}$  threshold then overloaded channels are turned OFF and restart only when case temperature decreased down to the reset threshold ( $T_{CRD}$ ). Non overloaded channels continue to operate normally.

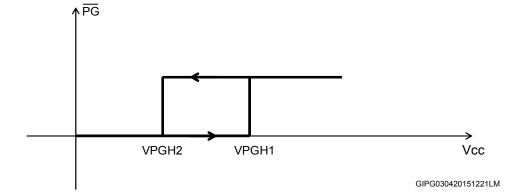

Loss of GND protection guarantees automatic turn off the outputs in case of ground wire break. Dedicated diagnostic pins report the detection of: invalid voltage range on VCC rail ( $\overline{PG}$  pin), case overtemperature (TWARN pin), SPI fault or junction over-temperature ( $\overline{FAULT}$  pin).

DS11044 - Rev 7 page 2/38

## 1 Block diagram

PHASE BOOT DCVDD VREF  $\mathbf{V}_{cc}$ FB DC-DC VREG V<sub>cc</sub> CLAMP PGOOD CONTROL SEL1/IN1 LOGIC **POWER GOOD** WD\_EN/IN2 OUT\_EN/IN3 UNDERVOLTAGE WD/IN4 LOCKOUT SDI/IN5 **x8** CLK/IN6 SPI SS/IN7 **OUTPUT CLAMP** SDO/IN8 SEL2 **FAULT CURRENT LIMITATION** TWARN **▶** OUT<sub>x</sub> **JUNCTION TEMP** ROW0 **DETECTION** ROW1 LED **CASE TEMP** ROW2 **MATRIX DETECTION** ROW3 COL0 GND COL<sub>1</sub>

Figure 1. Block diagram

DS11044 - Rev 7 page 3/38

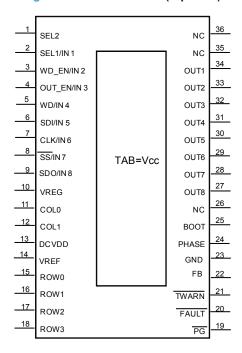

#### 2 Pin connection

Figure 2. Pin connection (top view)

GIPG020420151249LM

**Table 1. Pin description**

| Pin  | Name       | Time                   | Description                                                                              |                                   |

|------|------------|------------------------|------------------------------------------------------------------------------------------|-----------------------------------|

| PIII | Name       | Туре                   | SPI Mode                                                                                 | Parallel Mode                     |

| 1    | SEL2       | Logic input            | SEL2 = H.                                                                                | SEL2 = GND.                       |

| 2    | SEL1/IN1   | Logic input            | SEL1 = L or H selects the SPI 8-bits or 16-bits option.                                  | IN1 = L/H drives off/on the OUT1. |

| 3    | WD_EN/IN2  | Logic/analog<br>input  | WD_EN = H or L enables or disables the watchdog feature.                                 | IN2 = L/H drives off/on the OUT2. |

| 4    | OUT_EN/IN3 | Logic input            | OUT_EN = L or H forces off all OUT <sub>X</sub> or enables the control by SPI.           | IN3 = L/H drives off/on the OUT3. |

| 5    | WD/IN4     | Logic input            | WD is the watchdog input: the internal watchdog counter is cleared on the falling edges. | IN4 = L/H drives off/on the OUT4. |

| 6    | SDI/IN5    | Logic input            | Connected to the MOSI port of the MCU.                                                   | IN5 = L/H drives off/on the OUT5. |

| 7    | CLK/IN6    | Logic input            | Serial clock/channel 6 input.  Connected to the SPI Clock port of the MCU.               | IN6 = L/H drives off/on the OUT6. |

| 8    | SS /IN7    | Logic input            | Connected to the GPIO port of the MCU controlling the SPI chip select.                   | IN7 = L/H drives off/on the OUT7. |

| 9    | SDO/IN8    | Logic input/<br>output | Connected to the MISO port of the MCU.                                                   | IN8 = L/H drives off/on the OUT8. |

| 10   | VREG       | Power supply           | Supply of SPI, Inputs and LED Matrix.                                                    |                                   |

| 11   | COL0       | Open source output     | LED matrix column driver (odd OUT <sub>X</sub> ).                                        |                                   |

| 12   | COL1       | Open source output     | LED matrix column driver (even OUT <sub>X</sub> ).                                       |                                   |

| 13   | DCVDD      | Analog output          | Internally generated DC-DC voltage (to be connected to external 10 nF                    | capacitor).                       |

| 14   | VREF       | Analog output          | Internally generated DC-DC reference voltage (to be connected to extern                  | nal 10 nF capacitor).             |

DS11044 - Rev 7 page 4/38

| ·   |       |                   | Description                                                                                                                                              |                                    |

|-----|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Pin | Name  | Туре              | SPI Mode                                                                                                                                                 | Parallel Mode                      |

| 15  | ROW0  | Open drain output | LED matrix row driver (OUT <sub>1</sub> , OUT <sub>2</sub> ).                                                                                            |                                    |

| 16  | ROW1  | Open drain output | LED matrix row driver (OUT <sub>3</sub> , OUT <sub>4</sub> ).                                                                                            |                                    |

| 17  | ROW2  | Open drain output | LED matrix row driver (OUT <sub>5</sub> , OUT <sub>6</sub> ).                                                                                            |                                    |

| 18  | ROW3  | Open drain output | LED matrix row driver (OUT <sub>7</sub> , OUT <sub>8</sub> ).                                                                                            |                                    |

| 19  | PG    | Open drain output | Connect to VREG by a pull-up resistor. Power Good diagnostic pin is voltage on VCC pin goes below $V_{PGH2}$ .                                           | activated (forced low) when        |

| 20  | FAULT | Open drain output | Connect to VREG by a pull-up resistor. Common fault diagnostic pin junction over-temperature event or SPI communication fault event (paviolation) occur. |                                    |

| 21  | TWARN | Open drain output | Connect to VREG by a pull-up resistor. Case temperature diagnostic a case over-temperature event occurs.                                                 | pin is activated (forced low) when |

| 22  | FB    | Analog input      | Step-down feedback input. Connecting FB pin to DCVDD pin disable: VREG to make the DC-DC supplies 3.3 V. An external resistor divide voltage.            |                                    |

| 23  | GND   |                   | Ground.                                                                                                                                                  |                                    |

| 24  | PHASE | Power output      | Embedded power switch source pin of the DC-DC step-down (buck)                                                                                           | converter.                         |

| 25  | BOOT  | Power output      | Bootstrap voltage of the DC-DC converter. It is used to provide a driv voltage, to power the switch of the step-down regulator.                          | e voltage, higher than the supply  |

| 26  | NC    |                   | Not connected.                                                                                                                                           |                                    |

| 27  | OUT8  | Power output      | Channel 8 power output.                                                                                                                                  |                                    |

| 28  | OUT7  | Power output      | Channel 7 power output.                                                                                                                                  |                                    |

| 29  | OUT6  | Power output      | Channel 6 power output.                                                                                                                                  |                                    |

| 30  | OUT5  | Power output      | Channel 5 power output.                                                                                                                                  |                                    |

| 31  | OUT4  | Power output      | Channel 4 power output.                                                                                                                                  |                                    |

| 32  | OUT3  | Power output      | Channel 3 power output.                                                                                                                                  |                                    |

| 33  | OUT2  | Power output      | Channel 2 power output.                                                                                                                                  |                                    |

| 34  | OUT1  | Power output      | Channel 1 power output.                                                                                                                                  |                                    |

| 35  | NC    |                   | Not connected.                                                                                                                                           |                                    |

| 36  | NC    |                   | Not connected.                                                                                                                                           |                                    |

| TAB | TAB   | Power supply      | Exposed tab, internally connected to V <sub>CC</sub> IC supply rail.                                                                                     |                                    |

DS11044 - Rev 7 page 5/38

## 3 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol                                                    | Parameter                                                                                                     | Value                  | Unit |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------|------|

| V <sub>CC</sub>                                           | Power supply voltage                                                                                          | 45                     | V    |

| -V <sub>CC</sub>                                          | Reverse supply voltage                                                                                        | -0.3                   | V    |

| $V_{REG}$                                                 | Logic supply voltage                                                                                          | -0.3 to +6             | V    |

| V <sub>FAULT</sub> , V <sub>TWARN</sub> , V <sub>PG</sub> | Voltage range on pins TWARN, FAULT, PGOOD                                                                     | -0.3 to +6             | V    |

| V <sub>PHASE</sub>                                        | V <sub>PHASE</sub> voltage                                                                                    | V <sub>CC</sub>        | V    |

| V <sub>BOOT</sub>                                         | Bootstrap voltage                                                                                             | V <sub>PHASE</sub> +6  | V    |

| V <sub>ROW</sub>                                          | Voltage range on ROW pins                                                                                     | -0.3 to +6             | V    |

| V <sub>COL</sub>                                          | Voltage range on COL pins                                                                                     | -0.3 to +6             | V    |

| V <sub>IN</sub>                                           | Voltage level range on logic input pins                                                                       | -0.3 to +6             | V    |

| I <sub>OUT</sub>                                          | Output current (continuous)                                                                                   | Internally limited (1) | Α    |

| I <sub>R</sub>                                            | Reverse output current (per channel)                                                                          | -5                     | Α    |

| I <sub>GND</sub>                                          | DC ground reverse current                                                                                     | -250                   | mA   |

| I <sub>REG</sub>                                          | V <sub>REG</sub> input current                                                                                | -1 to +10              | mA   |

| I <sub>FAULT</sub> , I <sub>TWARN</sub> , I <sub>PG</sub> | Current range on pins TWARN, FAULT, PGOOD                                                                     | -1 to +10              | mA   |

| I <sub>IN</sub>                                           | Input current range                                                                                           | -1 to +10              | mA   |

| 1                                                         | Current range on ROW pins (ROW in ON-state)                                                                   | +20                    | mA   |

| I <sub>ROW</sub>                                          | Current range on ROW pins (ROW in OFF-state)                                                                  | -1 to +10              | mA   |

| I <sub>COL</sub>                                          | Current range on COL pins (COL in ON-state)                                                                   | -10                    | mA   |

| ·COL                                                      | Current range on COL pins (COL in OFF-state)                                                                  | -1 to +10              | mA   |

| V <sub>ESD</sub>                                          | Electrostatic discharge (R = 1.5 k $\Omega$ ; C = 100 pF)                                                     | 2000                   | V    |

| E <sub>AS</sub>                                           | Single pulse avalanche energy per channel not simultaneously $@T_{amb} = 125  ^{\circ}C$ , $I_{OUT} = 0.5  A$ | 3                      | J    |

| P <sub>TOT</sub>                                          | Power dissipation at T <sub>C</sub> = 25 °C                                                                   | Internally limited (1) | W    |

| TJ                                                        | Junction operating temperature                                                                                | Internally limited     | °C   |

| T <sub>STG</sub>                                          | Storage temperature                                                                                           | -55 to 150             | °C   |

<sup>1.</sup> Protection functions are intended to avoid IC damage in fault conditions and are not intended for continuous operation. Continuous and repetitive operation of protection functions may reduce the IC lifetime.

Table 3. Thermal data

| Symbol              | Parameter                           |      | Value <sup>(1)</sup> | Value <sup>(2)</sup> | Unit |

|---------------------|-------------------------------------|------|----------------------|----------------------|------|

| R <sub>th(JC)</sub> | Thermal resistance junction-case    | Max. | 0.7                  | 2                    | °C/W |

| R <sub>th(JA)</sub> | Thermal resistance junction-ambient | Max. | 21.5                 | 15                   | °C/W |

<sup>1.</sup> R<sub>th(JA)</sub> according to JESD51-7; R<sub>th(JC)</sub> intended between die and bottom case surface measured by cold plate as per

DS11044 - Rev 7 page 6/38

<sup>2.</sup> PowerSSO-36 mounted on a four-layer FR4, with 8 cm $^2$  for each layer, Cu thickness = 35  $\mu m$

#### 4 Electrical characteristics

#### 4.1 Power section

10.5 V <  $V_{CC}$  < 36 V; -40 °C <  $T_{J}$  < 125 °C; unless otherwise specified

**Table 4. Power section**

| Symbol                | Parameter                           | Test conditions                                                                            | Min. | Тур. | Max. | Unit |

|-----------------------|-------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>CC</sub>       | Supply voltage                      |                                                                                            | 10.5 |      | 36   | V    |

| V <sub>CC CLAMP</sub> | Clamp on V <sub>CC</sub>            | Current 20 mA                                                                              | 45   | 50   | 52   | V    |

| D                     | On state resistance                 | I <sub>OUT</sub> = 0.5 A @ T <sub>J</sub> = 25 °C                                          |      | 0.11 |      |      |

| R <sub>DS(on)</sub>   | On-state resistance                 | I <sub>OUT</sub> = 0.5 A @ T <sub>J</sub> = 125 °C                                         |      |      | 0.2  | Ω    |

|                       |                                     | All channels in OFF-state, DC-DC = OFF, V <sub>REG</sub> =5 V, SPI inactive <sup>(1)</sup> | 0.65 | 1    | 1.1  | mA   |

| Is                    | V <sub>CC</sub> supply current      | All channels in ON-state, DC-DC = ON, V <sub>REG</sub> = 5 V, SPI active <sup>(2)</sup>    |      | 5.3  |      | mA   |

|                       |                                     | All channels in ON-state, DC-DC = OFF, V <sub>REG</sub> = 5 V, SPI active <sup>(3)</sup>   | 3.5  |      | 5.2  | mA   |

|                       | V auguly august                     | DC-DC = OFF, V <sub>REG</sub> = 5 V, SPI inactive WD_EN = 0                                |      | 200  |      | μA   |

| I <sub>DS</sub>       | V <sub>REG</sub> supply current     | DC/DC = OFF, V <sub>REG</sub> = 5 V, SPI active, WD_EN = V <sub>REG</sub>                  |      | 250  |      | μA   |

| I <sub>LGND</sub>     | Output current at GND disconnection | All pins at 0 V except V <sub>OUTx</sub> = 24 V                                            |      |      | 0.5  | mA   |

| V <sub>OUT(OFF)</sub> | OFF-state output voltage            | V <sub>IN</sub> = 0 V, I <sub>OUT</sub> = 0 A                                              |      |      | 1    | V    |

| I <sub>OUT(OFF)</sub> | OFF-state output current            | V <sub>IN</sub> = V <sub>OUT</sub> = 0 V                                                   | 0    |      | 2    | μA   |

| f <sub>CP</sub>       | Charge pump frequency               | Channel in ON-state (4)                                                                    |      | 1.45 |      | MHz  |

<sup>1.</sup> SS signal high, no communication.

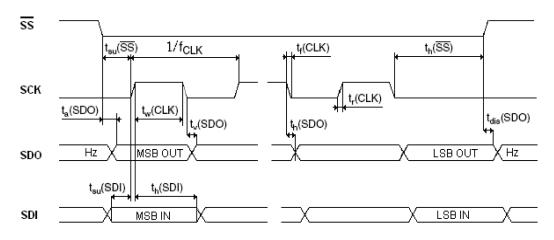

#### 4.2 SPI characteristics

10.5 V < V<sub>CC</sub> < 36 V; 2.7 V < V<sub>REG</sub> < 5 V; -40 < T<sub>j</sub> <125 °C; unless otherwise specified

**Table 5. SPI characteristics**

| Symbol                                        | Parameter                | Test conditions | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|--------------------------|-----------------|------|------|------|------|

| f <sub>CLK</sub>                              | SPI clock frequency      |                 |      |      | 5    | MHz  |

| t <sub>r</sub> (CLK),<br>t <sub>f</sub> (CLK) | SPI clock rise/fall time |                 |      |      | 20   | ns   |

| t <sub>su</sub> (SS)                          | SS setup time            |                 | 120  |      |      | ns   |

| t <sub>h</sub> (SS)                           | SS hold time             |                 | 120  |      |      | ns   |

| t <sub>w</sub> (CLK)                          | CLK high time            |                 | 80   |      |      | ns   |

| t <sub>su</sub> (SDI)                         | Data input setup time    |                 | 100  |      |      | ns   |

DS11044 - Rev 7 page 7/38

<sup>2.</sup> SS signal low, communication ON.

<sup>3.</sup> SS signal low, communication ON.

<sup>4.</sup> To cover EN55022 class A and class B normative.

| Symbol                 | Parameter                     | Test conditions           | Min.                   | Тур. | Max. | Unit |

|------------------------|-------------------------------|---------------------------|------------------------|------|------|------|

| t <sub>h</sub> (SDI)   | Data input hold time          |                           | 100                    |      |      | ns   |

| t <sub>a</sub> (SDO)   | Data output access time       |                           |                        |      | 100  | ns   |

| t <sub>dis</sub> (SDO) | Data output disable time      |                           |                        |      | 200  | ns   |

| t <sub>v</sub> (SDO)   | Data output valid time        |                           |                        |      | 100  | ns   |

| t <sub>h</sub> (SDO)   | Data output hold time         |                           | 0                      |      |      | ns   |

| V                      | Voltage on coriel data output | I <sub>SDO</sub> = 15 mA  | V <sub>REG</sub> - 0.8 |      |      | V    |

| $V_{SDO}$              | Voltage on serial data output | I <sub>SDO</sub> = - 4 mA |                        |      | 0.8  | V    |

Figure 3. Serial timing

GIPG030420151422LM

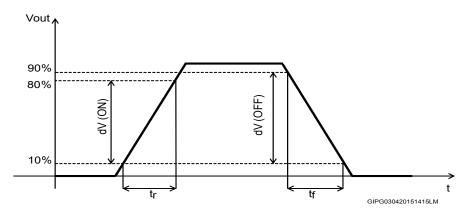

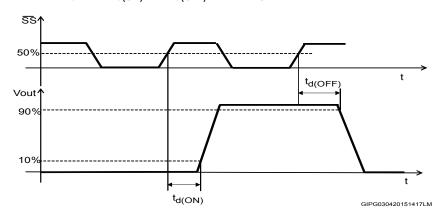

#### 4.3 Switching

$V_{CC}$  = 24 V; -40 °C <  $T_{J}$  < 125 °C

Table 6. Switching

| Symbol                 | Parameter              | Test conditions                                      | Min. | Тур. | Max. | Unit |

|------------------------|------------------------|------------------------------------------------------|------|------|------|------|

| t <sub>d(ON)</sub>     | Turn-on delay time     |                                                      |      | 5    |      | μs   |

| t <sub>r</sub>         | Rise time              | I <sub>OUT</sub> = 0.5 A, resistive load, input rise |      | 5    |      | μs   |

| t <sub>d(OFF)</sub>    | Turn-off delay time    |                                                      |      | 10   |      | μs   |

| t <sub>f</sub>         | Fall time              | time < 0.1 µs                                        |      | 5    |      | μs   |

| dV/dt <sub>(ON)</sub>  | Turn-on voltage slope  |                                                      |      | 3    |      | V/µs |

| dV/dt <sub>(OFF)</sub> | Turn-off voltage slope |                                                      |      | 4    |      | V/µs |

DS11044 - Rev 7 page 8/38

Figure 4. dV/dt(ON) and dV/dt(OFF), time diagram test conditions

Figure 5.  $t_{d(ON)}$  and  $t_{d(OFF)}$ , time diagram test conditions

#### 4.4 Logic inputs

10.5 V <  $V_{CC}$  < 36 V; -40 °C <  $T_{J}$  < 125 °C; unless otherwise specified

Table 7. Logic inputs

| Symbol               | Parameter                | Test conditions       | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------|-----------------------|------|------|------|------|

| V <sub>IL</sub>      | Input low level voltage  |                       |      |      | 0.8  | V    |

| V <sub>IH</sub>      | Input high level voltage |                       | 2.20 |      |      | V    |

| V <sub>I(HYST)</sub> | Input hysteresis voltage |                       |      | 0.15 |      | V    |

| I <sub>IN</sub>      | Input current            | V <sub>IN</sub> = 5 V | 8    |      |      | μA   |

#### 4.5 Protection and diagnostic

10.5 V <  $V_{CC}$  < 36 V; -40 °C <  $T_{J}$  < 125 °C; unless otherwise specified

Table 8. Protection and diagnostic

| Symbol            | Parameter                           | Test conditions | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------------------|-----------------|------|------|------|------|

| V <sub>PGH1</sub> | Power Good diagnostic ON threshold  |                 | 16.5 | 17.5 | 18.4 | V    |

| V <sub>PGH2</sub> | Power Good diagnostic OFF threshold |                 | 15.2 | 16.5 | 17.4 | V    |

DS11044 - Rev 7 page 9/38

| Symbol              | Parameter                                                         | Test conditions                                                       | Min.                | Тур.                | Max.                                  | Unit |

|---------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------|---------------------|---------------------------------------|------|

| V <sub>PGHYS</sub>  | Power Good diagnostic hysteresis                                  |                                                                       |                     | 1                   |                                       | V    |

| V                   | Undervoltage ON protection                                        |                                                                       |                     | 9.5                 | 10                                    | V    |

| $V_{USD}$           | Undervoltage OFF protection                                       |                                                                       | 8.4                 | 9                   |                                       | V    |

| V <sub>USDHYS</sub> | Undervoltage hysteresis                                           |                                                                       | 0.4                 | 0.5                 |                                       | V    |

| V <sub>demag</sub>  | Output voltage at turn-OFF                                        | I <sub>OUT</sub> = 0.5 A; L <sub>LOAD</sub> ≥ 1 mH                    | V <sub>CC</sub> -52 | V <sub>CC</sub> -50 | V <sub>CC</sub> -45                   | V    |

| V <sub>TWARN</sub>  | TWARN pin low-state output voltage                                | I <sub>TWARN</sub> = 3 mA (active condition)                          |                     |                     | 0.6                                   | V    |

| V <sub>FAULT</sub>  | FAULT pin low-state output voltage                                | I <sub>FAULT</sub> = 3 mA (active condition)                          |                     |                     | 0.6                                   | V    |

| $V_{PG}$            | PG pin low-state output voltage                                   | $I_{PG}$ = 3 mA (active condition); $V_{REG}$ = 3.3 V; $V_{CC}$ = 0   |                     |                     | 0.7                                   | V    |

|                     | Maximum DC output                                                 |                                                                       |                     |                     |                                       |      |

|                     | current before limitation (VNI8200XP)                             |                                                                       |                     |                     |                                       |      |

| I <sub>PEAK</sub>   | Maximum DC output                                                 |                                                                       |                     |                     |                                       | A    |

|                     | current before limitation<br>(VNI8200XP-32)                       |                                                                       |                     | 2.2                 |                                       |      |

| I                   | Short-circuit current<br>limitation per channel<br>(VNI8200XP)    |                                                                       | 0.7                 | 1.1                 | 1.7                                   |      |

| I <sub>LIM</sub>    | Short-circuit current<br>limitation per channel<br>(VNI8200XP-32) | R <sub>LOAD</sub> = 0; V <sub>CC</sub> = 24 V; T <sub>J</sub> = 25 °C | 1.1                 | 1.9                 | 2.7                                   | Α    |

| Hyst                | I <sub>LIM</sub> tracking limits                                  | R <sub>LOAD</sub> = 0                                                 |                     | 0.3                 |                                       | Α    |

| I <sub>LFAULT</sub> | FAULT leakage current                                             |                                                                       |                     |                     |                                       |      |

| I <sub>TWARN</sub>  | TWARN leakage current                                             | V <sub>open-drain pin</sub> = 5 V                                     |                     |                     | 2                                     | μA   |

| I <sub>PG</sub>     | PG leakage current                                                |                                                                       |                     |                     |                                       |      |

| T <sub>TSD</sub>    | Junction shutdown temperature                                     |                                                                       | 160                 | 180                 |                                       |      |

| T <sub>R</sub>      | Junction reset temperature                                        |                                                                       |                     | 160                 |                                       |      |

| T <sub>HYST</sub>   | Junction thermal hysteresis                                       |                                                                       |                     | 20                  |                                       | °C   |

| T <sub>CSD</sub>    | Case shutdown temperature                                         |                                                                       | 115                 | 130                 | 155                                   |      |

| T <sub>CR</sub>     | Case reset temperature                                            |                                                                       |                     | 110                 |                                       |      |

| T <sub>CHYST</sub>  | Case thermal hysteresis                                           |                                                                       |                     | 20                  |                                       |      |

| t <sub>WD</sub>     | Watchdog hold time                                                | See Figure 11                                                         | 50                  |                     |                                       | ns   |

| t <sub>WM</sub>     | Watchdog time                                                     | See Table 13 and Figure 11                                            |                     |                     |                                       |      |

| t <sub>OUT_EN</sub> | OUT_EN pin propagation delay (1)                                  | V <sub>CC</sub> = 24 V; I <sub>OUT</sub> = 72 mA                      |                     | 10                  |                                       | ns   |

| t <sub>RES</sub>    | OUT_EN hold time                                                  |                                                                       | 50                  |                     |                                       | ns   |

| t <sub>WO</sub>     | Watchdog timeout (2)                                              |                                                                       |                     |                     | t <sub>WM</sub> + t <sub>d(OFF)</sub> | ms   |

<sup>1.</sup> Time from reset active low and power out disable.

DS11044 - Rev 7 page 10/38

<sup>2.</sup> Time from  $t_{WM}$  elapsed to power out disable.

#### 4.6 Step-down switching regulator

10.5 V <  $V_{CC}$  < 36 V; -40 °C <  $T_{J}$  < 125 °C; unless otherwise specified

Table 9. Step-down switching regulator

| Symbol                 | Parameter                            | Test conditions                    | Min. | Тур.                                               | Max. | Unit |

|------------------------|--------------------------------------|------------------------------------|------|----------------------------------------------------|------|------|

|                        |                                      | I <sub>REG</sub> from 0 to 100 mA, | 3.1  | 3.3 3.5  5  3.3 3.5  1.5  0.9  0.6  15.8  400  80% |      |      |

| Vac                    | Voltage on VREG pin supplied by      | see Figure 15                      | 3.1  | 3.3                                                | 3.5  | V    |

| V <sub>DC_out</sub>    | the embedded DC-DC                   | I <sub>REG</sub> from 0 to 100 mA, |      | 5                                                  |      | V    |

|                        |                                      | see Figure 16                      |      | 3                                                  |      |      |

| $V_{FB}$               | Voltage feedback                     |                                    | 3.1  | 3.3                                                | 3.5  | V    |

| R <sub>DS(on)</sub>    | MOSFET on-resistance                 |                                    |      | 1.5                                                |      | Ω    |

| I <sub>DC-DC(PK)</sub> | Inductor peak current                |                                    | 0.55 |                                                    | 0.9  | Α    |

| I <sub>qop</sub>       | Total operating quiescent current    |                                    |      | 0.6                                                |      | mA   |

| I <sub>qst-by</sub>    | Total standby quiescent current      | Regulator standby                  |      | 15.8                                               |      | μA   |

| f <sub>s</sub>         | Switching frequency                  |                                    |      | 400                                                |      | kHz  |

| D <sub>max</sub>       | Maximum duty cycle                   |                                    |      | 80%                                                |      | %    |

| ton <sub>min</sub>     | Minimum on-time                      |                                    |      | 150                                                |      | ns   |

| $f_{sc}$               | Frequency in short-circuit condition |                                    |      | 50                                                 |      | kHz  |

#### 4.7 LED driving array

10.5 V <  $V_{CC}$  < 36 V; -40 °C <  $T_{J}$  < 125 °C; unless otherwise specified

Table 10. LED driving array

| Symbol           | Parameter                           | Test conditions           | Min.                  | Тур.                  | Max. | Unit |

|------------------|-------------------------------------|---------------------------|-----------------------|-----------------------|------|------|

| V <sub>COL</sub> | Output source voltage on COL pins   | Output current 0 to 7 mA  | V <sub>REG</sub> -0.3 | V <sub>REG</sub> -0.2 |      | V    |

| V <sub>ROW</sub> | Open drain voltage on ROW pins      | Output current 0 to 15 mA |                       | 0.2                   | 0.3  | V    |

| f <sub>sw</sub>  | Row refresh frequency with duty=25% |                           |                       | 780                   |      | Hz   |

DS11044 - Rev 7 page 11/38

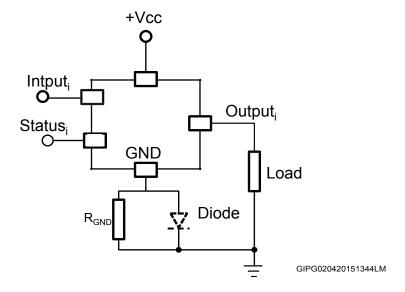

#### 5 Reverse polarity protection

Reverse polarity protection can be implemented on board using two different solutions:

- 1. Placing a resistor (R<sub>GND</sub>) between IC GND pin and load GND

- 2. Placing a diode between IC GND pin and load GND

If option 1 is selected, the minimum resistance value has to be selected according to the following equation:

R<sub>GND</sub> ≥ V<sub>CC</sub> / I<sub>GND</sub>

where  $I_{\mbox{\footnotesize GND}}$  is the DC reverse ground pin current and can be found in Section 3 of this datasheet.

Power dissipated by  $R_{GND}$  (when  $V_{CC}$  < 0: during reverse polarity situations) is:

$$P_D = (V_{CC})^2 / R_{GND}$$

If option 2 is selected, the diode has to be chosen by taking into account VRRM  $>|V_{CC}|$  and its power dissipation capability:

$P_D \ge I_S^*V_F$

Note:

In normal conditions (no reverse polarity), due to the diode, there is a voltage drop between GND of the device and GND of the system.

Figure 6. Reverse polarity protection

This schematic can be used with any type of load.

DS11044 - Rev 7 page 12/38

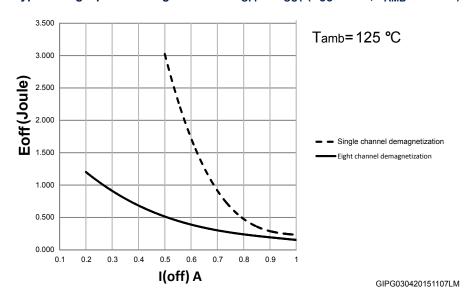

## Demagnetization energy

Figure 7. Typical single pulse demagnetization:  $E_{OFF}$  vs  $I_{OUT}$  ( $V_{CC}$  = 24 V,  $T_{AMB}$  = 125 °C)

DS11044 - Rev 7 page 13/38

#### 7 Truth table

Table 11. Truth table

| Condition                            | Input/<br>Driving<br>bit | Output           | SPI status<br>bit  | FAULT | TWARN   | PG   |

|--------------------------------------|--------------------------|------------------|--------------------|-------|---------|------|

| Normal operation                     | High                     | On               | Reset              | High  | High    | High |

| Normal operation                     | Low                      | Off              | Reset              | High  | High    | High |

| lunation accordance and una          | High                     | Off              | Set                | Low   | Х       | Х    |

| Junction overtemperature             | Low                      | Off              | Set <sup>(1)</sup> | High  | Х       | Х    |

| Casa avertamparatura                 | High                     | Off              | Set <sup>(1)</sup> | Х     | Low     | Х    |

| Case overtemperature                 | Low                      | Off              | Set <sup>(1)</sup> | Х     | Low (1) | Х    |

| Lindonvoltago                        | High                     | Off              | Reset              | X     | Х       | Х    |

| Undervoltage                         | Low                      | Off              | Reset              | X     | Х       | Х    |

| Dawer Cood                           | High                     | On               | Cat (2)            | High  | High    | Low  |

| Power Good                           | Low                      | Off              | Set (2)            | High  | High    | Low  |

| SPI communication fault              | High                     | (0)              | Set                | Low   | High    | High |

| (Parity check or module-8 violation) | Low                      | X <sup>(3)</sup> | Set                | Low   | High    | High |

- 1. This signal becomes high after the temperature falls below the reset threshold.

- 2. If fault expires, the reset condition occurs after SPI communication, otherwise it is set again.

- 3. When the SPI communication fails the output is frozen last valid state

DS11044 - Rev 7 page 14/38

#### Pin function description

#### 8.1 SPI/parallel selection mode (SEL2)

This pin allows the selection of the IC interfacing mode. The SPI interface is selected if SEL2 = H, while the parallel interface is selected if SEL2 = L, according to:

SEL2 = H(1) SEL2 = L Pin **SPI** operation parallel operation SDO/IN8 SDO Serial data output IN8 Input to channel 8 SS /IN7  $\overline{SS}$ Slave select IN7 Input to channel 7 CLK/IN6 CLK Serial clock IN<sub>6</sub> Input to channel 6 SDI/IN5 SDI Serial data input IN<sub>5</sub> Input to channel 5 WD/IN4 WD Watchdog input IN4 Input to channel 4 OUT EN/IN3 OUTx enable / disable IN3 **OUT EN** Input to channel 3 Watchdog enable / WD EN/IN2 WD EN disable and timing IN<sub>2</sub> Input to channel 2 preset 8/16-bit SPI selection SEL1/IN1 SEL1 IN1 Input to channel 1 mode

Table 12. Pin function description

#### 8.2 Serial data in (SDI)

If SEL2 = H, this pin is the input of the serial control frame. SDI is read on CLK rising edges and, therefore, the microcontroller must change SDI state during the CLK falling edges. After the SS falling edge, the SDI is equal to the most significant bit of the control frame (Figure 8).

#### 8.3 Serial data out (SDO)

If SEL2 = H, this pin is the output of the serial fault frame. SDO is updated on CLK falling edges and, therefore, the microcontroller must read SDO state during the CLK rising edges.

The SDO pin is tri-stated when  $\overline{SS}$  signal is high and it is equal to the most significant bit of the fault frame after the  $\overline{SS}$  falling edge (Figure 8).

#### 8.4 Serial data clock (CLK)

If SEL2 = H, the CLK line is the input clock for serial data sampling. On CLK rising edge the SDI input is sampled by the IC and the SDO output is sampled by the host microcontroller. On CLK falling edge, both SDI and SDO lines are updated to the next bit of the frame, from the most to the less significant one (see Figure 8). When the SS signal is high, slave not selected, the microcontroller should drive the CLK low (the settings for the MCU SPI port are CPHA = 0 and CPOL = 0).

#### 8.5 Slave select (SS)

If SEL2 = H, the slave select ( $\overline{SS}$ ) signal is used to enable the IC serial communication shift register; data is flushed-in through the SDI pin and flushed-out from the SDO pin only when the  $\overline{SS}$  pin is low. On the  $\overline{SS}$  pin falling edge the shift register (containing the fault conditions) is frozen, so any change on the power switches status is latched until the next  $\overline{SS}$  falling edge event and the SDO output is enabled. On the  $\overline{SS}$  pin rising edge event the 8/16 bits present on the SPI shift register are evaluated and the outputs are driven according to this frame. If more than 8/16 bits (depending on the SPI settings) are flushed inside only the last 8/16 are evaluated; the others are flushed out from the SDO pin after fault condition bits; in this way a proper communication is possible also in a daisy chain configuration.

DS11044 - Rev 7 page 15/38

<sup>1.</sup> SEL2 has an internal weak pull-down.

CPHA=0 SCK CPOL=0 **SDO** Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 **LSBit** SDI Bit 3 Bit MSBit. Bit 6 Bit 5 Bit 4 Bit 2 SS Capture strobe

Figure 8. SPI mode diagram

GIPG030420151131LM

#### 8.6 8/16-bit selection (SEL1)

If SEL2 = H, SEL1 is used to select between two possible SPI configurations: the 8-bit SPI mode (SEL1 = L) and the 16-bit SPI mode (SEL1 = H). 8/16-bit SPI operation is described below.

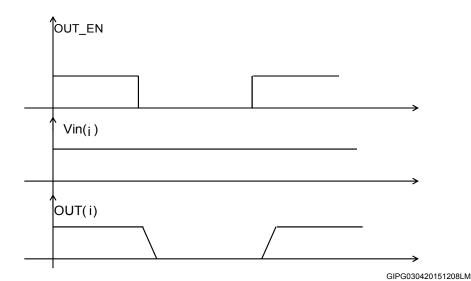

#### 8.7 Output enable (OUT\_EN)

If SEL2 = H, the OUT\_EN pin provides a fast way to disable all the outputs simultaneously. When the OUT\_EN pin is driven low for at least  $T_{RES}$ , the outputs are disabled while fault conditions in the SPI register are latched. To enable the outputs, the OUT\_EN pin should be raised and the IC should be re-programmed through the SPI interface. As fault conditions are latched inside the IC and SPI interface also works while the OUT\_EN pin is driven low, the SPI can be used to detect if a fault condition occurred before than the reset event.

The device is ready to operate normally after a T<sub>SU</sub> period. The OUT\_EN pin is the fastest way to disable all outputs when a fault occurs.

Figure 9. Output channel enable/disable behavior

DS11044 - Rev 7 page 16/38

#### 8.8 IC warning case temperature detection (TWARN)

The  $\overline{\text{TWARN}}$  pin is an active low open drain output. This pin is active if the IC case temperature exceeds  $T_{CSD}$ . According to the PCB thermal design and  $R_{th(JC)}$  value, this function allows a warning about a PCB overheating condition to be given.

The  $\overline{\text{TWARN}}$  bit is also available through SPI. This bit is not latched: the  $\overline{\text{TWARN}}$  pin is low only while the case overtemperature condition is active ( $T_C > T_{CSD}$ ) and is released when this condition is removed ( $T_C < T_{CR}$ ).

#### 8.9 Fault indication (FAULT)

The FAULT pin is an open drain active low fault indication pin. This pin is activated by one or more of the following conditions:

Channel overtemperature (OVT)

This pin is activated when at least one of the channels is in junction overtemperature.

Unlike the SPI fault detection bits, this signal is not latched: the  $\overline{FAULT}$  pin is low only when the fault condition is active and is released if the input driving signal is OFF or after the OVT protection condition has been removed. This last event occurs if the channel temperature decreases below the threshold level and the case temperature has not exceeded  $T_{CSD}$  or is below  $T_{CR}$ . This means that the  $\overline{FAULT}$  pin is low only while the junction overtemperature is active  $(T_J > T_{TSD})$  and is released after this condition has been removed  $(T_J < T_R)$  and  $T_C < T_{CR}$ .

SPI communication fault (parity check or module-8 violation)

When SPI mode is used (SEL2 = H), if a parity check fault of the incoming SPI frame is detected or counted CLK rising edges are different by a multiple of 8, the FAULT pin is kept low. When counted CLK rising edges are a multiple of 8 and parity check is valid, the FAULT pin is kept high.

#### 8.10 Power Good (PG)

The  $\overline{PG}$  terminal is an open drain, which indicates the status of the supply voltage. When  $V_{CC}$  supply voltage reaches the  $V_{sth1}$  threshold,  $\overline{PG}$  goes into a high impedance state. It goes into a low impedance state when  $V_{CC}$  falls below the  $V_{sth2}$  threshold.

In 16-bit SPI mode, a  $\overline{PG}$  bit is also available. This bit is set high when the Power Good diagnostic is active, it is otherwise cleared.

Figure 10. Power Good diagnostic

#### 8.11 Programmable watchdog counter reset (WD)

If SEL2 = H, and the WD\_EN = H, then the embedded watchdog counter is enabled. An H-L transition on the WD pin resets the watchdog counter.

If the counter elapses before of the H-L transition on WD pin, then the IC enters into an internal reset state where all the outputs are disabled; to restart normal operation a negative pulse must be applied to the WD pin.

The WD\_EN pin should be connected through an external divider to V<sub>REG</sub>.

The watchdog time is fixed in the following table:

DS11044 - Rev 7 page 17/38

Table 13. Programmable watchdog time

| $V_{WD\_EN}$                                                       | t <sub>WM</sub> |

|--------------------------------------------------------------------|-----------------|

| 0.25 V <sub>REG</sub> > V <sub>WD_EN</sub>                         | Disable         |

| 0.25 V <sub>REG</sub> ≤ V <sub>WD_EN</sub> < 0.5 V <sub>REG</sub>  | 40 ± 25% ms     |

| 0.25 V <sub>REG</sub> ≤ V <sub>WD_EN</sub> < 0.75 V <sub>REG</sub> | 80 ± 25% ms     |

| 0.75 V <sub>REG</sub> ≤ V <sub>WD_EN</sub> = V <sub>REG</sub>      | 160 ± 25% ms    |

Figure 11. Watchdog reset

DS11044 - Rev 7 page 18/38

#### 9 SPI operation (SEL2 = H)

Figure 12. SPI directional logic convention

#### 9.1 8-bit SPI mode (SEL1 = L)

If SEL2 = H, the 8-bit SPI mode is based on an 8-bit command frame sent from the microcontroller to the IC; each bit directly drives the corresponding output where LSB drives output 0 and MSB drives output 7. Each bit, set to '1', activates (closes) the corresponding output.

At the same time, the IC transfers the channel fault conditions (OVT) to the microcontroller. These fault conditions are latched at the occurrence and cleared after each communication (each time the  $\overline{SS}$  signal has a positive transition). Each bit, set to '1', indicates an OVT condition for the corresponding channel.

Table 14. Command 8-bit frame (master-to-slave)

| MSB | SB  |     |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|

| IN7 | IN6 | IN5 | IN4 | IN3 | IN2 | IN1 | IN0 |

Table 15. Fault 8-bit frame (slave-to-master)

| MSB |    |    |    |    |    |    |    |

|-----|----|----|----|----|----|----|----|

| F7  | F6 | F5 | F4 | F3 | F2 | F1 | F0 |

#### 9.2 16-bit SPI mode (SEL1 = H)

The 16-bit SPI mode is based on a 16-bit command frame sent from the microcontroller to the IC; the first 8 bits directly drive the output channels (each bit, set to '1', activates the corresponding output), the other 8 bits contain a 4-bit parity check code where the last bit (the inversion of the previous one) is used to detect a communication error condition (providing at least a transition in each frame):

P0 = IN0  $\oplus$  IN1 $\oplus$  IN2  $\oplus$  IN3  $\oplus$  IN4  $\oplus$  IN5  $\oplus$  IN6  $\oplus$  IN7

P1 = IN1 ⊕ IN3 ⊕ IN5 ⊕ IN7

$P2 = IN0 \oplus IN2 \oplus IN4 \oplus IN6$

nP0 = not P0

where  $\oplus$  is the XOR operator symbol.

Table 16. Command 16-bit frame (master-to-slave)

| MSB |     |     |     |     |     |     |     |  |  |    |    |    | LSB |

|-----|-----|-----|-----|-----|-----|-----|-----|--|--|----|----|----|-----|

| IN7 | IN6 | IN5 | IN4 | IN3 | IN2 | IN1 | IN0 |  |  | P2 | P1 | P0 | nP0 |

DS11044 - Rev 7 page 19/38

At the same time, the IC transfers to the microcontroller a 16-bit fault frame where the first 8 bits indicate a channel fault (OVT) condition (each bit, set to '1', indicates an OVT event), the following 4 bits provide general fault condition information. FB\_OK: this bit is related to the DC-DC regulation: at the DC-DC turn-on, this bit is low and becomes high after FB rises above 90% of the nominal  $V_{FB}$  voltage and a correct SPI communication occurred. If the FB voltage falls below 80% of the nominal  $V_{FB}$  voltage, this bit is zero;  $\overline{TWARN}$  (IC warning case temperature), PC (parity check fail, the bit, set to '1', indicates a PC fail or the length is not a multiple of 8) and  $\overline{PG}$  (Power Good, see Section 8.10). The last 4 bits are used as parity check bits and communication error condition (see command 16-bit frame):

P0 = F0  $\oplus$  F1 $\oplus$  F2  $\oplus$  F3  $\oplus$  F4  $\oplus$  F5  $\oplus$  F6  $\oplus$  F7

P1 = PC  $\oplus$  FB\_OK  $\oplus$  F1  $\oplus$  F3  $\oplus$  F5  $\oplus$  F7

P2 =  $\overrightarrow{PG}$   $\oplus$   $\overrightarrow{TWARN}$   $\oplus$  F0  $\oplus$  F2  $\oplus$  F4  $\oplus$  F6

nP0 = not P0

where  $\oplus$  is the XOR operator symbol.

Table 17. Fault 16-bit frame (slave-to-master)

| MSB |    |    |    |    |    |    |    |       | LSB   |    |    |    |    |    |     |

|-----|----|----|----|----|----|----|----|-------|-------|----|----|----|----|----|-----|

| F7  | F6 | F5 | F4 | F3 | F2 | F1 | F0 | FB_OK | TWARN | PC | PG | P2 | P1 | P0 | nP0 |

Channel indications are latched and cleared after a communication only.

#### 9.3 Daisy chaining

The VNI8200XP/XP-32 can be daisy-chained by connecting the MOSI port of the micro-controller to the SDI pin of the first IC of the chain; the SDO pin of the first IC of the chain to the SDI pin of the second (and similarly for the next ICs of chain); the SDO pin of the last IC of the chain to the MISO port of the micro-controller. See an example in Figure 13

UC SPI SCLK SS CLK SS CLK SS CLK

Figure 13. Example of daisy chaining connection

DS11044 - Rev 7 page 20/38

## 10 LED driving array

The LED driving array carries out the status of the output channels (ON or OFF).

Figure 14. LED driving array

GIPG030420151307LM

The following equation is an indication how to choose the R<sub>ext</sub> resistor value:

$R_{ext} = (V_{COLmin}) - (V_{ROWmax}) - V_{F(LED)} / I_{F(LED)}$

where  $I_{F(LED)} \le 7$  mA; ( $V_{COL}$  min) and ( $V_{ROW}$  max) can be found in Table 10;  $V_{F(LED)}$  and  $I_{F(LED)}$  depend of the LEDs electrical characteristics.

DS11044 - Rev 7 page 21/38

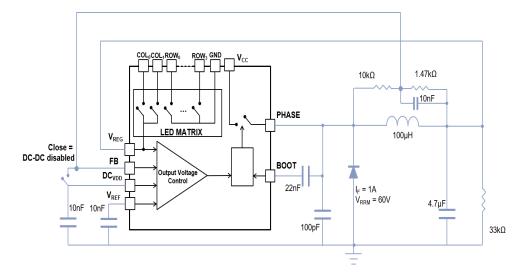

#### 11 Step-down switching regulator

The IC embeds a high efficiency 100 mA micropower step-down switching regulator. The regulator is protected against short-circuit or overload conditions. Pulse-by-pulse current limit regulation is obtained in normal operation through a current loop control.

A low ESR output capacitor connected to the  $V_{REG}$  pin helps to limit the regulated voltage ripple; a low ESR (less than 10 m $\Omega$ ) capacitor is preferable. The control loop pin FB allows 3.3 V to be regulated, connecting it directly to  $V_{REG}$ , or 5 V connecting it through a voltage divider. The DC-DC converter can be turned off by connecting the FB pin to the DCVDD pin.

In some applications, it is possible to switch off the embedded DC-DC and supply the  $V_{REG}$  by 5 V or 3.3 V externally. Also, in case of two or more IC inside the same board, the user can activate the DC-DC converter on only one IC and also supply the  $V_{REG}$  pins of the other ICs.

If the DC-DC converter is adjusted to provide 3.3 V regulation and the  $V_{DC\_out}$  is used to power an external load and not the device, a 33 k $\Omega$  resistor has to be connected on  $V_{REG}$  pin.

Figure 15. Typical circuit for switching regulation V<sub>DC-out</sub> = 3.3 V

Figure 16. Typical circuit for switching regulation  $V_{DC-out} = 5 V$

DS11044 - Rev 7 page 22/38

The embedded step-down can be disabled for the application where it is not required. In such cases, the recommended configuration is reported in the figure below:

Figure 17. Typical circuit for embedded step-down regulator disabled

DS11044 - Rev 7 page 23/38

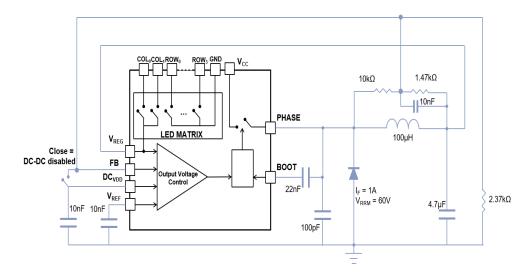

#### 12 Thermal management

The power dissipation in the IC is the main factor that sets the safe operating condition of the device in the application. Therefore, it must be taken into account very carefully. Heatsinking can be achieved using copper on the PCB with proper area and thickness. The following image shows the junction-to-ambient thermal impedance values for the PowerSSO-36 package.

Figure 18. PowerSSO-36 thermal impedance vs. time

For instance, three cases have been considered using a PowerSSO-36 packaged with copper slug soldered on a 1.6 mm thickness FR4 board with dissipating footprint (copper thickness of 70  $\mu$ m):

- single layer PCB with just IC footprint dissipating area

- double layer PCB with footprint dissipating area on the top side and a 2 cm² dissipating layer on the bottom side through 15 via holes

- double layer PCB with footprint dissipating area on the top side and an 8 cm<sup>2</sup> dissipating layer on the bottom side through 15 via holes

DS11044 - Rev 7 page 24/38

#### 12.1 Thermal behavior

Figure 19. Thermal behavior

Note: 1 Thermal shutdown

2 Junction hysteresis

3 Restore to idle condition

4 Case hysteresis

DS11044 - Rev 7 page 25/38

## 13 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

#### 13.1 PowerSSO-36 package information

<del>Ф</del>999МСА-ВD <del>Ф</del>999**М**СА-ВД ₼ ₼ G3 E4 **/**4**/**3\ OFFFCA-B D (0.25D index area x 0.75E1) G1×2 Ė  $\triangle$ G2 E'3 pin 1 indicator 2x □aaa€D 2x N/2 TIPS  $\mathbb{B}$

Figure 20. PowerSSO-36 package outline

7587131 rev9

DS11044 - Rev 7 page 26/38

Not in scale (section A-A)

Not in scale (section A-A)

Figure 21. PowerSSO-36 package outline details

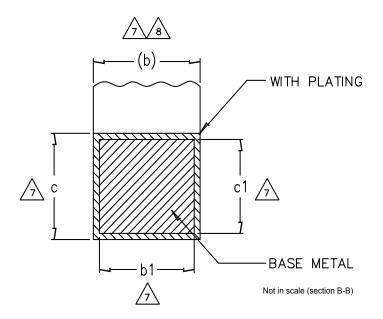

Figure 22. PowerSSO-36 package outline details (section B-B)

DS11044 - Rev 7 page 27/38

Table 18. PowerSSO-36 mechanical data

| D.   |      | mm        |       |

|------|------|-----------|-------|

| Dim. | Min. | Тур.      | Max.  |

| θ    | 0°   |           | 8°    |

| ө1   | 5°   |           | 10°   |

| е2   | 0°   |           |       |

| A    | 2.15 |           | 2.45  |

| A1   | 0.00 |           | 0.10  |

| A2   | 2.15 |           | 2.35  |

| b    | 0.18 |           | 0.32  |

| b1   | 0.13 | 0.25      | 0.30  |

| С    | 0.23 |           | 0.32  |

| c1   | 0.20 | 0.20      | 0.30  |

| D    |      | 10.30 BSC |       |

| D1   | 7.00 |           | 7.40  |

| D2   |      | 3.65      | 4.200 |

| D3   |      | 4.30      |       |

| е    |      | 0.50 BSC  |       |

| E    |      | 10.30 BSC |       |

| E1   |      | 7.50 BSC  |       |

| E2   | 4.20 |           | 4.60  |

| E3   |      | 2.30      |       |

| E4   |      | 2.90      |       |

| G1   |      | 1.20      |       |

| G2   |      | 1.00      |       |

| G3   |      | 0.80      |       |

| h    | 0.30 |           | 0.40  |

| L    | 0.60 | 0.70      | 0.85  |

| L1   |      | 1.40 REF  |       |

| L2   |      | 0.25 BSC  |       |

| N    |      | 36        |       |

| R    | 0.30 |           |       |

| R1   | 0.20 |           |       |

| S    | 0.25 |           |       |

DS11044 - Rev 7 page 28/38

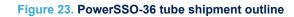

## 13.2 PowerSSO-36 packing information

Table 19. PowerSSO-36 tube shipment mechanical data

| Description         | Value |

|---------------------|-------|

| Base quantity       | 49    |

| Bulk quantity       | 1225  |

| Tube lenght (± 0.5) | 532   |

| А                   | 3.5   |

| В                   | 13.8  |

| C (± 0.1)           | 0.6   |

Note: All dimensions are in mm

DS11044 - Rev 7 page 29/38

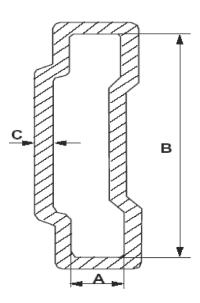

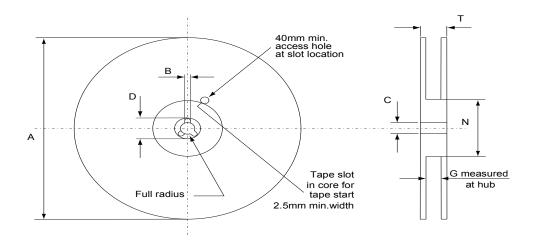

Figure 24. PowerSSO-36 tape dimension outline

Table 20. PowerSSO-36 tape dimension mechanical data

| Description       | Dimensions | Value |

|-------------------|------------|-------|

| Tape width        | W          | 24    |

| Tape hole spacing | P0 (± 0.1) | 4     |

| Component spacing | Р          | 12    |

| Hole diameter     | D (± 0.05) | 1.55  |

| Hole diameter     | D1 (min.)  | 1.5   |

| Hole position     | F (± 0.1)  | 11.5  |

| Compartment depth | K (max.)   | 2.85  |

| Hole spacing      | P1 (± 0.1) | 2     |

Note: According to the Electronic Industries Association (EIA) standard 481 rev. A, Feb 1986

DS11044 - Rev 7 page 30/38

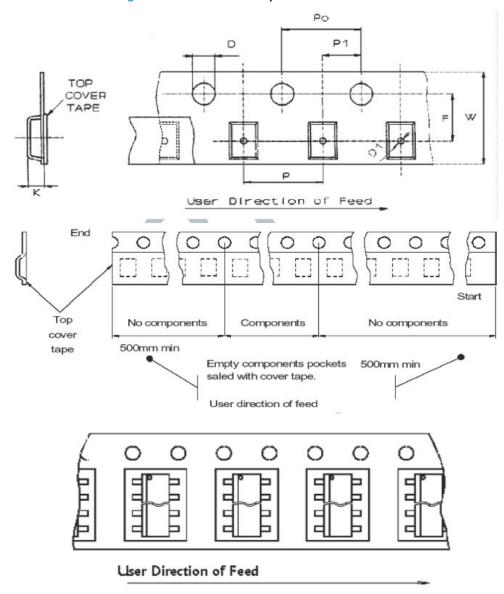

Figure 25. PowerSSO-36 reel shipment outline

AM06038v1

Table 21. PowerSSO-36 reel dimension mechanical data

| Description   | Value |

|---------------|-------|

| Base quantity | 1000  |

| Bulk quantity | 1000  |

| A max.        | 330   |

| B min.        | 1.5   |

| C (± 0.2)     | 13    |

| F             | 20.2  |

| G (2 ± 0)     | 24.4  |

| N min.        | 100   |

| T min.        | 30.4  |

DS11044 - Rev 7 page 31/38

## 14 Ordering information

**Table 22. Ordering information**

| Part number    | Package     | Packaging     |  |  |

|----------------|-------------|---------------|--|--|

| VNI8200XP      |             | Tube          |  |  |

| VNI8200XPTR    | PowerSSO-36 | Tape and reel |  |  |

| VNI8200XP-32   | F0We1330-30 | Tube          |  |  |

| VNI8200XPTR-32 |             | Tape and reel |  |  |

DS11044 - Rev 7 page 32/38

## **Revision history**

Table 23. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08-May-2015 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 09-Jun-2015 | 2        | Updated $V_{CC}$ supply current parameter in table 5 and updated $V_{PGH1}$ , $V_{PGH2}$ , $V_{USD}$ , $I_{PEAK}$ , $I_{LIM}$ and Hyst parameters in table 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 24-Aug-2015 | 3        | Updated programmable watchdog time table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24-Aug-2013 | 3        | Datasheet status promoted from preliminary data to production data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 08-May-2023 | 4        | Merged DS of VNI8200XP and VNI8200XP-32; changed IC Section Features in front page reordered; changed IC Section Description in front page; changed Figure 1; updated pin description in Table 1 changed Table 2; updated description in Table 3; changed I <sub>LIM</sub> (symbol and definition) in Table 9; changed title of Figure 7; add row (SPI communication fault) in Table 11; updated description in Section 8.11; updated description and add figures in Section 11; deleted old section 12 (Typical circuits and conventions) and moved Figure 12 in Section 9; deleted old section 14 (Interface timing diagram) and moved ex fig.15 (Serial timing) now Figure 3 in Section 4.2; deleted old section 15 (Switching parameter test conditions) and moved ex fig. 16 now Figure 4 and ex fig 17 now Figure 5 in Section 4.3; some minor changes. |

| 15-May-2023 | 5        | Changed Figure 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12-Feb-2024 | 6        | Changed XOR operator symbol in Section 9.2; some minor changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10-Jul-2025 | 7        | Corrected typo (t <sub>OUT_EN</sub> unit) in Table 8; added Figure 17; some minor changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

DS11044 - Rev 7 page 33/38

## **Contents**

| 1  | Bloc  | k diagram                                       | 3  |  |  |

|----|-------|-------------------------------------------------|----|--|--|

| 2  | Pin o | connection                                      | 4  |  |  |

| 3  | Maxi  | mum ratings                                     | 6  |  |  |

| 4  | Elec  | Electrical characteristics                      |    |  |  |

|    | 4.1   | Power section                                   | 7  |  |  |

|    | 4.2   | SPI characteristics                             | 7  |  |  |

|    | 4.3   | Switching                                       | 8  |  |  |

|    | 4.4   | Logic inputs                                    | 9  |  |  |

|    | 4.5   | Protection and diagnostic                       | 9  |  |  |

|    | 4.6   | Step-down switching regulator                   | 11 |  |  |

|    | 4.7   | LED driving array                               | 11 |  |  |

| 5  | Reve  | erse polarity protection                        | 12 |  |  |

| 6  | Dem   | agnetization energy                             | 13 |  |  |

| 7  | Truti | ո table․․․․․                                    | 14 |  |  |

| 8  | Pin f | unction description                             | 15 |  |  |

|    | 8.1   | SPI/parallel selection mode (SEL2)              | 15 |  |  |

|    | 8.2   | Serial data in (SDI)                            | 15 |  |  |

|    | 8.3   | Serial data out (SDO)                           | 15 |  |  |

|    | 8.4   | Serial data clock (CLK)                         | 15 |  |  |

|    | 8.5   | Slave select (SS)                               | 15 |  |  |

|    | 8.6   | 8/16-bit selection (SEL1)                       | 16 |  |  |

|    | 8.7   | Output enable (OUT_EN)                          | 16 |  |  |

|    | 8.8   | IC warning case temperature detection ( TWARN ) | 17 |  |  |

|    | 8.9   | Fault indication (FAULT)                        | 17 |  |  |

|    | 8.10  | Power Good (PG)                                 | 17 |  |  |

|    | 8.11  | Programmable watchdog counter reset (WD)        | 17 |  |  |

| 9  | SPI   | operation (SEL2 = H)                            | 19 |  |  |

|    | 9.1   | 8-bit SPI mode (SEL1 = L)                       | 19 |  |  |

|    | 9.2   | 16-bit SPI mode (SEL1 = H)                      | 19 |  |  |

|    | 9.3   | Daisy chaining                                  | 20 |  |  |

| 10 | LED   | driving array                                   | 21 |  |  |

| 11 | Step  | -down switching regulator                       | 22 |  |  |

| 12 | Ther  | mal management                                  | 24 |  |  |

|    |       |                                                 |    |  |  |

#### VNI8200XP / VNI8200XP-32

|      | 12.1   | Thermal behavior                | . 25 |

|------|--------|---------------------------------|------|

| 13   | Pack   | age information                 | .26  |

|      | 13.1   | PowerSSO-36 package information | . 26 |

|      | 13.2   | PowerSSO-36 packing information | . 29 |

| 14   | Orde   | ering information               | .32  |

| Rev  | ision  | history                         | .33  |

| List | of tak | oles                            | .36  |

| List | of fia | ures                            | 37   |

## **List of tables**

| Table 1.  | Pin description                            | . 4 |

|-----------|--------------------------------------------|-----|

| Table 2.  | Absolute maximum ratings                   | . 6 |

| Table 3.  | Thermal data                               | . 6 |

| Table 4.  | Power section                              | . 7 |

| Table 5.  | SPI characteristics                        | . 7 |

| Table 6.  | Switching                                  | . 8 |

| Table 7.  | Logic inputs                               | . 9 |

| Table 8.  | Protection and diagnostic                  | . 9 |

| Table 9.  | Step-down switching regulator              | 11  |

| Table 10. | LED driving array                          | 11  |

| Table 11. | Truth table                                | 14  |

| Table 12. | Pin function description                   | 15  |

| Table 13. | Programmable watchdog time                 | 18  |

| Table 14. | Command 8-bit frame (master-to-slave)      | 19  |

| Table 15. | Fault 8-bit frame (slave-to-master)        | 19  |

| Table 16. | Command 16-bit frame (master-to-slave)     |     |

| Table 17. | Fault 16-bit frame (slave-to-master)       |     |

| Table 18. | PowerSSO-36 mechanical data                | 28  |

| Table 19. | PowerSSO-36 tube shipment mechanical data  | 29  |

| Table 20. | PowerSSO-36 tape dimension mechanical data | 30  |

| Table 21. | PowerSSO-36 reel dimension mechanical data |     |

| Table 22. | Ordering information                       | 32  |