# 2-channel high-side driver with STi<sup>2</sup>Fuse protection for automotive power distribution applications

# Product status link VNF9D1M2Q

| Product summary        |               |  |  |  |  |  |

|------------------------|---------------|--|--|--|--|--|

| Order code VNF9D1M2QTR |               |  |  |  |  |  |

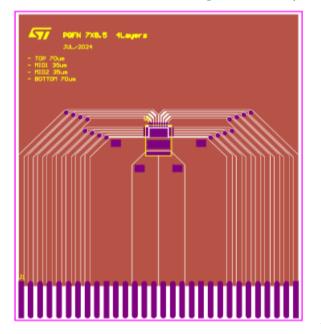

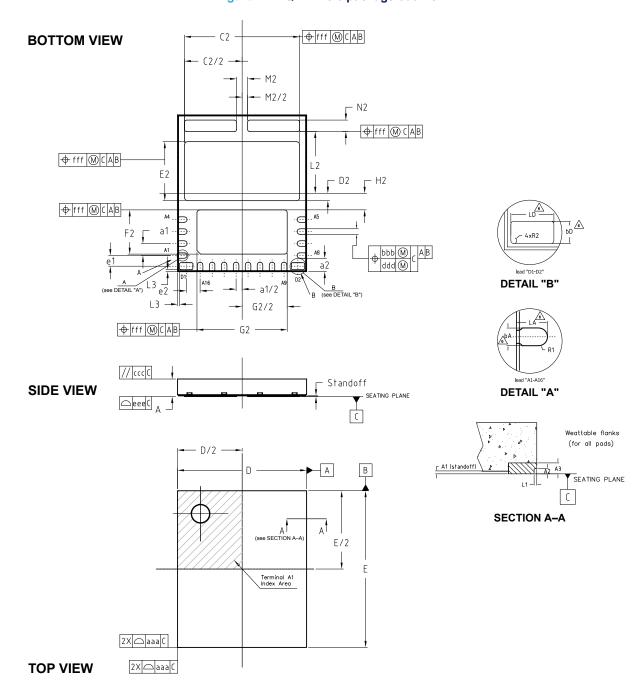

| Package                | PQFN 7X8.5    |  |  |  |  |  |

| Packing                | Tape and reel |  |  |  |  |  |

#### **Features**

| Channel | V <sub>cc</sub> | R <sub>ON</sub> typ. | I <sub>PEAK</sub> typ. |

|---------|-----------------|----------------------|------------------------|

| 0, 1    | 28 V            | 1.2 mΩ               | 145 A                  |

- AEC-Q100 qualified

- General

- 24-bit ST-SPI for full diagnostic and digital current sense feedback

- Integrated 10-bit ADC for digital current sense

- Integrated 10-bit ADC for STi<sup>2</sup>Fuse digital current sense

- Advanced limp-home functions for robust fail-safe system

- Very low standby current for parking mode functionality

- Control through direct inputs and/or SPI

- Emergency stop and limp-home pins for advanced safety features

- Capacitive loads charging mode

- PQFN 7x8.5 package with wettable flanks

- Compliant with European directive 2002/95/EC

- Diagnostic functions

- Digital proportional load current sense

- Diagnostic of overload and short to GND, harness protection

- V<sub>CC</sub> and output voltage digital feedback

- Case temperature monitoring

- Overtemperature shutdown, undervoltage, and overvoltage prewarning

- Protection

- Full programmable wire harness protection (STi<sup>2</sup>Fuse)

- Load peak current latch-off

- Overtemperature shutdown (latch-off)

- Overvoltage clamp

- Load dump protected

- Protection against loss of ground

## **Description**

The VNF9D1M2Q is a device made using STMicroelectronics VIPower technology. It is intended for driving resistive, inductive or capacitive loads directly connected to ground.

The device is protected against voltage transient on  $V_{CC}$  pin. Programming, control and diagnostics are implemented via the SPI bus. A digital current sense feedback and an STi²Fuse digital current sense feedback for each channel are provided through two independent integrated 10-bit ADCs per channel. Dedicated trimming bits adjust the ADC reference current. The device is equipped with 2 outputs controllable via SPI and/or with two dedicated direct inputs.

Real time diagnostic is available through the SPI bus (communication error, overtemperature, harness protection, overload protection,  $V_{CC}$  and output voltage monitoring,  $T_{C}$  monitoring). Output overcurrent detection protects the device in overload condition. Thermal shutdown is configured as latched off.

The VNF9D1M2Q embeds the ST proprietary I²t functionality, featuring an intelligent circuit breaking aimed at protecting PCB traces, connectors and wire harness from overheating, with no impact on load transients like inrush currents and capacitance charging. This function is set by two parameters, called I<sub>NOM</sub> and t<sub>NOM</sub>: there are 3 dedicated bits, per each parameter, to set respectively I<sub>NOM</sub> (nominal current) and t<sub>NOM</sub> (nominal timing). The I²t curve parameters can be individually set per each channel. The default values of these two parameters can be programmed twice using dedicated OTPs. The selection of default I²t configuration from OTPs for all channels is defined by the I2TCFGINIT in the ITCNTSR register. Further information about the OTP programming mode is provided in the dedicated user manual UM3275 (OTP programming for STi²Fuse devices).

The device enters a limp-home mode in case of reset of digital memory, watchdog monitoring time-out event or when LH (limp-home) pin is set to high. In limp-home mode each output is controlled by dedicated direct inputs. Emergency pins allow a rapid switch-off of the output channels in case of critical events in normal operation mode bypassing SPI control.

During standby mode, the device is able to support the parking mode functionality. In case the OUTPUT pin is pulled up to battery by an external secondary switch (for instance, the L99SP08 which is delivering the requested current to the load), the device offers a very low current consumption.

For further information refer to the application note AN6025 - Interaction of L99SP08 with single (VNF9SxQ) and dual (VNF9DxQ) hybrid eFuses.

DS14483 - Rev 3 page 2/74

# Block diagram and pin description

V<sub>CC</sub> Clamp protection VREG VDD VREG supply EM1 LATCH\_DIAGO Undervoltage LATCH\_DIAG1 Current Sense efuse Shadow ADC\_Ch0 SDI SDO SCK registers Current Sense efuse ADC Ch1 DIO ADC\_eFuse\_1 DI1 T-frame monitoring registers V<sub>cc</sub> monitoring ADC ADC V<sub>OUTO</sub> monitoring V<sub>OUT1</sub> monitoring

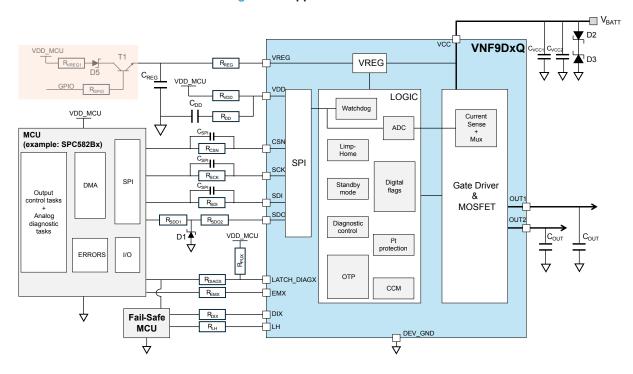

Figure 1. Block diagram

GADG210120221051GT

TAB =  $V_{CC}$ **SS**7 NC 4 (3) EM0 NC *ZZ*) 8 CTAB(\*) 3 (7.7.2) EM1 LATCH\_DIAG1 VREG 2 公 LATCH\_DIAG0 © 10 11 12 13 14 15 16 17 (CC) 8 8 8 8 8 8 8 GND DI11

LH

CSN

SCK

SCK

SDI

SDO

VDD

Figure 2. Connection diagram (top-through view)

(\*) To be soldered but kept electrically isolated at PCB level.

DS14483 - Rev 3 page 3/74

Table 1. Pin functionality description

| Pin# | Name            | Function                                                                                                                                                         |

|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAB  | V <sub>CC</sub> | Battery connection: this is the backside TAB and is the direct connection to the drain of the Power MOSFET switches.                                             |

| 1    | GND             | Ground connection: This pin serves as the ground connection for the logic part of the device.                                                                    |

| 2    | VREG            | DC output of internal pre-regulator generated from $V_{CC}$ to supply control circuit. To be connected to a filtering capacitor.                                 |

| 3    | EM1             | Emergency stop pins; turn off rapidly channel1 during normal operating mode.                                                                                     |

| 4    | EM0             | Emergency stop pins; turn off rapidly channel0 during normal operating mode.                                                                                     |

| 5    | OUT0            | Power OUTPUT0 is the direct connection to the source of the Power MOSFET switch $N^0$ 0.                                                                         |

| 6    | OUT1            | Power OUTPUT1 is the direct connection to the source of the Power MOSFET switch No 1.                                                                            |

| 7    | NC              | Not connected pin.                                                                                                                                               |

| 8    | NC              | Not connected pin.                                                                                                                                               |

| 9    | LATCH_DIAG1     | Open drain diagnostic pin; active in case of latched fault on channel1. Moreover, it is active for a limited time interval soon after wake up from standby mode. |

| 10   | LATCH_DIAG0     | Open drain diagnostic pin; active in case of latched fault on channel0. Moreover, it is active for a limited time interval soon after wake up from standby mode. |

| 11   | DI0             | Direct Input: direct control for OUT0 in limp-home mode. Configurable as OR combination with the relevant SPI OUT0 control bit in normal mode.                   |

| 12   | DI1             | Direct Input: direct control for OUT1 in limp-home mode. Configurable as OR combination with the relevant SPI OUT1 control bit in normal mode.                   |

| 13   | LH              | Limp-home pin. If set high, the device goes from normal mode to fail-safe mode.                                                                                  |

| 14   | CSN             | Chip select not (active low): It is the selection pin of the device. It is a CMOS compatible input.                                                              |

| 15   | SCK             | Serial clock: It is a CMOS compatible input.                                                                                                                     |

| 16   | SDI             | Serial data input: Transfers data to be written serially into the device on SCK rising edge.                                                                     |

| 17   | SDO             | Serial data output: Transfers data serially out of the device on SCK falling edge.                                                                               |

| 18   | VDD             | DC supply input for the SPI interface (3.3 V and 5 V compatible).                                                                                                |

DS14483 - Rev 3 page 4/74

# 2 Functional description

## 2.1 Device interfaces

- SPI: bi-directional interface, accessing RAM/ROM registers (CSN, SCK, SDI, SDO)

- Dlx: input pins for outputs control while the device is in fail-safe mode or normal mode

- V<sub>DD</sub>: 5 V supply or 3.3 V supply. V<sub>DD</sub> to be connected to microcontroller I/Os supply.

- EMx: emergency stop pins in normal mode operation.

- LATCH\_DIAGx: open drain output pins for advanced safety diagnostic.

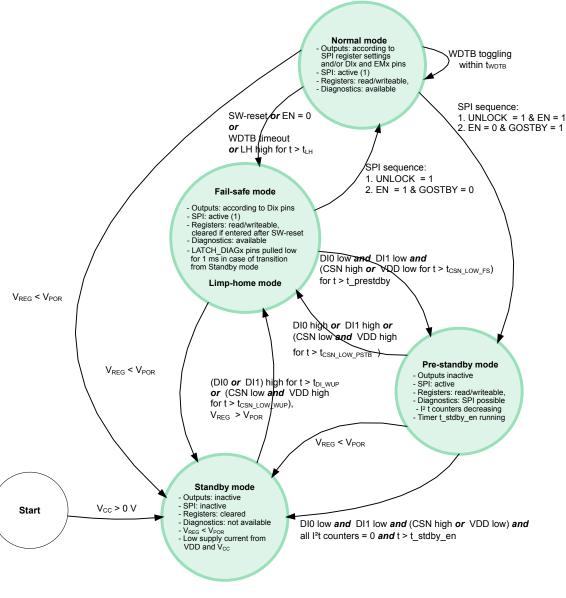

# 2.2 Operating modes

The device can operate in four different modes:

- Standby mode

- Fail-safe mode

- Normal mode

- Pre-standby mode

DS14483 - Rev 3 page 5/74

Table 2. Operating modes

| Operating mode                                           | Entering conditions                                                                                                                                                                                                                                                              | Leaving conditions                                                                                                                                                                                                                                                                        | Characteristics                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Startup transition<br>(this is not an<br>operating mode) |                                                                                                                                                                                                                                                                                  | • V <sub>CC</sub> > V <sub>USD:</sub> power on reset                                                                                                                                                                                                                                      | Outputs: OFF SPI: inactive Registers: reset values Diagnostics: not available                                                                                                                                                                                                                                                                        |

| Fail-safe<br>(Limp-home mode)                            | From standby mode if (DI0 or DI1) high or (CSN low and V <sub>DD</sub> high), and V <sub>REG</sub> > V <sub>POR</sub> From pre-standby mode if DI0 high or DI1 high or (CSN low and V <sub>DD</sub> high) From normal mode if SW reset or EN = 0 or watchdog timeout or LH high  | If V <sub>REG</sub> < V <sub>POR</sub> ; the device enters standby mode  If DI0 low and DI1 low and (CSN high or VDD low) for t > t_prestdby, the device enters pre-standby mode  If the following SPI sequence is sent:  UNLOCK = 1  EN = 1 and GOSTBY = 0 the device enters normal mode | Outputs: according to DIx  SPI: active  Registers: read/write possible, cleared if entered after SW reset  Diagnostics: available  The RESET is set to 1 if the last state is standby mode or in case the last command is an SW reset; it is reset to 0 at the first SPI access  Protections: available  LATCH_DIAGx pins pulled low for twkup_fdeck |

| Normal                                                   | • Fail-safe: SPI sequence 1. UNLOCK = 1 2. GOSTBY = 0 and EN = 1                                                                                                                                                                                                                 | VREG < VPOR: standby mode  SPI sequence  UNLOCK = 1 and EN = 1  GOSTBY = 1 and EN = 0: pre-standby mode  EN = 0: fail-safe mode  Watchdog time out: fail-safe mode  SW reset: fail-safe mode  LH pin is set to high for more than t <sub>LH</sub> : fail-safe mode                        | Outputs: according to SPI register settings and/or DIx and EMx pins SPI: active Registers: read/write possible Diagnostics: available Regular toggling of WDTB is necessary within timeout period twdtb                                                                                                                                              |

| Standby                                                  | Transition phase: V <sub>CC</sub> > 0  Fail-safe: V <sub>REG</sub> < V <sub>POR</sub> Normal mode: V <sub>REG</sub> < V <sub>POR</sub> Pre-standby:  V <sub>REG</sub> < V <sub>POR</sub> DIO low and DI1 low and (CSN high or VDD low), and all I²t counters = 0 and t > t_stdby | • DI0 = 1 or DI1 = 1 • CSN low and V <sub>DD</sub> high • VREG > VPOR                                                                                                                                                                                                                     | Outputs: OFF SPI: inactive Registers: cleared Diagnostics: not available Low supply current from V <sub>DD</sub> and V <sub>CC</sub>                                                                                                                                                                                                                 |

| Pre-standby                                              | Fail-safe mode: DI0 low and DI1 low and (CSN high or VDD low) for t > t_prestdby     Normal mode: SPI sequence     UNLOCK = 1 and EN = 1     GOSTBY = 1 and EN = 0                                                                                                               | I²t counters and t_stdby timer<br>are elapsed<br>DI0 = 0 and DI1 = 0 and<br>(CSN high or V <sub>DD</sub> low)                                                                                                                                                                             | Outputs: OFF  I²t counters decreasing SPI: active Registers: R/W possible Diagnostics: available Protections: active                                                                                                                                                                                                                                 |

DS14483 - Rev 3 page 6/74

Figure 3. Device state diagram

(1) SPI communication only if VDD is present.

## 2.2.1 Startup transition phase

This is not an operation mode but a transition step to standby operating mode at startup. In this phase,  $V_{CC}$  is applied.

## 2.2.2 Standby mode

The device is in low consumption state.

The outputs are in OFF state.

The diagnostics is not available.

The SPI communication is not active.

The registers are cleared.

The device enters standby mode under the following conditions:

- From transition phase if V<sub>CC</sub> is applied

- From fail-safe mode if V<sub>REG</sub> < V<sub>POR</sub>

DS14483 - Rev 3 page 7/74

- From normal mode if V<sub>REG</sub> < V<sub>POR</sub>

- · From pre-standby mode if:

- V<sub>REG</sub> < V<sub>POR</sub>

- DI0 low and DI1 low (CSN high or V<sub>DD</sub> low), and all I²t counters = 0 and t\_stdby\_en is elapsed

The device exits standby mode under the following conditions:

- If DI0 or DI1 are set to high

- If CSN is low and VDD is applied

#### 2.2.3 Fail-safe mode

The outputs are controlled by the direct inputs DIx.

The registers are in the read/write mode and are cleared to their reset value if fail-safe is entered through a software reset.

The RESET is 1 if the last state was standby mode or the last command was a SW reset and it is reset to 0 after the first SPI access (for more information refer to Section 4.3.1: Global status byte description).

The SPI interface is active and the diagnostics is available.

The protections are fully functional.

The device enters fail-safe mode under the following conditions:

- From standby mode if (DI0 OR DI1) high OR (CSN low AND VDD high) AND  $V_{REG} > V_{POR}$

- From pre-standby mode if (DI0 OR DI1) high OR (CSN low AND VDD high)

- From normal mode if SW reset or EN = 0 or watchdog timeout or LH high for t > t<sub>LH</sub>

The device exits fail-safe mode under the following conditions:

- If V<sub>REG</sub> < V<sub>POR</sub>, the device enters standby mode

- If (DI0 AND DI1) low AND (CSN high OR VDD low) for t > t\_prestdby, the device enters pre-standby mode

- If the SPI sends the following sequence:

- UNLOCK = 1

- EN = 1 and GOSTBY = 0

the device enters normal mode.

#### Transition to fail-safe mode from normal mode, using the SPI register

Only one frame is needed: write "CTRL" 0x0000.

Table 3. Frame 1 (write CTRL 0x0000)

|       | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    |

|-------|----------|----------|----------|----------|---------|----------|----------|----------|

| CMD   | OC1      | OC0      |          |          | Ado     | dress    |          |          |

| CIVID | 0        | 0        | 0        | 0        | 0       | 0        | 1        | 0        |

| DATA1 | GOSTBY   | UNLOCK   | CTDTH1   | CTDTH0   | EN      | Not used | Not used | Not used |

| DAIAI | 0        | 0        | 0        | 0        | 0       | 0        | 0        | 0        |

| DATA2 | Not used | Not used | Not used | Not used | LOCKEN1 | LOCKEN0  | Not used | Parity   |

|       | 0        | 0        | 0        | 0        | 0       | 0        | 0        | 0        |

### Transition to fail-safe mode from normal mode by SW-Reset

SPI reset occurs by using the "Read device information" command (applicable only on ROM area) at the reserved ROM address 0x3F. This is equivalent of sending a 0xFF command.

Only one frame is needed: read "ROM" 0x3F.

DS14483 - Rev 3 page 8/74

|       | Bit 7                   | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|-------|-------------------------|-------|-------|---------|-------|-------|-------|-------|--|--|

| CMD   | OC1                     | OC0   |       | Address |       |       |       |       |  |  |

|       | 1                       | 1     | 1     | 1       | 1     | 1     | 1     | 1     |  |  |

| DATA4 | <b>x</b> <sup>(1)</sup> | х     | х     | х       | х     | х     | х     | х     |  |  |

| DATA1 | 0                       | 0     | 0     | 0       | 0     | 0     | 0     | 0     |  |  |

| DATA2 | х                       | х     | х     | х       | х     | х     | х     | х     |  |  |

|       | 0                       | 0     | 0     | 0       | 0     | 0     | 0     | 0     |  |  |

Table 4. Frame 1: read (ROM) 0x3F 0x--

The entry to the fail-safe mode can occur due to the CSN timeout.

In this specific case, the following procedure must be executed to leave the fail-safe mode:

- Removing the cause of the CSN stuck

- Toggling the CSN pin for a min t<sub>SHCH</sub> (time to release the SDO line), see parameter in Table 38. Dynamic characteristics

- Sending the SPI frames

If the above procedure is not respected, the first SPI frame will be rejected and the state transition will be failed.

### 2.2.4 Normal mode

In this mode, all device functions are available. The transition to this mode is only possible from a previous failsafe mode.

Outputs can be driven by SPI commands, EMx emergency pins and direct inputs DIx (according to DIENCRx bits).

To maintain the device in normal mode, the watchdog toggle bit in register SOCR has to be toggled within the watchdog timeout period  $t_{WBTB}$  (see Table 38. Dynamic characteristics).

Diagnostic is available through the SPI bus (digital).

The protections are fully functional. The outputs are set to latch-off mode, except for capacitive charge mode that is always set to auto-restart mode for a time t\_ccm\_cycle. Latched-off fault diagnostics is delivered to LATCH\_DIAGx pin (open drain). Once channels are latched-off, the relevant status register has to be cleared to switch them on again.

The device enters in normal mode under one condition:

- If it is in fail-safe mode and the SPI sends the goto normal mode sequence:

- In a first communication set bit UNLOCK = 1 Write "CTRL" 0x4001;

- In the consecutive communication set bit GOSTBY = 0 and bit EN = 1 Write "CTRL" 0x0801;

#### Transition from fail-safe mode to normal mode is performed by two special SPI sequences

- Frame 1: Write "CTRL" 0x4001

- Frame 2: Write "CTRL" 0x0801

Table 5. Frame 1 (Write CTRL 0x4001)

|       | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|-------|----------|----------|----------|----------|----------|----------|----------|----------|

| CMD   | OC1      | OC0      | Address  |          |          |          |          |          |

| CMD   | 0        | 0        | 0        | 0        | 0        | 0        | 1        | 0        |

| DATA1 | GOSTBY   | UNLOCK   | CTDTH1   | CTDTH0   | EN       | Not used | Not used | Not used |

| DAIAI | 0        | 1        | 0        | 0        | 0        | 0        | 0        | 0        |

| DATAS | Not used | LOCKEN0  | Not used | Parity   |

| DATA2 | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 1        |

DS14483 - Rev 3 page 9/74

<sup>1.</sup> X: do not care. At least one of these bits must be zero, as 0xFFFF frame is not allowed.

|       | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|-------|----------|----------|----------|----------|----------|----------|----------|----------|

| CMD   | OC1      | OC0      |          |          | Ado      | dress    |          |          |

| CIVID | 0        | 0        | 0        | 0        | 0        | 0        | 1        | 0        |

| DATA1 | GOSTBY   | UNLOCK   | CTDTH1   | CTDTH0   | EN       | Not used | Not used | Not used |

| DAIAI | 0        | 0        | 0        | 0        | 1        | 0        | 0        | 0        |

| DATA2 | Not used | LOCKEN0  | Not used | Parity   |

|       | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 1        |

Table 6. Frame 2 (Write CTRL 0x0801)

The device exits normal mode under the following conditions:

- If V<sub>REG</sub> falls below V<sub>POR</sub>, the device enters standby mode.

- If the SPI sends the goto pre-standby sequence, the device enters pre-standby mode:

- In a first communication set bit UNLOCK = 1 and bit EN = 1

- In the consecutive communication set bit GOSTBY = 1 and bit EN = 0

This mechanism avoids entering pre-standby mode unintentionally.

- If the SPI clears the EN bit (EN = 0), the device enters fail-safe mode.

- Watchdog timeout: if WDTB is not toggled within the monitoring timeout period t<sub>WDTB</sub>, the device enters fail-safe mode.

- If the SPI sends a SW reset command (command byte = 0xFFh), all registers are cleared and the device enters fail-safe mode.

- If LH (limp-home) pin is set to high for t > t<sub>LH</sub> the device enters fail-safe mode.

## 2.2.5 Pre-standby mode

Usually, pre-standby mode is an intermediate state towards standby mode.

The outputs are in off state.

The diagnostics is available.

The protections are active.

The SPI communication is active.

The registers are available for R/W.

Once counters elapse (I²t counters and t\_stdby\_en), the device switches from pre-standby mode to standby mode if:

• (DI0 AND DI1) low AND (CSN high OR VDD low) AND  $V_{REG} < V_{POR}$

The device enters pre-standby mode under the following conditions:

- From fail-safe mode if DI0 low AND DI1 low AND (CSN high OR VDD low) for t > t prestdby

- From normal mode if the SPI sends the goto pre-standby mode sequence:

- In a first communication set UNLOCK = 1 and EN = 1

- In the consecutive communication set GOSTBY = 1 and EN = 0

This mechanism avoids entering pre-standby mode unintentionally.

The device exits pre-standby mode and switches back to fail-safe mode, if I²t counters are not zero and t\_stdby\_en is not elapsed, under the following condition:

• (DI0 OR DI1) high OR (CSN low AND VDD high)

The device leaves pre-standby to standby mode, if I2t counters and t stdby en are elapsed and:

(DI0 AND DI1) low AND (CSN high OR VDD low)

Transition from normal mode to pre-standby mode using SPI: two frames needed.

- Frame 1: write "CTRL"0x4800

- Frame 2: write "CTRL"0x8001

DS14483 - Rev 3 page 10/74

|   |       |       | -     | <del>-</del> |       |       | _     |  |

|---|-------|-------|-------|--------------|-------|-------|-------|--|

|   | Bit 7 | Bit 6 | Bit 5 | Bit 4        | Bit 3 | Bit 2 | Bit 1 |  |

| n | OC1   | OC0   |       |              | Ado   | dress |       |  |

Table 7. Frame 1 (write CTRL 0x4800)-Normal mode to pre-standby mode

Bit 0 CMD 0 0 0 0 0 0 0 **GOSTBY UNLOCK** CTDTH1 CTDTH0 ΕN Not used Not used Not used DATA1 0 0 1 Λ 0 1 Λ Λ LOCKEN0 Not used Not used Not used Not used Not used Not used Parity DATA2 0 0 0 0 0

Table 8. Frame 2 (write CTRL 0x8001)-Normal mode to pre-standby mode

|       | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|-------|----------|----------|----------|----------|----------|----------|----------|----------|

| CMD   | OC1      | OC0      |          |          | Add      | dress    |          |          |

| CIVID | 0        | 0        | 0        | 0        | 0        | 0        | 1        | 0        |

| DATA1 | GOSTBY   | UNLOCK   | CTDTH1   | CTDTH0   | EN       | Not used | Not used | Not used |

| DAIAI | 1        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| DATAS | Not used | LOCKEN0  | Not used | Parity   |

| DATA2 | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 1        |

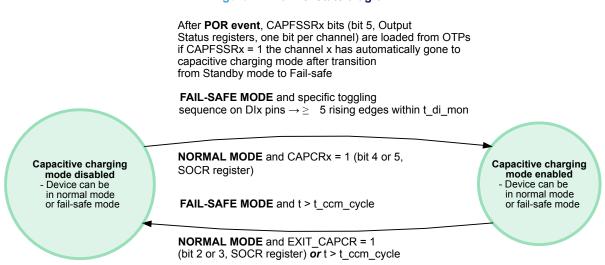

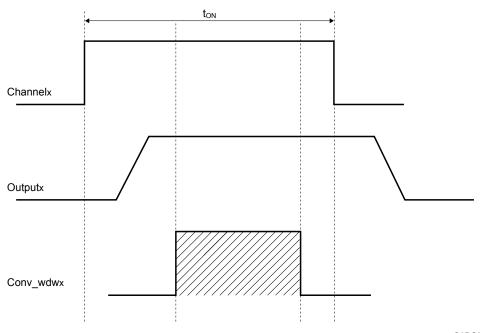

#### 2.3 Capacitive charging mode

It is not a device state but a channel state.

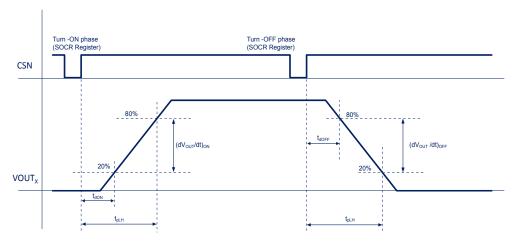

When the channel is set to this mode, a specific procedure, allowing auto-restart after I<sub>PFAK</sub> detection, allows to charge a capacitive load within the maximum required time (t ccm cycle), see Figure 4. Channel state diagram. The device enters this specific channel mode under the following conditions:

- In normal mode, if a specific SPI frame is sent: set CAPCRx bit localized in SOCR register (position 4 and 5) to high value, the bit is automatically reset and acts as a trigger

- In fail-safe mode, after POR, if OTP bit CAPFSSRx is set

- In fail-safe mode if a specific toggling sequence to DIx pins is applied: at least 5 rising edges on DIx pins within t < t\_di\_mon

The device exits this specific channel mode under the following conditions:

- In normal mode, if a specific SPI frame is sent: set EXIT CAPCRx bit in SOCR register (position 2 and 3)

- In normal mode, if t ccm cycle is elapsed

- In fail-safe mode, if t ccm cycle is elapsed

The capacitive charging mode charges capacitors with a burst of low frequency IPEAK pulses, provided that the total impedance is low enough to reach IPEAK when charging the capacitor. If IPEAK is not reached, the capacitor is charged with a single continuous charging pulse. In this specific channel operating mode, the device can distinguish a capacitor load from a short circuit.

DS14483 - Rev 3 page 11/74

When a channel is set in capacitive charging mode and the output stage is turned on, an autorestart procedure is started first in a low frequency mode. If the ESR of the connected capacitor and the total output line impedance is low enough to let the channel reach its  $I_{PEAK}$  value, the channel will turn off after  $t_{filter}$  jeeak filter time elapsed and remain off for a  $t_{LF}$  period. At the end of the  $t_{FL}$  period the device samples the output voltage of the channel in capacitive charging mode. As long as the output voltage remains below VOUT\_THR and the number of low frequency charging cycles remains below the MAX\_COUNTER\_LF threshold, the device remains in low frequency mode and will turn on its output again. The channel exits from the low frequency charging mode, as soon as VOUT\_THR threshold is exceeded or MAX\_COUNTER\_LF is reached. In the latter case, the channel will latch off for short circuit detection and the status flag IPEAKLSRx in OUTSRx register – Channel Feedback Status bit and in the Global Status Byte will be set. Otherwise, the channel enters a high frequency charging mode (with a period equal to  $t_{HF}$ ) and continues to charge the capacitor with a burst of  $t_{PEAK}$  pulses, provided that the line impedance is still low enough to let the channel reach  $t_{PEAK}$ . After each  $t_{PEAK}$  pulse, the channel will turn off after  $t_{TEAK}$  filter time elapsed and remains off for a  $t_{TEAK}$  period. The process will be continued till the threshold MAX\_COUNTER\_LF is reached,  $t_{TEAK}$  elapsed or CCM is aborted through SPI command.

Figure 4. Channel state diagram

DS14483 - Rev 3 page 12/74

## 3 Protections

## 3.1 Thermal case temperature monitoring and pre-warning

Case-temperature is constantly monitored via a 10-bit ADC converter and data is available through T<sub>CASE</sub> register (0x27h).

Case-temperature diagnostic is available through the global status byte. Temperature threshold is programmable via the control register (4 levels). T<sub>CASE</sub> is cleared automatically when the case-temperature drops below the case-temperature threshold.

## 3.2 Junction overtemperature (OT)

If the junction temperature of one channel rises above the shutdown temperature  $T_{TSD}$ , an overtemperature event (OT) is detected.

In normal mode, the channel is switched OFF and the corresponding bit in the OUTSRx register-channel feedback status register (OTSRx) is set. Consequently, the thermal shutdown bit (bit 4) in the global status byte and the global error flag are set. LATCH\_DIAGx open drain pin is set low if OTMASK = 0.

The output remains switched OFF until the junction temperature falls below  $T_R$  and the MCU resets the latch-off event by clearing the OTSRx bit in the channel status register. The bit 4 in the global status byte register is cleared and the LATCH DIAGx pin is released.

In fail-safe mode, the channel is switched OFF and the corresponding bit in the OUTSRx register-channel feedback status bit (OTSRx) is set. Consequently, the thermal shutdown bit (bit 4) in the global status byte and the global error flag are set. LATCH\_DIAGx open drain pin is set low.

The output remains switched OFF until the junction temperature falls below T<sub>R</sub> and the latch is reset either by toggling the corresponding DIx pin or by clearing OTSRx bit by the MCU. The action clears the OTSRx bit in the channel status register and the corresponding bit 4 in the global status byte. LATCH DIAGx pin is released.

# 3.3 Overcurrent protection (I<sub>PEAK</sub>)

In case of short circuit, the channel is protected by switching OFF if the current rises above the overcurrent threshold ( $I_{PEAK}$ ) for a time longer than t\_filter\_ipeak. In addition, another filter (analog) is applied only after turn on (8  $\mu$ s typ.).

I<sub>PEAK</sub> protection is configured to operate in latched OFF mode.

In normal mode, once a fault is detected, the corresponding channel is turned OFF, both fault bits (IPEAKLSRx and ITLOFFSRx) in the channel status register (OUTSRx) are set, bits 2 and 3 in the global status byte are set, and diagnostic is delivered (if IPEAKMASK = 0 and I2TMASK = 0) to the LATCH\_DIAGx pin for safety purposes. Fault can be reset by clearing the fault bits, IPEAKLSRx and ITLOFFSRx; bits 2 and 3 in the global status byte are cleared and the LATCH\_DIAGx pin is released.

In fail-safe mode, once a fault is detected, the corresponding channel is turned OFF, both fault bits (IPEAKLSRx and ITLOFFSRx) in the channel status register (OUTSRx) are set, bits 2 and 3 in the global status byte are set high, and diagnostic is delivered to LATCH\_DIAGx pin for safety purposes. Fault can be reset either by toggling the corresponding DIx pin or by clearing fault bits (IPEAKLSRx). Fault bit (IPEAKLSRx and ITLOFFSRx) are cleared, bits 2 and 3 in the global status byte are cleared and LATCH\_DIAGx pin is released.

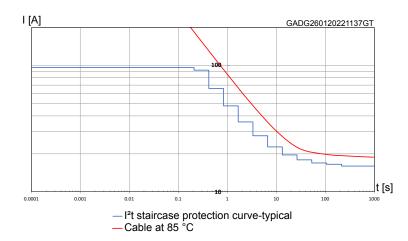

# 3.4 Electronic harness protection (STi<sup>2</sup>Fuse)

The electronic wire harness protection, I²t protection, is active in all operating modes, except in standby mode when the device is in lowest quiescent current consumption mode and all analog and digital functions are in idle mode and output stages are off. In all conditions, the wire harness protection works fully autonomous and in particular does not require any MCU control or supervision. A specific digital I²t current sense register ADCI2tSRx allows to readback the value of the current monitored by the I²t protection block at any time during on-state of the channel. In the ITCNTSR register, the current value of the integrated I²t budget is reported (ITCNTx bits) and allows the application to monitor how much of the available I²t budget is actually consumed.

DS14483 - Rev 3 page 13/74

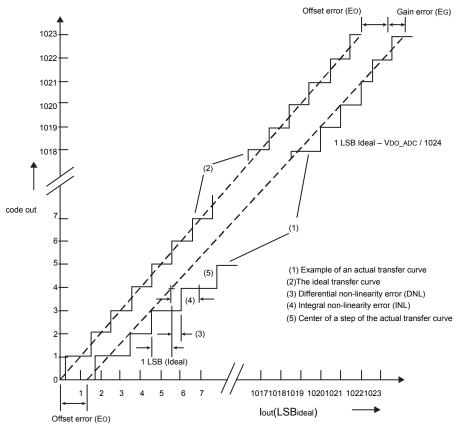

The I²t protection is based on a continuous RMS output current calculation with a dedicated current sense block for each channel and linearity guaranteed up to  $I_{PEAK}$  value. Current sense for I²t calculation is sampled for each channel every  $t_{I}^2$  SAMPLE. The shape of the actual I²t protection curve is a staircase curve, which is determined by two configurable parameters,  $I_{NOM}$  and  $t_{NOM}$ . Both parameters are accessible through SPI, read and writeable. Default values of  $I_{NOM}$  and  $t_{NOM}$  are stored in a user-accessible area of the OTP (one time programmable memory) with a dual programming option. The user can select any combination of the  $I_{NOM}$  and  $t_{NOM}$  values reported in the below table.

Table 9. Typical values of configurable I<sub>NOM</sub>

| I <sub>NOM</sub> [A] | INOM2 | INOM1 | INOM0 |

|----------------------|-------|-------|-------|

| 10<br>(default)      | 0     | 0     | 0     |

| 11                   | 0     | 0     | 1     |

| 15                   | 0     | 1     | 0     |

| 17.5                 | 0     | 1     | 1     |

| 20                   | 1     | 0     | 0     |

| 26                   | 1     | 0     | 1     |

| 28.5                 | 1     | 1     | 0     |

| 33.5                 | 1     | 1     | 1     |

Table 10. Typical values of configurable t<sub>NOM</sub>

| t <sub>NOM</sub> [s] | TNOM2 | TNOM1 | TNOM0 |

|----------------------|-------|-------|-------|

| 300<br>(default)     | 0     | 0     | 0     |

| 257                  | 0     | 0     | 1     |

| 214                  | 0     | 1     | 0     |

| 172                  | 0     | 1     | 1     |

| 129                  | 1     | 0     | 0     |

| 86                   | 1     | 0     | 1     |

| 44                   | 1     | 1     | 0     |

| 1                    | 1     | 1     | 1     |

The value of  $I_{NOM}$  represents the level of steady state current, which can be accepted for infinite time in the system consisting of IC, routing, connectors, wiring, and load. The value of  $t_{NOM}$  specifies the speed how fast the staircase curve reaches  $I_{NOM}$  value. The following Figure 5 depicts the I²t staircase protection curve with a configuration of  $I_{NOM}$  = 15 A and  $t_{NOM}$  = 214 s and for comparison the I-t isothermic curve of a wire with 1 mm² cross-section at  $T_A$  = 85 °C heating up to 150 °C. As it can be seen, the I²t staircase protection curve is always left and below the wire isothermic curve, which means the I²t protection algorithm protects the wire from carrying an RMS current, which would lead to a higher temperature increase than the one of the isothermic curve.

DS14483 - Rev 3 page 14/74

Figure 5. I<sup>2</sup>t staircase protection curve

with  $I_{NOM}$  = 15 A and  $t_{NOM}$  = 214 s vs a 1 mm<sup>2</sup> wire isothermic curve

The I²t protection curve can be moved in y-direction by changing the  $I_{NOM}$  value and in x-direction changing the  $t_{NOM}$  value. The following Figure  $6^{(1)}$  and Figure  $7^{(1)}$  represent the total range of I²t the device can cover, ranging from  $I_{NOM\_min} = 10$  A with  $t_{NOM\_min} = 1$  s up to  $I_{NOM\_max} = 33.5$  A with  $t_{NOM\_max} = 300$  s.

Figure 6. Lowest I<sub>NOM</sub> and t<sub>NOM</sub> configuration setting

\*\*Property of the state o

Figure 7. Highest I<sub>NOM</sub> and t<sub>NOM</sub> configuration setting

OADCQ26012022133GT

GADCQ26012022133GT

GADCQ26

1. To be intended as example of the protection behavior.

The I²t protection curve consists of 13 steps, each of them corresponding to a specific current threshold. Whenever the load current exceeds a threshold, a counter is counting up. If for instance, looking at the example of Figure 5 the current would exceed the value of  $I_{NOM} = 15$  A, but stay below the current threshold of the next step, which is set at  $1.03*I_{NOM}$  about, the counter would reach its threshold value after  $t_{NOM} = 214$  s, the harness protection is triggered and the output channel is automatically latched off. In normal mode, the ITLOFFSRx bit is set high and bit 3 in the global status byte is set. Diagnostic is also available through LATCH\_DIAGx pin (I2TMASK = 0 via SPI programming). The fault can be unlatched by resetting the fault status bit, ITLOFFSRx, in the channel status register (OUTSRx). Bit 3 in the global status byte is cleared and LATCH\_DIAGx pin is released after the time TF\_UNLATCH.

In fail-safe mode, once the harness protection is triggered the bit 3 in the global status byte is set. Diagnostic is available through LATCH\_DIAGx pin (pulled down). The fault can be unlatched by toggling the corresponding DIx pin, and LATCH\_DIAGx pin is released after the time TF\_UNLATCH\_DIX\_TOGGLE. The ITLOFFSRx bit and bit 3 in the global status byte will remain set and can be clear only via SPI.

DS14483 - Rev 3 page 15/74

The speed of the counter is increased every time the load current reaches the next staircase current threshold of the I²t curve. Every time the load current drops below the  $I_{NOM}$  threshold the counter is decreasing. The speed of the down-counting depends on how far the load current is below the  $I_{NOM}$ . This algorithm perfectly emulates a continuous RMS–root mean square–current integration, which in fact is the proper indicator to measure the losses in the wire by the Joule effect, causing the temperature rise in the wire. The last  $(13^{th})$  step of the I²t protection staircase curve is equal to  $10^*I_{NOM}$ . Whenever the load current exceeds the  $13^{th}$  threshold, the output channel is latched off immediately within  $t_{doff} + t_f$ , protecting the integrity of the boardnet power supply.

In case the application requires a high I<sub>NOM</sub>, but at the same time a fast protection against high-transient currents is required, the highest value of the I²t staircase protection curve can be selected between 10\*I<sub>NOM</sub> and 6\*I<sub>NOM</sub>. The default value can be configured in the OTP memory map through the INOMx\_6X\_10X bit. In normal mode, the configuration can be changed through SPI by writing to INOMx\_6X\_10X bit in the I²t configuration control register.

The Figure 8 shows the shape of the I²t staircase protection curve with configuration values as in the Figure 5, but with the highest threshold reduced to 6\*I<sub>NOM</sub>.

Figure 8. I2t staircase protection curve

with I<sub>NOM</sub> = 15 A and t<sub>NOM</sub> = 214 s vs a 1 mm<sup>2</sup> wire isothermic curve with maximum threshold reduced to 6\*I<sub>NOM</sub>

In case of short battery glitches an external capacitor (100 nF) connected to VREG pin supplying digital part prevents logic reset and fuse counter reset. I<sup>2</sup>t protection continues to protect efficiently the harness in these conditions.

DS14483 - Rev 3 page 16/74

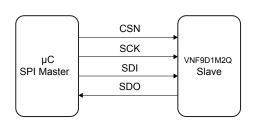

# 4 SPI functional description

## 4.1 SPI communication

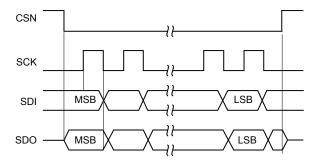

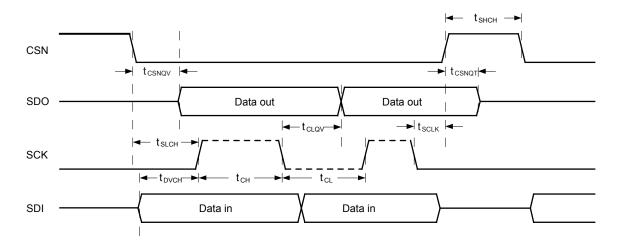

The SPI communication is based on a standard ST-SPI 24-bit interface, using CSN, SDI, SDO and SCK signal lines

Input data are shifted into SDI, MSB first while output data are shifted out on SDO, MSB first.

## 4.1.1 Signal description

During all operations,  $V_{DD}$  must be held stable and within the specified valid range:  $V_{DD}$  min. to  $V_{DD}$  max.

Table 11. SPI signal description

| Name                         | Function                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

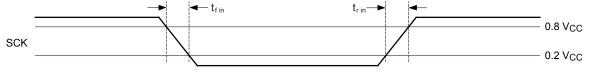

| Serial clock SCK             | This input signal provides the timing of the serial interface. Data present at serial data input (SDI) are latched on the rising edge of serial clock (SCK). Data on serial data output (SDO) change after the falling edge of serial clock (SCK).                                                                                                                                    |  |  |  |  |  |  |  |

| Serial data input SDI        | This input signal is used to transfer data serially into the device. It receives data to be written. Values are sampled on the rising edge of serial clock (SCK).                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

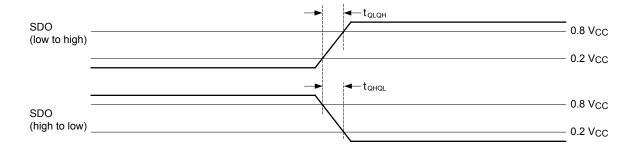

| Serial data<br>output<br>SDO | his output signal is used to transfer data serially out of the device. Data are shifted out on the falling edge of erial clock (SCK).                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                              | When this input signal is high, the device is deselected and serial data output (SDO) is high impedance. Driving this input low enables the communication. The communication must start on a low level of serial clock (SCK). Data are accepted only if exactly 24 bits have been shifted in.                                                                                         |  |  |  |  |  |  |  |

|                              | Note: as per the ST_SPI standard, in case of failing communication:                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|                              | CSN stuck at high:                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Chip select<br>CSN           | <ul> <li>If the device is in normal mode, a WDTB timeout will force the device into fail-safe mode. The serial data output (SDO) will stay in high impedance (High Z).         Any valid communication arrived after this event will be accepted by the device.     </li> <li>CSN stuck at low:</li> </ul>                                                                            |  |  |  |  |  |  |  |

|                              | <ul> <li>in this case and whatever the mode of the device, a CSN timeout protection will be activated and<br/>force the device to release the SPI bus. Then the serial data output (SDO) will go into high<br/>impedance (High Z)</li> </ul>                                                                                                                                          |  |  |  |  |  |  |  |

|                              | A reset of the CSN timeout (see T <sub>SHCH</sub> in the Table 3) is activated with a transition low to high on CSN pin (or with a Power-on Reset or Software reset). With this reset, the serial data output (SDO) will be released and any valid communication will be accepted by the device. Without this reset, next communication will not be taken into account by the device. |  |  |  |  |  |  |  |

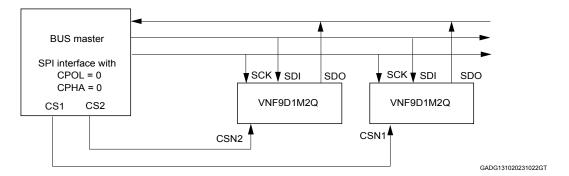

## 4.1.2 Connecting to the SPI bus

A schematic view of the architecture between the bus and devices can be seen in Figure 10.

All input data bytes are shifted into the device, MSB first. The serial data input (SDI) is sampled on the first rising edge of the serial clock (SCK) after chip select (CSN) goes low. All output data bytes are shifted out of the device on the falling edge of SCK, MSB first on the first falling edge of the chip select (CSN).

DS14483 - Rev 3 page 17/74

## 4.1.3 SPI mode

Supported SPI mode during a communication phase can be seen in the following figure:

Figure 9. Supported SPI mode

This device can be driven by a micro controller with its SPI peripheral running in the following mode:

CPOL = 0, CPHA = 0

Figure 10. Bus master and two devices in a normal configuration

DS14483 - Rev 3 page 18/74

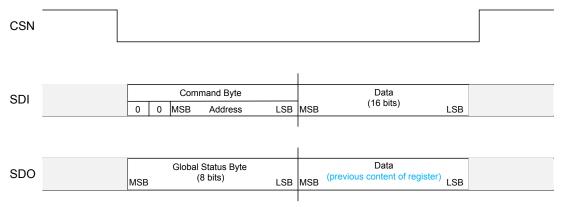

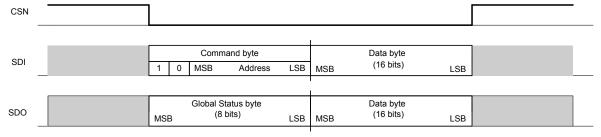

## 4.2 SPI protocol

## 4.2.1 SDI, SDO format

SDI format during each communication frame starts with a command byte. It begins with two bits of operating code (OC0, OC1) which specify the type of operation (read, write, read and clear status, read device information) and it is followed by a 6-bit address (A0:A5). The command byte is followed by two input data bytes (D15:D8) and (D7:D0).

Table 12. Command byte

| MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |

|-----|-------|-------|-------|-------|-------|-------|-----|

| OC1 | OC0   | A5    | A4    | A3    | A2    | A1    | A0  |

Table 13. Input data byte 1

| MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |

|-----|-------|-------|-------|-------|-------|-------|-----|

| D15 | D14   | D13   | D12   | D11   | D10   | D9    | D8  |

Table 14. Input data byte 2

| MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB               |

|-----|-------|-------|-------|-------|-------|-------|-------------------|

| D7  | D6    | D5    | D4    | D3    | D2    | D1    | D0 <sup>(1)</sup> |

#### 1. D0 is the parity bit.

SDO format during each communication frame starts with a specific byte called global status byte (see Table 15 for more details of bit0-bit7). This byte is followed by two output data bytes (D15:D8) and (D7:D0).

Table 15. Global status byte

| MSB  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB  |

|------|-------|-------|-------|-------|-------|-------|------|

| bit7 | bit6  | bit5  | bit4  | bit3  | bit2  | bit1  | bit0 |

## Table 16. Output data byte 1

| MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |

|-----|-------|-------|-------|-------|-------|-------|-----|

| D15 | D14   | D13   | D12   | D11   | D10   | D9    | D8  |

## Table 17. Output data byte 2

| MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |

|-----|-------|-------|-------|-------|-------|-------|-----|

| D7  | D6    | D5    | D4    | D3    | D2    | D1    | D0  |

DS14483 - Rev 3 page 19/74

## 4.2.2 Operating code definition

The SPI interface features four different addressing modes which are listed in Table 18. Operating codes.

Table 18. Operating codes

| OC1 | OC0 | Meaning                         |  |  |  |

|-----|-----|---------------------------------|--|--|--|

| 0   | 0   | Write operation                 |  |  |  |

| 0   | 1   | Read operation                  |  |  |  |

| 1   | 0   | Read and clear status operation |  |  |  |

| 1   | 1   | Read device information         |  |  |  |

#### Write mode

The write mode of the device allows to write the content of the input data byte into the addressed register (see list of registers in Table 23. RAM memory map). Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first.

During the same sequence the outgoing data are shifted out MSB first on the falling edge of the CSN pin and the subsequent bits on the falling edge of the serial clock (SCK). The first byte corresponds to the global status byte and the second to the previous content of the addressed register.

Figure 11. SPI write operation

GADG311020171214MT

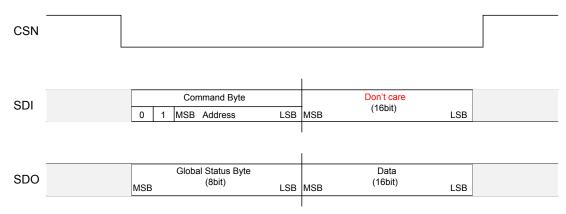

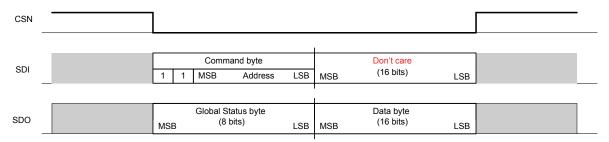

#### Read mode

The read mode of the device allows to read and to check the state of any register.

Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first.

The command byte allows to determine which register content is read, whilst the other two data bytes are "don't care".

In case of a read mode on an unused address, the global status/error byte on the SDO pin is followed by 0x0000 word.

In order to avoid inconsistency between the global status byte and the Status register, the Status register contents are frozen during the SPI communication.

DS14483 - Rev 3 page 20/74

Figure 12. SPI read operation

GADG311020171215MT

#### Read and clear status command

The read and clear status operation is used to clear the content of the addressed status register (see Table 23. RAM memory map). A read and clear status operation with address 0x3Fh clears all Status registers simultaneously.

Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first. The command byte allows to determine which register content is read and the payload bits set to 1 into the data byte determine the bits into the register which have to be cleared.

Outgoing data are shifted out MSB first on the falling edge of the CSN pin and others on the falling edge of the serial clock (SCK). The first byte corresponds to the global status byte and the second to the content of the addressed register.

In order to avoid inconsistency between the global status byte and the Status register, the Status register contents are frozen during SPI communication.

Figure 13. SPI read and clear operation

GADG1010171505PS

#### Read device information

Specific information can be read but not modified during this mode. Accessible data can be seen in Section 4.3.3: ROM.

Incoming data are sampled on the rising edge of the serial clock (SCK), MSB first. The command byte allows to determine which information is read whilst the other two data bytes are "don't care".

Outgoing data are shifted out MSB first on the falling edge of the CSN pin and others on the falling edge of the serial clock (SCK). The first byte corresponds to the global status byte and the second to the content of the addressed register and the third byte is 0x00.

Note:

ROM is based on the 8-bit registers, then even if 16 bits are returned, only the second byte contains the addressed ROM register.

DS14483 - Rev 3 page 21/74

Figure 14. SPI read device information

GADG1010171521PS

## 4.2.3 Special commands

## 0xFF - SW-Reset: set all control registers to default

An OpCode '11' (read device information) addressed at '111111' forces a software reset of the device, second and third bytes are "don't care" provided that at least one bit is zero.

Note:

An OpCode '11' at address '111111' with data field equal to '11111111111111' on the SPI frame is recognized as a frame error and the SPIE bit of GSB is set.

Table 19. 0xFF: SW\_Reset

| Bit 7           | Bit 6            | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|-----------------|------------------|-------|-------|-------|-------|-------|-------|--|--|--|

|                 | Command          |       |       |       |       |       |       |  |  |  |

| OC1 OC0 Address |                  |       |       |       |       |       |       |  |  |  |

| 1               | 1                | 1     | 1     | 1     | 1     | 1     | 1     |  |  |  |

| DATA1           | X <sup>(1)</sup> | Х     | X     | X     | Х     | Х     | Х     |  |  |  |

| DAIAI           | 0                | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |

| DATA2           | X                | Х     | X     | Х     | Х     | Х     | Х     |  |  |  |

| DATAZ           | 0 0 0 0 0        |       |       |       |       |       |       |  |  |  |

1. X: do not care.

## 0xBF - clear all status registers (RAM access)

When an OpCode '10' (read and clear operation) at address b'111111 is performed.

Table 20. Clear all status registers (RAM access)

| Bit 7 | Bit 6            | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|-------|------------------|-------------|-------|-------|-------|-------|-------|--|--|--|

|       | Command          |             |       |       |       |       |       |  |  |  |

| OC1   | OC0              | OC0 Address |       |       |       |       |       |  |  |  |

| 1     | 0                | 1           | 1     | 1     | 1     | 1     | 1     |  |  |  |

| DATA1 | X <sup>(1)</sup> | Х           | Х     | X     | X     | Х     | Х     |  |  |  |

| DAIAI | 0                | 0           | 0     | 0     | 0     | 0     | 0     |  |  |  |

| DATA2 | Х                | Х           | Х     | Х     | Х     | X     | Х     |  |  |  |

| DATAZ | 0                | 0           | 0     | 0     | 0     | 0     | 0     |  |  |  |

1. X: do not care.

Note: Reset value = the value of the register after a power on.

Default value = the default value of the register. Currently this is equivalent to the reset value.

Cleared register = explicitly read and clear of the register, if it is not write protected.

DS14483 - Rev 3 page 22/74

## 4.3 Register map

The device contains a set of RAM and ROM registers. The RAM registers are used for device configuration and device status while ROM registers are used for device identification. Since ST-SPI is used, the global status byte defines the device status, containing fault information.

### 4.3.1 Global status byte description

The data shifted out on SDO during each communication starts with a specific byte called global status byte. This one is used to inform the microcontroller about global faults, which can happen at channel-side level (that is like thermal shutdown, OLOFF...) or on the SPI interface (like watchdog monitoring timeout event, communication error,...). This specific register has the following format:

Table 21. Global status byte (GSB)

| MSB  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2                    | Bit 1               | LSB |

|------|-------|-------|-------|--------|--------------------------|---------------------|-----|

| GSBN | RSTB  | SPIE  | TSD   | ITLOFF | I <sub>PEAK_DETECT</sub> | Bit1 <sup>(1)</sup> | FS  |

1. Bit1 in GSB is defined as T<sub>CASE</sub> OR V<sub>CC\_UV</sub> OR V<sub>CC\_OV</sub>.

Table 22. Global status byte description

| Bit | Name                                                             | Reset | Content                                                                                                                                                                                                   |

|-----|------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Global status bit not                                            | 0     | The GSBN is a logically NOR combination of bit0 to bit6. This bit can also be used as global status flag without starting a complete communication frame as it is present directly after pulling CSN low. |

| 6   | Reset bit                                                        |       | The RSTB indicates a device reset. In case this bit is set, all internal control registers are set to default and kept in that state until the bit is cleared.                                            |

|     |                                                                  |       | The reset bit is automatically cleared by any valid SPI communication                                                                                                                                     |

|     |                                                                  |       | The SPIE is a logical OR combination of errors related to a wrong SPI communication (SCK count and SDI stuck at errors).                                                                                  |

| 5   | SPI error                                                        | 0     | The SPIE bit is automatically set when SDI is stuck at high or Low.                                                                                                                                       |

|     |                                                                  |       | The SPIE is automatically cleared by a valid SPI communication.                                                                                                                                           |

| 4   | Thermal shutdown (OT)                                            | 0     | This bit is set in case of thermal shutdown.                                                                                                                                                              |

| 3   | ITLOFF                                                           | 0     | Logical OR combination of STi <sup>2</sup> Fuse latch for all channels.                                                                                                                                   |

| 2   | I <sub>PEAK_DETECT</sub>                                         | 0     | Logical OR combination of I <sub>PEAK</sub> detection for all channels.                                                                                                                                   |

| 1   | T <sub>CASE</sub> OR V <sub>CC_UV</sub><br>OR V <sub>CC_OV</sub> | 0     | This bit is set in case of frame temperature detection or $V_{CC}$ undervoltage or $V_{CC}$ overvoltage.                                                                                                  |

| 0   | Fail-safe                                                        | 1     | The bit is set in case device operates in fail-safe mode. A detailed description of these root-causes and the fail-safe state itself is specified in the Section 2.2.3: Fail-safe mode                    |

Note:

The FFh or 00h combinations for the global status byte are not possible, due to the active low of global status bit (bit7), exclusive combination exists between bit7 and bit0-bit6. Consequently, a FFh or 00h combination for the global status byte must be detected by the microcontroller as a failure (SDO stuck to GND or to  $V_{DD}$  or loss of SCK).

DS14483 - Rev 3 page 23/74

#### 4.3.2 RAM

RAM registers can be separated according to the frequency of usage:

- Init register is read/written during the initialization phase (single shot action)

- Continuous read/write / read and clear registers are often accessed, applying outputs control and diagnostic

- Rare read/read and clear status of device registers accessed on demand (in case of failure)

Table 23. RAM memory map

| Address | Name      | Access     | Content                                     | Access type | Reset value |

|---------|-----------|------------|---------------------------------------------|-------------|-------------|

|         |           |            | CONTROL REGISTERS                           |             |             |

| 01h     | SOCR      | Read/Write | Channel control register                    | Init        | 0x0000      |

| 02h     | CTRL      | Read/Write | Control register                            | Init        | 0x0000      |

| 03h     | ITCFGCR0  | Read/Write | I²t configuration control register channel0 | Init        | 0x0000      |

| 04h     | ITCFGCR1  | Read/Write | I²t configuration control register channel1 | Init        | 0x0000      |

|         |           |            | not used area                               |             |             |

|         |           |            | STATUS REGISTERS                            |             |             |

| 10h     | OUTSR0    | Read/Clear | Output status register channel0             | rare        | 0x0000      |

| 11h     | OUTSR1    | Read/Clear | Output status register channel1             | rare        | 0x0000      |

|         |           |            | not used area                               |             |             |

| 12h     | ITCNTSR   | Read       | I²t counter status register                 | rare        | 0x0000      |

| 20h     | ADCISR0   | Read       | Digital current sense channel0              | continuous  | 0x0000      |

| 21h     | ADCISR1   | Read       | Digital current sense channel1              | continuous  | 0x0000      |

| 22h     | ADCI2TSR0 | Read       | Digital current sense for I²t channel0      | continuous  | 0x0000      |

| 23h     | ADCI2TSR1 | Read       | Digital current sense for I²t channel1      | continuous  | 0x0000      |

| 24h     | ADCVSR0   | Read       | Digital output voltage channel0             | continuous  | 0x0000      |

| 25h     | ADCVSR1   | Read       | Digital output voltage channel1             | continuous  | 0x0000      |

| 26h     | ADCVBSR   | Read       | Digital battery voltage                     | continuous  | 0x0000      |

| 27h     | ADCVTSR   | Read       | Digital frame temperature sense             | continuous  | 0x0000      |

| 3Dh     |           |            | RESERVED                                    |             |             |

| 3Eh     |           |            | RESERVED                                    |             |             |

Note:

Any command (write, read, or read and clear status) executed on a "not used" RAM register that is a not assigned address does not have any effect: there is no change in the global status byte (no communication error, no error flag). The data written to this address is ignored. The data read from this address contains 00, independently of what has been written previously to this address.

A write command on "don't care" bits of an assigned RAM register address does not have any effect: There is no change on the global status byte. The data written to the "don't care bits" is ignored. The content of the "don't care bits" remains at "0" independently of the data written to these bits.

DS14483 - Rev 3 page 24/74

#### 4.3.3 ROM

This memory is used for device identification.

Table 24. ROM memory map

| Address | Name              | Description                                                        | Access    | Content |

|---------|-------------------|--------------------------------------------------------------------|-----------|---------|

| 00h     | Company code      | Indicates the code of STM company                                  | Read only | 00H     |

| 01h     | Device family     | Indicates the product family                                       | Read only | 03H     |

| 02h     | Product code 1    | Indicates the first code of the product                            | Read only | 58H     |

| 03h     | Product code 2    | Indicates the 2nd code of the product                              | Read only | 56H     |

| 04h     | Product code 3    | Indicates the third code of the product                            | Read only | 06H     |

| 05h     | Product Code 4    | Indicates the fourth code of the product                           | Read only | 42H     |

| 0Ah     | Version           | Silicon version                                                    | Read only | 01H     |

|         |                   | not used area                                                      |           |         |

| 10h     | SPI Mode          | Different Modes of the SPI (see SPI mode)                          | Read only | A1H     |

| 11h     | WD Type 1         | Indicates the type of watchdog used in the product                 | Read only | 46H     |

| 13h     | WD bit position 1 | Indicates the address of the register containing the WD toggle bit | Read only | 40H     |

| 14h     | WD bit position 2 | Indicates the position of the WD toggle bit                        | Read only | C1H     |

|         |                   | not used area                                                      |           |         |

| 20h     | SPI CPHA          | Indicates the polarity and phase of the SPI interface              | Read only | 55H     |

| 3Eh     | GSB options       | Options of GSB byte (standard GSB definition)                      | Read only | 00H     |

| 3Fh     | Advanced OP. Code | Access to this address results in a SW reset                       |           |         |

## 4.3.4 SPI modes

By reading out the <SPI mode> register general information of SPI usage of the device application registers can be read.

Table 25. SPI mode

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Content |

|-------|-------|-------|-------|-------|-------|-------|-------|---------|

| BR    | DL2   | DL1   | DL0   | SPI8  | 0     | S1    | S0    | A1H     |

#### SPI burst read

Table 26. SPI burst read

| Bit 7 | Description |

|-------|-------------|

| 0     | BR disabled |

| 1     | BR enabled  |

The burst read is implemented in this product so this bit is enabled.

## SPI data length

The SPI data length value indicates the length of the SCK count monitor, which is running for all the accesses to the device application registers. In case a communication frame with an SCK count is not equal to the reported one, the device leads to a SPI error and the data is rejected.

The frame length is specified on 3 bits in the SPI mode register located in the ROM part.

The 24-bit SPI communication is implemented in this product so these bits are '010'.

DS14483 - Rev 3 page 25/74

Table 27. SPI data length

| Bit 6 | Bit 5 | Bit 4 | Description |

|-------|-------|-------|-------------|

| DL2   | DL1   | DL0   | Description |

| 0     | 0     | 0     | Invalid     |

| 0     | 0     | 1     | 16-bit SPI  |

| 0     | 1     | 0     | 24-bit SPI  |

|       |       |       |             |

| 1     | 1     | 1     | 64-bit SPI  |

## Data consistency check (parity/CRC)

For some devices, a data consistency check is required. Therefore, either a parity-check or for very sensitive systems a CRC may be implemented.

It is defined on 2 bits in the SPI mode register located in the ROM part. A check is then applied on the incoming frame (SDI) while a calculation elaborated on one/multiple bits is done and integrated on the outgoing frame (SDO).

Table 28. SPI data consistency check

| Bit 61     | Bit 0 | Description |

|------------|-------|-------------|

| <b>\$1</b> | S0    | Description |

| 0          | 0     | Not used    |

| 0          | 1     | Parity used |

| 1          | 0     | CRC used    |

| 1          | 1     | Invalid     |

In case either the parity or the CRC check is implemented it is always located at the end of the communication.

The device is equipped with the parity control check. In the Tx device, the parity bit is calculated based on the first 23 bits: even number of "1" will set the parity bit to "1", while the odd number of "1" will set the parity bit to "0". In the Rx device, the parity bit is calculated in the same way and compared with the received one. In the case of different parity bit, the received SPI frame is considered as not valid and it is not executed.

DS14483 - Rev 3 page 26/74

## 4.4 Outputs control

Depending on the actual device mode, outputs can be controlled by the SPI register or the direct input DIx.

## **SPI register SOCR**

In normal mode outputs can be turned ON/OFF, applying Bit[n] = 1/0

[n]: is the related channel, n = 0 for the channel 0, and n = 1 for channel 1

## Example 1:

Turning ON channel 0 and 1

Table 29. Write SOCR 0x01

| Bit 7    | Bit 6    | Bit 5       | Bit 4    | Bit 3       | Bit 2       | Bit 1 | Bit 0  |  |  |  |  |

|----------|----------|-------------|----------|-------------|-------------|-------|--------|--|--|--|--|

|          | Command  |             |          |             |             |       |        |  |  |  |  |

| OC1      | OC0      | OC0 Address |          |             |             |       |        |  |  |  |  |

| 0        | 0        | 0           | 0        | 0           | 0           | 0     | 1      |  |  |  |  |

| D15      |          | Data 1      |          |             |             |       |        |  |  |  |  |

| Not used | Not used | Not used    | Not used | DIENCR1     | DIENCR0     | SOCR1 | SOCR0  |  |  |  |  |

| х        | х        | х           | х        | 0           | 0           | 1     | 1      |  |  |  |  |

| D7       |          |             |          | Data 2      |             |       |        |  |  |  |  |

| SPCR1    | SPCR0    | CAPCR1      | CAPCR0   | EXIT_CAPCR1 | EXIT_CAPCR0 | WDTB  | Parity |  |  |  |  |

| Х        | x        | x           | x        | x           | x           | 1/0   | 0      |  |  |  |  |

## **Direct input DIx**

Applying logical high/low to pin turns ON/OFF the associated output in fail-safe. In normal mode, DIx effect is OR-ed with SPI configuration in case DIENCR bit is set.

## **Emergency input EMx**

Setting EMx = High in normal mode will turn off the Channelx.

DS14483 - Rev 3 page 27/74

# 4.5 Control registers and Status registers

SOCR Channel control register

| 15       | 14       | 13       | 12       | 11      | 10      | 9     | 8     | 7     | 6     | 5      | 4      | 3           | 2           | 1    | 0      |

|----------|----------|----------|----------|---------|---------|-------|-------|-------|-------|--------|--------|-------------|-------------|------|--------|

| Not used | Not used | Not used | Not used | DIENCR1 | DIENCRO | SOCR1 | SOCRO | SPCR1 | SPCR0 | CAPCR1 | CAPCR0 | EXIT_CAPCR1 | EXIT_CAPCR0 | WDTB | PARITY |

| R        | R        | R        | R        | RW      | RW      | RW    | RW    | RW    | RW    | RW     | RW     | RW          | RW          | RW   | R      |

Address: 0x01h

Type: RW

Reset: 0

**Description:** Channel control register

This bit is automatically reset

| [15:12]    | Not used                                                                                                                                                       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11]        | Direct input signal enable in normal mode of channel 1                                                                                                         |

| 10]        | Direct input signal enable in normal mode of channel 0                                                                                                         |

|            | SOCR1 bit controls output state of channel 1:                                                                                                                  |

| 9]         | 1 - output enabled                                                                                                                                             |

|            | 0 - output disabled                                                                                                                                            |

|            | SOCR0 bit controls output state of channel 0:                                                                                                                  |

| 3]         | 1 - output enabled                                                                                                                                             |

|            | 0 - output disabled                                                                                                                                            |

| [7]        | Digital current sense sampling point of channel 1 (this setting is only valid for digital current sense, not for STi²Fuse digital current sense):              |

|            | 0 - continuous mode: it allows digital conversion during all ON phase of the selected channel                                                                  |

|            | 1 – filtered mode: it allows digital conversion as in continuous mode in addition to a low pass filter to filter data                                          |

|            | Digital current sense sampling point of channel 0 (this setting is only valid for digital current sense, not for STi <sup>2</sup> Fuse digital current sense): |

| 5]         | 0 - continuous mode: it allows digital conversion during all ON phase of the selected channel                                                                  |

|            | 1 – filtered mode: it allows digital conversion as in continuous mode in addition to a low pass filter to filter data                                          |

|            | Trigger for capacitive charging mode of channel 1 in normal mode:                                                                                              |

| 5]         | 1 – enables CCM in normal mode                                                                                                                                 |