# High-side switch controller with intelligent fuse protection for 12 V, 24 V and 48 V automotive applications

# West 2485 The State of the Stat

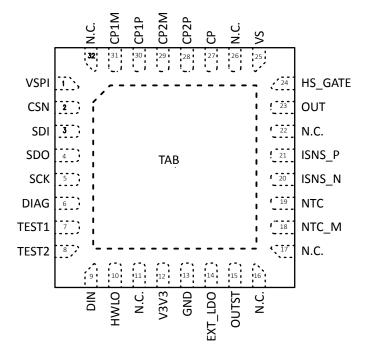

QFN32L 5X5 mm

#### **Features**

| Maximum transient supply voltage   | VS     | 70 V         |

|------------------------------------|--------|--------------|

| Operating voltage range            | VS     | 6 V to 60 V  |

| Operating voltage range (extended) | VS     | 6 V to 70 V  |

| Standby current (max.)             | IS_Q   | 75 µA        |

| SPI I/O supply voltage             | VSPI   | 3 V to 5.5 V |

| SPI standby current (max.)         | I_STBY | 5 μΑ         |

- AFC-

- General

- High-side switch control IC with e-fuse protection for automotive 12 V,

24 V and 48 V applications

- 32-bit ST-SPI interface compatible with 3.3 V and 5 V CMOS level

- 2-stage charge pump

- Gate drive for an external MOSFET in high-side configuration

- High precision uni-directional current sense through an external high side shunt resistor

- Input for a NTC resistor to monitor the external MOSFET temperature

- Very low standby current

- Device configuration lock out by a dedicated digital input pin

- Integrated ADC for TJ, VNTC, VOUT, VSENSE conversion

- Fast ADC for VDS, VSENSE conversion

- CCM: capacitive charging mode

- Few times programmable non-volatile memory (FTP NVM) embedded for customer sector program/erase/read

- Direct input pin for hardware control of external MOSFET gate pin

- Package QFN32L 5x5 package with wettable flanks

- Protections

- Battery undervoltage shut-down

- External MOSFET desaturation shutdown configurable via SPI

- Hard short circuit latch-off configurable via SPI

- Current vs time latch-off configurable via SPI (fuse-emulation)

- Device overtemperature shutdown

- External MOSFET overtemperature shutdown

- Reverse battery

- Loss of GND

## **Application**

- Specially intended for Automotive power distribution applications

- Intelligent high current fuse replacement for automotive applications

#### Product status

VNF1248F

| Product summary      |               |  |  |  |

|----------------------|---------------|--|--|--|

| Order code VNF1248FT |               |  |  |  |

| Package              | QFN32L        |  |  |  |

| Packing              | Tape and reel |  |  |  |

# **Description**

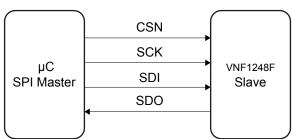

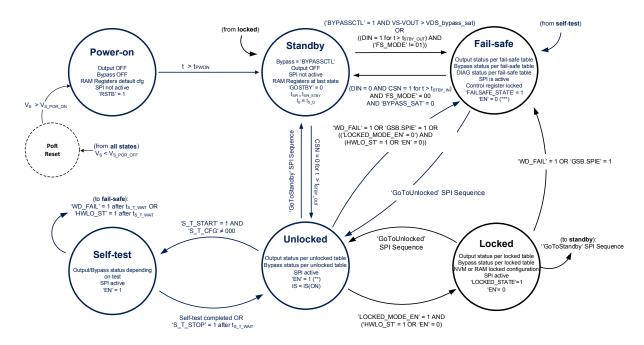

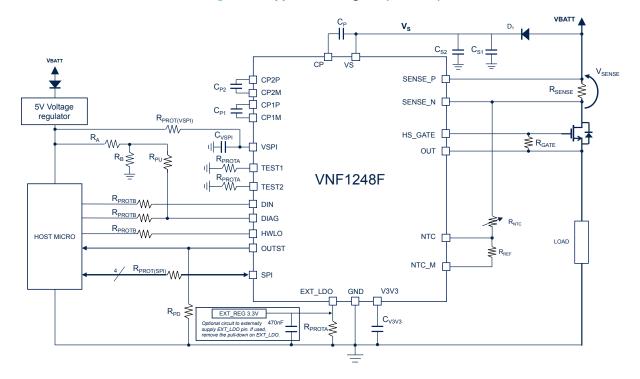

The device is an advanced controller for a Power MOSFET in high-side configuration, designed for the implementation of an intelligent high-side switch for 12 V, 24 V, and 48 V automotive applications. The control IC is interfaced to a host microcontroller through a 3.3 V and 5 V CMOS-compatible SPI interface and provides protection and diagnostics to the system.

DS14109 - Rev 7 page 2/79

# Block diagram and pin description

P-Channel bypass V<sub>SENSE\_ADO</sub> СР Current sense ISNS\_P CP2P amplifier + 13-bits ADC ISNS\_N CP2M Charge Pump Internal CP1P 10-bits Fast ADC LDO CP1M  $V_{CP}$ HS\_GATE Gate Driver HS VSPI OUT CCM CSN  $V_{DS\_ADC}$ SDI V<sub>DS</sub> Detection 24-bit SPI SDO 🗖 10-bits Fast ADC  $V_{OUT\_ADC}$ LOGIC SCK 10-bits ADC OUTST DIAG 🗖  $\mathsf{T}_\mathsf{J}$ HWLO 10-bits ADC DIN  $V_{NTC\_ADC}$ NTC Comp EXT LDO V<sub>NTC</sub> 10-bits ADC V<sub>NTC</sub> level shifter EXT\_LDO NTC\_M

Figure 1. Block diagram

Figure 2. Configuration diagram (top through view)

Note: TAB connection must be to the ground. TAB is not intended as the device reference ground (a dedicated pin shall be used).

DS14109 - Rev 7 page 3/79

**Table 1. Pin functions**

| Pin#                         | Name    | Function                                                                                                                                                                                                            |

|------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAB                          |         | GND                                                                                                                                                                                                                 |

| 1                            | VSPI    | DC supply input for the SPI interface. 3.3 V and 5 V are compatible.                                                                                                                                                |

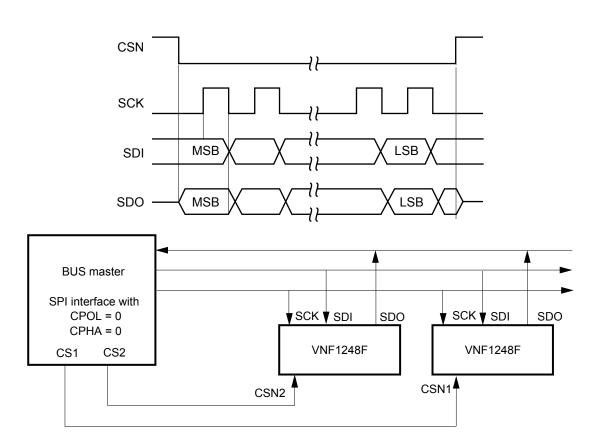

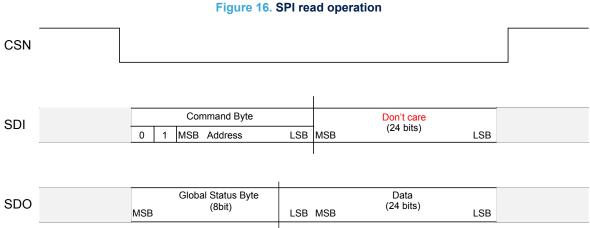

| 2                            | CSN     | Chip select (active low) for SPI communication. It is the selection pin of the device. CMOS compatible input.                                                                                                       |

| 3                            | SDI     | Serial data input for SPI communication. Data is transferred serially into the device and sampled on SCK rising edge.                                                                                               |

| 4                            | SDO     | Serial data output for SPI communication. Data is transferred serially out of the device on the SCK falling edge.                                                                                                   |

| 5                            | SCK     | Serial clock for SPI communication. It is a CMOS compatible input.                                                                                                                                                  |

| 6                            | DIAG    | Open drain logic output. Diagnostic feedback. DIAG = '0' if ((SR1.FAILSAFE_ST='1' or (CR1.AUTO_ON_DIS='1') and BYPASS_SAT='1') or (GSB.DIAGS = '1') or (GSB.DE = '1') or "internal oscillator fault event" else '1' |

| 7                            | TEST1   | Test mode pin 1 - It must be connected to the ground through 1 $k\Omega$ resistor.                                                                                                                                  |

| 8                            | TEST2   | Test mode pin 2 - It must be connected to the ground through 1 $k\Omega$ resistor.                                                                                                                                  |

| 9                            | DIN     | Direct input to wake-up device from standby and to control directly gate turn-on/turn-off. If not used, must be connected to the ground through 1 $k\Omega$ resistor.                                               |

| 10                           | HWLO    | Active high input pin compatible with 3.3 V and 5 V CMOS. If not used, must be connected to the ground through 1 k $\Omega$ resistor.                                                                               |

| 11, 16,<br>17, 22,<br>26, 32 | N.C     | Not connected.                                                                                                                                                                                                      |

| 12                           | V3V3    | Output of the 3.3 V internal LDO voltage regulator (logic and I/O supply).                                                                                                                                          |

|                              |         | Connect a low ESR capacitor (1 µF) close to this pin.                                                                                                                                                               |

| 13                           | GND     | Ground connection.                                                                                                                                                                                                  |

| 14                           | EXT_LDO | External V3V3 supply. If not used, must be connected to the ground through 1 $k\Omega$ resistor.                                                                                                                    |

| 15                           | OUTST   | Gate status monitor.                                                                                                                                                                                                |

| 18                           | NTC_M   | Negative input pin for external NTC resistor.                                                                                                                                                                       |

| 19                           | NTC     | Positive input pin for external NTC resistor.                                                                                                                                                                       |

| 20                           | ISNS_N  | Current sense amplifier negative input.                                                                                                                                                                             |

| 21                           | ISNS_P  | Current sense amplifier positive input.                                                                                                                                                                             |

| 23                           | OUT     | External FET source connection.                                                                                                                                                                                     |

| 24                           | HS_GATE | Output of the gate driver for the external FET.                                                                                                                                                                     |

| 25                           | VS      | Input supply pin. Connect to the 12 V, 24 V, 48 V battery voltage.                                                                                                                                                  |

| 27                           | СР      | Charge pump output.                                                                                                                                                                                                 |

| 28                           | CP2P    | Charge pump–Positive terminal of the flying capacitor C <sub>P2</sub> .                                                                                                                                             |

| 29                           | CP2M    | Charge pump–Negative terminal of the flying capacitor C <sub>P2</sub> .                                                                                                                                             |

| 30                           | CP1P    | Charge pump–Positive terminal of the flying capacitor C <sub>P1</sub> .                                                                                                                                             |

| 31                           | CP1M    | Charge pump–Negative terminal of the flying capacitor C <sub>P1</sub> .                                                                                                                                             |

DS14109 - Rev 7 page 4/79

# 2 Electrical specification

#### 2.1 Absolute maximum ratings

Stressing the device above the rating listed in Table 2 may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to the conditions in the table below for extended periods may affect device reliability.

Table 2. Absolute maximum rating

| Symbol                                                 | Parameter                                                                  | Value                                       | Unit |

|--------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------|------|

| Vs                                                     | DC supply voltage                                                          | -0.3 to 70                                  | V    |

| -I <sub>GND</sub>                                      | DC reverse ground pin current                                              | 200                                         | mA   |

| V <sub>SPI</sub>                                       | DC input voltage                                                           | -0.3 to 6.5                                 | ٧    |

| V <sub>3V3</sub>                                       | DC Output voltage                                                          | -0.3 to 4.6                                 | ٧    |

| V <sub>EXT_LDO</sub>                                   | External V3V3 supply                                                       | -0.3 to 4.6                                 | ٧    |

| V <sub>CSN</sub> , V <sub>SDI</sub> , V <sub>SCK</sub> | SPI pins DC input voltage                                                  | -0.3 to 6.5                                 | V    |

| $V_{SDO}$                                              | SPI pins DC output voltage                                                 | -0.3 to V <sub>SPI</sub> + 0.3              | V    |

| V <sub>HWLO</sub>                                      | DC input voltage                                                           | -0.3 to 70                                  | V    |

| $V_{DIAG}$                                             | DC output voltage                                                          | -0.3 to V3V3 + 0.3 < 4.6                    | V    |

| I <sub>DIAG</sub>                                      | DC input current                                                           | Internally limited                          | mA   |

| V <sub>ISNS_P</sub>                                    | DC input voltage                                                           | -15 to 70                                   | V    |

| ΔV_ISNS                                                | Differential DC input voltage (V <sub>ISNS_P</sub> - V <sub>ISNS_N</sub> ) | < 3.3                                       | V    |

| V <sub>HS_GATE</sub>                                   | DC output voltage                                                          | -15 to V <sub>out</sub> + 20                | V    |

| V <sub>OUT</sub>                                       | DC output voltage                                                          | -15 to V <sub>S</sub> + 3                   | V    |

| V <sub>NTC</sub>                                       | DC input voltage                                                           | -15 to I <sub>SNS_P</sub> + 0.3             | V    |

| V <sub>NTC_M</sub>                                     | DC input voltage                                                           | -15 to I <sub>SNS_P</sub> + 0.3             | V    |

| V <sub>CP</sub>                                        | DC input voltage                                                           | V <sub>S</sub> - 0.3 to V <sub>S</sub> + 20 | ٧    |

| V <sub>CP1P</sub>                                      | DC input voltage                                                           | V <sub>S</sub> - 0.3 to V <sub>S</sub> + 20 | ٧    |

| V <sub>CP2P</sub>                                      | DC input voltage                                                           | V <sub>S</sub> - 0.6 to V <sub>S</sub> + 20 | ٧    |

| V <sub>CP1M</sub> ,                                    | DC input voltage                                                           | -0.3 to V <sub>S</sub> + 0.3                | V    |

|                                                        | Electrostatic discharge (JEDEC 22A-114F)                                   | 2000                                        |      |

| V <sub>ESD</sub>                                       | Liectiostatic discharge (JEDEO 22A-1141 )                                  | 4000 <sup>(1)</sup>                         | V    |

| VESD.                                                  | Charge device model (CDM-AEC-Q100-011)                                     | ±500 <sup>(2)</sup>                         | V    |

|                                                        | Charge device model (ODM-ALO-Q 100-011)                                    | ±750 <sup>(3)</sup>                         |      |

| OUTST                                                  | Open drain active high. Gate status monitor.                               | -0.3 to V3V3 + 0.3 < 4.6                    | V    |

| DIN                                                    | Direct input                                                               | -0.3 to 70                                  | V    |

| $T_J$                                                  | Junction operating temperature                                             | -40 to 150                                  | °C   |

DS14109 - Rev 7 page 5/79

| Symbol           | Parameter                                                                                | Value      | Unit |

|------------------|------------------------------------------------------------------------------------------|------------|------|

| T <sub>stg</sub> | Storage temperature                                                                      | -55 to 150 | °C   |

| N <sub>FTP</sub> | Maximum number of few time programmable non-volatile memory (FTP NVM) programming cycles | 1000       |      |

- 1. Only for pin: VS, OUT, DIN.

- 2. All pins except corners.

- 3. Corner pins.

#### 2.2 Thermal data

Table 3. Thermal data

| Symbol            | Parameter                                                                    | Typ. value | Unit |

|-------------------|------------------------------------------------------------------------------|------------|------|

| D                 | Thermal resistance, junction-to-ambient (JEDEC JESD 51-2, -7) <sup>(1)</sup> | 56         | °C/W |

| R <sub>thJA</sub> | Thermal resistance, junction-to-ambient (JEDEC JESD 51-2, -5) <sup>(2)</sup> | 26         | C/VV |

- 1. Device mounted on two-layer 2s0p PCB with 2 cm² heatsink copper trace.

- 2. Device mounted on four-layer 2s2p PCB.

Note:

Board finish thickness 1.6 mm  $\pm 10\%$ ; Board double layer and four layers; board dimension 129x60; board material FR4; Cu thickness 0.070 mm (outer layers), Cu thickness 0.035 mm (inner layers); Thermal vias separation 1.2 mm, Thermal vias diameter 0.3 mm  $\pm 0.08$  mm, Cu thickness on vias 0.025 mm; footprint dimension 3.5 mm x 3.5 mm.

#### 2.3 Main electrical characteristics

6 V <  $V_S$  < 60 V; -40 °C <  $T_J$  < 150 °C, unless otherwise specified.

All typical values refer to  $V_S$  = 48 V;  $T_J$  = 25 °C, unless otherwise specified.

**Table 4. Supply specification**

| Symbol                  | Parameter                                         | Test conditions                               | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------------------------------------|-----------------------------------------------|------|------|------|------|

| V <sub>S</sub>          | Operating supply voltage                          |                                               | 6    | 48   | 60   | V    |

| V <sub>S_EXT</sub>      | Extended operating supply voltage                 | 100 ms max. duration                          | 6    | -    | 70   | V    |

| V <sub>EXT_LDO_L</sub>  | Low level voltage EXT_LDO                         |                                               | 2.6  | 2.8  | 3    | V    |

| V <sub>EXT_LDO_H</sub>  | High level voltage EXT_LDO                        |                                               | 2.8  | 3    | 3.2  | V    |

| I <sub>EXT_LDO_H</sub>  | Current consumption from EXT_LDO in supplier mode | V <sub>EXT_LDO</sub> > V <sub>EXT_LDO_H</sub> | 3.5  | 5    | 6    | mA   |

| I <sub>EXT_LDO_L</sub>  | Current consumption from EXT_LDO                  | V <sub>EXT_LDO</sub> < V <sub>EXT_LDO_L</sub> | 6    | 10   | 16   | μA   |

| V <sub>S_USD1</sub>     |                                                   |                                               | 3.8  | 4    | 4.2  |      |

| V <sub>S_USD2</sub>     | Undervoltage shutdown <sup>(1)</sup>              |                                               | 12   | 13   | 14   | V    |

| V <sub>S_USD3</sub>     |                                                   |                                               | 22   | 24   | 25   |      |

| V <sub>S_USD_RES1</sub> |                                                   |                                               | 4.3  | 4.5  | 4.8  |      |

| V <sub>S_USD_RES2</sub> | Undervoltage shutdown reset                       |                                               | 13   | 14   | 15   | V    |

| V <sub>S_USD_RES3</sub> |                                                   |                                               | 24   | 27   | 29   |      |

| V <sub>S_USD_HYS1</sub> | Undervoltage shutdown hysteresis                  |                                               | -    | 0.5  | -    | V    |

| V <sub>S_USD_HYS2</sub> | Undervoltage shutdown hysteresis                  |                                               | -    | 1    | -    | V    |

| V <sub>S_USD_HYS3</sub> | Undervoltage shutdown hysteresis                  |                                               | -    | 3    | -    | V    |

DS14109 - Rev 7 page 6/79

| Symbol                  | Parameter                                                                                     | Test conditions                                                                                                                 | Min. | Тур. | Max. | Unit |

|-------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>VS_USD</sub>     | Undervoltage shutdown filtering time.                                                         |                                                                                                                                 | -    | 33   | -    | μs   |

| VSPI_UV                 | Undervoltage shutdown on VSPI                                                                 |                                                                                                                                 | 1.5  | 1.6  | 1.8  | V    |

| VSPI_UV_RESET           | Undervoltage shutdown reset on VSPI                                                           |                                                                                                                                 | 2    | 2.1  | 2.2  | V    |

| I <sub>SPI</sub>        | SPI supply current during frame communication                                                 |                                                                                                                                 | -    | -    | 3    | mA   |

| I <sub>SPI_STBY</sub>   | SPI supply current in standby state                                                           |                                                                                                                                 | -    | -    | 5    | μΑ   |

|                         |                                                                                               | $f_{PWM}$ = 1 Hz,<br>$V_{EXT\_LDO} < V_{EXT\_LDO\_L}$<br>$V_{S}$ = 13 V, OUT = $V_{S}$<br>Gate ON, $R_{GATE}$ = 47 k $\Omega$   | -    | 8.6  | -    | mA   |

|                         |                                                                                               | $f_{PWM}$ = 1 Hz,<br>$V_{EXT\_LDO} < V_{EXT\_LDO\_L}$<br>$V_S$ = 48 V, OUT = $V_S$<br>Gate ON, $R_{GATE}$ = 47 k $\Omega$       | -    | 7.9  | -    | mA   |

| I <sub>S(ON)</sub>      | Supply current on VS pin (includes logic)                                                     | $f_{PWM}$ = 1 Hz,<br>$V_{EXT\_LDO} < V_{EXT\_LDO\_L}$<br>$V_S$ = 48 V, OUT = $V_S$                                              | 4.5  | 7.2  | 8.5  | mA   |

|                         |                                                                                               | $f_{PWM}$ = 1 Hz,<br>$V_{EXT\_LDO} > V_{EXT\_LDO\_H}$ ,<br>$V_{S}$ = 13 V, OUT = $V_{S}$<br>Gate ON, $R_{GATE}$ = 47 k $\Omega$ | _    | 4    | -    | mA   |

|                         |                                                                                               | $f_{PWM}$ = 1 Hz,<br>$V_{EXT\_LDO} > V_{EXT\_LDO\_H}$ ,<br>$V_{S}$ = 48 V, OUT = $V_{S}$<br>Gate ON, $R_{GATE}$ = 47 k $\Omega$ | -    | 3.1  | -    | mA   |

|                         |                                                                                               | V <sub>S</sub> = 13 V, standby mode,<br>OUT = GND                                                                               | 1.5  | 3    | 5    | μA   |

| IOUT_STDBY              | Output current standby mode                                                                   | V <sub>S</sub> = 48 V, standby mode,<br>OUT = GND                                                                               | 1    | 3    | 5    | μA   |

| lour ou                 | Output current unlocked mode                                                                  | V <sub>S</sub> = 13 V, unlocked mode,<br>OUT=GND                                                                                | 140  | 185  | 230  | μA   |

| I <sub>OUT</sub> ON     | Output current unlocked mode                                                                  | V <sub>S</sub> = 48 V, unlocked mode,<br>OUT = GND                                                                              | 210  | 250  | 320  | μA   |

|                         |                                                                                               | V <sub>S</sub> = 48 V, T <sub>J</sub> = 25 °C, OUT = V <sub>S</sub>                                                             | 45   | 60   | 70   | μA   |

| I <sub>S_Q</sub>        | V <sub>S</sub> quiescent current (includes logic)– independently from bypass switch condition | V <sub>S</sub> = 48 V, T <sub>J</sub> = 25 °C, OUT = GND                                                                        | 50   | 60   | 75   | μA   |

|                         | macpointently from Sypass Switch continuon                                                    | V <sub>S</sub> = 13 V, T <sub>J</sub> = 25 °C, OUT = V <sub>S</sub>                                                             | 30   | 48   | 57   | μA   |

| V <sub>S_POR_ON</sub>   | Power-on reset the threshold. The device leaves the reset mode                                |                                                                                                                                 | 2.4  | 2.5  | 2.65 | V    |

| V <sub>S_POR_OFF</sub>  | Power-on shutdown threshold. Device enters reset mode                                         |                                                                                                                                 | 2.2  | 2.3  | 2.45 | V    |

| V <sub>S_POR_HYST</sub> | Power-on reset hysteresis                                                                     |                                                                                                                                 | -    | 0.2  | -    | V    |

| t <sub>PWON</sub>       | Time from power-on to standby                                                                 | $V_S > V_{S\_POR\_ON}$                                                                                                          | -    | -    | 500  | μs   |

DS14109 - Rev 7 page 7/79

| Symbol | Parameter | Test conditions              | Min. | Тур. | Max. | Unit |

|--------|-----------|------------------------------|------|------|------|------|

|        |           | V3V3 external capacitor 1 μF |      |      |      |      |

- 1. See Table 51. CR#3: control register 3 (read/write); address 03h.

- 2. Measured in test mode with the charge pump off.

Table 5. SPI logic inputs (CSN, SCK, and SDI) specification

| Symbol              | Parameter                              | Test conditions         | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------------|-------------------------|------|------|------|------|

|                     | Low level input current (SCK and SDI)  | V <sub>II</sub> = 1.5 V | 1.7  | -    | 4    | μA   |

| I <sub>IL</sub>     | Low level input current (CSN)          | V <sub>IL</sub> = 1.5 V | -2.9 | -    | -2   | μA   |

| I                   | High level input current (SCK and SDI) | V <sub>IH</sub> = 2.1 V | -13  | -    | -3   | μA   |

| I <sub>IH</sub>     | High level input current (CSN)         |                         | -18  | -    | -10  | μA   |

| V <sub>IL</sub>     | Low level input voltage                |                         | -    | -    | 1.5  | V    |

| V <sub>IH</sub>     | High level input voltage               |                         | 2.1  | -    | -    | V    |

| V <sub>I_HYST</sub> | Input hysteresis voltage               |                         | -    | 0.4  | -    | V    |

Table 6. SPI logic output (SDO) specification

| Symbol          | Parameter                 | Test conditions        | Min.                   | Тур. | Max.                   | Unit |

|-----------------|---------------------------|------------------------|------------------------|------|------------------------|------|

| V <sub>OL</sub> | Low level output voltage  |                        | -                      | -    | 0.3 * V <sub>SPI</sub> | V    |

| V <sub>OH</sub> | High level output voltage |                        | 0.7 * V <sub>SPI</sub> | -    | -                      | V    |

| ISDO_llow       | Low level output current  | VSDO = 1 V, VSPI = 5 V | 45                     | -    | 96                     | mA   |

| ISDO_Ihigh      | High level output current | VSDO = 4 V, VSPI = 5 V | 15                     | -    | 32                     | mA   |

| I <sub>LO</sub> | Output leakage current    |                        | -1                     | -    | 1                      | μΑ   |

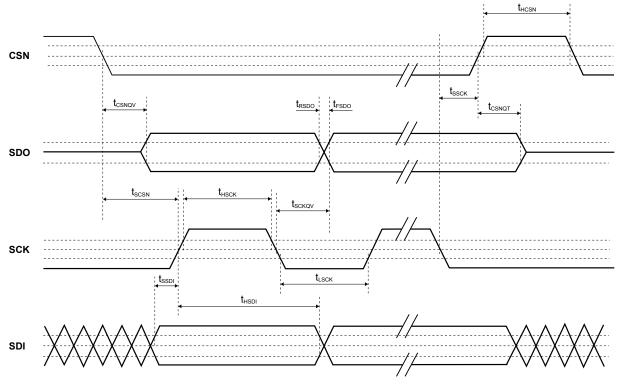

Table 7. SPI timing specification

| Symbol             | Parameter                                     | Test condition | s  | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------------------------|----------------|----|------|------|------|------|

| f <sub>SCK</sub>   | SPI clock frequency                           |                |    | -    | -    | 8    | MHz  |

| t <sub>HSCK</sub>  | SCK high time                                 |                |    | 55   | -    | -    | ns   |

| t <sub>LSCK</sub>  | SCK low time                                  |                |    | 55   | -    | -    | ns   |

| t <sub>HCSN</sub>  | CSN high time                                 |                |    | 1    | -    | -    | μs   |

| t <sub>SCSN</sub>  | CSN setup time–CSN low before SCK rising edge |                |    | 100  | -    | -    | ns   |

| tssck              | SCK setup time–SCK low before CSN rising edge |                |    | 100  | -    | -    | ns   |

| t <sub>SSDI</sub>  | SDI setup time before SCK rising edge         |                |    | 25   | -    | -    | ns   |

| t <sub>HSDI</sub>  | SDI hold time                                 |                |    | 20   | -    | -    | ns   |

| t <sub>CSNQV</sub> | CSN falling edge until SDO valid              |                |    | -    | -    | 70   | ns   |

| t <sub>CSNQT</sub> | CSN rising edge until SDO tristate            |                |    | -    | 220  | -    | ns   |

| t <sub>SCKQV</sub> | SCK falling edge until SDO valid              |                |    | -    | -    | 50   | ns   |

| t <sub>RSDO</sub>  | SDO rise time                                 |                |    | -    | -    | 25   | ns   |

| t <sub>FSDO</sub>  | SDO fall time                                 |                |    | -    | -    | 25   | ns   |

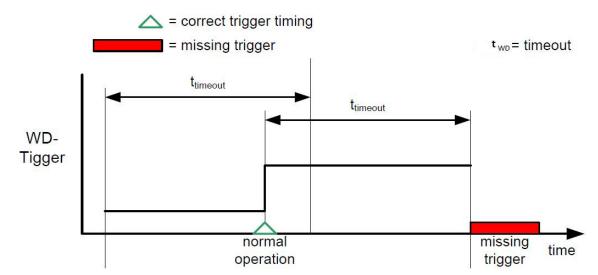

| t <sub>WHCH</sub>  | CSN low timeout                               |                |    | -10% | 50   | +10% | ms   |

| •                  | Watahdag taggla hit timeaut                   | WD_TIME        | 00 | -10% | 50   | +10% |      |

| t <sub>WDTB</sub>  | Watchdog toggle bit timeout                   | configuration: | 01 | -10% | 100  | +10% | ms   |

DS14109 - Rev 7 page 8/79

| Symbol               | Parameter                                                                                  | Test conditions         |    | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------------------------------------------------------------|-------------------------|----|------|------|------|------|

| t <sub>WDTB</sub>    | Watchdod toddle hit timeout                                                                | WD_TIME                 | 10 | -10% | 150  | +10% | ms   |

| WDIB                 |                                                                                            | configuration:          | 11 | 1070 | 200  |      | 1110 |

| t <sub>STBY_OU</sub> | Minimum time during which CSN must be toggled low to the wake-up device from standby state | Device in standby state |    | 2    | 4    | 6    | μs   |

Figure 3. SPI specification: timing waveforms

$t_{\text{HCSN}}$

: CSN high time : CSN falling until SDO valid : SDO fall time  $t_{\text{CSNQV}}$

$t_{\text{RSDO}}$

$t_{\text{FSDO}}$

SDO fall time

SDO rise time

SCK setup time before CSN rising

CSN rising until SDO tristate

CSN setup time before SCK rising

SCK high time

SCK falling until SDO valid

SDI setup time before SCK rising

SDI hold time  $t_{\sf SSCK}$  $t_{CSNQT}$

$t_{SCSN}$  $t_{\text{HSCK}}$

$t_{\text{SCKQV}}$  $t_{SSDI}$

t<sub>HSDI</sub> : SCK low time  $t_{\scriptscriptstyle LSCK}$

Table 8. HWLO logic input pin specification

| Symbol              | Parameter                | Test conditions         | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------|-------------------------|------|------|------|------|

| I <sub>IL</sub>     | Low level input current  | V <sub>IL</sub> = 1.5 V | 0.5  | -    | 2.5  | μΑ   |

| I <sub>IH</sub>     | High level input current | V <sub>IH</sub> = 2.1 V | 1.6  | -    | 3.5  | μΑ   |

| V <sub>IL</sub>     | Low level input voltage  |                         | -    | -    | 1.5  | V    |

| V <sub>IH</sub>     | High level input voltage |                         | 2.1  | -    | -    | V    |

| V <sub>I_HYST</sub> | Input hysteresis voltage |                         | -    | 0.4  | -    | V    |

| t <sub>HWLO</sub>   | HWLO filtering time      |                         | -10% | 33   | 10%  | μs   |

page 9/79

#### Table 9. DIAG logic output pin specification

| Symbol                | Parameter                             | Test conditions                               | Min. | Тур. | Max. | Unit |

|-----------------------|---------------------------------------|-----------------------------------------------|------|------|------|------|

| V <sub>DIAG_PD</sub>  | DIAG pin open-drain pull-down voltage | I <sub>DIAG_PD</sub> = 1 mA                   | -    | -    | 0.2  | V    |

| I <sub>DIAG_PD</sub>  | DIAG pin open-drain input current     | V <sub>DIAG</sub> = V <sub>DIAG_PD</sub>      | -    | -    | 1    | mA   |

| I <sub>DIAG_LKG</sub> | DIAG pin open-drain leakage current   | V <sub>DIAG</sub> = V <sub>V3V3</sub> = 4.6 V | 0    | -    | 1    | μA   |

Table 10. Device thermal shutdown

| Symbol                  | Parameter                                                | Test conditions | Min. | Тур. | Max. | Unit      |

|-------------------------|----------------------------------------------------------|-----------------|------|------|------|-----------|

| T <sub>TSD</sub>        | Junction temperature thermal shutdown threshold          |                 | 160  | 175  | 190  | °C        |

| T <sub>TSD_HYS</sub>    | Junction temperature thermal shutdown hysteresis         |                 | -    | 15   | -    | °C        |

| T <sub>J_ADC_CONV</sub> | Junction temperature ADC full-scale range resolution (1) |                 | 0    | -    | 1023 | -         |

| T <sub>J_ADC_RATE</sub> | Junction temperature ADC sample rate                     |                 | -    | 10   | -    | kSample/s |

1.  $T_{J\_ADC}$  (°C) =  $T_{J\_ADC}$  [9:0]/3 - 72

Table 11. DIN logic input pin specification

| Symbol                       | Parameter                                                                                 | Test conditions       | Min. | Тур. | Max. | Unit |

|------------------------------|-------------------------------------------------------------------------------------------|-----------------------|------|------|------|------|

| I <sub>IL</sub>              | Low level input current                                                                   | V <sub>IL</sub> = 1.5 | 1.5  | -    | 5    | μΑ   |

| I <sub>IH</sub>              | High level input current                                                                  | V <sub>IH</sub> = 2.1 | -12  | -    | -2   | μΑ   |

| V <sub>IL</sub>              | Low level input voltage                                                                   |                       | 1.48 | 1.59 | 1.73 | ٧    |

| V <sub>IH</sub>              | High level input voltage                                                                  |                       | 2.01 | 2.05 | 2.10 | V    |

| V <sub>I_HYST</sub>          | Input hysteresis voltage                                                                  |                       | -    | 0.4  | -    | V    |

| t <sub>DIN_WAKEUP</sub>      | Filtering time on DIN rise edge for device wakeup                                         |                       | -    | 4    | -    | μs   |

| t <sub>DIN_DEGLITCH</sub>    | De-glitch filtering time on DIN rise/fall edges                                           |                       | -    | 1    | -    | μs   |

| t <sub>DIN_RISE_FILTER</sub> | Filtering time on DIN rise edge for DIN direct control of external FET in fail-safe state |                       | -    | 10   | -    | μs   |

| tDIN_TOGGLE_TOUT             | DIN toggling timeout                                                                      |                       | -    | 20   | -    | μs   |

Table 12. OUTST logic output pin specification

| Symbol                 | Parameter                            | Test conditions              | Min. | Тур. | Max. | Unit |

|------------------------|--------------------------------------|------------------------------|------|------|------|------|

| V <sub>OUTST_PU</sub>  | OUTST pin open-drain pull-up voltage | I <sub>OUTST_PU</sub> = 1 mA | 3.15 | -    | -    | V    |

| I <sub>OUTST_PU</sub>  | OUTST pin open-drain output current  |                              | -    | -    | 1    | mA   |

| I <sub>OUTST_LKG</sub> |                                      | V <sub>OUTST</sub> = 4.6 V   | 0    | -    | 16   | μΑ   |

Table 13. Charge pump specification

| Symbol                   | Parameter                                       | Test conditions              | Min.                  | Тур.                  | Max.                  | Unit |

|--------------------------|-------------------------------------------------|------------------------------|-----------------------|-----------------------|-----------------------|------|

| V <sub>CP_6V</sub>       | Charge pump output voltage                      | V <sub>S</sub> = 6 V         | V <sub>S</sub> + 7    | V <sub>S</sub> + 11   | -                     | V    |

| V <sub>CP_10V</sub>      | Charge pump output voltage                      | V <sub>S</sub> > 10 V        | V <sub>S</sub> + 13.5 | V <sub>S</sub> + 14.5 | V <sub>S</sub> + 15.5 | V    |

| V <sub>CP_LOW_H</sub>    | Charge pump output under voltage high threshold | Ramp up on V <sub>CP</sub>   | V <sub>S</sub> + 5.5  | V <sub>S</sub> + 6    | V <sub>S</sub> + 6.5  | V    |

| V <sub>CP_LOW_L</sub>    | Charge pump output undervoltage low threshold   | Ramp down on V <sub>CP</sub> | V <sub>S</sub> + 5.1  | V <sub>S</sub> + 5.6  | V <sub>S</sub> + 6.2  | V    |

| V <sub>CP_LOW_hyst</sub> | Charge pump output undervoltage hysteresis      |                              | -                     | 0.4                   | -                     | V    |

DS14109 - Rev 7 page 10/79

| Symbol               | Parameter                                                       | Test conditions | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------------------------------|-----------------|------|------|------|------|

| f <sub>CP</sub>      | Charge pump frequency                                           |                 | -5%  | 400  | +5%  | kHz  |

| t <sub>CP_RISE</sub> | Charge pump low (CP_LOW diagnostic) rising edge filtering time  |                 | -5%  | 60   | 5%   | μs   |

| t <sub>CP_FALL</sub> | Charge pump low (CP_LOW diagnostic) falling edge filtering time |                 | -10% | 2.3  | 10%  | μs   |

Table 14. External FET gate driver specification

| Symbol                       | Parameter                                          | Test conditions                                                                                                       | Min. | Тур. | Max. | Unit |

|------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>GSON_6V</sub>         | Gate-on voltage                                    | $V_S = 6 \text{ V}, I_G = 50  \mu\text{A}$                                                                            | 6    | -    | -    | V    |

| V <sub>GSON_10V</sub>        | Gate-on voltage                                    | V <sub>S</sub> > 10 V, I <sub>G</sub> = 50 μA                                                                         | 11.5 | -    | 15   | V    |

| V <sub>GSOFF</sub>           | Gate-off voltage                                   |                                                                                                                       | -    | -    | 0.5  | V    |

| V <sub>GSMAX</sub>           | Maximum gate voltage (internally limited)          |                                                                                                                       | -    | -    | 20   | V    |

| t <sub>ON</sub>              | Gate turn-on                                       | $V_{GS}$ = 0.5 V to $V_{GS}$ = 10 V, $C_{GATE}$ = 80 nF                                                               | -    | -    | 3    | μs   |

| t <sub>OFF</sub>             | Gate turn-off                                      | Full V <sub>GS</sub> to V <sub>GS</sub> < 0.5, C <sub>GATE</sub> = 80 nF                                              | -    | -    | 10   | μs   |

| V <sub>GS_UVLO_6V</sub>      | Gate undervoltage lockout                          | V <sub>S</sub> = 6 V                                                                                                  | 3.5  | -    |      | V    |

| V <sub>GS_UVLO_10V</sub>     | Gate undervoltage lockout                          | V <sub>S</sub> > 10 V, C <sub>GATE_max</sub> = 30 nF                                                                  | 7    | -    | -    | V    |

| V <sub>G_UVLO_BLK</sub>      | Gate undervoltage lockout blanking                 | Enable at charge pump startup if external FET turn-on is required, and applied after CP_LOW expiration (falling edge) | -5%  | 100  | 5%   | μs   |

| V <sub>G_UVLO_DEGLITCH</sub> | Gate undervoltage lockout de-glitch filtering time |                                                                                                                       | -15% | 8    | 15%  | μs   |

Table 15. Current sense amplifier

| Symbol                 | Parameter                                   | Test conditions                                                         | Min.  | Тур. | Max. | Unit |

|------------------------|---------------------------------------------|-------------------------------------------------------------------------|-------|------|------|------|

| V <sub>SENSE_CM</sub>  | Common-mode input voltage range             |                                                                         | CS_UV | -    | VS   | V    |

| V <sub>SENSE_FSR</sub> | Differential input voltage full-scale range |                                                                         | 0     | -    | 160  | mV   |

| I <sub>SNS_P</sub>     | CSA positive input current                  | V <sub>S</sub> = 12 V                                                   | 1.1   | 1.3  | 1.5  | mA   |

| I <sub>SNS_N</sub>     |                                             | I <sub>sense_P</sub> = 12 V<br>I <sub>sense_N</sub> = 11.9 V<br>Gate ON | 100   | 200  | 300  | μА   |

Table 16. Integrated VSENSE 13-bit ADC

| Symbol                       | Parameter                                         | Test conditions                                                             | Min. | Тур. | Max. | Unit      |

|------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------|------|------|------|-----------|

| V <sub>SENSE_ADC_CONV</sub>  | Current sense ADC full-<br>scale range resolution | V <sub>SENSE_ADC</sub> [12:0] = min((V <sub>SENSE</sub> /160 * 8192), 8191) | 0    | -    | 8191 | -         |

| V <sub>SENSE_REFRESH</sub>   | Current sense ADC sample rate                     |                                                                             | -    | 2.4  | -    | kSample/s |

| V <sub>SENSE_ACC_6mV</sub>   |                                                   | 6 mV < V <sub>SENSE_DIFF</sub> < 10 mV                                      | -10  | -    | +10  | %         |

| V <sub>SENSE_ACC_10mV</sub>  |                                                   | 10 mV < V <sub>SENSE_DIFF</sub> < 20 mV                                     | -5   | -    | +5   | %         |

| V <sub>SENSE_ACC_20mV</sub>  | Digital current sense accuracy                    | V <sub>SENSE_DIFF</sub> > 20 mV                                             | -3   | -    | +3   | %         |

| V <sub>SENSE_ACC_3mV</sub>   | •                                                 | 3 mV < V <sub>SENSE_DIFF</sub> < 6 mV                                       | -17  | -    | +17  | %         |

| V <sub>SENSE_ACC_1.8mV</sub> |                                                   | 1.8 mV < V <sub>SENSE_DIFF</sub> < 3 mV                                     | -0.5 | -    | +0.5 | mV        |

DS14109 - Rev 7 page 11/79

Note:

The accuracies showed in the Table 16 are referred to the sigma delta converter at 13-bit, while the hard short and overcurrent protections are related to the 10-bit SAR converter as reported in the Table 18.

Table 17. External FET VDS protection

| Symbol                     | Parameter                                                                 | Test conditions | Min. | Тур. | Max. | Unit |

|----------------------------|---------------------------------------------------------------------------|-----------------|------|------|------|------|

| V <sub>DS_THRS_RANGE</sub> | V <sub>DS</sub> monitor threshold range 31 steps programmable through SPI |                 | 300  | -    | 1800 | mV   |

| V <sub>DS_THRS_STEP</sub>  | V <sub>DS</sub> monitor threshold step                                    |                 | -    | 50   | -    | mV   |

| V <sub>DS_THRS_0</sub>     |                                                                           |                 | -    | 300  | -    |      |

| V <sub>DS_THRS_1</sub>     |                                                                           |                 | -    | 350  | -    |      |

| V <sub>DS_THRS_2</sub>     |                                                                           |                 | -    | 400  | -    |      |

| V <sub>DS_THRS_3</sub>     |                                                                           |                 | -    | 450  | -    |      |

| V <sub>DS_THRS_4</sub>     |                                                                           |                 | -    | 500  | -    |      |

| V <sub>DS_THRS_5</sub>     |                                                                           |                 | -    | 550  | -    |      |

| V <sub>DS_THRS_6</sub>     |                                                                           |                 | -    | 600  | -    |      |

| V <sub>DS_THRS_7</sub>     |                                                                           |                 | -    | 650  | -    |      |

| V <sub>DS_THRS_8</sub>     |                                                                           |                 | -    | 700  | -    |      |

| V <sub>DS_THRS_9</sub>     |                                                                           |                 | -    | 750  | -    |      |

| V <sub>DS_THRS_10</sub>    |                                                                           |                 | -    | 800  | -    |      |

| V <sub>DS_THRS_11</sub>    |                                                                           |                 | -    | 850  | -    |      |

| V <sub>DS_THRS_12</sub>    |                                                                           |                 | -    | 900  | -    |      |

| V <sub>DS_THRS_13</sub>    |                                                                           |                 | -    | 950  | -    |      |

| V <sub>DS_THRS_14</sub>    |                                                                           |                 | -    | 1000 | -    |      |

| V <sub>DS_THRS_15</sub>    | V <sub>DS</sub> monitor thresholds                                        |                 | -    | 1050 | -    | mV   |

| V <sub>DS_THRS_16</sub>    |                                                                           |                 | -    | 1100 | -    |      |

| V <sub>DS_THRS_17</sub>    |                                                                           |                 | -    | 1150 | -    |      |

| V <sub>DS_THRS_18</sub>    |                                                                           |                 | -    | 1200 | -    |      |

| V <sub>DS_THRS_19</sub>    |                                                                           |                 | -    | 1250 | -    |      |

| V <sub>DS_THRS_20</sub>    |                                                                           |                 | -    | 1300 | -    |      |

| V <sub>DS_THRS_21</sub>    |                                                                           |                 | -    | 1350 | -    |      |

| V <sub>DS_THRS_22</sub>    |                                                                           |                 | -    | 1400 | -    |      |

| V <sub>DS_THRS_23</sub>    |                                                                           |                 | -    | 1450 | -    |      |

| V <sub>DS_THRS_24</sub>    |                                                                           |                 | -    | 1500 | -    |      |

| V <sub>DS_THRS_25</sub>    |                                                                           |                 | -    | 1550 | -    |      |

| V <sub>DS_THRS_26</sub>    |                                                                           |                 | -    | 1600 | -    |      |

| V <sub>DS_THRS_27</sub>    |                                                                           |                 | -    | 1650 | -    |      |

| V <sub>DS_THRS_28</sub>    |                                                                           |                 | -    | 1700 | -    |      |

| V <sub>DS_THRS_29</sub>    |                                                                           |                 | -    | 1750 | -    |      |

| V <sub>DS_THRS_30</sub>    |                                                                           |                 | -    | 1800 | -    |      |

| V <sub>DS_THRS_ACC</sub>   | V <sub>DS</sub> monitor threshold accuracy                                |                 | -5   | -    | 5    | %    |

DS14109 - Rev 7 page 12/79

| Symbol                       | Parameter                                            | Test conditions                          | Min.  | Тур. | Max. | Unit      |

|------------------------------|------------------------------------------------------|------------------------------------------|-------|------|------|-----------|

| V <sub>DS_DEGLITCH</sub>     | V <sub>DS</sub> monitor shut-off deglitch time       |                                          | -20%  | 5    | +20% | μs        |

| V <sub>DS_DELAY</sub>        | V <sub>DS</sub> monitor shut-off delay time          | C <sub>GATE</sub> = 30 nF,<br>T = 105 °C | -     | -    | 5    | μs        |

| V <sub>DS_BLK</sub>          | V <sub>DS</sub> monitor shut-off blanking time       | At high-side<br>external FET<br>startup  | -10%  | 960  | +10% | μs        |

| V <sub>DS_ADC_CONV_RES</sub> | VDS monitor ADC full-scale range solution (1)        |                                          | 0     | -    | 1023 | Bit       |

| V <sub>DS_ADC_CONV</sub>     | V <sub>DS</sub> monitor ADC full-scale voltage range |                                          | -0.05 | -    | 1.87 | V         |

| V <sub>DS_ADC_RATE</sub>     | V <sub>DS</sub> monitor ADC sample rate              |                                          | -     | 0.9  | -    | MSample/s |

<sup>1.</sup>  $V_{DS}(V) = V_{DS\_ADC}[9:0] * 2.4/1280 - 0.05$

Table 18. Hard short circuit protection with integrated 10-bit ADC

| Symbol                      | Parameter                                                                   | Test conditions                          | Min. | Тур.  | Max. | Unit      |

|-----------------------------|-----------------------------------------------------------------------------|------------------------------------------|------|-------|------|-----------|

| V <sub>HSC_THRS_RANGE</sub> | Hard short circuit protection threshold range 16 steps programmable via SPI |                                          | 20   | -     | 160  | mV        |

| V <sub>HSC_THRS_0</sub>     |                                                                             |                                          | -    | 20    | -    |           |

| V <sub>HSC_THRS_1</sub>     |                                                                             |                                          | -    | 23    | -    |           |

| V <sub>HSC_THRS_2</sub>     |                                                                             |                                          | -    | 26.4  | -    |           |

| V <sub>HSC_THRS_3</sub>     |                                                                             |                                          | -    | 30.3  | -    |           |

| V <sub>HSC_THRS_4</sub>     |                                                                             |                                          | -    | 34.8  | -    |           |

| V <sub>HSC_THRS_5</sub>     |                                                                             |                                          | -    | 40    | -    |           |

| V <sub>HSC_THRS_6</sub>     |                                                                             |                                          | -    | 45.9  | -    |           |

| V <sub>HSC_THRS_7</sub>     |                                                                             |                                          | -    | 52.8  | -    |           |

| V <sub>HSC_THRS_8</sub>     | Hard short circuit protection thresholds                                    |                                          | -    | 60.6  | -    | mV        |

| V <sub>HSC_THRS_9</sub>     |                                                                             |                                          | -    | 69.6  | -    |           |

| V <sub>HSC_THRS_10</sub>    |                                                                             |                                          | -    | 80    | -    |           |

| V <sub>HSC_THRS_11</sub>    |                                                                             |                                          | -    | 91.9  | -    |           |

| V <sub>HSC_THRS_12</sub>    |                                                                             |                                          | -    | 105.6 | -    |           |

| V <sub>HSC_THRS_13</sub>    |                                                                             |                                          | -    | 121.3 | -    |           |

| V <sub>HSC_THRS_14</sub>    |                                                                             |                                          | -    | 139.3 | -    |           |

| V <sub>HSC_THRS_15</sub>    |                                                                             |                                          | -    | 160   | -    |           |

| V <sub>HSC_THRS_ACC</sub>   | Hard short circuit protection threshold accuracy                            |                                          | -5   | _     | 5    | %         |

| V <sub>HSC_DELAY</sub>      | Hard short circuit protection delay time                                    | C <sub>GATE</sub> = 30 nF,<br>T = 105 °C | -    | -     | 5    | μs        |

| V <sub>HSC_ADC_CONV</sub>   | Hard short circuit protection ADC full range resolution <sup>(1)</sup>      |                                          | 0    | -     | 1023 | -         |

| V <sub>HSC_ADC_RATE</sub>   | Hard short circuit ADC sample rate                                          |                                          | -    | 0.9   | -    | MSample/s |

<sup>1.</sup>  $V_{SENSE}(mV) = V_{SENSE\_ADC}[9:0] * 160 / 1024.$

DS14109 - Rev 7 page 13/79

Table 19. Overcurrent protection

| Symbol                  | Parameter                                                                  | Test conditions | Min.         | Тур. | Max.         | Unit |

|-------------------------|----------------------------------------------------------------------------|-----------------|--------------|------|--------------|------|

| Voc_thrs_range          | Overcurrent protection first threshold range 32 steps programmable via SPI |                 | 6            | -    | 90           | mV   |

| V <sub>OC_THRS_0</sub>  |                                                                            |                 |              | 6    |              |      |

| V <sub>OC_THRS_1</sub>  |                                                                            |                 | -12%         | 7.2  | +12%         |      |

| V <sub>OC_THRS_2</sub>  |                                                                            |                 |              | 8.7  |              |      |

| V <sub>OC_THRS_3</sub>  |                                                                            |                 |              | 10.4 |              |      |

| V <sub>OC_THRS_4</sub>  |                                                                            |                 |              | 11.8 |              |      |

| V <sub>OC_THRS_5</sub>  |                                                                            |                 |              | 13   |              |      |

| V <sub>OC_THRS_6</sub>  |                                                                            |                 |              | 13.8 |              |      |

| V <sub>OC_THRS_7</sub>  |                                                                            |                 | 70/          | 14.8 | 70/          |      |

| V <sub>OC_THRS_8</sub>  |                                                                            |                 | -7%          | 15.8 | 7%           |      |

| V <sub>OC_THRS_9</sub>  |                                                                            |                 |              | 16.8 | -            |      |

| V <sub>OC_THRS_10</sub> |                                                                            |                 |              | 17.9 | -            |      |

| V <sub>OC_THRS_11</sub> |                                                                            |                 |              | 19.1 |              |      |

| V <sub>OC_THRS_12</sub> |                                                                            |                 |              | 20.4 |              |      |

| V <sub>OC_THRS_13</sub> |                                                                            |                 |              | 21.8 |              |      |

| V <sub>OC_THRS_14</sub> |                                                                            |                 |              | 23.3 |              |      |

| V <sub>OC_THRS_15</sub> |                                                                            |                 |              | 24.8 |              |      |

| V <sub>OC_THRS_16</sub> | Overcurrent protection thresholds                                          |                 |              | 26.5 |              | mV   |

| V <sub>OC_THRS_17</sub> |                                                                            |                 |              | 28.2 |              |      |

| V <sub>OC_THRS_18</sub> |                                                                            |                 |              | 30.1 |              |      |

| V <sub>OC_THRS_19</sub> |                                                                            |                 |              | 32.2 |              |      |

| V <sub>OC_THRS_20</sub> |                                                                            |                 |              | 34.3 |              |      |

| V <sub>OC_THRS_21</sub> |                                                                            |                 |              | 36.6 |              |      |

| V <sub>OC_THRS_22</sub> |                                                                            |                 | -5%          | 39.1 | 5%           |      |

| V <sub>OC_THRS_23</sub> |                                                                            |                 |              | 41.7 | -            |      |

| V <sub>OC_THRS_24</sub> |                                                                            |                 |              | 44.5 | -            |      |

| V <sub>OC_THRS_25</sub> |                                                                            |                 |              | 47.5 | -            |      |

| V <sub>OC_THRS_26</sub> |                                                                            |                 |              | 50.6 | -            |      |

| V <sub>OC_THRS_27</sub> |                                                                            |                 |              | 54   | -            |      |

| V <sub>OC_THRS_28</sub> |                                                                            |                 |              | 61.3 | -            |      |

| V <sub>OC_THRS_29</sub> |                                                                            |                 |              | 69.5 | 1            |      |

| V <sub>OC_THRS_30</sub> |                                                                            |                 |              | 78.8 | -            |      |

| V <sub>OC_THRS_31</sub> |                                                                            |                 |              | 89.3 | -            |      |

| i-time_tol_t            | I-t tolerance on time step (y axis)                                        |                 | (t-10%) - 32 | -    | (t+10%) + 32 | μs   |

| t <sub>I_SAMPLING</sub> | I <sup>2</sup> t algorithm sampling time                                   |                 | -10%         | 61   | 10%          | μs   |

Note: Overcurrent protection is based on the same 10-bit ADC used for hard short protection.

DS14109 - Rev 7 page 14/79

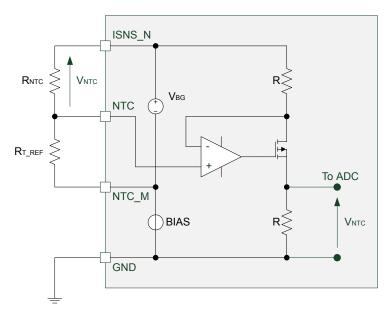

Table 20. External FET thermal shutdown via NTC input

| Symbol                    | Parameter                                                              | Test conditions | Min.              | Тур.              | Max.     | Unit      |

|---------------------------|------------------------------------------------------------------------|-----------------|-------------------|-------------------|----------|-----------|

| V <sub>NTC_FSR</sub>      | NTC input voltage full-<br>scale range                                 |                 | VSENSE_N -<br>1.2 | -                 | VSENSE_N | V         |

| V <sub>NTC_M</sub>        | NTC_M output voltage                                                   |                 | -                 | VSENSE_N -<br>1.2 | -        | V         |

| V <sub>NTC_ACC</sub>      | NTC input voltage threshold accuracy                                   |                 | -5                | -                 | 5        | mV        |

| V <sub>NTC_THRS_0</sub>   |                                                                        |                 | -                 | 110.92            | -        |           |

| V <sub>NTC_THRS_1</sub>   |                                                                        |                 | -                 | 98.76             | -        |           |

| V <sub>NTC_THRS_2</sub>   |                                                                        |                 | -                 | 88.07             | -        |           |

| V <sub>NTC_THRS_3</sub>   |                                                                        |                 | -                 | 78.66             | -        |           |

| V <sub>NTC_THRS_4</sub>   |                                                                        |                 | -                 | 70.38             | -        |           |

| V <sub>NTC_THRS_5</sub>   |                                                                        |                 | -                 | 63.08             | -        |           |

| V <sub>NTC_THRS_6</sub>   |                                                                        |                 | -                 | 56.64             | -        |           |

| V <sub>NTC_THRS_7</sub>   | External FET thermal                                                   |                 | -                 | 50.95             | -        |           |

| V <sub>NTC_THRS_8</sub>   | shutdown NTC input voltage thresholds                                  |                 | -                 | 45.92             | -        | mV        |

| V <sub>NTC_THRS_9</sub>   |                                                                        |                 | -                 | 41.46             | -        |           |

| V <sub>NTC_THRS_10</sub>  |                                                                        |                 | -                 | 37.50             | -        |           |

| V <sub>NTC_THRS_11</sub>  |                                                                        |                 | -                 | 37.50             | -        |           |

| V <sub>NTC_THRS_12</sub>  |                                                                        |                 | -                 | 37.50             | -        |           |

| V <sub>NTC_THRS_13</sub>  |                                                                        |                 | -                 | 37.50             | -        |           |

| V <sub>NTC_THRS_14</sub>  |                                                                        |                 | -                 | 37.50             | -        |           |

| V <sub>NTC_THRS_15</sub>  |                                                                        |                 | -                 | 37.50             | -        |           |

| V <sub>NTC_DEGLITCH</sub> | External FET thermal shutdown deglitch time                            |                 | 10                | -                 | 500      | μs        |

| V <sub>NTC_ADC_CONV</sub> | External FET thermal shutdown ADC full range resolution <sup>(1)</sup> |                 | 0                 | -                 | 1023     |           |

| V <sub>NTC_ADC_RATE</sub> | External FET thermal shutdown ADC sample rate                          |                 | -                 | 4.9               | -        | kSample/s |

<sup>1.</sup>  $V_{NTC}(V) = V_{NTC\_ADC}[9:0] * 1.2 / 1024$  $R_{NTC}(\Omega) = V_{NTC} * R_{T\_REF} / (V_{BG} - V_{NTC}).$

DS14109 - Rev 7 page 15/79

Figure 4. NTC bridge

Note:

- $V_{NTC}(V) = V_{NTC\_ADC}[9:0] * 1.2 / 1024$

- $R_{NTC}(\Omega) = V_{NTC} * R_{T\_REF} / (V_{BG} V_{NTC}).$

- $R_{NTC} = B57232V5103F360 (10 k\Omega at 25 °C)$

- $R_{T\_REF} = 10 k\Omega \pm 1\%$

- $V_{BG} = 1.2 \text{ V}$

Table 21. Bypass switch

| Symbol                           | Parameter                                                    | Test conditions                                                | Min. | Тур. | Max. | Unit |

|----------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|------|------|------|------|

| V <sub>DS_BYPASS_SAT</sub>       | Bypass switch VDS saturation protection threshold            |                                                                | 1    | -    | 2    | V    |

| I <sub>BYPASS_SAT</sub>          | Bypass switch saturation current                             | V <sub>S</sub> - V <sub>OUT</sub> = V <sub>DS_BYPASS_SAT</sub> | 297  | 572  | 900  | mA   |

| R <sub>DS(ON)_BYPASS</sub>       | Bypass switch on state resistance                            |                                                                | 1    | 2    | 4.5  | Ω    |

| t <sub>ON_BYPOFF</sub>           | Output turn-on time on bypass-shutting off                   |                                                                | -    | -    | 100  | μs   |

| t <sub>BYPASS_SAT_DEGLITCH</sub> | Bypass switch saturation diagnostic de-glitch filtering time | Standby state                                                  | -20% | 5    | +20% | μs   |

Table 22. V<sub>OUT</sub> A-to-D conversion

| Symbol                    | Parameter                                                 | Test conditions                | Min. | Тур. | Max. | Unit      |

|---------------------------|-----------------------------------------------------------|--------------------------------|------|------|------|-----------|

| V <sub>OUT_ADC_CONV</sub> | V <sub>OUT</sub> ADC full range resolution <sup>(1)</sup> |                                | 0    | -    | 1023 |           |

| V <sub>OUT_ADC_RATE</sub> | V <sub>OUT</sub> ADC sample rate                          |                                | -    | 4.9  | -    | kSample/s |

| V <sub>OUT_ACC_1V</sub>   | Output voltage accuracy                                   | 1 < V <sub>OUT</sub> ≤ 2 V     | -18  | -    | 18   | %         |

| V <sub>OUT_ACC_2V</sub>   | Output voltage accuracy                                   | 2 V < V <sub>OUT</sub> ≤ 3 V   | -9   | -    | 9    | %         |

| V <sub>OUT_ACC_3V</sub>   | Output voltage accuracy                                   | 3 V < V <sub>OUT</sub> ≤ 12 V  | -6   | -    | 6    | %         |

| V <sub>OUT_ACC_12</sub> V | Output voltage accuracy                                   | 12 V < V <sub>OUT</sub> ≤ 60 V | -3   | -    | 3    | %         |

1.  $V_{OUT}(mV) = V_{OUT\_ADC}[9:0] * 1.2 * 51 / 1024.$

DS14109 - Rev 7 page 16/79

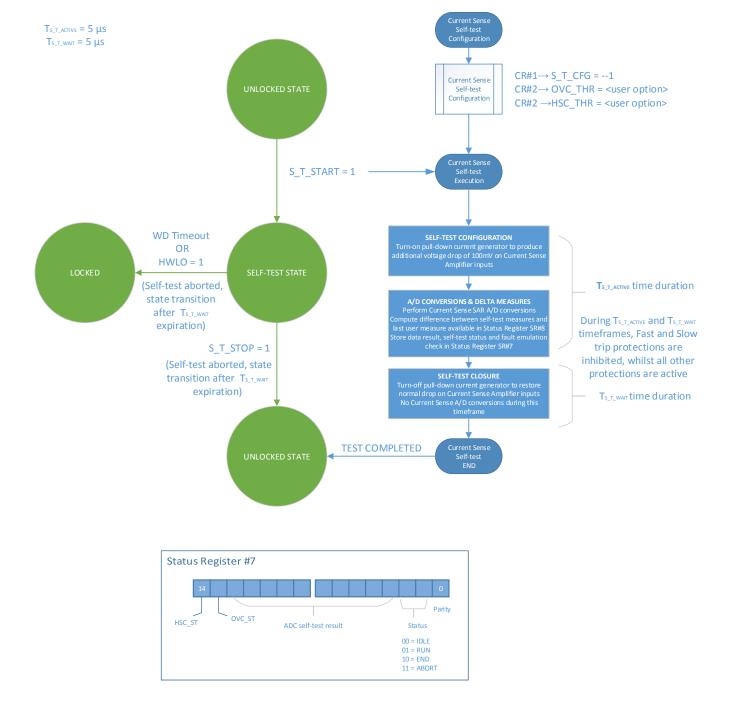

#### Table 23. Self-test timing

| Symbo               | 1    | Parameter                | Test conditions | Min. | Тур. | Max. | Unit |

|---------------------|------|--------------------------|-----------------|------|------|------|------|

| ts_t_acti           | VE S | Self-test execution time |                 | -10% | 5    | +10% | μs   |

| t <sub>S_T_WA</sub> | IT S | Self-test wait time      |                 | -10% | 5    | +10% | μs   |

DS14109 - Rev 7 page 17/79

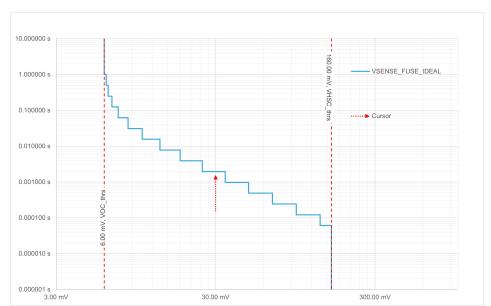

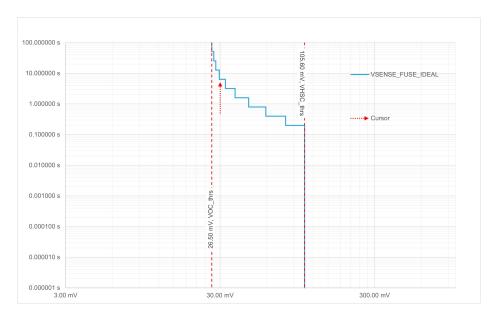

#### 3 eFuse function

Protection of wire harness and PCB can be performed by defining an ideal time to fuse curve as a result of a maximum power dissipation over the time in the wire or copper PCB traces themselves. This function can ensure that the insulation of wires and PCB are subject to a limited temperature and time budget that is below the reliability specified values. Not respecting such specified limits can lead to the formation of a conducting path by carbonization across the organic insulation materials and therefore local hot spot can conduct to sparking and fire ignition.

The VNF1248F embeds the ST proprietary eFuse functionality for the implementation of a robust and flexible overcurrent protection mechanism. The eFuse functionality features an intelligent circuit breaking aimed at protecting PCB traces, connectors and wire harness from overheating, with no impact on load transients like inrush currents and capacitance charging.

This function is set by two parameters called  $I_{NOM}$  and  $t_{NOM}$ . The value of  $I_{NOM}$  corresponds to the maximum continuous current while  $t_{NOM}$  will determine a current versus time-to-fuse curve when load current is higher than  $I_{NOM}$ . The expression of current versus time-to-fuse is approximated by an optimized stepwise function, which can be adjusted in a range between the wire  $I^2$ -t limit on one side and load transient characteristics on the other side. The value of  $t_{NOM}$  corresponds to the first step up of the curve. The current time curve is always active in combination with very fast overcurrent protection that will be triggered when the current reaches a defined threshold for hard short circuit condition.

When the current in the load is pulse wide modulated the eFuse function calculates the mean square root of the current. Mean square root of the current is also calculated when switching on/off the power switch during normal operation or after a switch off due to short circuit/overload condition. So, if for example the circuit is broken due to an overload and after a while the circuit is activated again, the eFuse keeps in memory the previous condition and still avoids that maximum I<sub>RMS</sub> is higher than I<sub>NOM</sub>.

VIP-Fuse is programmed via SPI as follows:

- VOC THRS sets I<sub>NOM</sub> = VOC THRS/Rsense

- VHSC\_THRS sets hard short circuit current = VHSC\_THRS/Rsense

- T\_NOM sets t<sub>NOM</sub> from 1 to 511 s

No intervention occurs for VSENSE < VOC\_THRS, whilst an immediate shut-off occurs for VSENSE > VHSC\_THRS.

The eFuse functionality operating range is defined between VOC\_THRS and VHSC\_THRS. In that range, the circuit breaking profile is defined by the stepwise function reported in Figure 5. The number of steps is consequential to the selection of VOC\_THRS and VHSC\_THRS, the maximum being 15, when VOC\_THRS = 6 mV and VHSC\_THRS = 160 mV. This corresponds to a 1:26.67 ratio between the maximum allowed continuous current and hard short circuit.

The Figure 6 shows the  $I^2$ -t curve when VOC\_THRS = 26.5 mV and VHSC\_THRS = 105.60 mV. The number of steps is reduced to 9 accordingly.

DS14109 - Rev 7 page 18/79