## Standalone SINK USB PD controller

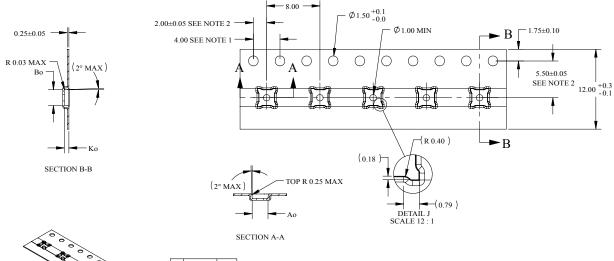

QFN-16 3 x 3 mm<sup>2</sup>

**CSP-16** 2.3 x 2.3 mm<sup>2</sup>

### **Maturity status link**

STUSB4531

### **Features**

- Up to 5 SINK PDO profiles (fixed, variable, PPS)

- Static or dynamic PDO configuration support

- Source profile reporting

- Standalone PD stack

- · Hybrid software mode

- Active V<sub>BUS</sub> voltage monitoring

- Integrated system and cable discharge path

- Integrated V<sub>BUS</sub> switches gate driver (PMOS)

- External Vconn support

- Short-to-V<sub>BUS</sub> protections

- AMR = 28 V

- Temperature range: -40 °C up to 105 °C

- ESD = 1 kV CDM / 4 kV HBM

#### Certification

- USB Type-C® (rev2.4)

- USB Power delivery specifications (rev3.2)

- TID: 13956

- EU conformity: IEC 62680-1-3:2024 / IEC 62680-1-2:2024

# **Applications**

- USB micro-B and DC barrel replacement

- VBUS powered, battery powered, and externally powered applications

- Set-top-box, camcorders, cameras, gaming, displays, and TV

- IoT, drones, printers, 3D printers

- Computer accessories and data hubs

- Accessories and battery-powered devices

- · LED lighting and industrial

- · Healthcare and handheld devices

- Any Type-C / PD sink device

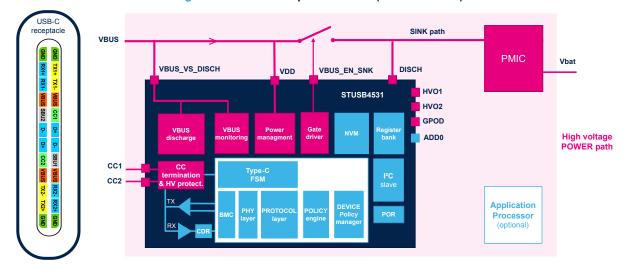

## **Description**

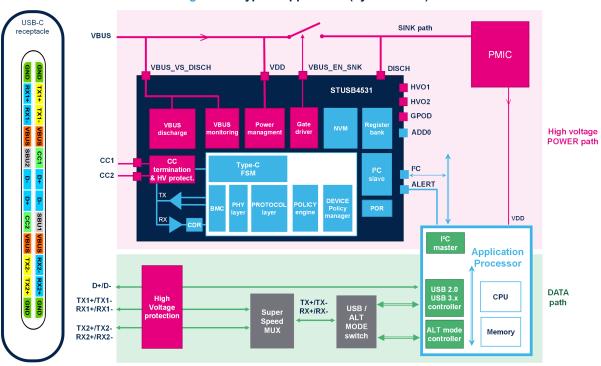

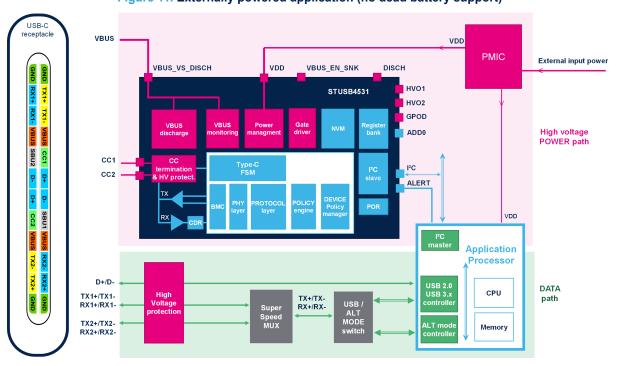

STUSB4531 addresses USB Type-C® sink devices. Based on default PDO configuration stored in an internal non-volatile memory, STUSB4531 implements proprietary algorithms to negotiate a power delivery contract with a source without any software support (autorun mode), making it the ideal device for automatic high power profile charging, especially from a dead battery power state.

STUSB4531 also implements a simple interface (hybrid mode) to support full feature applications with a light external software layer.

# 1 Functional description

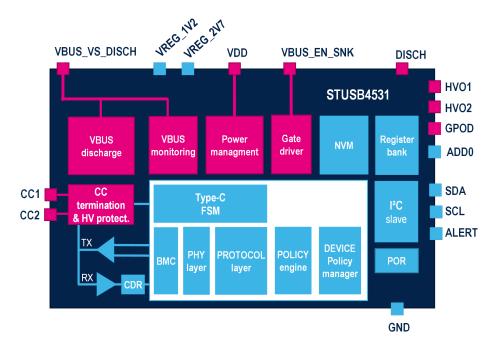

The STUSB4531 is a USB Type-C and power delivery controller IC designed for sink applications.

The main functions of STUSB4531 are:

- 1. Detect the connection between two ports (attach detection)

- 2. Establish a valid Source-to-Sink connection

- 3. Determine the attached device mode: Sink or Debug Accessory Mode (oriented or not)

- 4. Resolve cable orientation and twist connections to establish USB data routing (mux control)

- 5. Negotiate a USB PD contract with a PD capable device

- 6. Configure the power input path accordingly

- 7. Monitor VBUS, manage transitions, handle protections.

Additionally, STUSB4531 offers customizable Power Data Objects (PDO), an integrated discharge path and is natively robust to high-voltage surge, including on CC pins.

STUSB4531 addresses USB Type-C sink devices. Based on the default PDO configuration stored in an internal non-volatile memory, STUSB4531 implements proprietary algorithms to negotiate a power delivery contract with a source without any software support (Autorun mode), making it the ideal device for automatic high-power profile charging, especially from a dead battery power state. Additionally, STUSB4531 implements a simple interface to enable any kind of USB PD operation from an external MCU.

The product is available in 2 versions:

- with dead battery support to address battery/VBUS powered applications (STUSB4531QTR and STUSB4531BJR)

- without dead battery support to address externally powered applications (STUSB4531Q2TR)

Figure 1. Block diagram

DS15023 - Rev 1 page 2/50

# 2 Inputs/Outputs

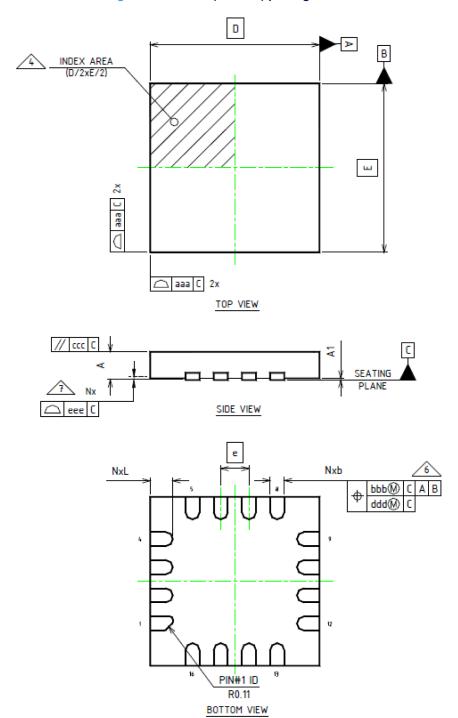

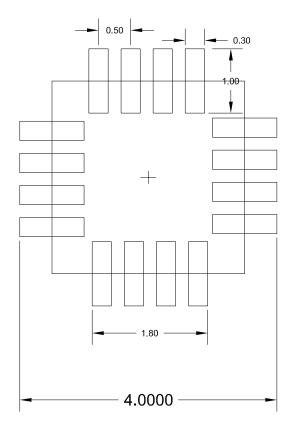

# 2.1 Pinout

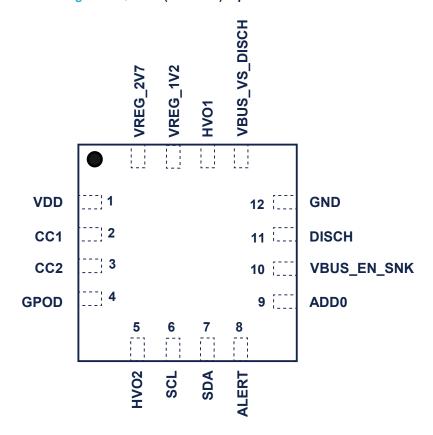

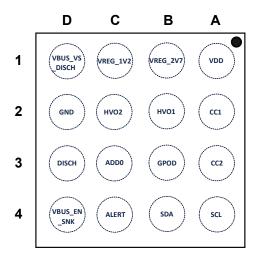

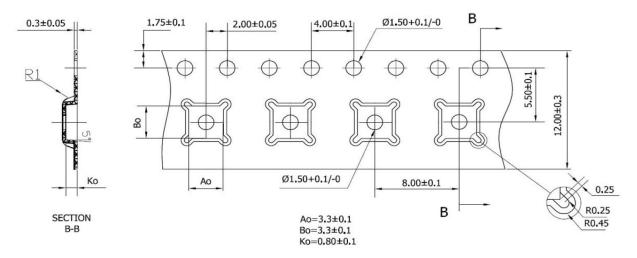

Figure 2. QFN-16 (3 x 3 mm) top view - not in scale

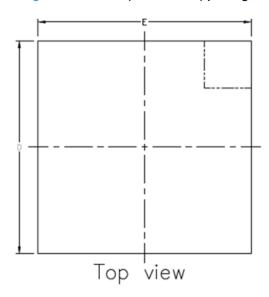

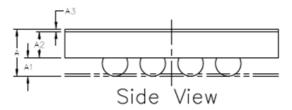

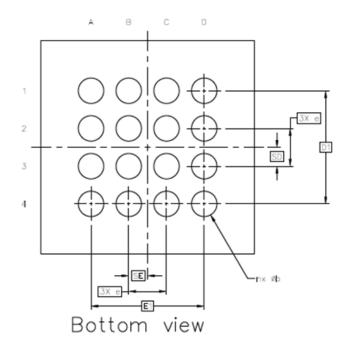

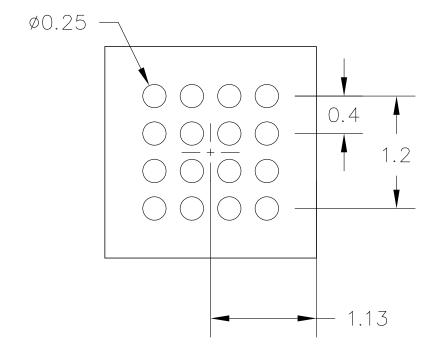

Figure 3. CSP-16 (2.3 x 2.3 mm) top view - not in scale

DS15023 - Rev 1 page 3/50

# 2.2 Pin list

Table 1. Detailed pin list (QFN and CSP)

| QFN | CSP        | Name          | Туре               | Description                                                           | Typical connection                                                               |

|-----|------------|---------------|--------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1   | <b>A</b> 1 | VDD           | High-voltage power | Main power supply (USB power line)                                    | from V <sub>BUS</sub> , receptacle side                                          |

| 2   | A2         | CC1           | HV analog input    | Type-C configuration channel 1                                        | to Type-C receptacle A5                                                          |

| 3   | А3         | CC2           | HV analog input    | Type-C configuration channel 2                                        | to Type-C receptacle B5                                                          |

| 4   | В3         | GPOD          | HV open drain      | General purpose output (open drain).                                  | By default: POWER_OK4                                                            |

| 5   | C2         | HVO2          | HV open drain      | High-voltage general output #2                                        | Power contract flag, active low. By default: POWER_OK3                           |

| 6   | <b>A</b> 4 | SCL           | Open drain         | I <sup>2</sup> C clock input                                          | a) to I <sup>2</sup> C master – ext. pull-up<br>b) to GND if not used            |

| 7   | B4         | SDA           | Open drain         | I <sup>2</sup> C data input/output – active low open drain            | a) to I <sup>2</sup> C master – ext. pull-up<br>b) to GND if not used            |

| 8   | C4         | ALERT         | Open drain         | I <sup>2</sup> C interrupt – active low open drain                    | a) to I <sup>2</sup> C master – ext. pull-up<br>b) to GND if not used            |

| 9   | C3         | ADD0          | Analog             | I <sup>2</sup> C device address configuration                         | I <sup>2</sup> C address: 1) 0x28: Pull down to GND 2) 0x29: Pull up to VREG_2V7 |

| 10  | D4         | VBUS_EN_SNK   | HV open drain      | VBUS sink power path enable, active low                               | To power switch or to power system, ext. pull-up                                 |

| 11  | D3         | DISCH         | HV open drain      | Internal discharge path or external discharge path enable, active low | To power path (system side) or to the discharge path switch, ext. pull-up        |

| 12  | D2         | GND           | Power              | Ground                                                                | Ground                                                                           |

| 13  | D1         | VBUS_VS_DISCH | HV open drain      | V <sub>BUS</sub> voltage monitoring and discharge path                | From V <sub>BUS</sub> , receptacle side                                          |

| 14  | B2         | HVO1          | HV open drain      | High-voltage general output #1                                        | Power contract flag, active low. By default: POWER_OK2                           |

| 15  | C1         | VREG_1V2      | Power              | 1.2 V internal regulator output                                       | 1 μF typ. decoupling capacitor                                                   |

| 16  | B1         | VREG_2V7      | Power              | 2.7 V internal regulator output                                       | 1 μF typ. decoupling capacitor                                                   |

DS15023 - Rev 1 page 4/50

## 2.3 Pin description

#### 2.3.1 VDD

This is the only power supply for the IC. It can be connected to VBUS from the USB Type-C receptacle, so that STUSB4531 is powered by VBUS.

### 2.3.2 GND

Ground.

### 2.3.3 CC1 / CC2

CC1 and CC2 are the configuration channel pins used for connection and attachment detection, plug orientation determination, USB power delivery communication, and system configuration management across USB Type-C cable.

Table 2. Dead battery and CC pins termination (QFN and CSP)

|                              | Dead battery support | CC pin termination                                                   |

|------------------------------|----------------------|----------------------------------------------------------------------|

| STUSB4531BJR<br>STUSB4531QTR | YES                  | always present (whatever VDD is powered or not)                      |

| STUSB4531Q2TR                | NO                   | present only when VDD is powered CC1 and CC2 are HiZ when unpowered. |

## 2.3.4 I<sup>2</sup>C interface pins

Table 3. I<sup>2</sup>C interface pin list

| Name  | Description                           |

|-------|---------------------------------------|

| SCL   | I²C clock, needs external pull-up     |

| SDA   | I²C data, needs external pull-up      |

| ALERT | l²C interrupt, needs external pull-up |

### 2.3.5 DISCH

This input/output pin can be used to implement a discharge path for a highly capacitive VBUS line on the power system side. When used as an input, the discharge is internal, and a serial resistor must be used to limit the discharge current through the pin. Maximum discharge current is 100 mA. The pin can also be used as an open drain output to control an external VBUS discharge path when a higher discharge current is required by the application, for instance. The pin is activated at the same time as the internal discharge path on VBUS\_VS\_DISCH pin. The discharge is activated automatically during cable disconnection, transition to a lower PDO voltage, hard reset, and error recovery state. The maximum discharge time is programmable by NVM (see Section 5: Startup configuration)

## 2.3.6 VBUS\_EN\_SNK

This pin handles the power path control and allows the incoming VBUS power (from the USB Type-C receptacle) to supply the application when a valid source is connected. The VBUS power path closure condition can be changed by NVM programming (see Section 3.6: VBUS power path and Section 5: Startup configuration).

### 2.3.7 VBUS VS DISCH

This input pin is used to sense VBUS presence, monitor VBUS voltage, and discharge VBUS from the USB Type-C receptacle side. A serial resistor must be used to limit the discharge current through the pin. Maximum discharge current is 50 mA. The discharge is activated automatically during cable disconnection, transition to a lower PDO voltage, hard reset, and error recovery state. The maximum discharge time is programmable by NVM (see Section 5: Startup configuration).

DS15023 - Rev 1 page 5/50

## 2.3.8 VREG\_1V2

This pin is used for external decoupling of the 1.2 V internal regulator.

## 2.3.9 VREG\_2V7

This pin is used for external decoupling of the 2.7 V internal regulator.

### 2.3.10 ADD0

ADD0 is latched at power-up to get the I2C ADDR0 of the device (see Section 4: I2C Interface).

## 2.3.11 General purpose I/O

### **GPOD**

This pin is an active low high voltage open drain output that can be configured by NVM as per Table 4. Depending on GPIO\_CONF value, it can be used either as:

- MISMATCH: "Capability mismatch" bit (active low, set during USB PD negotiation)

- VCONN CTRL1 : command to open or close external VCONN switch on the CC1 (active low)

- POWER\_OK4 : explicit contract based on variable or PPS Sink PDO (active low)

- SW\_GPOD : software driven output

### HVO[2:1]

These pins are active low high voltage open drain general purpose outputs. Different configurations are proposed as stated in Table 4 to meet specific application requirements.

The configuration of the GPIO pins can be changed by NVM programming (see Table 4). Depending on the programmed configuration (GPIO\_CONF), they can be used in combination with VBUS\_EN\_SNK pin to enable different power path scenarios.

Table 4. General purpose I/O pin configuration

| NVM parameter<br>GPIO_CONF[2:0] | Pin name              | Value | Description                                              |

|---------------------------------|-----------------------|-------|----------------------------------------------------------|

|                                 | GPOD = MISMATCH       | Hi-Z  | SOURCE capabilities offer enough power to the SINK       |

|                                 | GPOD - IVIISIVIATOR   | 0     | SINK unable to fully operate at the offered capabilities |

| 000b                            | HVO1 - VTDANS WINDOW  | Hi-Z  | no ongoing power negotiation                             |

| (conf 0)                        | HVO1 = VTRANS_WINDOW  | 0     | ongoing power negotiation                                |

|                                 | HVO2 = ERROR REC      | Hi-Z  | STUSB4531 is in normal operation                         |

|                                 | NVOZ = ERROR_REC      | 0     | STUSB4531 is in ErrorRecovery state                      |

|                                 | CDOD - VCONN, CTDI 4  | Hi-Z  | opens external CC1 VCONN switch                          |

|                                 | GPOD = VCONN_CTRL1    | 0     | closes external CC1 VCONN switch                         |

| 001b                            | HVO1 = VTRANS_WINDOW  | Hi-Z  | no ongoing power negotiation                             |

| (conf 1)                        |                       | 0     | ongoing power negotiation                                |

|                                 | LIVOS - VOONNI CTDI S | Hi-Z  | opens external CC2 VCONN switch                          |

|                                 | HVO2 = VCONN_CTRL2    | 0     | closes external CC2 VCONN switch                         |

|                                 | ODOD - MICMATCH       | Hi-Z  | SOURCE capabilities offer enough power to the SINK       |

|                                 | GPOD = MISMATCH       | 0     | SINK unable to fully operate at the offered capabilities |

| 010b                            | LIVO4 - DOWED OKO     | Hi-Z  | No PD explicit contract on fixed sink PDO2               |

| (conf 2)                        | HVO1 = POWER_OK2      | 0     | explicit contract based on fixed sink PDO2               |

|                                 | LIVO2 - DOWED OK2     | Hi-Z  | No PD explicit contract on fixed sink PDO3               |

|                                 | HVO2 = POWER_OK3      | 0     | explicit contract based on fixed sink PDO3               |

DS15023 - Rev 1 page 6/50

| NVM parameter<br>GPIO_CONF[2:0] | Pin name          | Value | Description                                               |

|---------------------------------|-------------------|-------|-----------------------------------------------------------|

|                                 | CDOD - DOWED OKA  | Hi-Z  | No PD explicit contract on variable or APDO PPS PDO       |

|                                 | GPOD = POWER_OK4  | 0     | explicit contract based on variable or APDO PPS PDO       |

| 011b                            | LIVO1 - DOWED OKO | Hi-Z  | No PD explicit contract on fixed sink PDO2                |

| (conf 3 - default)              | HVO1 = POWER_OK2  | 0     | explicit contract based on fixed sink PDO2                |

|                                 | LIVOR DOWED OVE   | Hi-Z  | No PD explicit contract on fixed sink PDO3                |

|                                 | HVO2 = POWER_OK3  | 0     | explicit contract based on fixed sink PDO3                |

|                                 | CDOD - CW CDOD    | Hi-Z  | Software controlled general purpose output (0x40 – bit 7) |

|                                 | GPOD = SW_GPOD    | 0     | Software controlled general purpose output (0x40 – bit 7) |

| 100b                            | HVO1 = POWER_OK2  | Hi-Z  | No PD explicit contract on fixed Sink PDO2                |

| (conf 4)                        |                   | 0     | explicit contract based on fixed Sink PDO2                |

|                                 | LIVO2 - DOWED OK2 | Hi-Z  | No PD explicit contract on fixed Sink PDO3                |

|                                 | HVO2 = POWER_OK3  | 0     | explicit contract based on fixed Sink PDO3                |

DS15023 - Rev 1 page 7/50

# Main features description

## 3.1 Dead battery mode

Dead battery mode (STUSB4531QTR and STUSB4531BJR) allows battery-powered systems to charge in any battery condition. Being powered directly from the  $V_{BUS}$  receptacle pins, the IC can run independently from the application battery state of charge, even if it is fully depleted (SOC = 0%). Therefore, STUSB4531 is powered only when a source is connected and never draws current from the local battery, contributing to extended battery lifetime.

For STUSB4531QTR and STUSB4531BJR, dead battery mode is always operating. The STUSB4531 presents a pull-down termination on its CC pins and advertises itself as a sink even when the device is not supplied.

When a source system connects to a USB Type-C port with STUSB4531, it detects the pull-down termination, establishes the source-to-sink connection, and provides the VBUS. The STUSB4531 is then supplied through the VDD pin, connected to VBUS on the USB Type-C receptacle side.

The STUSB4531 can finalize the connection and enable the system power path thanks to the VBUS\_EN\_SNK pin, which allows the system to be powered.

By contrast, for STUSB4531Q2TR, dead battery mode is disabled, preventing correct biasing of sink termination if the IC is not already powered. This is the expected behavior for USB PD sink controllers in application that are externally powered. In this case, STUSB4531 is detected by SOURCES only when the application is powered, and not detected when the application is off.

# 3.2 CC pin interface

## 3.2.1 Functionality

The STUSB4531 controls the connection to the configuration channel (CC) pins, CC1 and CC2, through two main blocks: the CC line interface block and the CC control logic block.

The CC line interface block is used to:

- Set pull-down termination mode on the CC pins

- Monitor the CC pin voltage values related to the attachment detection thresholds

- Protect the CC pins against overvoltage

The CC control logic block is used to:

- Execute the Type-C FSM related to the sink power role with debug accessory support

- Determine the electrical state for each CC pin related to the detected thresholds

- Evaluate the conditions relative to the CC pin states and the VBUS voltage value to transition from one state to another in the Type-C FSM

- Advertise a valid source-to-sink connection

- Determine the attached device mode: source or debug accessory (oriented or not)

- Determine cable orientation to allow external routing of the USB data

- Report USB Type-C power capability on VBUS: USB default, medium, or high current mode

- Handle hardware faults

## 3.2.2 High-voltage protection

The STUSB4531 can be safely used in systems or connected to systems that handle high voltage on the VBUS power path. The device integrates an internal circuitry on the CC pins that tolerates high voltage and ensures protection up to 24 V in case of unexpected short-circuits with the VBUS.

DS15023 - Rev 1 page 8/50

## 3.3 Power delivery blocks

## 3.3.1 Physical layer (PHY)

The physical layer defines the signaling technology for USB power delivery. It is the physical link between CC pins and the protocol layer. In Tx mode, it receives packet data from the protocol layer, calculates and appends a CRC, encodes the payload (i.e. packet data and CRC), and transmits the packet (i.e. preamble, SOP\*, payload, CRC and EOP) using biphase mark coding (i.e. BMC) over CC pins. In Rx mode, it recovers the clock and the data, detects the SOP\*, decodes the received data including the CRC, detects the EOP, and validates the CRC.

#### 3.3.2 Protocol layer (PRL)

The protocol layer has the responsibility to manage the messages from/to the physical layer. It automatically manages the protocol receiver timeouts, the message counter, the retry counter, and the GoodCRC messages. It communicates with the internal policy engine.

## 3.3.3 Policy engine (PE)

The policy engine implements the power negotiation with the connected device according to its sink role. It implements all state machines controlling the protocol layer that forms and schedules the messages. The policy engine uses the protocol layer to send/receive messages. The policy engine interprets the device policy manager's input to implement policy for port and directs the protocol layer to send appropriate messages.

### 3.3.4 Device policy manager (DPM)

The device policy manager deals with the power capability request and change management. It operates according to the decision algorithm described in Section 3.4: Autorun mode or according to Section 3.5: Hybrid mode.

### 3.4 Autorun mode

#### 3.4.1 Overview

The STUSB4531 implements a configurable and hardcoded decision algorithm in the DPM allowing the device to negotiate autonomously a power delivery transaction with a source according to predefined power profiles called PDO (power data objects) configured in the NVM. It makes the STUSB4531 a plug-and-play, autonomous and effective solution to develop USB PD sink systems operating in standalone (ie. without external MCU support).

Additionally, STUSB4531 is also able to answer autonomously to any incoming mandatory message request using NVM default settings.

More complex power negotiation can also be managed with limited software support from the MCU. At any time, it is indeed possible to monitor, via a few I²C accesses, the status of standalone operations, the USB Type-C port, or the ongoing power negotiation. For instance, the MCU can ask STUSB4531 to collect source capabilities, overwrite default PDO settings, change negotiation algorithm parameters, or force STUSB4531 to renegotiate a power delivery contract according to new application requirements. With this limited external assistance, STUSB4531 handles incoming and outgoing messages autonomously, while still allowing dynamic application settings.

### 3.4.2 Power data objects (PDO) configuration

The STUSB4531 features up to 3 FIXED PDOs (1 minimum) + 1 optional VARIABLE PDO + 1 optional programmable power supply APDO or both:

- FIXED PDO can be used to support mandatory voltage nodes (9 V, 15 V, 20 V) or a custom voltage value.

- VARIABLE PDO is defined with MINIMUM and MAXIMUM voltage values (from 5 V to 20 V), and an OPERATING current (up to 5 A)

- PPS APDO is defined with MINIMUM and MAXIMUM voltage values (from 5 V to 21 V), and a MAXIMUM current (up to 5 A)

The number of fixed PDO, their value, and the selection of optional VARIABLE PDO or PPS APDO, and their respective value can be programmed in the non-volatile-memory and/or updated by software (volatile I<sup>2</sup>C registers). See Section 5: Startup configuration.

DS15023 - Rev 1 page 9/50

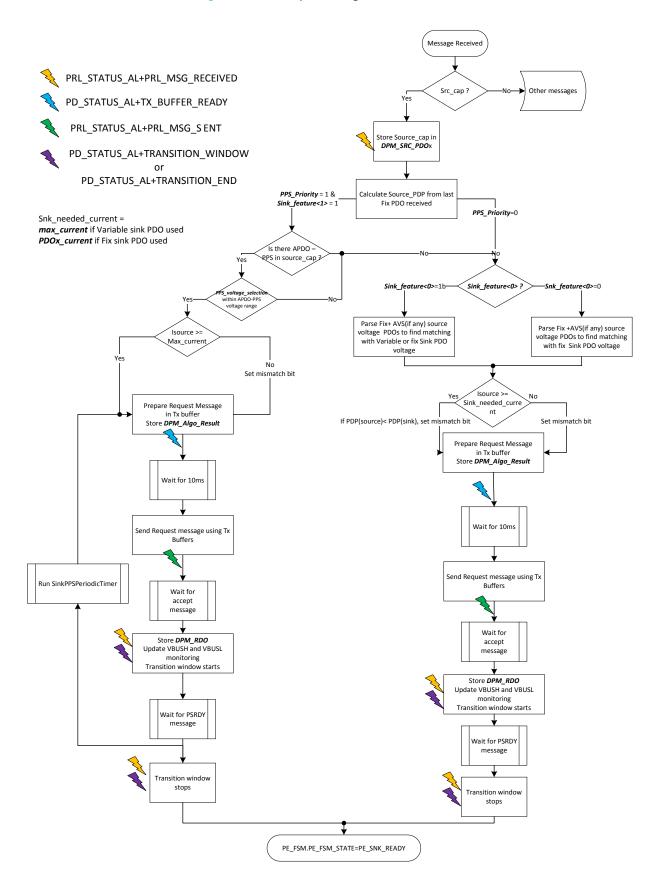

## 3.4.3 Power negotiation algorithm (AUTORUN)

The decision algorithm first compares the SOURCE maximum power delivery power (PDP) with the SINK PDP. The source PDP is calculated based on its highest voltage FIXED PDO profile. The result is used to set the MISMATCH bit in the RDO of the PDO requested.

Then, the algorithm compares the STUSB4531 PDOs (SNK\_PDOi) with the PDO received from the source (SRC\_PDOj). Table 5 summarizes the compatibility between SINK and SOURCE PDOs, depending on their type. For instance, a PPS negotiation is possible only when both SINK and SOURCE are compatible (support of PPS APDO respectively).

| PDO TYPES           | FIXED PDO<br>(SOURCE) | AVS APDO<br>(SOURCE) | PPS APDO<br>(SOURCE) | VARIABLE PDO<br>(SOURCE) | BATTERY PDO<br>(SOURCE) |

|---------------------|-----------------------|----------------------|----------------------|--------------------------|-------------------------|

| FIXED PDO (SINK)    | yes                   | yes                  | ignore               | ignore                   | ignore                  |

| VARIABLE PDO (SINK) | yes                   | yes                  | ignore               | ignore                   | ignore                  |

| PPS APDO (SINK)     | ignore                | ignore               | yes                  | ignore                   | ignore                  |

Table 5. SINK PDO interoperability with SOURCE PDO in autorun mode

Note:

PPS\_APDO is not exposed in case of connection with a USB PD2.0 source.

Source PDOs marked as "ignore" are not considered by the STUSB4531 internal power negotiation algorithm. However, a more complex decision algorithm can still be implemented in software running on an external application MCU. This is possible by overwriting, before the end of the allocated time, the default PDO request message prepared by the STUSB4531 internal decision algorithm.

If a PPS APDO is available, the algorithm prioritizes a PPS contract (assuming SOURCE also supports PPS APDO) only if PPS\_PRIORITY = 1. By default (PPS\_PRIORITY = 0), the algorithm looks for an explicit contract with the highest power delivery power (PDP) based on all possible combinations of FIXED/VARIABLE PDOs comparisons. At equivalent PDP, the one with the highest voltage is selected. At identical conditions, an AVS contract is preferred to a FIXED contract.

### a) Fixed PDO comparison (between SINK and SOURCE)

STUSB4531 FIXED PDO is compared by default with FIXED PDO from the SOURCE, starting from the highest voltage PDO to the lowest.

Voltage is compared first, current afterwards (ISINK = PDP/VSINK)

If VSOURCE = VSINK, the algorithm:

- stops if ISOURCE ≥ ISINK,

- stops if ISOURCE < ISINK and MISMATCH\_PD is set to "Any current",

- continues with a lower-priority PDO if ISOURCE < ISINK and MISMATCH PD is set to "Enough current".

- □ No PDO request is generated based on scanned PDO

When the algorithm stops on a given voltage node, an RDO (request data object) message is formed and sent to the source. If accepted, the source transitions to the matched PDO voltage and sends a PS\_READY message to the sink, signaling the end of the power transition.

| V <sub>SOURCE</sub> | I <sub>SOURCE</sub> | MISMATCH_PD        | REQUESTED CURRENT     |

|---------------------|---------------------|--------------------|-----------------------|

|                     | ≥ I <sub>SINK</sub> | do not care        | ISINK                 |

| = V <sub>SINK</sub> |                     | = "Any current"    | Isource               |

|                     | < I <sub>SINK</sub> | = "Enough current" | No contract, next PDO |

Table 6. Fixed PDO summary

At the end of the comparison loop, if no match happens, the USB PD negotiation ends with an explicit USB PD contract: an RDO message is sent to the source on PDO1 with capability mismatch enabled, operating and maximum current set to source current.

DS15023 - Rev 1 page 10/50

### b) Fixed PDO (SINK) comparison with AVS APDO (SOURCE)

STUSB4531 FIXED PDO(s) are by default compared with AVS APDO from the SOURCE, when available, and with FIXED PDO(s) from the SOURCE.

The algorithm looks for a compatible voltage, and if any, a compatible current. If both are met, a PDO request is made according to the table below. If one condition is missing, current PDOi is skipped, and the algorithm looks for a lower priority PDO.

Condition / comment Field value **RDO** parameter V\_FIX\_PDOi<sub>(SINK)</sub> < 9 V no RDO; Skip to a lower priority SINK PDO V\_FIX\_PDOi(SINK) > V\_AVS\_max(SOURCE) no RDO; Skip to a lower priority SINK PDO **VOLTAGE** V\_AVS\_min(SOURCE) ≤V\_FIX\_PDOi(SINK)  $V_{REQ} = V_FIX_PDOi_{(SINK)}$ ≤V\_AVS\_max(SOURCE) I<sub>OPERATING</sub> = I\_FIX\_PDOi<sub>(SINK)</sub> I\_FIX\_PDOi<sub>(SINK)</sub> ≤ I\_AVS<sub>(SOURCE)</sub> CAPA\_MISMATCH = 0 I\_FIX\_PDOi(SINK) > I\_AVS(SOURCE) I<sub>OPERATING</sub> = I\_AVS<sub>(SOURCE)</sub> **CURRENT** MISMATCH\_PD = "Any current" CAPA\_MISMATCH = 1 I\_FIX\_PDOi(SINK) >I\_AVS(SOURCE) no RDO; Skip to a lower priority SINK PDO MISMATCH\_PD = "Enough current"

Table 7. Fixed PDO with AVS APDO summary

# c) VARIABLE\_PDO (SINK) comparison with FIXED\_PDO (SOURCE)

The algorithm also compares STUSB4531 VARIABLE PDO (when instantiated) with FIXED PDOi from the SOURCE, starting from the highest voltage PDO to the lowest.

The algorithm looks for a compatible voltage, and if any, a compatible current. If both are met, a PDO request is made according to the table below. If one condition is missing, the current PDO is skipped, and the algorithm looks for a lower priority PDO.

Table 8. Variable PDO with FIXED PDO summary

| RDO parameter | Condition / comment                                                                         | Field value                                                        |

|---------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|               | V_FIX_PDOi <sub>(SOURCE)</sub> > V_VAR_max <sub>(SINK)</sub>                                | no RDO; Skip to a lower priority SOURCE PDO                        |

| VOLTAGE       | V_FIX_PDOi <sub>(SOURCE)</sub> < V_VAR_min <sub>(SINK)</sub>                                | no RDO; Skip to a lower priority SOURCE PDO                        |

| VOLIAGE       | V_VAR_min <sub>(SINK)</sub> ≤V_FIX_PDOi <sub>(SOURCE)</sub><br>≤V_VAR_max <sub>(SINK)</sub> | V <sub>REQ</sub> = V_FIX_PDOi <sub>(SOURCE)</sub>                  |

|               | I_FIX_PDOi <sub>(SOURCE)</sub> ≥ I_VAR <sub>(SINK)</sub>                                    | I <sub>OPERATING</sub> = I_VAR <sub>(SINK)</sub> CAPA_MISMATCH = 0 |

| CURRENT       | I_FIX_PDOi <sub>(SOURCE)</sub> < I_VAR <sub>(SINK)</sub>                                    | I <sub>OPERATING</sub> = I_FIX_PDOi <sub>(SOURCE)</sub>            |

| CORRENT       | MISMATCH_PD = "Any current"                                                                 | CAPA_MISMATCH = 1                                                  |

|               | I_FIX_PDOi <sub>(SOURCE)</sub> < I_VAR <sub>(SINK)</sub> MISMATCH_PD = "Enough current"     | Skip to a lower priority SOURCE PDO                                |

DS15023 - Rev 1 page 11/50

### d) VARIABLE\_PDO (SINK) comparison with AVS\_APDO (SOURCE)

VARIABLE PDO are compared by default with FIXED PDO from the SOURCE (see previous section), but also, when available, with AVS APDO from the SOURCE.

If PDP<sub>SOURCE</sub> > PDP<sub>SINK</sub>, the algorithm looks for a compatible voltage, and if any, a compatible current. If both are met, a PDO request is made according to the table below. If one condition is missing, the current PDO is skipped, and the algorithm looks for a lower priority PDO

| RDO parameter | Condition / comment                                               | Field value                                                                              |

|---------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|               | V_VAR_max <sub>(SINK)</sub> < 9 V                                 | check fix SOURCE PDOs, otherwise skip to lower SINK PDO priority                         |

| VOLTAGE       | V_VAR_min <sub>(SINK)</sub> > V_AVS_max <sub>(SOURCE)</sub>       | Check SOURCE fixed PDO otherwise lower sink PDO priority                                 |

|               | V_VAR <sub>(SINK)</sub> compatible with V_AVS <sub>(SOURCE)</sub> | V <sub>REQ</sub> = Min (V_AVS_max <sub>(SOURCE)</sub> ;<br>V_VAR_max <sub>(SINK)</sub> ) |

|               | I_VAR(SINK) ≤ I_AVS(SOURCE)                                       | I <sub>OPERATING</sub> = I_VAR <sub>(SINK)</sub>                                         |

|               | I_VAIN(SINK) = I_AVO(SOURCE)                                      | CAPA_MISMATCH = 0                                                                        |

| CURRENT       | I_VAR <sub>(SINK)</sub> > I_AVS <sub>(SOURCE)</sub>               | I <sub>OPERATING</sub> = I_AVS <sub>(SOURCE)</sub>                                       |

| CORRENT       | MISMATCH_PD = "Any current"                                       | CAPA_MISMATCH = 1                                                                        |

|               | I_VAR <sub>(SINK)</sub> > I_AVS <sub>(SOURCE)</sub>               | no RDO; Skip to a lower priority SINK PDO                                                |

|               | MISMATCH_PD = "Enough current"                                    | TIO REO, SKIP to a lower priority SHAK FEO                                               |

Table 9. Variable PDO with AVS APDO summary

### e) PPS\_APDO comparison (between SINK and SOURCE)

PPS negotiation has been introduced to enable ultra-fast battery charging based on custom algorithms. It relies on very fine grain voltage stepping (20 mV) and high current. Therefore, an advanced charging algorithm is implemented at the application processor level. STUSB4531 facilitates PPS negotiation by continuously repeating PPS requests according to standard requirements (ie, with a maximum period of 10 seconds) without any MCU specific action.

STUSB4531 PPS APDO is compared only with PPS APDO from the SOURCE. Other SOURCE PDO types are ignored.

An initial voltage is negotiated according to the PPS\_VOLTAGE\_SELECTION setting. If the SOURCE is compatible, a request is done automatically considering SOURCE and SINK PDPs. If no specific action is taken by the MCU, the request is repeated every 10 seconds maximum to maintain an active PPS connection (keep alive). At any time, the MCU can modify the voltage requirements up or down.

## 3.5 Hybrid mode

In this mode, the STUSB4531 shares policy engine (PE) and device policy manager (DPM) tasks with an external MCU. Both rely on the physical layer (PHY) and protocol layer (PRL) resources of the chip, significantly decreasing the software complexity from the user's standpoint. This mode requires average understanding of the USB PD protocol, and average software skills:

- STUSB4531 PE and DPM are used in autorun mode to handle the initial power delivery negotiation and guarantee effective system powering and boot. Extra features can then be managed by software with a stable power connection.

For every incoming message, STUSB4531 prepares an answer, and simultaneously, an interrupt is sent to the application MCU. The application software can then decide whether the default answer is appropriate or should be overridden with more relevant application information.

At the end of the allocated time, with or without MCU action, the answer (default or updated) is sent by STUSB4531 to the source, and so on, and so forth.

- Finally, any sequence can be initiated by using this mode.

DS15023 - Rev 1 page 12/50

With minimum software code, hybrid mode enables advanced users to implement the most advanced features defined by the standard seamlessly, without being a specialist of the protocol itself. Additionally, it saves MCU resources related to the implementation of the lower-level protocol layers, associated actions, and protections.

The detailed list of supported transmitted/received messages is available from a separate user manual. It describes the handling of control, data, extended data, and extended control messages, as well as VDM commands and reset signaling.

This mode is very effective for:

- Updating battery messages in real time

- Structured vendor define message support

- Alternate mode support

- Message support (non exhaustive list):

- Get source capabilities

- Get extended capabilities

- Get manufacturer information

- Get country codes / information

- PPS update requests

- Any request message

# 3.6 VBUS power path

#### 3.6.1 VBUS assertion

The STUSB4531 controls the assertion of the VBUS power path from the USB Type-C receptacle, directly or indirectly, through the VBUS\_EN\_SNK pin.

To handle different application requirements, the following parameters are used to define the voltage and current condition in which the power path must be closed:

| PARAMETER        | FUNCTION                                                                                                                                                                                    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABOVE_5V         | Prevents VBUS switch from closing at USB Type-C attach in case 5 V is not supported by the application (MISMATCH_5V is then "don't care").                                                  |

| MISMATCH_5V      | This parameter prevents the VBUS switch from closing if available current at 5 V is less than required by the application during the TypeC phase or if PDO1 is negotiated.                  |

| MISMATCH_PD      | For PDO higher than PDO1, it allows to request a matching voltage profile even in case of current mismatch (if PDO is equal to PDO1, MISMATCH_5V condition applies instead of MISMATCH_PD). |

| PDO_0mA_MISMATCH | STUSB4531 opens the VBUS switch to limit sinking current (no load) when current offer from source is 0 mA.                                                                                  |

Table 10. Power path parameters

The table below summarizes the operating conditions that determine the electrical value of the VBUS\_EN\_SNK pin, and therefore the closure of the VBUS switch (powering the system).

| ABOVE_5V | MISMATCH_5V | Power path                                                                                                                                                     |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 0           | Power path is closed at USB Type-C attach, whatever USB Type-C source current  VBUS_EN_SNK = 0                                                                 |

| 0        | 1           | Power path is closed at USB Type-C attach if USB Type-C or PDO1 source current is equal or greater than PDO1 Sink current                                      |

|          |             | $\label{eq:VBUS_EN_SNK} VBUS\_EN\_SNK = High Z if I\_Rp_{(SOURCE)} < I\_FIX\_PDO1_{(SINK)} or I\_FIX\_PDO1_{(SOURCE)} < I\_FIX\_PDO1_{(SINK)}$                 |

|          |             | $\label{eq:VBUS_EN_SNK} VBUS\_EN\_SNK = 0 \text{ if } I\_Rp(SOURCE) \geq I\_FIX\_PDO1_{(SINK)} \text{ or } I\_FIX\_PDO1_{(SOURCE)} \geq I\_FIX\_PDO1_{(SINK)}$ |

DS15023 - Rev 1 page 13/50

| ABOVE_5V | MISMATCH_5V | Power path                                                                                                                              |

|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1        | -           | VBUS switch does not close with a source USB Type-C only, or for a USB PD source before an explicit contract and if PDO1 is negotiated. |

|          |             | VBUS_EN_SNK = High Z                                                                                                                    |

At the end of USB Type-C operations (Attach detection), the VBUS switch can be either closed (default) or open (application not managing 5 V or only with a minimum amount of current). See Figure 4.

USB PD negotiation between the SOURCE and STUSB4531 is then starting and may close VBUS\_EN\_SNK (if not closed during USB Type-C operation according to negotiation results). See Figure 5

Unattach CC event Attach\_wait Wait for tCCdebounce Is Above\_5V? Is Mismatch\_5V? Yes Yes Rp current >: Yes I\_PDO1? Vbus >= 4.01V Vbus >= 4.01V -No Yes Attach\_SNK Keep VBUS\_EN\_SNK VBUS\_EN\_SNK opened closed

Figure 4. USB Type-C connection flow chart

I PDO1 defined by SNK PDO PARAMS.VSAFE 5V CURRENT

CONNECTION\_STATUS\_AL+ CC\_STATUS\_AL

CONNECTION\_STATUS\_AL+ ATTACH\_STATUS\_AL

DS15023 - Rev 1 page 14/50

Figure 5. USB-PD power negotiation flow chart

DS15023 - Rev 1 page 15/50

## 3.6.2 VBUS monitoring

This monitoring block supervises the VBUS voltage from the VBUS\_VS\_DISCH input pin (the USB Type-C receptacle side). It is used to check that VBUS is within a valid voltage range to establish a valid source-to-sink connection and to safely enable the VBUS power path through the VBUS\_EN\_SNK pin.

It detects unexpected VBUS voltage conditions such as undervoltage or overvoltage relative to the negotiated VBUS voltage.

When such conditions occur, the STUSB4531 reacts as follows:

- At attachment, it prevents the source-to-sink connection to be established and the VBUS power path to be asserted

- After attachment, it disables the VBUS power path, protecting the application and goes into unattached state or ErrorRecovery state.

The valid VBUS voltage range is defined by a low limit VTH\_LOW and a high limit  $V_{TH\_HIGH}$ . Those limits depend on system operation and VBUS negotiated voltage ( $V_{RDO}$ ). As per USBPD standard, source dispersion on voltage VPDO\_SRC is  $\pm 5\%$ . Additionally, specific rules apply to the disconnection thresholds (according to "USB Type-C cable and connector specification). Finally, user-defined derating factors can be adjusted to fit application specific requirements: MONITORING\_SHIFT\_LOW (MSL) and MONITORING\_SHIFT\_HIGH (MSH) (see default value in Section 5: Startup configuration).

Table 11 clarifies the low and high VBUS monitoring thresholds settings according to all these parameters.

**VBUS Voltage STATE** V<sub>TH\_LOW</sub> V<sub>TH\_HIGH</sub> (V<sub>RDO</sub>) = 5 V min(( V<sub>RDO</sub> x 1.05) x MSH; 5.9 V) **ATTACHED**  $V_{\mathsf{TH\ LOW-5V}}$ **ATTACHED** (V<sub>RDO</sub> x 0.95 - 1.25 V) x MSL > 5 V (non PPS RDO) min((V<sub>RDO</sub> x 1.05) x MSH; 23 V) **ATTACHED** > 5 V (V<sub>RDO</sub> x 0.95 - 0.85 V) x MSL (PPS RDO)

Table 11. VBUS monitoring low and high thresholds definition

Note:

STUSB4531 implements active VBUS monitoring during high and low voltage transitions, according to USB PD source transition behavior (as defined by the standard).

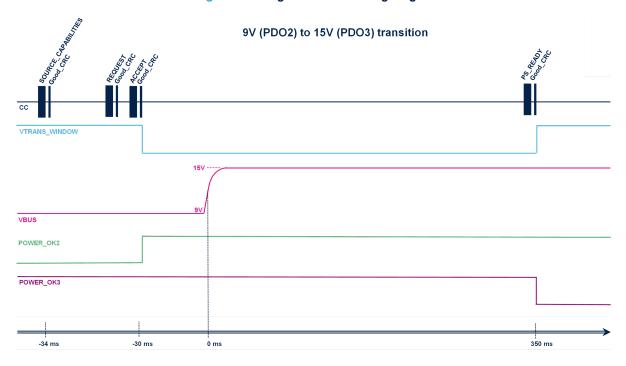

#### 3.6.3 VBUS discharge

The monitoring block also handles discharge connected to Type-C receptacle (VBUS\_VS\_DISCH pin) and on system side (DISCH pin).

The discharge paths are activated at the time that a disconnection is detected, during transition to a lower PDO voltage, when a hard reset is performed or when the device enters the error recovery state (see Section 3.7: Hardware fault management).

Although discharge times are preset by default (see Section 7.1: Electrical and timing characteristics), it can also be adjusted through NVM programming:

- At detachment, during error recovery state or hard reset, the discharge is activated for maximum DISCHARGE\_TIME\_TO\_0V time (665 ms by default)

- During transition to a lower PDO voltage, the discharge is activated for DISCHARGE\_TIME\_TRANS time maximum (350 ms by default).

DS15023 - Rev 1 page 16/50

## 3.7 Hardware fault management

During system operations, the STUSB4531 handles some preidentified hardware fault conditions. When such conditions happen, the circuit goes into ErrorRecovery.

The error recovery state is equivalent to forcing a detach event. When entering this state, the device de-asserts the VBUS power path by disabling VBUS\_EN\_SNK, HVO1, HVO2 and GPOD, and removing the terminations from the CC pins during 275 ms (as long as  $V_{VBUS_VS_DISCH} > V_{TH_LOW-5V}$ ). Then, it transitions to the unattached state.

The STUSB4531 goes into error recovery state when at least one condition listed below is met:

- Internal overtemperature (junction temperature exceeds maximum T<sub>J</sub>)

- Overvoltage detected on one CC pin (voltage on CC pins above V<sub>OVP</sub>)

- Overvoltage detected on VBUS

- After a hard reset, when power delivery communication with the source cannot be re-established despite

multiple tentatives.

### 3.8 Thermal shutdown

STUSB4531 thermal shutdown is set to 125 °C. In case the IC internal temperature is reaching such a high level, STUSB4531 goes to Error\_Recovery, and VBUS\_EN\_SINK is de-asserted.

To prevent such extreme conditions, a warning threshold is set to 105 °C (increasing internal temperature). If it is reached, interrupt is generated. For MCU based applications, it is recommended to take corrective action to reduce the temperature. A 15 °C hysteresis applies to resume operation (warning is released when the internal temperature decreases below 90 °C).

A new connection is not possible when the temperature is inside the warning window.

DS15023 - Rev 1 page 17/50

# 4 I<sup>2</sup>C Interface

# 4.1 Read and write operations

STUSB4531 implements a Fast-mode Plus I<sup>2</sup>C slave interface for high-speed Read/Write accesses (1 MHz). All data bytes are transmitted with the most significant bit first. It implements Automatic IDLE mode to save power.

The default I<sup>2</sup>C address is 0x28 or 0x29. Address selection is triggered at power-up by reading the ADD0 pin value. To guarantee proper initialization, the pin should be set as follows:

Table 12. Default I<sup>2</sup>C address

| I <sup>2</sup> C address | ADD0 connection     | Resistor value (R <sub>ADD0</sub> ) |

|--------------------------|---------------------|-------------------------------------|

| 0x28                     | Pull-down to GND    | 0 to 47 kOhms                       |

| 0x29                     | Pull-up to VREG_2V7 | 0 to 47 kOhms                       |

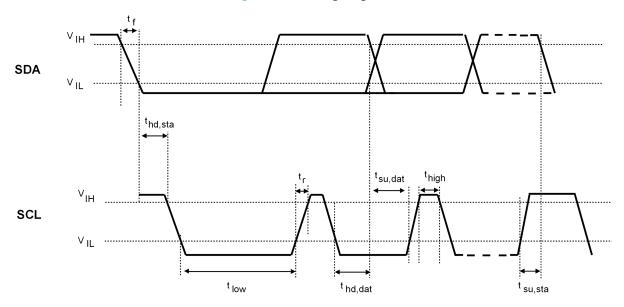

# 4.2 Timing specifications

Table 13. I<sup>2</sup>C timing for  $V_{I2C} = [1.7; 4.8 V]$

|                     |                                                                  | Fast m             | ode <sup>(1)</sup> | Fast mod           | le plus <sup>(1)</sup> |     |

|---------------------|------------------------------------------------------------------|--------------------|--------------------|--------------------|------------------------|-----|

| Symbol              | Parameter                                                        | Min <sup>(2)</sup> | Max                | Min <sup>(2)</sup> | Max.                   | Uni |

| F <sub>SCL</sub>    | SCL clock frequency                                              |                    | 400                | -                  | 1000                   | kHz |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                      | 1.3                | -                  | 0.50               | -                      |     |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                     | 0.6                | -                  | 0.26               | -                      |     |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition                             | 0.6                | -                  | 0.26               | -                      |     |

| t <sub>SU;STA</sub> | Setup time for repeated START condition                          | 0.6                | -                  | 0.26               | -                      |     |

| t <sub>su;sто</sub> | Set-up time for STOP condition                                   | 0.6                | -                  | 0.26               | -                      | μs  |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition START condition | 1.3                | -                  | 0.50               | -                      |     |

| t <sub>HD;DAT</sub> | Data hold time                                                   | 0                  | -                  | 0                  | -                      | _   |

| t <sub>SU;DAT</sub> | Data setup time                                                  | 100                | -                  | 50                 | -                      |     |

| t <sub>VD;DAT</sub> | Data valid time                                                  | -                  | 0.9                | -                  | 0.45                   | μs  |

| t <sub>VD;ACK</sub> | Data valid acknowledge time                                      | -                  | 0.9                | -                  | 0.45                   | μs  |

| tr                  | Rise time of both SDA and SCL signals                            | -                  | 300                | -                  | 120                    |     |

| tf                  | Fall time of both SDA and SCL signals                            | -                  | 300                | -                  | 120                    | ns  |

| Cb                  | Capacitive load for each bus line                                | -                  | 400                | -                  | 550                    | pF  |

<sup>1.</sup> ALL timings have been evaluated by characterization at [-40 °C; 105 °C]

DS15023 - Rev 1 page 18/50

<sup>2.</sup> MIN timings tested in production at  $T_{amb}$  = 25 °C

NB: Measurement points are done at V<sub>IL</sub>=0.3\*V<sub>I2C</sub> and V<sub>IH</sub>=0.7\*V<sub>I2C</sub>

DS15023 - Rev 1 page 19/50

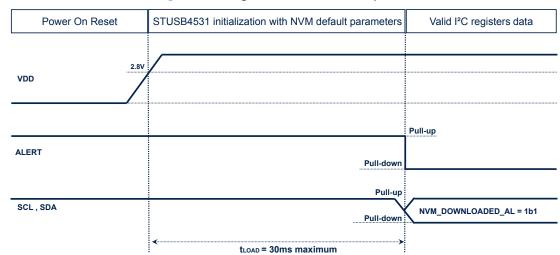

# 5 Startup configuration

## 5.1 User-defined parameters

The STUSB4531 provides a set of user-defined parameters that can be customized by NVM reprogramming through a dedicated I<sup>2</sup>C sequence. This feature allows users to change the default configuration of the IC to meet specific application requirements and to address various use cases or specific implementations.

NVM reprogramming overwrites the initial factory settings, defining a new default configuration that is loaded at each power-up. This default setting is copied at each power-up from the embedded NVM into the I<sup>2</sup>C registers. Only the values copied in the I<sup>2</sup>C registers are used by the STUSB4531 during system operation. Therefore, new settings defined during NVM reprogramming are not effective until the next power-off and power-up sequence.

The list of customizable parameters is described in the tables below.

**Table 14. PDO configuration**

| Parameter           | Description                       | Possible values                 | Values description                                                                  |

|---------------------|-----------------------------------|---------------------------------|-------------------------------------------------------------------------------------|

| DEVICE PDP          | Power delivery minimum power      | 8 bits                          | Contains the minimum power required by the Sink to operate at its functional modes. |

| DEVICE_PDP          | Power delivery minimum power      | (from 0 W to 100 W)             | Expressed in steps of 0.5 Watt (LSB ignored for PDP greater than 10 W)              |

|                     |                                   | 2b00: Fixed only                | Only fixed PDO is used                                                              |

|                     | Sink PDO type selection: define   | 2b01: Fixed +<br>VARIABLE       | Fixed PDOs + 1 variable PDO                                                         |

| SINK_FEATURE        | the mix of PDO used               | 2b10: Fixed + PPS               | Fixed PDOs + 1 Programmable power supply augmented PDO (PPS APDO)                   |

|                     |                                   | 2b11: Fixed +<br>VARIABLE + PPS | Fixed PDOs + 1 variable PDO + 1 PPS APDO                                            |

|                     |                                   | 2b00: 0                         | 1 Sink fixed PDO                                                                    |

| FIXED_PDO_NUMB      | Number of sink fixed PDO          | 2b01: 1                         | 1 Sink fixed PDO                                                                    |

| FIXED_FDO_NOMB      | Number of sink fixed PDO          | 2b10: 2                         | 2 Sink fixed PDO                                                                    |

|                     |                                   | 2b11: 3                         | 3 Sink fixed PDO                                                                    |

|                     | PDO1 current (5 V)                | 2b00: Default                   | Clamped to 500 mA                                                                   |

| VSAFE 5V CURRENT    |                                   | 2b01: 1.5 A                     | Clamped to 1.5 A                                                                    |

| VSAFE_SV_CORRENT    |                                   | 2b10: 3 A                       | Clamped to 3 A                                                                      |

|                     |                                   | 2b11: PDP/5                     | Clamped to 5 A                                                                      |

|                     |                                   | 2b00: VSEL_VAR                  | Custom voltage value                                                                |

| PDO2_VSEL           | Fixed sink PDO2 voltage           | 2b01: 9 V                       | Fixed 9 V                                                                           |

| FDO2_V3EL           | Tixed Slifk FDO2 Voltage          | 2b10: 15 V                      | Fixed 15 V                                                                          |

|                     |                                   | 2b11: 20 V                      | Fixed 20 V                                                                          |

| FIXED PDO2 CURRENT  | Fixed sink PDO2 current clamp     | 1b0: clamped to 3 A             | = PDP/FIXED_PDO2_VOLTAGE (3 A Max)                                                  |

| FIXED_PDO2_CORRENT  | Fixed Sink PDO2 current clamp     | 1b1: clamped to 5 A             | = PDP/FIXED_PDO2_VOLTAGE (5 A Max)                                                  |

|                     |                                   | 2b00: VSEL_VAR                  | Custom value                                                                        |

| PDO3_VSEL           | Fixed sink PDO3 voltage           | 2b01: 9 V                       | Fixed 9 V                                                                           |

|                     | Fixed sink PDO3 voltage           | 2b10: 15 V                      | Fixed 15 V                                                                          |

|                     |                                   | 2b11: 20 V                      | Fixed 20 V                                                                          |

| FIXED_PDO3_CURRENT  | Fixed sink PDO3 current clamp     | 1b0: clamped to 3 A             | = PDP/FIXED_PDO3_VOLTAGE (3 A Max)                                                  |

| I IVED_LDO2_COKKENI | I IVER 2111K LDO2 criticil ciquib | 1b1: clamped to 5 A             | = PDP/FIXED_PDO3_VOLTAGE (5 A Max)                                                  |

DS15023 - Rev 1 page 20/50

| Parameter             | Description                                                               | Possible values  | Values description                                         |

|-----------------------|---------------------------------------------------------------------------|------------------|------------------------------------------------------------|

| VSEL_VAR              | Custom voltage value for PDO2_VSEL or PDO3_VSEL and PPS_VOLTAGE_SELECTION | 10 bits          | Custom voltage value (by steps of 50 mV)                   |

| APDO_MAX_VOLTAGE      | VARIABLE and PPS maximum voltage field                                    | 8 bits           | in 100 mV steps                                            |

| APDO_MIN_VOLTAGE      | VARIABLE and PPS Minimum voltage field                                    | 8 bits           | in 100 mV steps                                            |

| APDO_MAX_CURRENT      | VARIABLE and PPS current field                                            | 7 bits           | in 50 mA steps                                             |

|                       |                                                                           | 2b00: DEVICE_PDP | DEVICE_PDP value                                           |

|                       | Sink maximum PDP in sink                                                  | 2b01: 16 W       | Expected source voltages: 5 V + 9 V                        |

| SINK_MAX_PDP          | capabilities extended message                                             | 2b10: 28 W       | Expected source voltages: 5 V + 9 V + 15 V + AVS           |

|                       |                                                                           | 2b11: 46 W       | Expected source voltages: 5 V + 9 V + 15 V + 20 V + AVS    |

|                       | Sink operating PDP in sink capabilities extended message                  | 2b00: DEVICE_PDP | DEVICE_PDP value                                           |

|                       |                                                                           | 2b01: 16 W       | Expected source voltages: 5 V + 9 V                        |

| SINK_OP_PDP           |                                                                           | 2b10: 28 W       | Expected source voltages: 5 V + 9 V + 15 V + AVS           |

|                       |                                                                           | 2b11: 46 W       | Expected source voltages: 5 V + 9 V + 15 V + 20 V + AVS    |

|                       | Sink minimum PDP in sink capabilities extended message                    | 2b00: DEVICE_PDP | DEVICE_PDP value                                           |

|                       |                                                                           | 2b01: 16 W       | Expected source voltages: 5 V + 9 V                        |

| SINK_MIN_PDP          |                                                                           | 2b10: 28 W       | Expected source voltages: 5 V + 9 V + 15 V + AVS           |

|                       |                                                                           | 2b11: 46 W       | Expected source voltages: 5 V + 9 V + 15 V + 20 V + AVS    |

|                       |                                                                           | 2b00: 0.95       | vSinkPD_Min threshold derated by -5%                       |

| MONITORING SHIET LOW  | VBUS monitoring: low-voltage                                              | 2b01: 0.90       | vSinkPD_Min threshold derated by -10%                      |

| MONITORING_SHIFT_LOW  | threshold derating factor                                                 | 2b10: 0.85       | vSinkPD_Min threshold derated by -15%                      |

|                       |                                                                           | 2b11: 1.00       | vSinkPD_Min                                                |

| MONITORING_SHIFT_HIGH |                                                                           | 2b00: 1.10       | V <sub>TH_HIGH</sub> set to V <sub>RDO</sub> x 1.05 x 1.10 |

|                       | VBUS monitoring: high-voltage                                             | 2b01: 1.15       | V <sub>TH_HIGH</sub> set to V <sub>RDO</sub> x 1.05 x 1.15 |

|                       | threshold derating factor                                                 | 2b10: 1.20       | V <sub>TH_HIGH</sub> set to V <sub>RDO</sub> x 1.05 x 1.20 |

|                       |                                                                           | 2b11: reserved   | Do not use                                                 |

DS15023 - Rev 1 page 21/50

Table 15. Autorun algorithm parameters and power path management

| Parameter             | Description                                                                                         | Possible values              | Values description                                                                                                                 |

|-----------------------|-----------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                       |                                                                                                     |                              | 5 V is supported by the application:                                                                                               |

|                       |                                                                                                     | 1b0: no                      | At USB Type-C attach, VBUS switch closes according to MISMATCH_5V condition                                                        |

| ABOVE_5V              | Controls VBUS path assertion at 5 V                                                                 |                              | 5 V is not supported by the application:                                                                                           |

|                       |                                                                                                     | 1b1: yes                     | At USB Type-C attach, VBUS switch does not close. In USB PD mode, VBUS_EN_SNK is not closed if 5 V is requested                    |

|                       |                                                                                                     | 1b0: Any current             | At USB Type-C connection, power path is closed whatever Type-C source current                                                      |

| MISMATCH_5V           | Defines current needed for closing the VBUS switch in 5 V operation (USB Type-C and PDO1), assuming |                              | At USB Type-C connection, power path is closed if Type-C source current is equal or greater than PDO1 sink current.                |

|                       | ABOVE_5V = 0                                                                                        | 1b1: Enough current          | During USB PD negotiation, power path is closed on PDO1 contract if PDO1 source current is equal or greater than PDO1 sink current |

|                       | Defines USB PD algorithm behavior when comparing source current to sink current                     | 1b0: Enough current          | SOURCE PDO is skipped if proposed current is lower than SINK requirements                                                          |

| MISMATCH_PD           |                                                                                                     | 1b1: Any current             | SOURCE PDO is selected whatever current capability                                                                                 |

|                       | Defines USB PD algorithm behavior when 0 mA PDO negotiated with SOURCE                              | 1b0: System operated         | No load condition is managed by the system                                                                                         |

| PDO_0mA_MISMATCH      |                                                                                                     | 1b1: Default                 | STUSB4531 manages no load condition (Suspend_Mode) by opening VBUS power path                                                      |

|                       | In case a PDO is selected, defines operating current field from RDO                                 | 1b0: SINK                    | Operating current = calculated through the algorithm                                                                               |

| OPERATING_CURRENT SEL |                                                                                                     |                              | Maximum current = Operating current                                                                                                |

| _022                  | operating current held from NDO                                                                     | 1b1: SOURCE                  | Operating current = SOURCE current                                                                                                 |

|                       |                                                                                                     | IDT. GOUNGE                  | Maximum current = SOURCE current                                                                                                   |

|                       |                                                                                                     | 1b0: High priority to fixed/ | Priority to FIXED/ VARIABLE PDO,                                                                                                   |

| PPS PRIORITY          | Defines the order in which the sink PDOs must be compared with the                                  | variable                     | then to PPS APDO                                                                                                                   |

| _                     | source PDOs                                                                                         | 1b1: High priority to PPS    | Priority to PPS APDO,                                                                                                              |

|                       |                                                                                                     | 5 , 1 , 5                    | then to FIXED/ VARIABLE PDO.                                                                                                       |

| PPS_VOLTAGE_SELECTION |                                                                                                     | 2b00: Min                    | APDO_MIN_VOLTAGE is used                                                                                                           |

|                       | PPS voltage value used by the algorithm                                                             | 2b01: Mid                    | Mean of APDO_MIN_VOLTAGE and APDO_MAX_VOLTAGE                                                                                      |

|                       |                                                                                                     | 2b10: Max                    | APDO_MAX_VOLTAGE is used                                                                                                           |

|                       |                                                                                                     | 2b11: VSEL_VAR               | VSEL_VAR is used                                                                                                                   |

DS15023 - Rev 1 page 22/50

Table 16. Application specific parameters

| Parameter         | Description                          | Possible values | Values description                                                                                                                    |

|-------------------|--------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| DATTERY PRESENT   |                                      | 1b0: No         | No battery in application                                                                                                             |

| BATTERY_PRESENT   | Application implements a battery     | 1b1: yes        | Battery in application                                                                                                                |

| DATTEDY OWAR      | Indicates if battery can be removed  | 1b0: No         | Fixed battery                                                                                                                         |

| BATTERY_SWAP      | or not                               | 1b1: Yes        | Swappable battery                                                                                                                     |

|                   |                                      | 1b0: No         | Sink is fully functional at vSafe5V.                                                                                                  |

| HIGHER_CAPABILITY | PDO1 higher capability bit           | 1b1: Yes        | In the case the Sink needs more than vSafe5V (e.g., 15 V) to provide full functionality, then the higher capability bit shall be set. |

|                   |                                      | 1b0: No         | No external power supply or power supply is not always able to sustain system functionality                                           |

| UNCONS_POWER      | Unconstrainted power                 | 1b1: Yes        | An external power supply is available and is sufficient to adequately power the system while charging external devices                |

| USB_COMM_CAPABLE  | USB2.0 or 3.x data capable           | 1b0: No         | Application does not support USB data communication                                                                                   |

| _ <b>_</b>        |                                      | 1b1: Yes        | Application implements USB data controller                                                                                            |

|                   |                                      | 1b0: No         | Single role only                                                                                                                      |

| DRD_CAPABLE       | Dual role data support               | IDO. NO         | (UFP - Peripheral)                                                                                                                    |

| DRD_CAPABLE       | Dual fole data support               | 1b1: Yes        | Dual role data capable                                                                                                                |

|                   |                                      | IDT. 163        | (UFP and DFP - Peripheral and host)                                                                                                   |

| DR_SWAP_2_UFP     | Data role swap to UFP support        | 1b0: Disabled   | Data role swap to UFP is rejected                                                                                                     |

| DK_OWAF_2_OFF     | Data fole swap to of 1 support       | 1b1: Enabled    | Data role swap to UFP can be accepted                                                                                                 |

| DR_SWAP_2_DFP     | Data role swap to DFP support        | 1b0: Disabled   | Data role swap to DFP is rejected                                                                                                     |

| DK_SWAF_Z_DI F    | Data fole swap to Diff Support       | 1b1: Enabled    | Data role swap to DFP can be accepted                                                                                                 |

| VDM_SUPPORT       | Indicated if vendor defined message  | 1b0: No         | Incoming VDM message requests are discarded                                                                                           |

|                   | is supported by the application      | 1b1: yes        | Incoming VDM message requests are supported                                                                                           |

| VBUS_CTRL_LOW_MA  | V <sub>TH LOW</sub> threshold bypass | 1b0: No         | V <sub>TH_LOW</sub> info is not masked to VBUS switch control                                                                         |

| SK                |                                      | 1b1: Yes        | V <sub>TH_LOW</sub> info is masked to VBUS switch control                                                                             |

|                   |                                      | 1b0: Disabled   | V <sub>CONN</sub> is disabled                                                                                                         |

| VCONN_EN          | V <sub>CONN</sub> supply ENABLE      | 1b1: Enabled    | V <sub>CONN</sub> is supplied (see Table 4: GPIO – conf 1)                                                                            |

|                   |                                      | 1b0: Disabled   | VCONN_SWAPP_2_ON is rejected                                                                                                          |

| VCONN_SWAPP_2_ON  | Support of VCONN SWAP to ON          | 1b1: Enabled    | VCONN_SWAPP_2_ON can be accepted                                                                                                      |

|                   |                                      | 1b0: Disabled   | VCONN_SWAPP_2_OFF is rejected                                                                                                         |

| VCONN_SWAPP_2_OFF | Support of VCONN SWAP to OFF         | 1b1: Enabled    | VCONN_SWAPP_2_OFF can be accepted                                                                                                     |

| GPIO_CONF         |                                      | 3b000: Conf 0   | Recommended for current transition management                                                                                         |

|                   |                                      | 3b001: Conf 1   | Recommended for external VCONN support                                                                                                |

|                   | GPIO pin selection                   | 3b010: Conf 2   | Recommended for POWER_OK support                                                                                                      |

|                   |                                      | 3b011: Conf 3   | Recommended for extended POWER_OK support                                                                                             |

|                   |                                      | 3b100: Conf 4   | Recommended for software controlled GPIO                                                                                              |

DS15023 - Rev 1 page 23/50

Startup configuration

| Parameter                | Description                                  | Possible values              | Values description                                           |

|--------------------------|----------------------------------------------|------------------------------|--------------------------------------------------------------|

| DISCHARGE_TIME_TO_<br>0V | Maximum VBUS discharge time to 0 V           | 5b10010: 665 ms<br>(default) | Discharge time (max.):<br>(DISCHARGE_TIME_TO_0V + 1) x 35 ms |

| DISCHARGE_TIME_TR ANS    | Maximum VBUS discharge time to lower voltage | 3b111: 350 ms<br>(default)   | Discharge time (max.): (DISCHARGE_TIME_TRANS + 3) x 35 ms    |

DS15023 - Rev 1 page 24/50

# **5.2** Factory settings

**Table 17. Power profiles**

| Parameter             | Description              |  |

|-----------------------|--------------------------|--|

| DEVICE_PDP            | 30 W                     |  |

| SINK_FEATURE          | Fixed PDO + VARIABLE PDO |  |

| SNK_PDO_NUMB          | 3                        |  |

| VSAFE_5V_CURRENT      | 3 A                      |  |

| FIXED_PDO2_VOLTAGE    | 9 V                      |  |

| FIXED_PDO2_CURRENT    | Clamped to 3 A           |  |

| FIXED_PDO3_VOLTAGE    | 15 V                     |  |

| FIXED_PDO3_CURRENT    | Clamped to 5 A           |  |

| VSEL_VAR              | 12 V                     |  |

| APDO_MIN_VOLTAGE      | 9 V                      |  |

| APDO_MAX_VOLTAGE      | 20 V                     |  |

| APDO_MAX_CURRENT      | 1.5 A                    |  |

| SINK_MAX_PDP          | Device PDP               |  |

| SINK_OP_PDP           | Device PDP               |  |

| SINK_MIN_PDP          | Device PDP               |  |

| MONITORING_SHIFT_LOW  | -5%                      |  |

| MONITORING_SHIFT_HIGH | +10%                     |  |

# Summary

- PDO1 FIXED 5 V; 3 A

- PDO2 FIXED 9 V; 3 A

- PDO3 FIXED 15 V; 2 A

- PDO4 VARIABLE [9 V 20 V; 1.5 A]

Table 18. Autorun algorithm

| Parameter             | Description                       |