**Datasheet**

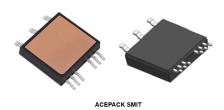

# 60 A 1200 V half-controlled bridge rectifier in ACEPACK SMIT module

# Product status Internal

| Product summary                          |        |  |  |  |  |

|------------------------------------------|--------|--|--|--|--|

| I <sub>T(RMS)</sub> ,I <sub>F(RMS)</sub> | 60 A   |  |  |  |  |

| I <sub>OUT(AV)</sub>                     | 75 A   |  |  |  |  |

| V <sub>DRM</sub> /V <sub>RRM</sub>       | 1200 V |  |  |  |  |

| V <sub>DSM</sub> /V <sub>RSM</sub>       | 1400 V |  |  |  |  |

| I <sub>GT</sub>                          | 50 mA  |  |  |  |  |

| T <sub>j</sub> max.                      | 150 °C |  |  |  |  |

#### **Features**

- 1200 V symmetrical blocking voltage

- High junction temperature: 150 °C

- High noise immunity, static dV/dt: 1000 V/µs

- Embed two TN6050HP-12 and two STBR6012 dies

- Module qualified according to AQG324 recommendation

- · SMD with isolated top cooled tab

- · Terminal pins opposite to cooling side

- Fully automatic PCB mounting to heat sink

- · Moisture Sensitivity Level: Level 3

- IPC/JEDEC J-STD-033

- 4000 V insulated tab-to-lead package

- UL recognized, File E81734

- Large creepage distance to meet IEC 60664-1

- 250 V<sub>AC</sub>, material group 2, pollution degree 3

- 600 V<sub>AC</sub>, material group 2, pollution degree 2

- Smaller footprint than four TO-247

- ECOPACK2 compliant component

#### **Applications**

- Single-phase controlled bridge rectifier

- On-board and stationary chargers

- · AC DC converter for motor drive, UPS and SMPS

- AC input converter current up to 85 A<sub>RMS</sub>

- Output full wave DC current up to 75 A<sub>AV</sub>

#### **Description**

The STTD6050H-12M2Y is a top cooled surface mount module that integrates a single-phase half-controlled bridge rectifier. It is rated at 1200 V and delivers an output full wave DC current up to 75  $A_{\mbox{\scriptsize AV}}$ . Each single embedded device has a rated current of 60  $A_{\mbox{\scriptsize RMS}}$  and a symmetric blocking voltage of 1200 V.

With its top cooling pad opposite to the printed circuit board this device allows the PCB-module-heat sink stack to be automatically assembled.

This provides a low profile and compact converter in the field of on-board charger, charging station, motor drive, UPS and AC-DC power supplies.

Based on the ST high temperature automotive planar technology, it offers higher specified noise immunity of 1000 V/ $\mu$ s up to the 150 °C junction temperature T $_j$ , and an over-voltage robustness V $_{DSM}$  up to 1400 V.

# 1 Characteristics

Table 1. Diode and SCR absolute maximum ratings (limiting values)

| Symbol                                    | Paramete                                                                                         | Value                   | Unit                              |             |                  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------|-------------|------------------|

| I <sub>T(RMS)</sub> , I <sub>F(RMS)</sub> | RMS on-state current, sine half wave                                                             | 60                      | Α                                 |             |                  |

| I <sub>T(AV)</sub> , I <sub>F(AV)</sub>   | Average on-state current, sine half wave                                                         |                         | T <sub>C_DIODE</sub> = 110 °C     | 38          | Α                |

| I <sub>OUT(AV)</sub>                      | Average output current, sine full wave                                                           |                         | T <sub>C(AV)</sub> = 106 °C       | 75          | Α                |

| 1 1                                       | Non repetitive surge peak on-state current,                                                      | $t_p = 8.3 \text{ ms}$  | T initial = 25 °C                 | 525         |                  |

| I <sub>TSM</sub> , I <sub>FSM</sub>       | $V_R = 0 \text{ V}, I_G = 100 \text{ mA}$                                                        | t <sub>p</sub> = 10 ms  | T <sub>j</sub> initial = 25 °C    | 500         | Α                |

| I <sup>2</sup> t                          | I <sup>2</sup> t value for fusing                                                                | t <sub>p</sub> = 10 ms  | T <sub>j</sub> = 25 °C            | 1250        | A <sup>2</sup> s |

| dl/dt                                     | Critical rate of rise of on-state SCR current $I_G = 2 \times I_{GT}$ , tr $\leq 100 \text{ ns}$ | T <sub>j</sub> = 150 °C | 200                               | A/µs        |                  |

| V <sub>DRM</sub> / V <sub>RRM</sub>       | Repetitive off-state voltage <sup>(1)</sup>                                                      |                         | T <sub>j</sub> = -40 °C to 150 °C | 1200        | V                |

| V <sub>DSM</sub> / V <sub>RSM</sub>       | Non repetitive surge peak off-state voltage <sup>(1)</sup>                                       | t <sub>p</sub> = 10 ms  | T <sub>j</sub> = 25 °C            | 1400        | V                |

| $V_{GM}$                                  | Peak forward SCR gate voltage                                                                    | t <sub>p</sub> = 20 μs  | T <sub>j</sub> = 150 °C           | 10          | V                |

| I <sub>GM</sub>                           | Peak forward SCR gate current                                                                    | t <sub>p</sub> = 20 μs  | T <sub>j</sub> = 150 °C           | 8           | Α                |

| $V_{RGM}$                                 | Peak SCR gate voltage                                                                            |                         | T <sub>j</sub> = 25 °C            | 5           | V                |

| $P_{G(AV)}$                               | Average SCR gate power dissipation                                                               | 1                       | W                                 |             |                  |

| T <sub>stg</sub>                          | Storage junction temperature range                                                               | -40 to +150             | °C                                |             |                  |

| T <sub>j</sub>                            | Operating junction temperature range                                                             |                         |                                   | -40 to +150 | °C               |

| V <sub>INS</sub>                          | RMS tab-to-leads insulation voltage, 1 minu                                                      | ite, f = 50 - 60        | 0 Hz                              | 4           | kV               |

<sup>1.</sup>  $V_{DRM}$  and  $V_{DSM}$  apply to SCR only.

Table 2. SCR electrical characteristics, per single SCR

| Symbol            | Test Cond                                                                       | litions <sup>(1)</sup>  |      | Value | Unit |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------|-------------------------|------|-------|------|--|--|--|--|--|

| SCR triggering ch | SCR triggering characteristics                                                  |                         |      |       |      |  |  |  |  |  |

| I <sub>GT</sub>   | V <sub>D</sub> = 12 V, R <sub>I</sub> = 33 Ω                                    | T <sub>i</sub> = 25 °C  | Min. | 10    | mA   |  |  |  |  |  |

| iGI               | VD = 12 V, NL = 55 12                                                           | 1, - 25 0               | Max. | 50    | IIIA |  |  |  |  |  |

| V <sub>GT</sub>   | $V_D = 12 \text{ V}, R_L = 33 \Omega$                                           | T <sub>j</sub> = 25 °C  | Max. | 1.3   | V    |  |  |  |  |  |

| $V_{GD}$          | $V_D = 2/3 V_{DRM}, R_L = 3.3 k\Omega$                                          | T <sub>j</sub> = 150 °C | Min. | 0.2   | V    |  |  |  |  |  |

| I <sub>H</sub>    | I <sub>T</sub> = 500 mA, gate open                                              | T <sub>j</sub> = 25 °C  | Max. | 100   | mA   |  |  |  |  |  |

| IL                | I <sub>G</sub> = 1.2 x I <sub>GT</sub>                                          | T <sub>j</sub> = 25 °C  | Max. | 125   | mA   |  |  |  |  |  |

| SCR dynamic cha   | racteristics                                                                    | '                       | '    |       |      |  |  |  |  |  |

| <b>+</b>          | $I_T = 60 \text{ A}$ , $V_D = 800 \text{ V}$ , $I_G = 100 \text{ mA}$ ,         | T. = 25 °C              | Tun  | 1     |      |  |  |  |  |  |

| t <sub>GT</sub>   | $dI_G/dt = 0.2 A/\mu s$                                                         | T <sub>j</sub> = 25 °C  | Тур. | '     | μs   |  |  |  |  |  |

|                   | $I_T = 38 \text{ A}, V_D = 800 \text{ V}, dI_T/dt = 10 \text{ A/}\mu\text{s},$  | T = 450 °C              | T    | 450   |      |  |  |  |  |  |

| t <sub>Q</sub>    | $V_R = 75 \text{ V}, dV_D/dt = 20 \text{ V/}\mu\text{s}, t_p = 100 \mu\text{s}$ | T <sub>j</sub> = 150 °C | Тур. | 150   | μs   |  |  |  |  |  |

| dV/dt             | V <sub>D</sub> = 800 V, gate open                                               | T <sub>j</sub> = 150 °C | Min. | 1000  | V/µs |  |  |  |  |  |

DS13702 - Rev 2 page 2/18

| Symbol                               | Test Co                                                 | Test Conditions <sup>(1)</sup> |      |      |    |  |  |  |  |  |  |

|--------------------------------------|---------------------------------------------------------|--------------------------------|------|------|----|--|--|--|--|--|--|

| SCR static characteristics           |                                                         |                                |      |      |    |  |  |  |  |  |  |

| V                                    | I <sub>TM</sub> = 60 A, t <sub>P</sub> = 380 μs         | T <sub>j</sub> = 25 °C         | Max. | 1.3  | V  |  |  |  |  |  |  |

| V <sub>TM</sub>                      | 1 <sub>TM</sub> - 00 A, tp - 300 μs                     | T <sub>j</sub> = 150 °C        | Max. | 1.3  | V  |  |  |  |  |  |  |

| V <sub>TOT</sub>                     | SCR on-state threshold voltage                          | T <sub>j</sub> = 150 °C        | Max. | 0.8  | V  |  |  |  |  |  |  |

| R <sub>DT</sub>                      | SCR on-state dynamic resistance                         | T <sub>j</sub> = 150 °C        | Max. | 7.45 | mΩ |  |  |  |  |  |  |

| I <sub>DRMT</sub> /I <sub>RRMT</sub> | $V_D = V_{DRM}, V_R = V_{RRM}$                          | T <sub>j</sub> = 25 °C         | Max. | 5    | μA |  |  |  |  |  |  |

| 'DRMT' 'RRMT                         | VD - VDRM, VR - VRRM                                    | T <sub>j</sub> = 150 °C        | Max. | 7.5  | mA |  |  |  |  |  |  |

| I <sub>DSMT</sub> /I <sub>RSMT</sub> | $V_D = V_{DSM}, V_R = V_{RSM}$                          | Max.                           | 10   | μA   |    |  |  |  |  |  |  |

| SCR losses evaluat                   | ion                                                     | ·                              | '    |      |    |  |  |  |  |  |  |

| P <sub>LT</sub>                      | $V_{TOT} \times I_{T(AV)} + R_{DT} \times I_{T(RMS)}^2$ |                                |      |      | W  |  |  |  |  |  |  |

<sup>1.</sup> Refer to application note AN4608 for parameter definition

Table 3. Diode Electrical Characteristics, per single diode

| Symbol                  | Test Conditions Val                                                |                                           |      |      |    |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------|-------------------------------------------|------|------|----|--|--|--|--|--|

| Diode static characte   | Diode static characteristics                                       |                                           |      |      |    |  |  |  |  |  |

| VF                      | $I_{\rm F}$ = 60 A, $t_{\rm P}$ = 380 µs, duty cycle $\delta$ < 2% | T <sub>j</sub> = 25 °C                    | Max. | 1.3  | V  |  |  |  |  |  |

| VF                      | 1F - 00 A, tp - 300 μs, duty cycle 0 < 2%                          | T <sub>j</sub> = 150 °C                   | Max. | 1.2  | V  |  |  |  |  |  |

| V <sub>TOD</sub>        | On-state rectifier threshold                                       | T <sub>j</sub> = 150 °C                   | Max. | 0.96 | V  |  |  |  |  |  |

| R <sub>DD</sub>         | On-state rectifier dynamic resistance                              | T <sub>j</sub> = 150 °C                   | Max. | 4    | mΩ |  |  |  |  |  |

|                         | V = V                                                              | T <sub>j</sub> = 25 °C                    | Max. | 5    |    |  |  |  |  |  |

| IRRMD                   | $V_R = V_{RRM}$ , $t_p = 5$ ms, duty cycle $\delta < 2\%$          | T <sub>j</sub> = 150 °C                   | Max. | 250  | μA |  |  |  |  |  |

| I <sub>RSMD</sub>       | $V_R = V_{RSM}$                                                    | $V_R = V_{RSM}$ $T_j = 25 ^{\circ}C$ Max. |      |      |    |  |  |  |  |  |

| Diode losses evaluation |                                                                    |                                           |      |      |    |  |  |  |  |  |

| P <sub>LD</sub>         | $V_{TOD} \times I_{T(AV)} + R_{DD} \times I_{T(RMS)}^2$            |                                           |      |      | W  |  |  |  |  |  |

**Table 4. Thermal characteristics**

| Symbol                 | Parameter                                     | Value | Unit |

|------------------------|-----------------------------------------------|-------|------|

| R <sub>th(j-c)</sub> T | Junction to case (DC), per SCR <sup>(1)</sup> | 0.75  | °C/W |

| R <sub>th(j-c) D</sub> | Junction to case (DC), per diode (1)          | 0.75  | °C/W |

<sup>1.</sup> The case temperature is measured right underneath the device die on cooling pad

For more information, please refer to the following application note related to the thermal management:

AN5384: ACEPACK SMIT module package guidelines for mounting and thermal management

DS13702 - Rev 2 page 3/18

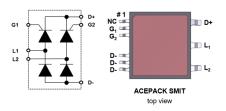

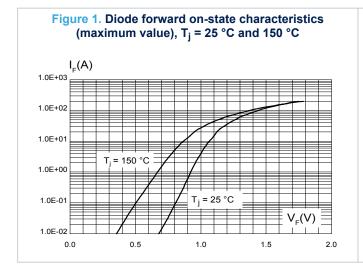

# 1.1 Characteristics (curves)

Figure 2. SCR on-state characteristics (maximum values), T<sub>i</sub> = 25 °C and 150 °C  $I_{TM}(A)$ 1000  $T_{j}$  max: V = 0.8 V  $R_{D}^{TO} = 7.45 m\Omega$ T<sub>i</sub> = 150 °C 100 10 = 25 °C  $V_{TM}(V)$ 0 0.5 1.5 2 2.5 3.5 4

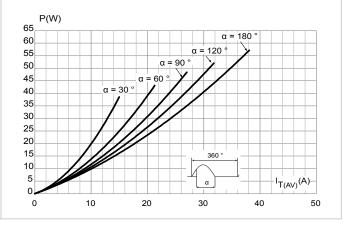

Figure 3. Diode maximum average power dissipation versus average half-wave on-state current, a = 30  $^{\circ}$  to 180  $^{\circ}$

Figure 4. SCR maximum average power dissipation versus average half-wave on-state current, a = 30 ° to 180 °

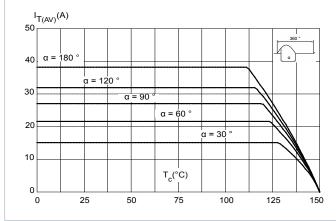

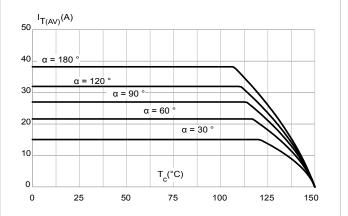

Figure 5. Diode average on-state current versus case temperature

Figure 6. SCR average on-state current versus case temperature

DS13702 - Rev 2 page 4/18

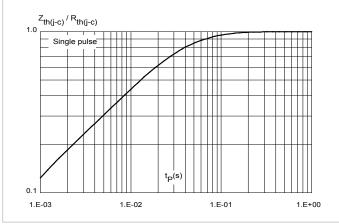

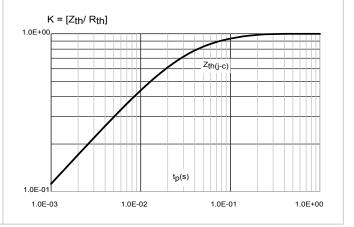

Figure 7. Diode relative variation of thermal impedance junction to case versus pulse duration, 1 ms to 1 s

Figure 8. SCR relative variation of thermal impedance junction to case versus pulse duration, 1 ms to 1 s

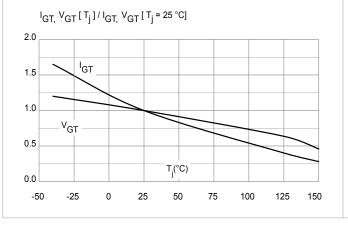

Figure 9. SCR relative variation of gate trigger current and gate trigger voltage versus junction temperature (typical values)

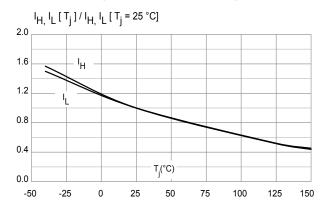

Figure 10. SCR relative variation of holding and latching current versus junction temperature (typical values)

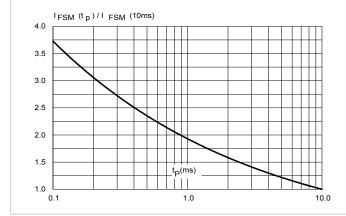

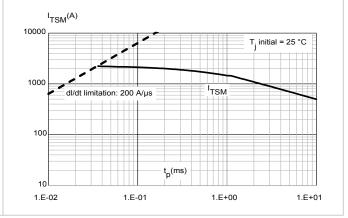

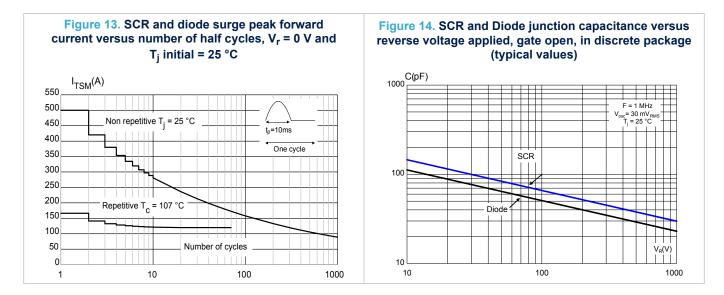

Figure 11. Diode non repetitive surge peak on-state current for a sinusoidal pulse ( $t_p < 10 \text{ ms}$ ),  $V_r = 0 \text{ V}$

Figure 12. SCR non repetitive surge peak on-state current for a sinusoidal pulse ( $t_p < 10 \text{ ms}$ ) ,  $V_r = 0 \text{ V}$

DS13702 - Rev 2 page 5/18

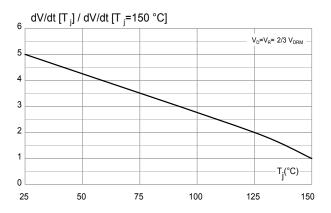

Figure 15. SCR relative variation of the static dV/dt immunity versus junction temperature (typical values)

DS13702 - Rev 2 page 6/18

# 2 Application

### 2.1 Solid state Inrush current limitation topologies using STTD6050H-12M2Y

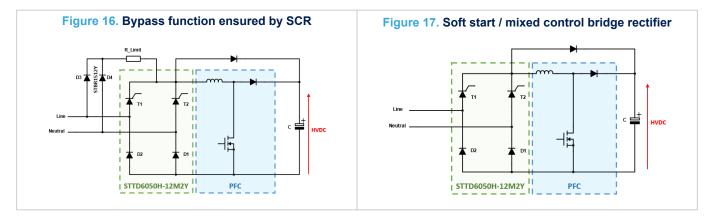

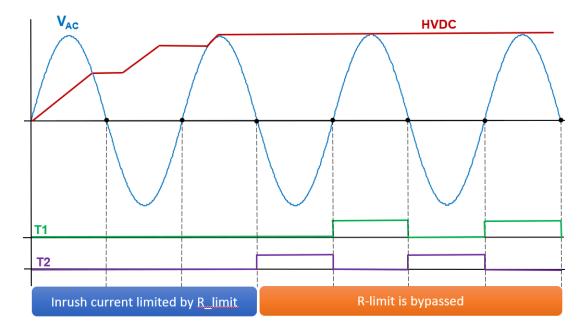

As illustrated here below, bypass and mixed bridge rectifiers are two topologies dedicated to the AC line voltage rectification which include the solid-state inrush current limitation feature.

In the bypass topology, at system start-up both T1 and T2 SCRs are OFF. The output bulk capacitor is then charged through the D3, D4, D2, D1 diodes and the current is limited by the R\_limit resistor placed in the current path.

At steady state, R\_limit power losses are cut by switching ON alternatively the T1 and T2 SCRs according to line polarity which are then bypassing R limit.

Figure 18. Bypass topology waveform working principle

DS13702 - Rev 2 page 7/18

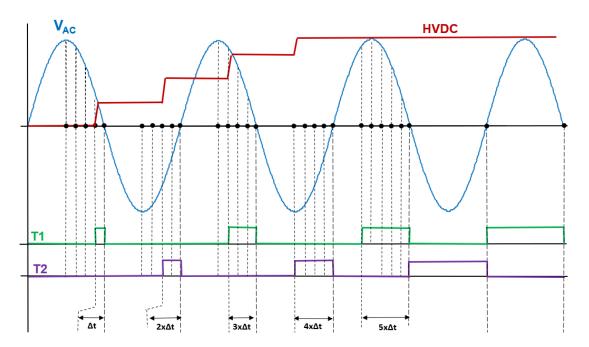

In the mixed bridge topology, SCRs are controlled in phase angle to smoothly increase the PFC output capacitor voltage up to peak AC line voltage. The pre-charging peak current value is controlled by a microcontroller which smartly synchronizes the SCRs gate driving signal angle step (referred as  $\Delta t$  in the figure here below). Limiting resistor is no more needed.

Figure 19. Mixed bridge phase angle principle

For more information, refer to the application note:

AN4606: Inrush-current limiter circuits (ICL) with Triacs and Thyristors (SCR) and controlled bridge design tips.

Those two robust solid-state topologies allow the applications to easily comply to the following standards:

- 1. IEC61000-3-3 (voltage fluctuations and flicker in public low-voltage supply systems, for equipment with rated current ≤ 16 A). the high current powered from the grid may lead to voltage fluctuations and drops due to the line impedance. Those mains voltage disturbances have an impact on any other equipment connected to the same circuit and cause undesired brightness variation of lamps or displays (commonly called flickering phenomenon).

- 2. IEC61000-4-11 (voltage dips, short interruptions, and voltage variations immunity tests) As any appliance connected to the mains can be subject to line voltage dips or interruptions, a high input current may occur when the line voltage suddenly comes back to its nominal value. This high current may damage the front-end circuit components and can trigger an AC fuse for example.

DS13702 - Rev 2 page 8/18

# Prerelease product(s)

## 2.2 Dissipated power and junction temperature calculation at steady state

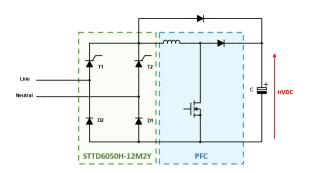

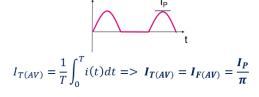

In below example, STTD6050H-12M2Y is placed upstream from PFC stage.  $I_T$  and  $I_F$  define respectively SCR and diode current value. Therefore, the current taken from the line and flowing through the mixed bridge is a sinus waveform.

Figure 20. Soft start / mixed control bridge rectifier

Figure 21. SCR / diode current waveform (sinusoidal half wave)

$$I_{T(RMS)}^2 = \frac{1}{T} \int_0^T i^2(t) dt = > I_{T(RMS)}^2 = I_{F(RMS)}^2 = \frac{I_{P}^2}{4}$$

#### 2.2.1 Dissipated power into SCRs and diodes

Dissipated power into SCRs and diodes is defined by the following equation:

$$P_d = V_{TOX} \times I_{T(AV)} + R_{DX} \times I_{T(RMS)}^2$$

(1)

Note:  $V_{TOX}$  and  $R_{DX}$  are given in Eq. (1) and Eq. (4) where X = T for the SCR and F for the diode.

$$I_{T(AV)} = \frac{I_P}{\pi}; I_P = I_{Line(RMS)} \times \sqrt{2} = > I_{T(AV)} = \frac{\sqrt{2}}{\pi} \times I_{L(RMS)}$$

(2)

$$I_{T(RMS)}^{2} = \frac{I_{P}^{2}}{4} = \frac{I_{L(RMS)}^{2}}{2} \tag{3}$$

Using equations (1), (2) and (3), dissipated power can directly be calculated from AC line RMS current value  $I_{L(RMS)}$  for a single SCR or diode in the mixed bridge:

$$P_{d} = \frac{V_{T0X} \cdot \sqrt{2}}{\pi} \times I_{L(RMS)} + \frac{R_{DX}}{2} \times I_{L(RMS)}^{2}$$

(4)

DS13702 - Rev 2 page 9/18

#### 2.2.2 Junction temperature calculation

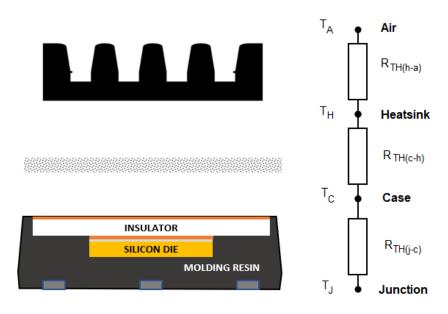

Figure 22. Die assembly representation

When Tc value is known, silicon junction temperature can be calculated as follows:

$$T_j = T_C + P_D \times R_{TH(j-c)}$$

Otherwise, starting from ambient temperature measurement, junction temperature can be calculated as follows:

$$T_j = T_A + P_D \times R_{TH}(j - a)$$

Note:  $R_{th(j-c)}$  and  $R_{th(j-a)}$  values are given in the datasheet.

with:

$$R_{TH(j-a)} = R_{TH(j-c)} + R_{TH(c-h)} + R_{TH(h-a)}$$

and where  $R_{TH(c-h)}$  is the thermal interface resistance (grease or foil) and  $R_{TH(h-a)}$  is the heatsink thermal resistance.

For more information about the thermal management and power dissipation calculation, refer to the application note:

- AN533: SCRs, TRIACs, and AC switches, thermal management precautions for handling and mounting

- AN604: Calculation of conduction losses in a power rectifier

- AN4021 : Calculation of reverse losses in a power diode

DS13702 - Rev 2 page 10/18

# 3 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

## 3.1 ACEPACK SMIT package information

- · Lead-free package leads finishing

- Halogen-free molding compound resin meets UL94 standard level V0

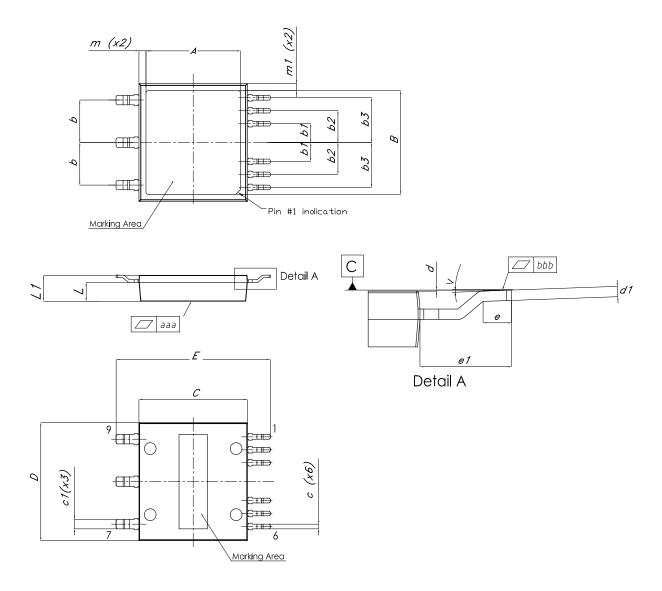

Figure 23. ACEPACK SMIT package outline

DM00447519\_Rev.5

DS13702 - Rev 2 page 11/18

m1

٧

aaa

bbb

1.30

0°

0.01

0.00

1.50

2°

Inches (for reference only) mm Dim. Max. Min. Тур. Max. Min. Тур. Α 19.50 20.00 20.50 0.7677 0.7874 0.8071 В 21.50 22.00 22.50 0.8465 0.8661 0.8858 0.9134 С 22.80 23.00 23.20 0.8976 0.9055 D 24.80 25.00 25.20 0.9764 0.9843 0.9921 Ε 32.20 32.70 1.2874 1.3071 33.20 1.2677 b 9.00 0.3543 b1 4.00 0.1575 b2 6.75 0.2657 b3 9.50 0.3740 0.95 1.00 1.10 0.0374 0.0394 0.0433 С 1.95 2.00 2.10 0.0768 0.0787 0.0827 c1 0.0059 d 0.00 0.15 0.0000 0.0000 d1 0.45 0.55 0.65 0.0177 0.0217 0.0256 0.0512 1.30 1.50 0.0591 0.0669 1.70 е 4.65 0.1831 0.1909 0.1988 e1 4.85 5.05 L 3.95 4.00 4.05 0.1555 0.1575 0.1594 L1 5.40 5.50 5.60 0.2126 0.2165 0.2205 0.0512 0.0591 0.0709 1.30 1.50 1.80 m

Table 5. ACEPACK SMIT package mechanical data

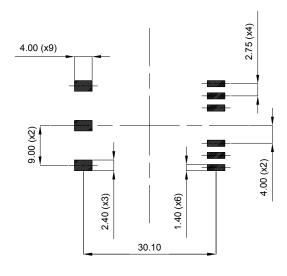

Figure 24. ACEPACK SMIT recommended footprint (dimensions are in mm)

0.0512

0°

1.80

4°

0.05

0.10

DM00447519\_FP\_Rev.5

0.0591

2°

0.0004

0.0000

0.0709

4°

0.0020

0.0039

Note: Recommended pressing force on package to the heatsink: 50 N as described in application note AN5384.

DS13702 - Rev 2 page 12/18

# 3.2 ACEPACK SMIT package insulation information

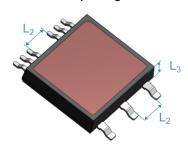

Figure 25. ACEPACK SMIT package insulation information

Table 6. ACEPACK SMIT package insulation characteristics

| Symbol           |                                        | Value                                        | Unit |     |    |

|------------------|----------------------------------------|----------------------------------------------|------|-----|----|

| L2               | Pin-to-pin creepage distance           | Terminal to terminal: 3 to 4, 7 to 8, 8 to 9 | Min. | 6.6 | mm |

| L3               | Pin-to-backside creepage distance      |                                              | Min. | 4   | mm |

| I <sub>INS</sub> | RMS tab-to-pin lead insulation current | Duration = 1 s., V <sub>INS</sub> = 4.8 kV   | Max. | 1   | mA |

Note: Recommended pressing force on package to the heatsink: 50 N as described in application note AN5384.

DS13702 - Rev 2 page 13/18

# Prerelease product(s)

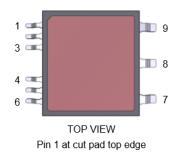

# 3.3 ACEPACK SMIT terminal description

Table 7. ACEPACK SMIT STTD6050H-12M2Y module pinout description

| Pin # | Name | Description   |

|-------|------|---------------|

| 1     | NC   | Not connected |

| 2     | G1   | Gate SCR1     |

| 3     | G2   | Gate SCR2     |

| 4     | D-   | Output minus  |

| 5     | D-   | Output minus  |

| 6     | D-   | Output minus  |

| 7     | L2   | AC line 2     |

| 8     | L1   | AC line 1     |

| 9     | D+   | Output plus   |

Figure 26. ACEPACK SMIT STTD6050H-12M2Y module pinout

DS13702 - Rev 2 page 14/18

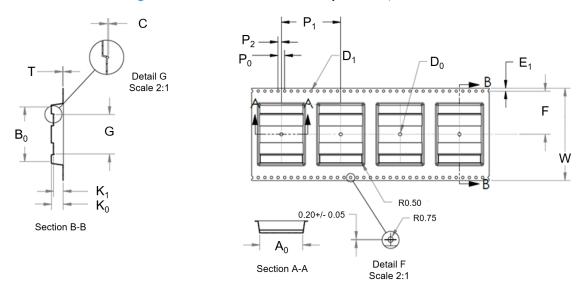

# 3.4 ACEPACK SMIT packing information

Figure 27. ACEPACK SMIT carrier tape outline, bottom view

**Table 8. ACEPACK SMIT carrier tape dimensions**

|                | Carrier tape typical dimension (mm) |      |                |                |                |       |       |                |                |                |                |                |      |       |

|----------------|-------------------------------------|------|----------------|----------------|----------------|-------|-------|----------------|----------------|----------------|----------------|----------------|------|-------|

| A <sub>0</sub> | B <sub>0</sub>                      | С    | D <sub>0</sub> | D <sub>1</sub> | E <sub>1</sub> | F     | G     | K <sub>0</sub> | K <sub>1</sub> | P <sub>0</sub> | P <sub>1</sub> | P <sub>2</sub> | Т    | W     |

| 26.00          | 33.30                               | 0.40 | 2.00           | 1.50           | 1.75           | 26.20 | 24.10 | 7.10           | 5.80           | 4.00           | 36.00          | 2.00           | 0.35 | 56.00 |

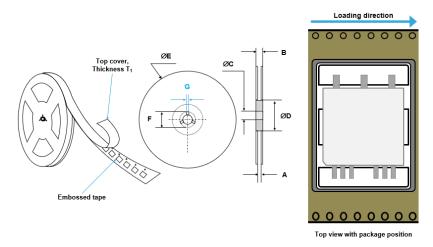

Figure 28. ACEPACK SMIT reel outline

Table 9. ACEPACK SMIT reel dimensions

| Door atr  |           | Reel dimension (mm) |           |            |          |          |          |                       |  |  |

|-----------|-----------|---------------------|-----------|------------|----------|----------|----------|-----------------------|--|--|

| Base qty. | A         | B (max.)            | С         | D (min.)   | E (max.) | F (min.) | G        | T <sub>1</sub> (max.) |  |  |

| 200       | 16.4 ±0.3 | 22.4                | 13.2 ±0.2 | 20.2 ±0.25 | 330      | 20.2     | 2.0 ±0.5 | 0.1                   |  |  |

DS13702 - Rev 2 page 15/18

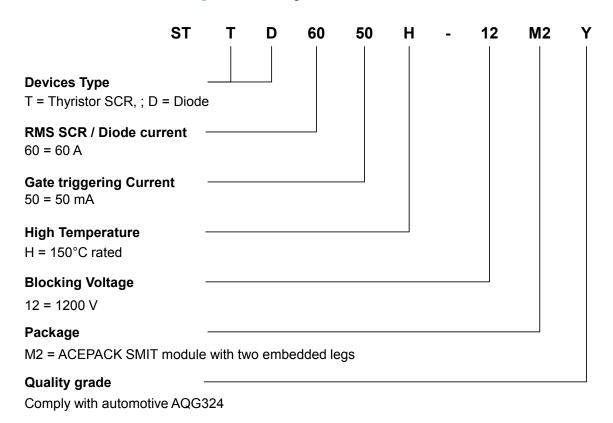

# 4 Ordering information

Figure 29. Ordering information scheme

Table 10. Ordering information

| Order code      | Marking        | Package      | Weight | Base qty. | Delivery mode |

|-----------------|----------------|--------------|--------|-----------|---------------|

| STTD6050H-12M2Y | STTD6050H12M2Y | ACEPACK SMIT | 8.1 g  | 200       | Tape and reel |

DS13702 - Rev 2 page 16/18

# **Revision history**

Table 11. Document revision history

| Date        | Version | Changes                                                      |

|-------------|---------|--------------------------------------------------------------|

| 14-Apr-2021 | 1       | Initial release.                                             |

| 22-Apr-2021 | 2       | Confidentiality level changed from ST Resctricted to public. |

DS13702 - Rev 2 page 17/18

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DS13702 - Rev 2 page 18/18