# 75 V high-current full-bridge advanced motor driver series

#### **Features**

- Supply voltage from 7 V to 75 V

- Embedded power MOSFETs with current ratings: 6  $A_{rms}$ ,  $R_{DS(ON)}$  = 27  $m\Omega$  typ

- Current sensing amplifier

- Current limiter implementing PWM trimming or fixed OFF time control

- Adjustable slew rate for improved EMI/efficiency trade-off

- Full set of protections: overtemperature, overcurrent and UVLO

- Open-load detection

#### **Applications**

- Stage lighting

- Factory automation

- ATM and money handling machines

- Textile machines

- Home appliances

- Robotics

#### **Description**

the model), the BOM space saving comparing to discrete solutions is significant. The supply voltage is wide, ranging from 7 to 75 V. The series offers a set of pin-to-

The STSPIN9P series is an extremely flexible platform that supports a wide range of

pin compatible half-bridge and full-bridge topologies, enabling coverage of a broad variety of applications.

The STSPIN9P2 sub-series includes pin-to-pin compatible full-bridge devices. Components in the STSPIN9P2 series differ in driving mode, and control features to enable the adoption of a tailored solution for each specific application.

Despite their topological simplicity, the devices integrate a wide set of functional blocks and advanced features.

All versions integrate regulators making the device fully self-supplied. A charge pump allows unlimited high-side on time.

The integrated AFE, composed of a differential amplifier and a comparator, is designed to amplify the signal from a shunt resistor and compare it to a reference.

In case of versions with integrated current limiter, the comparator output is used to implement a fixed off time or a PWM trimming control strategy, otherwise it is only available for the application on the COUT open-drain output.

All devices in the STSPIN9P series feature the adjustable slew rate, enabling optimization of the EMI/efficiency trade-off. This capability improves overall performance and accelerates customer design qualification.

The devices are also fully protected thanks to UVLO (overcurrent protection and thermal shutdown). Additionally, open-load detection verifies proper motor connection when the power stage is disabled, providing dedicated signaling on the nOL output. The STSPIN9P2 products come in a compact 7x9 QFN package.

| Product status link |

|---------------------|

| STSPIN9P21          |

| STSPIN9P22          |

| STSPIN9P23          |

| STSPIN9P24          |

# Product label

# 1 Overview

The STSPIN9P2 platform targets high-current motor-driving solutions with particular focus on brushed-DC motor. The family encompasses several systems-in-package composed of one control die and four MOSFET dies implementing a full-bridge topology.

Products differentiate according to features provided by the control die as listed in Table 1.

Table 1. Full-bridge ordering codes

| Order code | R <sub>DSON</sub> (mΩ) | I <sub>RMS</sub> (A) | Input logic | Curr. limiter |

|------------|------------------------|----------------------|-------------|---------------|

| STSPIN9P21 | 27                     | 6                    | INx, ENx    | Yes           |

| STSPIN9P22 | 27                     | 6                    | INx, ENx    | No            |

| STSPIN9P23 | 27                     | 6                    | PWM, PH     | Yes           |

| STSPIN9P24 | 27                     | 6                    | PWM, PH     | No            |

DS15030 - Rev 1 page 2/33

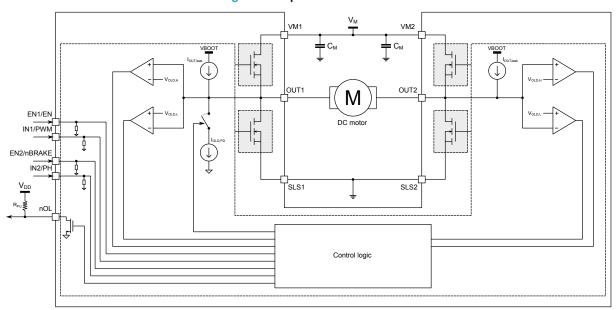

# 2 Block diagrams

Тј 3.3 V Reg. Tj Tj,reg nSTBY OUT1 Open-load and OCD ģ EN1/EN IN1/PWM Тј EN2/nBRAKE IN2/PH Control SR logic Tj TOFF Open-load and OCD Tj LSS2

SNSP

Figure 1. STSPIN9P21 / STSPIN9P23 full-bridge with current limiter

DS15030 - Rev 1 page 3/33

SNSO

Тј 3.3 V Reg. Tj Tj,reg 14 V Reg. nSTBY Open-load and OCD OUT1 Ŷ EN1/EN IN1/PWM Тј M IN2/PH DC motor nΟl LSS1 nFAULT Control logic Tj,HS2 Tj GND Open-load and OCD OUT2 Тј V<sub>DD</sub> LSS2 SNSO SNSP SNSN R<sub>SHUNT</sub>

Figure 2. STSPIN9P22 / STSPIN9P24 full-bridge with uncommitted AFE

DS15030 - Rev 1 page 4/33

# 3 Pin description

24 ENZ\_nBRAKE 99 IN1\_PWM 54 EN1\_EN 6ND ₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹₹< CP1 40 000 000 0 00000000 VM 39 VM 2 VM VM VM 37 VM EPAD4 EPAD1 VM 4 36 VM 5 VM  $\supset$ VM 35 VM 6 34 VM EPAD3 OUT1 OUT2 33 OUT2 OUT1 OUT1 OUT2 9 OUT1 10 EPAD2 EPAD5 30 OUT2 LSS1 11 29 LSS2 LSS1 12 LSS2 00000000 0.0 TOFF\_COUT 65 nFAULT 12 21 22 23 24 SNSN S SNSO S 25 2100 13 14 15 26 27 OUT1 LSS2 LSS2 LSS1 LSS1

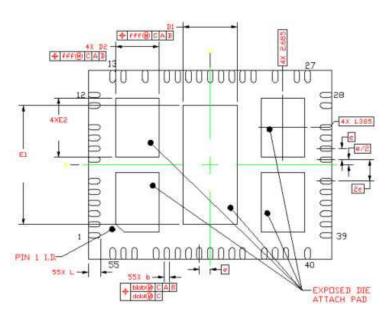

Figure 3. STSPIN9P2 full-bridge - pinout

Table 2. STSPIN9P2 full-bridge - pin assignment

| Pin n.                                                                 |      | STSPIN9P23<br>STSPIN9P24 | Туре                                                       | Function                                                                 |

|------------------------------------------------------------------------|------|--------------------------|------------------------------------------------------------|--------------------------------------------------------------------------|

| 1, 2, 3, 4, 5, 6, 34, 35, 36, 37, 38, 39, 43, 53, 54, 55, EPAD1, EPAD4 | V    | VM                       |                                                            | Main supply voltage (HS MOSFET drain)                                    |

| 7, 8, 9, 10, 15, EPAD2                                                 | OL   | OUT1                     |                                                            | Half-bridge A output (LS MOSFET drain, HS MOSFET source)                 |

| 11, 12, 13, 14                                                         | LSS1 |                          | LSS1 Analog out Half-bridge A reference (LS MOSFET source) |                                                                          |

| 16                                                                     | REG  | 33V3                     | Supply                                                     | 3.3 V regulator output                                                   |

| 17                                                                     | nFA  | ULT                      | Open-drain output                                          | Fault open drain output                                                  |

| 18                                                                     | nC   | DL                       | Open-drain output                                          | Open load detection drain output                                         |

| 19                                                                     | CO   | UT                       | Open-drain output                                          | Comparator open-drain output                                             |

| 19                                                                     | TO   | FF                       | Analog input                                               | Current limiter off-time setting. Short to ground for PWM trimming mode. |

| 20, 44, 50, EPAD3                                                      | GND  |                          | Ground                                                     | Ground                                                                   |

| 21                                                                     | VR   | EF                       | Analog input                                               | Current limiter reference/Comparator inverting input                     |

DS15030 - Rev 1 page 5/33

| Pin n.              | STSPIN9P21<br>STSPIN9P22 | STSPIN9P23<br>STSPIN9P24 | Туре          | Function                                              |

|---------------------|--------------------------|--------------------------|---------------|-------------------------------------------------------|

| 22                  | SN                       | SP                       | Analog input  | Sense amplifier non inverting input                   |

| 23                  | SN                       | SN                       | Analog input  | Sense amplifier inverting input                       |

| 24                  | SN                       | SO                       | Analog output | Sense amplifier output/Comparator non inverting input |

| 25, 30, 31, 32, 33, | 01                       | JT2                      | Analanaut     | Half-bridge B output                                  |

| EPAD5               |                          | 112                      | Analog out    | (LS MOSFET drain, HS MOSFET source)                   |

| 26, 27, 28, 29      | 1.0                      | S2                       | Analog out    | Half-bridge B reference voltage                       |

| 20, 21, 20, 29      | LS                       | 32                       | Arialog out   | (LS MOSFET source)                                    |

| 40                  | CI                       | P1                       | Analog out    | Fly capacitor pin 1                                   |

| 41                  | CI                       | 2                        | Analog out    | Fly capacitor pin 2                                   |

| 42                  | ВО                       | ОТ                       | Supply        | Bootstrap voltage                                     |

| 45                  | EN1                      | -                        | Digital input | Enable input 1                                        |

| 45                  | -                        | EN                       | Digital input | Enable input                                          |

| 46                  | IN1                      | -                        | Digital input | Driving input 1                                       |

| 46                  | -                        | PWM                      | Digital input | PWM input                                             |

| 47                  | EN2                      | -                        | Digital input | Enable input 2                                        |

| 47                  | -                        | nBRAKE                   | Digital input | Brake input (active low)                              |

| 48                  | IN2                      | -                        | Digital input | Driving input 2                                       |

| 48                  | -                        | PH                       | Digital input | Phase input                                           |

| 49                  | S                        | R                        | Analog input  | Slew-rate setting                                     |

| 51                  | nS1                      | ГВҮ                      | Digital input | Active low standby                                    |

| 52                  | VC                       | CC                       | Supply        | 14 V regulator output                                 |

DS15030 - Rev 1 page 6/33

# 4 Device ratings

# 4.1 Absolute maximum ratings (AMR)

Stresses above the absolute maximum ratings listed in Table 3may cause permanent damage to the device. Prolonged exposure to conditions at or above the maximum ratings may affect device reliability.

Table 3. Absolute maximum ratings

| Symbol              | Parameter                                             | Test condition | Value                            | Unit |

|---------------------|-------------------------------------------------------|----------------|----------------------------------|------|

| V <sub>M</sub>      | Main supply voltage                                   |                | -0.3 to 80 <sup>(1)</sup>        | V    |

| V <sub>CC</sub>     | Gate driver supply voltage                            |                | -0.3 to 18                       | V    |

| V <sub>REG3V3</sub> | 3.3 V regulator supply voltage                        |                | -0.3 to 4                        | V    |

| I <sub>OUT</sub>    | Output current (each output)                          | DC current     | 6                                | Α    |

| CP1                 | Charge pump capacitor pin 1 voltage                   |                | -0.3 to V <sub>M</sub> +0.3      | V    |

| CP2                 | Charge pump capacitor pin 2 voltage                   |                | -0.3 to BOOT+0.3                 | V    |

| V <sub>BOOT</sub>   | Bootstrap voltage                                     |                | -0.3 to V <sub>M</sub> +18       | V    |

| V <sub>OUTx</sub>   | OUTx pin voltage                                      | DC             | -0.6 to V <sub>M</sub> +0.4      | V    |

| V <sub>SLS</sub>    | Low-side source voltage                               | DC             | -0.6 to +0.6                     | V    |

| V <sub>IO</sub>     | Logic input/output voltage                            |                | -0.3 to 5.5                      | V    |

| V <sub>SR</sub>     | Slew rate pin voltage                                 |                | -0.3 to V <sub>REG3V3</sub> +0.3 | V    |

| I <sub>OD</sub>     | Open-drain sink current                               |                | Up to 10                         | mA   |

| V <sub>SNSO</sub>   | Current-sensing amplifier output voltage              |                | -0.3 to V <sub>REG3V3</sub> +0.3 | V    |

| I <sub>SNSO</sub>   | Current-sensing amplifier output current              |                | Up to 35                         | mA   |

| V <sub>SNSP</sub>   | Current-sensing amplifier non-inverting input voltage | DC             | -0.6 to +0.6                     | V    |

| V <sub>SNSN</sub>   | Current sensing amplifier inverting input voltage     | DC             | -0.6 to +0.6                     | V    |

| $V_{REF}$           | Reference voltage                                     |                | -0.3 to V <sub>REG3V3</sub> +0.3 | V    |

| T <sub>stg</sub>    | Storage temperature                                   |                | -55 to 150                       | °C   |

| T <sub>J</sub>      | Junction temperature                                  |                | -40 to 150                       | °C   |

<sup>1.</sup> MOSFETs are based on 100 V technology, the actual supply voltage could be limited by gate driver ratings.

### 4.2 ESD characteristics

Table 4. ESD protection ratings

| Symbol                  | Parameter                                          | Test Condition                                             | Class | Value | Unit |

|-------------------------|----------------------------------------------------|------------------------------------------------------------|-------|-------|------|

| HBM                     | Human Body Model                                   | Conforming to ANSI/ESDA/JEDEC JS-001-2014                  | H2    | 2000  | V    |

| CDM Charge Device Model | All pins Conforming to ANSI/ESDA/JEDEC JS-002-2014 | C2a                                                        | 500   | V     |      |

| CDIVI                   | Charge Device Model                                | Corner pins only Conforming to ANSI/ESDA/JEDEC JS-002-2014 | C2    | 750   | V    |

DS15030 - Rev 1 page 7/33

# 4.3 Recommended operating conditions

Table 5. Recommended operating conditions

| Symbol              | Parameter                                             | Test condition         | Min | Тур                             | Max                         | Unit |

|---------------------|-------------------------------------------------------|------------------------|-----|---------------------------------|-----------------------------|------|

| V <sub>M</sub>      | Motor supply voltage                                  |                        | 7   |                                 | 75                          | V    |

| V                   | Cata driver symply veltage                            |                        |     | 14                              |                             | V    |

| V <sub>CC</sub>     | Gate driver supply voltage                            | VM and VCC pin shorted | 7   |                                 | 15                          | V    |

| C <sub>CC</sub>     | VCC regulator output capacitor                        |                        |     | 4.7                             |                             | μF   |

| V <sub>BOOT</sub>   | Bootstrap voltage                                     |                        |     | V <sub>M</sub> +V <sub>CC</sub> |                             | V    |

| C <sub>BOOT</sub>   | Bootstrap capacitor                                   |                        |     | 1                               |                             | μF   |

| C <sub>FLY</sub>    | Charge pump fly capacitor                             |                        |     | 220                             |                             | nF   |

| C <sub>REG3V3</sub> | REG3V3 capacitor                                      |                        |     | 4.7                             |                             | μF   |

| C <sub>SNSO</sub>   | Differential amplifier output capacitor               |                        |     |                                 | 100                         | pF   |

| V <sub>IO</sub>     | Logic input/output voltage                            |                        | 0   |                                 | 5                           | V    |

| I <sub>OD</sub>     | Open-drain sink current                               |                        |     |                                 | 4                           | mA   |

| V <sub>SNSO</sub>   | Current-sensing amplifier output voltage              |                        | 0   |                                 | 3.3                         | V    |

| V <sub>SNSP</sub>   | Current-sensing amplifier non-inverting input voltage |                        | 0   |                                 | 0.5                         | V    |

| V <sub>SNSN</sub>   | Current-sensing amplifier inverting input voltage     |                        |     | 0                               |                             | V    |

| V <sub>REF</sub>    | Reference voltage                                     |                        | 0   |                                 | 3.3                         | V    |

| _                   |                                                       | V <sub>M</sub> ≥ 15 V  |     |                                 | 100                         | kHz  |

| f <sub>PWM</sub>    | PWM frequency                                         | V <sub>M</sub> < 15 V  |     |                                 | 100<br>5<br>4<br>3.3<br>0.5 | kHz  |

| T <sub>amb</sub>    | Operative ambient temperature                         |                        | -40 |                                 | 125 (1)                     | °C   |

<sup>1.</sup> The actual operative range depends on power dissipation and actual junction-ambient thermal resistance of the device in the final application.

#### 4.4 Thermal data

Table 6. Thermal data

| Symbol                | Parameter                                   | Value | Unit |

|-----------------------|---------------------------------------------|-------|------|

| R <sub>th(J-CT)</sub> | Thermal resistance, junction-to-case top    | 13.6  | °C/W |

| R <sub>th(J-CB)</sub> | Thermal resistance, junction-to-case bottom | 1.2   | °C/W |

DS15030 - Rev 1 page 8/33

# 5 Electrical characteristics

Testing conditions:  $V_M$  = 48 V, unless otherwise specified.

Typical values are tested at  $T_J$  = 25 °C, minimum and maximum values are guaranteed by thermal characterization in the range of -40 to 125 °C, unless otherwise specified

**Table 7. Electrical characteristics**

| Symbol                 | Parameter                                   | Test condition                                | Min  | Тур  | Max | Unit |

|------------------------|---------------------------------------------|-----------------------------------------------|------|------|-----|------|

| Supply                 |                                             |                                               |      |      |     |      |

| $V_{CC,on}$            | VCC supply UVLO turn-on threshold           |                                               | 6.45 |      | 7   | V    |

| Van                    | VCC supply UVLO hysteresis                  |                                               |      | 240  |     | m)/  |

| $V_{CC,hyst}$          | (V <sub>CC,on</sub> - V <sub>CC,off</sub> ) |                                               |      | 240  |     | mV   |

| $V_{\text{BO,on}}$     | Bootstrap supply UVLO turn-on threshold     | $V_{BO} = V_{BOOT} - V_{M}$                   | 5.8  |      | 7   | V    |

| V <sub>BO,hyst</sub>   | Bootstrap supply UVLO hysteresis            |                                               |      | 240  |     | mV   |

| *BO,nyst               | (V <sub>BO,on</sub> - V <sub>BO,off</sub> ) |                                               |      | 240  |     | 1110 |

| $V_{REG3V3}$           | Internal 3.3 V regulator output voltage     | I <sub>SHORT</sub> = 41 mA                    |      | 3.3  |     | V    |

|                        |                                             | All MOSFETs off                               |      |      |     |      |

| I <sub>Mq</sub>        | Overall quiescent consumption from VM       | No external load on user regulator            |      | 5.2  |     | mA   |

|                        | ·                                           | No load on SNSO                               |      |      |     |      |

|                        |                                             | $R_{OFF}$ = 12 k $\Omega$ , fixed $t_{OFF}$   |      |      |     |      |

| I <sub>STBY</sub>      | Standby current consumption                 | nSTBY = low, T <sub>J</sub> = 25 °C           |      |      | 0.5 | μΑ   |

|                        | ,                                           | nSTBY = low, full temperature range           |      |      | 1   |      |

| t <sub>STBY,off</sub>  | Standby to MOSFETs turn-off                 | See Figure 6                                  |      | 22.5 |     | μs   |

| t <sub>STBY,dis</sub>  | MOSFETs turn-off to circuitry disabling     | See Figure 6                                  |      | 5    |     | μs   |

| t <sub>STBY,on</sub>   | Standby wake-up time                        | See Figure 6 (1)                              |      | 32   |     | μs   |

| -51B1,0II              | Claridady wante up time                     | nSTBY low pulse 1 ms                          |      | 02   |     | μο   |

| 14 V LDO linea         | ar regulator                                |                                               | _    |      | _   |      |

| V <sub>CC</sub>        | 14 V linear regulator output                |                                               |      | 14.2 |     | V    |

| $I_{CC,lim}$           | Maximum regulator current                   |                                               |      | 40   |     | mA   |

| Power stage            |                                             |                                               |      |      |     |      |

| R <sub>DS(ON),LS</sub> | Low-side turn-on resistance                 | T <sub>J</sub> = 25 °C                        |      | 27   |     | mΩ   |

| TVDS(UN),LS            | Low-side turn-on resistance                 | Full temperature range                        |      |      | 59  | mΩ   |

| Provention             | High eide turn on registance                | T <sub>J</sub> = 25 °C                        |      | 27   |     | mΩ   |

| R <sub>DS(ON),HS</sub> | High-side turn-on resistance                | Full temperature range                        |      |      | 59  | mΩ   |

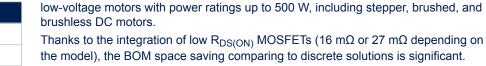

| t <sub>dINH</sub>      | Input-high to high-side turn-on propagation | Maximum slew rate                             |      | 1.6  |     | μs   |

| GINH                   | delay (including DT)                        | 50% IN to 20% OUT                             |      | 1.0  |     | μο   |

| t <sub>dINL</sub>      | Input-low to low-side turn-on propagation   | Maximum slew rate                             |      | 1.6  |     | μs   |

| UIIVE                  | delay (including DT)                        | 50% IN to 80% OUT                             |      |      |     |      |

|                        |                                             | $V_{BOOT} = V_{M} + V_{CC}$                   |      |      |     |      |

| t <sub>on_MOS</sub>    | High-side MOSFET turn-on propagation        | V <sub>in</sub> = 0 - 3.3 V                   |      | 250  |     | ns   |

| 5 <u>_</u> m00         | delay                                       | OUT 500 $\Omega$ to 0V, V <sub>M</sub> = 48 V |      |      |     |      |

|                        |                                             | 50% V <sub>in</sub> to 10 or 90% OUT          |      |      |     |      |

DS15030 - Rev 1 page 9/33

characteristics

| Symbol                         | Parameter                                 | Test condition                                 | Min | Тур  | Max | Ur |

|--------------------------------|-------------------------------------------|------------------------------------------------|-----|------|-----|----|

|                                |                                           | Max slew rate                                  |     |      |     |    |

|                                |                                           | $V_{BOOT} = V_{M} + V_{CC}$                    |     |      |     |    |

| t <sub>on_MOS</sub> Low-side M |                                           | V <sub>in</sub> = 0 - 3.3 V                    |     |      |     |    |

|                                | Low-side MOSFET turn-on propagation       | OUT 500 Ω to 48 V                              |     | 270  |     | n  |

|                                | delay                                     | 50% V <sub>in</sub> to 10 or 90% OUT           |     |      |     |    |

|                                |                                           | Max slew rate                                  |     |      |     |    |

|                                |                                           | $V_{BOOT} = V_{M} + V_{CC}$                    |     |      |     |    |

|                                |                                           | V <sub>in</sub> = 0 - 3.3 V                    |     |      |     |    |

|                                | High-side MOSFET turn-on propagation      | OUT 500 $\Omega$ to 0V, V <sub>M</sub> = 48 V  |     | 850  |     |    |

|                                | delay                                     |                                                |     | 030  |     |    |

|                                |                                           | 50% V <sub>in</sub> to 10 or 90% OUT           |     |      |     |    |

| t <sub>off_MOS</sub>           |                                           | Max slew rate                                  |     |      |     | r  |

|                                |                                           | $V_{BOOT} = V_{M} + V_{CC}$                    |     |      |     |    |

|                                | Low side MOSEET turn on propagation       | $V_{in} = 0 - 3.3 \text{ V}$                   |     |      |     |    |

|                                | Low-side MOSFET turn-on propagation delay | OUT 500 Ω to 48 V                              |     | 480  |     |    |

|                                |                                           | 50% V <sub>in</sub> to 10 or 90% OUT           |     |      |     |    |

|                                |                                           | Max slew rate                                  |     |      |     |    |

| $t_{DT}$                       | Deadtime                                  |                                                |     | 1.3  |     | ı  |

| NAT                            | Duana matica delau matakina               | Maximum Slew Rate                              |     |      | 450 |    |

| MT                             | Propagation delay matching                | $MT =  t_{dINH} - t_{dINL} $                   |     |      | 150 | '  |

|                                |                                           | $V_{BOOT} = V_{M} + V_{CC}$                    |     |      |     |    |

|                                |                                           | EN = 0 - 3.3 V                                 |     |      |     |    |

|                                | High-side MOSFET enable propagation       | OUT 500 $\Omega$ to 0 V, V <sub>M</sub> = 48 V |     | 250  |     |    |

|                                | delay                                     | 50% EN to 10 or 90% OUT                        |     |      |     |    |

|                                |                                           | Max slew rate                                  |     |      |     |    |

| t <sub>dENH</sub>              |                                           | $V_{BOOT} = V_{M} + V_{CC}$                    |     |      |     | 1  |

|                                |                                           | EN = 0 - 3.3 V                                 |     |      |     |    |

|                                | Low-side MOSFET enable propagation        | OUT 500 Ω to 48 V                              |     | 270  |     |    |

|                                | delay                                     | 50% EN to 10 or 90% OUT                        |     |      |     |    |

|                                |                                           | Max slew rate                                  |     |      |     |    |

|                                |                                           | $V_{BOOT} = V_{M} + V_{CC}$                    |     |      |     |    |

|                                |                                           | EN = 0 - 3.3 V                                 |     |      |     |    |

|                                | High-side MOSFET disable propagation      | OUT 500 $\Omega$ to 0 V, V <sub>M</sub> = 48 V |     | 760  |     |    |

|                                | delay                                     | 50% EN to 10 or 90% OUT                        |     |      |     |    |

|                                |                                           | Max slew rate                                  |     |      |     |    |

| $t_{dENL}$                     |                                           | $V_{BOOT} = V_{M} + V_{CC}$                    |     |      |     | 1  |

|                                |                                           | VBOOT - VM + VCC<br>EN = 0 - 3.3 V             |     |      |     |    |

|                                | Low-side MOSFET disable propagation       | OUT 500 Ω to 48 V                              |     | 450  |     |    |

|                                | delay                                     | 50% EN to 10 or 90% OUT                        |     | -100 |     |    |

|                                |                                           | Max slew rate                                  |     |      |     |    |

|                                |                                           | R <sub>SR</sub> = short to 3.3 V               |     | 1    |     |    |

| CD.                            | Rising slew rate                          |                                                |     |      |     |    |

| SR <sub>rise</sub>             | (20% - 80%)                               | $R_{SR} = 44 \text{ k}\Omega$                  |     | 0.5  |     | V  |

|                                |                                           | $R_{SR} = 22 k\Omega$                          |     | 0.3  |     |    |

page 10/33

**Electrical**

| Symbol                     | Parameter                                  | Test condition                                  | Min  | Тур | Max  | Unit |

|----------------------------|--------------------------------------------|-------------------------------------------------|------|-----|------|------|

| SR <sub>rise</sub>         | Rising slew rate (20% - 80%)               | R <sub>SR</sub> = short to 0 V                  |      | 0.2 |      | V/ns |

|                            |                                            | R <sub>SR</sub> = short to 3.3 V                |      | 1   |      |      |

| 0.5                        | Falling slew rate                          | R <sub>SR</sub> = 44 kΩ                         |      | 0.5 |      |      |

| SR <sub>fall</sub>         | (80% - 20%)                                | R <sub>SR</sub> = 22 kΩ                         |      | 0.3 |      | V/ns |

|                            |                                            | R <sub>SR</sub> = short to 0 V                  |      | 0.2 |      |      |

| Logic input an             | d outputs                                  |                                                 |      |     |      |      |

| V <sub>IL(EN)</sub>        | Low logic input voltage                    | EN, ENx and nBRAKE inputs                       |      |     | 0.4  | ٧    |

| V <sub>IH(EN)</sub>        | High logic input voltage                   | EN, ENx and nBRAKE inputs                       | 2.55 |     |      | ٧    |

| V <sub>IL</sub>            | Low logic input voltage                    | INx, PWM and PH inputs                          |      |     | 0.8  | ٧    |

| V <sub>IH</sub>            | High logic input voltage                   | INx, PWM and PH inputs                          | 2.1  |     |      | V    |

| R <sub>PDin</sub>          | Input pull-down resistor                   |                                                 |      | 500 |      | kΩ   |

| V <sub>OL</sub>            | Open drain outputs low logic voltage       | I <sub>SINK</sub> = 4 mA                        |      |     | 0.35 | ٧    |

| I <sub>H,SR</sub>          | SR current generator                       |                                                 |      | 50  |      | μA   |

| Integrated con             | nparator                                   |                                                 |      |     |      |      |

| V <sub>COMP,offset</sub>   | Comparator offset                          | V <sub>REF</sub> = 1 V                          |      |     | 10   | mV   |

| t <sub>COMP,delay</sub>    | Propagation delay                          | V <sub>REF</sub> = 1 V                          |      | 240 |      | ns   |

| t <sub>COMP,deglitch</sub> | Deglitch filter                            |                                                 |      | 130 |      | ns   |

| Integrated amp             | olifier                                    |                                                 |      |     |      |      |

| V <sub>AMPoffset</sub>     | Amplifier offset                           | T <sub>J</sub> = 25 °C                          |      |     | 6    | mV   |

| ▼ AMPoffset                | Ampliner onset                             | Full temperature range                          |      |     | 7    | mV   |

| A <sub>CL</sub>            | Amplifier gain                             |                                                 | 9.5  | 10  | 10.5 | V/V  |

| R <sub>in,AMP</sub>        | Equivalent input resistance                |                                                 |      | 90  |      | kΩ   |

|                            | High-level output voltage                  | V <sub>SNSP</sub> = 0.36 V                      |      |     |      |      |

| V <sub>SNSOH</sub>         | (V <sub>REG3V3</sub> - V <sub>SNSO</sub> ) | V <sub>SNSN</sub> = 0 V                         |      | 14  |      | mV   |

|                            | (*REG3V3 *3NSO/                            | I <sub>L</sub> = 500 μA                         |      |     |      |      |

| V <sub>SNSOL</sub>         | Low-level output voltage                   | I <sub>L</sub> = 500 μA                         |      | 20  |      | mV   |

| t <sub>settling</sub>      | Output voltage settling time               | V <sub>in</sub> 150 mV step                     |      | 150 |      | ns   |

| Setting                    | Surput voltage setting time                | $R_L = 3 \text{ k}\Omega, C_L = 100 \text{ pF}$ |      | 100 |      | 110  |

| Current limiter            |                                            |                                                 |      |     | ,    |      |

| V <sub>toffDIS</sub>       | PWM trimming mode voltage on TOFF pin      |                                                 |      |     | 0.2  | V    |

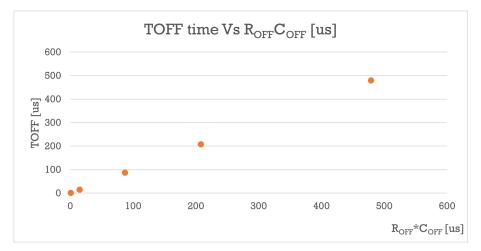

|                            |                                            | $R_{OFF}$ = 10 k $\Omega$ , $C_{OFF}$ = 0.1 nF  |      | 1   |      | μs   |

| t <sub>OFF</sub>           | Current limiter off time                   | $R_{OFF}$ = 23 k $\Omega$ , $C_{OFF}$ = 0.5 nF  |      | 10  |      | μs   |

|                            |                                            | $R_{OFF}$ = 630 k $\Omega$ , $C_{OFF}$ = 1 nF   |      | 550 |      | μs   |

|                            |                                            | SR short to 3.3 V                               |      | 1.3 |      |      |

| t <sub>BLANK</sub>         | Blanking time                              | $R_{SR}$ = 44 k $\Omega$                        |      | 2.1 |      | μs   |

| BLANK                      | Banking unc                                | $R_{SR}$ = 22 k $\Omega$                        |      | 3.2 |      | μο   |

|                            |                                            | SR short to 0 V                                 |      | 4.5 |      |      |

DS15030 - Rev 1 page 11/33

characteristics

| Symbol                       | Parameter                                                 | Test condition         | Min | Тур                | Max | Unit |

|------------------------------|-----------------------------------------------------------|------------------------|-----|--------------------|-----|------|

| Open-load dete               | ction                                                     |                        |     |                    |     |      |

| t <sub>OLD,refresh</sub>     | Open-load detection refresh time                          |                        |     | 100                |     | μs   |

| t <sub>OLD,check</sub>       | Open-load detection check time                            |                        |     | 100                |     | μs   |

| I <sub>OLD,PD</sub>          | Open-load detection pull-down                             |                        |     | 2.5                | 3   | mA   |

| V <sub>OLDL</sub>            | Open-load detection low threshold                         |                        |     | 2.3                |     | V    |

| V <sub>OLDH</sub>            | Open-load detection high threshold                        |                        |     | V <sub>M</sub> + 2 |     | V    |

| Overcurrent pro              | otection                                                  |                        |     |                    |     |      |

| loc                          | Overcurrent threshold                                     | T <sub>J</sub> = 25 °C | 8   | 13                 |     | Α    |

| OC                           |                                                           | Full temperature range | 6   |                    |     |      |

| V <sub>RELEASE</sub>         | OC release ENABLE threshold                               |                        | 0.4 |                    |     | V    |

| Thermal shutdo               | own                                                       |                        |     |                    |     |      |

| T <sub>SD</sub>              | Thermal shutdown threshold (regulator protection)         |                        |     | 150                |     | °C   |

| T <sub>SD,release</sub>      | Thermal shutdown release threshold (regulator protection) |                        |     | 120                |     | °C   |

| T <sub>SD(MOS)</sub>         | Thermal shutdown threshold (MOSFETs protection)           |                        | 120 | 130                |     | °C   |

| T <sub>SD(MOS),release</sub> | Thermal shutdown release threshold (MOSFETs protection)   |                        | 100 |                    |     | °C   |

<sup>1.</sup> The actual time to return to operative condition may depend on settling time of supply voltages ( $V_{REG3V3}$ ,  $V_{CC}$  and  $V_{BOOT}$ ).

page 12/33

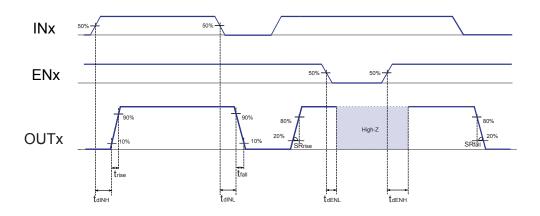

# **5.1** Timing diagrams

Figure 5. Propagation delay definition, PWM, EN, nBRAKE, OUTx

DS15030 - Rev 1 page 13/33

# 6 Control die description

The following sections describe in detail the control-die architecture and the function of the sub-blocks.

#### 6.1 Supply and regulators

The control die integrates three linear regulators generating different supply voltages, starting from the main supply input (VM).

#### 6.1.1 Power-up and power-down

During power-up, all the MOSFETs are kept off, with maximum allowed sink current, until:

- Low-side (V<sub>CC</sub>) and high-side (V<sub>BOOT</sub>) gate driver supplies are asserted above respective ULVO thresholds.

- Internal control blocks are properly supplied and operative.

#### 6.1.2 3.3 V regulator (REG3V3)

The control circuitry requires a 3.3 V supply voltage for proper operation. This voltage is internally generated by a linear regulator requiring an external capacitor on the output line.

Note: This regulator cannot be used for supplying external components.

#### 6.1.3 14 V regulator (VCC)

The device integrates a 14 V linear regulator, which generates the gate drivers supply (V<sub>CC</sub>). The regulator has a maximum overall current availability I<sub>CC,lim</sub>, protecting the regulator against short circuit and overload.

Note: This regulator cannot be used for supplying external components.

#### 6.1.4 Charge pump

A charge pump supplies the high-side gate drivers and guarantees a 100% duty-cycle operation.

#### 6.1.5 Standby

Setting the nSTBY input low disables the power stage and forces the device in low consumption mode (current consumption:  $I_{STBY}$ ).

In this condition, the following circuits are disabled:

- All internal regulators

- Charge pump

- Gate drivers

- Analog front-end (differential amplifier and comparator)

- All protections

The embedded MOSFETs are kept off by the 100 k $\Omega$  pull-down resistor on the gate driver outputs.

Power stage enabled

Power stage disabled

Power stage disabled

Power stage enabled

Operative

Standby

Operative

Figure 6. Standby

DS15030 - Rev 1 page 14/33

#### 6.2 Control logic

The power stage is controlled using different driving strategies according to the device product code.

Table 8. Full-bridge with ENx/INx driving strategy, inputs to output

| ENx | INx | DECAY (1) | ОИТх           |

|-----|-----|-----------|----------------|

| 0   | X   | X         | High impedance |

| 1   | 0   | 0         | LS on          |

| 1   | 1   | 0         | HS on          |

| 1   | X   | 1         | LS on          |

<sup>1.</sup> Decay status forced by the current limiter circuit, if enabled. See Section 6.4.1.

Table 9. Full-bridge with PWM/PH driving strategy - inputs to outputs

| EN | nBRAKE | PWM | PH | DECAY (1) | OUT1           | OUT2           |

|----|--------|-----|----|-----------|----------------|----------------|

| 0  | ×      | X   | Х  | X         | High impedance | High impedance |

| 1  | 0      | X   | Х  | X         | LS on          | LS on          |

| 1  | 1      | 0   | 0  | 0         | LS on          | LS on          |

| 1  | 1      | 1   | 0  | 0         | LS on          | HS on          |

| 1  | 1      | 0   | 1  | 0         | LS on          | LS on          |

| 1  | 1      | 1   | 1  | 0         | HS on          | LS on          |

| 1  | 1      | X   | Х  | 1         | LS on          | LS on          |

<sup>1.</sup> Decay status forced by the current limiter circuit, if enabled. See Section 6.4.1.

All control inputs of the device have pull-down resistors to avoid unpredictable behaviour in case of pin disconnection.

#### 6.2.1 Dead time

The dead time feature, in companion with interlocking function, ensures that the high-side and low-side MOSFETs of the same channel are not turned ON simultaneously. A minimum dead time is enforced between the turn-off of one gate driver output and the turn-on of its complementary output.

DS15030 - Rev 1 page 15/33

#### 6.3 Gate driver

The high-side (HS) and low-side (LS) gate drivers have a similar block diagram:

- A reference pin for the low level (OUT for HS and LSS for LS).

- The output pad (GHS or GLS), directly connected to the gate of the embedded MOSFET.

- The supply pin (BOOT or VCC), fixed and independent of the reference node.

When the control die is disabled (e.g. in standby mode or not supplied), an equivalent 100 k $\Omega$  resistor ensures that the MOSFETs remain off.

The driver source current and turn-on timing are set to change the output slew rate among four values: for each slew rate, a pair of current and timing is selected based on the characteristics of the embedded MOSFET.

The sink current and turn-off timing are set only according to the integrated power MOSFETs targeting a fast turn-off. Turning off the MOSFETs with the maximum current allows for minimizing the dead time duration.

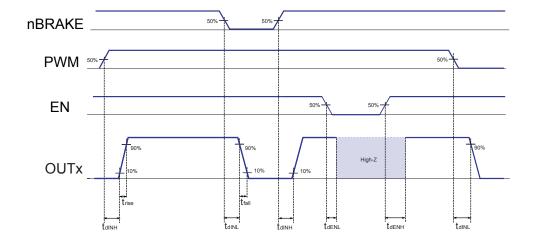

The voltage on the SR pin is set through an external pull-down resistor combined with an integrated pull-up.

Figure 7. Slew rate (SR) selection circuit

Table 10. Slew rate selection

| V <sub>SR</sub>                                                         | R <sub>SR</sub> (± 5%) | Output slew rate (typ)<br>at V <sub>M</sub> = 48 V | t <sub>rise</sub> / t <sub>fall</sub> |

|-------------------------------------------------------------------------|------------------------|----------------------------------------------------|---------------------------------------|

| V <sub>SR</sub> > 5/6 x V <sub>REG3V3</sub>                             | Short REG3V3           | 1 V/ns                                             | 50 ns                                 |

| 3/6 x V <sub>REG3V3</sub> < V <sub>SR</sub> < 5/6 x V <sub>REG3V3</sub> | 44 kΩ                  | 0.5 V/ns                                           | 100 ns                                |

| 1/6 x V <sub>REG3V3</sub> < V <sub>SR</sub> < 3/6 x V <sub>REG3V3</sub> | 22 kΩ                  | 0.3 V/ns                                           | 150 ns                                |

| V <sub>SR</sub> < 1/6 x V <sub>REG3V3</sub>                             | Short GND              | 0.2 V/ns                                           | 200 ns                                |

DS15030 - Rev 1 page 16/33

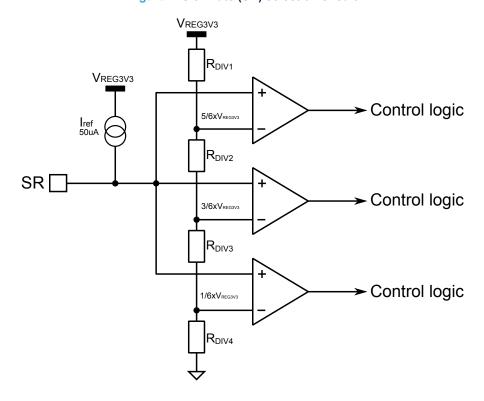

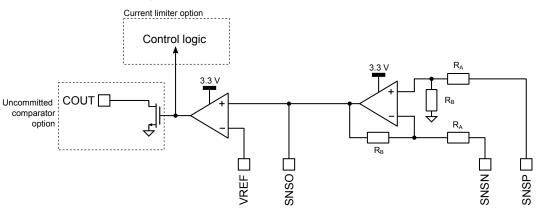

#### 6.4 Current sensing amplifier and comparator

The control die integrates one differential amplifier with a fixed gain factor of  $A_{CL}$  designed to amplify the signal from an external shunt resistor.

The differential voltage between SNSP (non-inverting input) and SNSN (inverting input) is amplified and available on the SNSO output.

The same signal is internally connected to the non-inverting input of a comparator, which according to the ordering code, is at user disposal or dedicated to a current limiting feature (see Section 6.4.1).

In the first case (uncommitted comparator), the result of the comparison is available on the COUT open-drain output with an inverted logic: when amplifier output is greater than VREF voltage, COUT is forced low.

In both cases, the inverting input of the comparator is available on the VREF input pin.

Figure 8. Embedded amplifier and comparator

It is possible to filter the amplifier output connecting to a small capacitor on the SNSO pin. This affects the comparator input as well.

#### 6.4.1 Current limiter

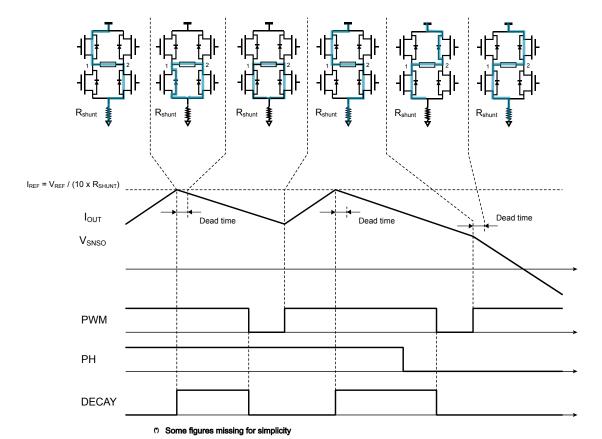

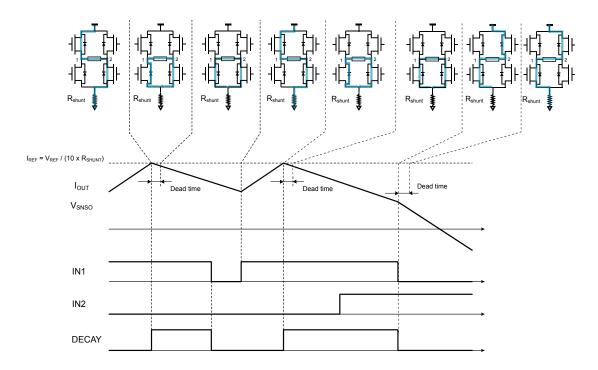

When the amplifier and the comparator are dedicated to the current limiter feature, the voltage drop of an external shunt resistor connected between SNSP and SNSN is amplified by  $A_{CL}$  and compared with the reference voltage  $(V_{RFF})$ .

When  $V_{SNSO} > V_{REF}$ , the comparator triggers, and the device operates according to the selected decay strategy. Two current limiter modes are available:

- Fixed OFF time (RC network on the TOFF pin)

- PWM trimming (TOFF pin shorted to ground)

To avoid spurious triggering of the current limiter, a blanking signal is applied to the comparator output during each power stage commutation.

DS15030 - Rev 1 page 17/33

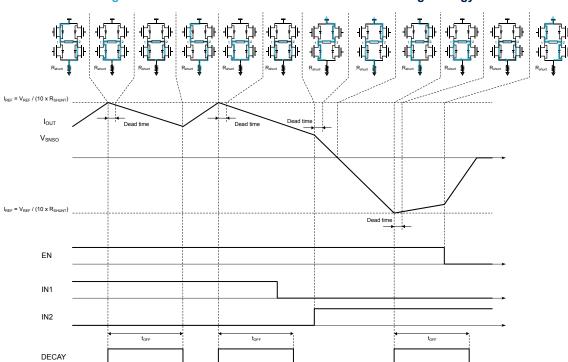

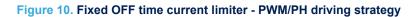

#### 6.4.1.1 Fixed OFF time

In fixed off time mode, when the comparator is triggered, the control circuitry sets the device in decay status for a  $t_{\text{off}}$  time.

This timing is adjusted through an RC network connected to the TOFF pin as shown in Figure 11.

Figure 9. Fixed OFF time current limiter - ENx/INx driving strategy

DS15030 - Rev 1 page 18/33

Figure 11. t<sub>OFF</sub> vs. R<sub>OFF</sub>- C<sub>OFF</sub> network

#### 6.4.1.2 PWM trimming mode

PWM trimming mode is activated by shorting the TOFF pin to ground. When the comparator is triggered, the control circuitry sets the device in decay status until one of the following conditions occurs:

- Full-bridge device with ENx/INx driving strategy: at least one of the inputs EN1, EN2, IN1 or IN2 is forced low.

- Full-bridge device with PWM/PH driving strategy: at least one of the inputs EN, PWM or nBRAKE is forced low.

Figure 12. PWM trimming current limiter (PWM/PH driving)

DS15030 - Rev 1 page 19/33

Figure 13. PWM trimming current limiter (ENx/INx driving)

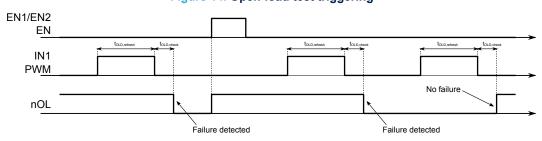

#### 6.5 Open-load detection

The control die integrates open-load detection circuitry.

If open-load failure condition is asserted, the nOL pin is forced low until one of the following conditions is satisfied:

- The bridge is enabled (i.e. leaving high impedance condition).

- The bridge successfully passes the next open-load check.

Note: The open-load failure does not interfere with normal operation.

In the device, an open-load test is performed when:

- PWM/PH driving case: EN input is low and a positive pulse of t<sub>OLD,refresh</sub> is applied on the PWM input (see Figure 14).

- ENx/INx driving case: both EN1 and EN2 inputs are low and a positive pulse of t<sub>OLD,refresh</sub> is applied on the IN1 input (see Figure 14).

Figure 14. Open-load test triggering

DS15030 - Rev 1 page 20/33

The test is performed as follows:

- 1. The OUT1 and OUT2 voltages are checked in accordance with the following cases:

- a. The voltage is above  $V_{\text{OLD},H}$ .

- b. The voltage is below  $V_{OLD,L}$ .

- c. The voltage is neither above  $V_{\mbox{\scriptsize OLD},\mbox{\scriptsize H}}$  nor below  $V_{\mbox{\scriptsize OLD},\mbox{\scriptsize L}}.$

- 2. A pull-down current I<sub>OLD,PD</sub> is applied to OUT1 and the output voltages (both OUT1 and OUT2) are checked again.

Figure 15. Open-load detection

The result of the two checks, which is available after  $t_{OLD,check}$ , defines the open-load condition assortment.

Table 11. Open-load detection test result

|                                                | Check 1 (pull-up)                        |                                                               |                                          |                                                                 |  |

|------------------------------------------------|------------------------------------------|---------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------|--|

| Check 2 (pull-down)                            | V <sub>OUT1,2</sub> > V <sub>OLD,H</sub> | V <sub>OLD,L</sub> < V <sub>OUT1,2</sub> < V <sub>OLD,H</sub> | V <sub>OUT1,2</sub> < V <sub>OLD,L</sub> | Mismatch between V <sub>OUT1</sub> and V <sub>OUT2</sub> status |  |

| V                                              | FAIL                                     | FAIL                                                          | FAIL                                     | FAIL                                                            |  |

| $V_{OUT1,2} > V_{OLD,H}$                       | (Anomalous)                              | (Anomalous)                                                   | (Anomalous)                              | (Anomalous)                                                     |  |

| V                                              | ОК                                       | FAIL                                                          | FAIL                                     | FAIL                                                            |  |

| $V_{OLD,L} < V_{OUT1,2} < V_{OLD,H}$           | (weak pull-up)                           | (Anomalous)                                                   | (Anomalous)                              | (Anomalous)                                                     |  |

| V                                              | ОК                                       | ОК                                                            | FAIL                                     | FAIL                                                            |  |

| $V_{OUT1,2} < V_{OLD,L}$                       | (load detected)                          | (weak pull-down)                                              | (Anomalous)                              | (Anomalous)                                                     |  |

| V <sub>OUT1</sub> and V <sub>OUT2</sub> status | FAIL                                     | FAIL                                                          | FAIL                                     | FAIL                                                            |  |

|                                                | (Anomalous)                              | (Anomalous)                                                   | (Anomalous)                              | (Anomalous)                                                     |  |

DS15030 - Rev 1 page 21/33

#### 6.6 Protections

The device integrates several protections as listed in Table 12.

All protections force the nFAULT output low until they are released.

Table 12. Protection summary table

| Protection                  | Triggering condition                               | Effect                                                 | Release condition                                             |

|-----------------------------|----------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|

| V <sub>CC</sub> UVLO        | $V_{CC} < V_{CC,off}$                              | Power stage disabled                                   | V <sub>CC</sub> ≥ V <sub>CC,on</sub>                          |

| Control die overtemperature | T <sub>J,control</sub> > T <sub>SD</sub>           | Power stage disabled VCC regulator and charge pump off | $T_{J,control} \le T_{SD,release}$                            |

| V <sub>BOOT</sub> UVLO      | $V_{BOOT} - V_{M} < V_{BO,off}$                    | HS MOSFET off LS MOSFET driven according to inputs     | $V_{BOOT} - V_{M} \ge V_{BO,on}$                              |

| V <sub>DS</sub> monitoring  | V <sub>DS</sub> of one MOSFET > V <sub>DS,th</sub> | Power stage disabled                                   | EN input forced low (V <sub>EN</sub> < V <sub>RELEASE</sub> ) |

| MOSFETs' overtemperature    | T <sub>J,MOS</sub> > T <sub>SD</sub>               | Power stage disabled                                   | $T_{J,MOS} \le T_{SD,release}$                                |

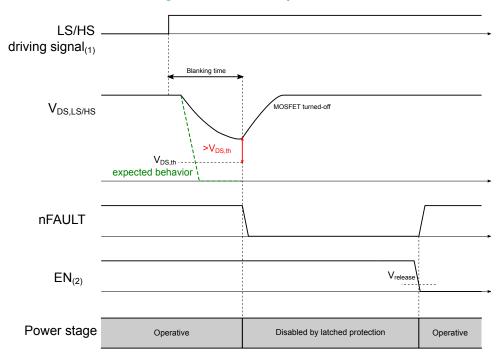

#### 6.6.1 Overcurrent protection (V<sub>DS</sub> monitoring)

The control die constantly monitors the drain-source drop of each power MOSFET:  $V_M - V_{OUT}$  for the high-side, and  $V_{OUT} - V_{SLS}$  for the low-side.

When a power MOSFET is expected to be on (i.e. at the end of the turn-on phase), and its drain-source drop exceeds the  $V_{DS,th}$  threshold, an overcurrent condition is triggered. This forces the power stage into a safe state and pulls the nFAULT output low.

The safe condition is achieved by turning off all MOSFETs using a reduced turn-off current to limit the dl/dt and avoid critical overshoots or undershoots below ground on the switching node.

The control die keeps the MOSFETs off until normal operation is restored by forcing the EN input low ( $V_{EN} < V_{RELEASE}$ ).

DS15030 - Rev 1 page 22/33

Figure 16. Overcurrent protection

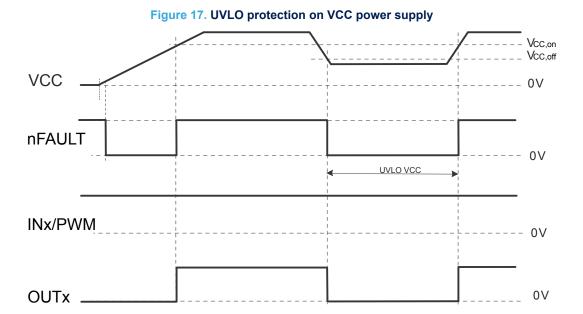

#### **Under-voltage lockout protection (UVLO)** 6.6.2

Undervoltage lockout protection (UVLO) is present on the following supplies:

- Low-side gate driver supply (V<sub>CC</sub>)

- High-side gate driver supply  $(V_{BOOT}-V_{M})$

During power-up, UVLO is released when the supply exceeds its respective "on" threshold. After power-up, the UVLO is triggered when the supply falls below its respective "off" threshold and is released again once the supply rises above the "on" threshold.

Deglitch filtering on the protection comparators prevents spurious triggering due to internally generated or externally coupled noises.

When at least one of the supplies is in UVLO condition, the power stage is forced into a safe state (i.e. all MOSFETs turned off), and the nFAULT output is forced low.

DS15030 - Rev 1 page 23/33

<sup>(1)</sup> According to specific driving option

(2) In ENx/INx option, both the EN1 and EN2 must be forced low.

#### 6.6.3 Thermal shutdown

Each MOSFET in the system-in-sackage is protected against overtemperature by a dedicated temperature sensor located in the driver die (one sensor per MOSFET). When the measured temperature of any MOSFET is above the safe threshold  $T_{SD(MOS)}$ , the control die turns off the power stage until the temperature of all MOSFETs is below  $T_{SD(MOS),release}$ .

A temperature monitoring circuit is also present in the control die. If the measured temperature is above the safe threshold  $T_{SD}$ , the VCC regulator and the charge pump are turned off until the temperature returns below  $T_{SD,release}$ .

In both cases, the nFAULT output is forced low.

DS15030 - Rev 1 page 24/33

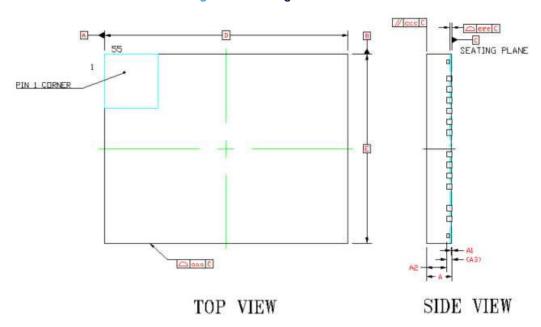

# 7 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

# 7.1 VFQFPN 9x7x1.0 mm 55L pitch 0.4 package information

Table 13. Package mechanical data

| Complete | Min. | Nom.       | Max. |

|----------|------|------------|------|

| Symbol   |      | [mm]       |      |

| Α        | 0.90 | 0.95       | 1.00 |

| A1       | 0.00 | 0.035      | 0.05 |

| A2       | -    | 0.75       | -    |

| A3       |      | 0.203 REF. |      |

| b        | 0.15 | 0.2        | 0.25 |

| D        |      | 9.00 BSC   |      |

| D1       | 1.91 | 2.01       | 2.11 |

| D2       | 1.50 | 1.60       | 1.70 |

| Е        |      | 7.00 BSC   |      |

| E1       | 4.30 | 4.40       | 4.50 |

| E2       | 2.10 | 2.20       | 2.30 |

| L        | 0.35 | 0.45       | 0.55 |

| е        |      | 0.4 BSC    |      |

|          | Tole | rance      |      |

| aaa      |      | 0.10       |      |

| bbb      |      | 0.07       |      |

| ccc      | 0.10 |            |      |

| ddd      | 0.05 |            |      |

| eee      | 0.08 |            |      |

| fff      |      | 0.1        |      |

DS15030 - Rev 1 page 25/33

Figure 18. Package outline

DS15030 - Rev 1 page 26/33

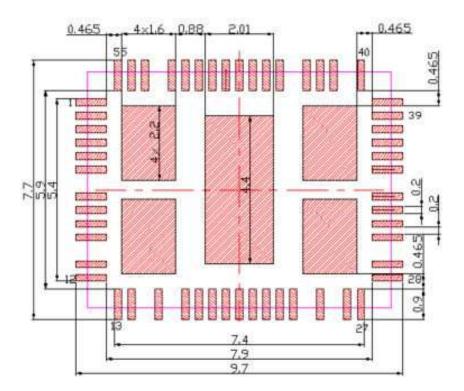

#### 7.2 Suggested footprint

The STSPIN9P2 footprint for the PCB layout is typically defined based on multiple design factors, such as assembly plant technology capabilities and board component density. For easy device usage and evaluation, ST provides the following footprint design, which is suitable for a wide range of PCBs.

Figure 19. Suggested footprint

DS15030 - Rev 1 page 27/33

# 8 Ordering information

Table 14. Order code

| Order code | Package                         | Package marking | Packing       |

|------------|---------------------------------|-----------------|---------------|

| STSPIN9P21 | VFQFPN 9x7x1.0 mm 55L pitch 0.4 | SPIN9P21        | Tape and reel |

| STSPIN9P22 | VFQFPN 9x7x1.0 mm 55L pitch 0.4 | SPIN9P22        | Tape and reel |

| STSPIN9P23 | VFQFPN 9x7x1.0 mm 55L pitch 0.4 | SPIN9P23        | Tape and reel |

| STSPIN9P24 | VFQFPN 9x7x1.0 mm 55L pitch 0.4 | SPIN9P24        | Tape and reel |

DS15030 - Rev 1 page 28/33

# **Revision history**

Table 15. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 12-Sep-2025 | 1       | Initial release. |

DS15030 - Rev 1 page 29/33

# **Contents**

| 1   | Ove      | rview          |                                                     | 2  |  |  |  |

|-----|----------|----------------|-----------------------------------------------------|----|--|--|--|

| 2   | Bloc     | k diagr        | rams                                                | 3  |  |  |  |

| 3   | Pin      | າ description  |                                                     |    |  |  |  |

| 4   | Devi     | Device ratings |                                                     |    |  |  |  |

|     | 4.1      | Absolu         | ute maximum ratings (AMR)                           | 7  |  |  |  |

|     | 4.2      | ESD c          | characteristics                                     | 7  |  |  |  |

|     | 4.3      | Recon          | mmended operating conditions                        | 8  |  |  |  |

|     | 4.4      | Therm          | nal data                                            | 8  |  |  |  |

| 5   | Elec     | trical c       | haracteristics                                      | 9  |  |  |  |

|     | 5.1      | Timing         | g diagrams                                          | 13 |  |  |  |

| 6   | Con      | trol die       | description                                         | 14 |  |  |  |

|     | 6.1      | Supply         | y and regulators                                    | 14 |  |  |  |

|     |          | 6.1.1          | Power-up and power-down                             | 14 |  |  |  |

|     |          | 6.1.2          | 3.3 V regulator (REG3V3)                            | 14 |  |  |  |

|     |          | 6.1.3          | 14 V regulator (VCC)                                | 14 |  |  |  |

|     |          | 6.1.4          | Charge pump                                         | 14 |  |  |  |

|     |          | 6.1.5          | Standby                                             | 14 |  |  |  |

|     | 6.2      | Contro         | ol logic                                            |    |  |  |  |

|     |          | 6.2.1          | Dead time                                           | 15 |  |  |  |

|     | 6.3      |                | driver                                              |    |  |  |  |

|     | 6.4      | Currer         | nt sensing amplifier and comparator                 |    |  |  |  |

|     |          | 6.4.1          | Current limiter                                     |    |  |  |  |

|     | 6.5      |                | load detection                                      |    |  |  |  |

|     | 6.6      | Protec         | ctions                                              |    |  |  |  |

|     |          | 6.6.1          | Overcurrent protection (V <sub>DS</sub> monitoring) |    |  |  |  |

|     |          | 6.6.2          | Under-voltage lockout protection (UVLO)             |    |  |  |  |

|     |          | 6.6.3          | Thermal shutdown                                    |    |  |  |  |

| 7   | Pacl     | •              | formation                                           |    |  |  |  |

|     | 7.1      |                | PN 9x7x1.0 mm 55L pitch 0.4 package information     |    |  |  |  |

|     | 7.2      |                | ested footprint                                     |    |  |  |  |

| 8   |          |                | formation                                           |    |  |  |  |

| Rev | vision   | history        | <sup>,</sup>                                        | 29 |  |  |  |

| Lis | t of tal | bles           |                                                     | 31 |  |  |  |

| Lis | t of fig | ıures          |                                                     | 32 |  |  |  |

# **List of tables**

| Table 1.  | Full-bridge ordering codes                                   | . 2 |

|-----------|--------------------------------------------------------------|-----|

| Table 2.  | STSPIN9P2 full-bridge - pin assignment                       | . 5 |

| Table 3.  | Absolute maximum ratings                                     | . 7 |

| Table 4.  | ESD protection ratings                                       | . 7 |

| Table 5.  | Recommended operating conditions                             | . 8 |

| Table 6.  | Thermal data                                                 |     |

| Table 7.  | Electrical characteristics                                   | . 9 |

| Table 8.  | Full-bridge with ENx/INx driving strategy, inputs to output  | 15  |

| Table 9.  | Full-bridge with PWM/PH driving strategy - inputs to outputs | 15  |

| Table 10. | Slew rate selection                                          | 16  |

| Table 11. | Open-load detection test result                              | 21  |

| Table 12. | Protection summary table                                     | 22  |

| Table 13. | Package mechanical data                                      | 25  |

| Table 14. | Order code                                                   | 28  |

| Table 15. | Document revision history                                    | 29  |

# **List of figures**

| Figure 1.  | STSPIN9P21 / STSPIN9P23 full-bridge with current limiter         | . 3 |

|------------|------------------------------------------------------------------|-----|

| Figure 2.  | STSPIN9P22 / STSPIN9P24 full-bridge with uncommitted AFE         |     |

| Figure 3.  | STSPIN9P2 full-bridge - pinout                                   |     |

| Figure 4.  | Propagation delay definition, INx/ENx, OUTx                      |     |

| Figure 5.  | Propagation delay definition, PWM, EN, nBRAKE, OUTx              | 13  |

| Figure 6.  | Standby                                                          | 14  |

| Figure 7.  | Slew rate (SR) selection circuit                                 | 16  |

| Figure 8.  | Embedded amplifier and comparator                                | 17  |

| Figure 9.  | Fixed OFF time current limiter - ENx/INx driving strategy        | 18  |

| Figure 10. | Fixed OFF time current limiter - PWM/PH driving strategy         | 18  |

| Figure 11. | t <sub>OFF</sub> vs. R <sub>OFF</sub> - C <sub>OFF</sub> network | 19  |

| Figure 12. | PWM trimming current limiter (PWM/PH driving)                    | 19  |

| Figure 13. | PWM trimming current limiter (ENx/INx driving)                   | 20  |

| Figure 14. | Open-load test triggering                                        | 20  |

| Figure 15. | Open-load detection                                              | 21  |

| Figure 16. | Overcurrent protection                                           | 23  |

| Figure 17. | UVLO protection on VCC power supply                              | 24  |

| Figure 18. | Package outline                                                  |     |

| Figure 19. | Suggested footprint                                              | 27  |

|            |                                                                  |     |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

DS15030 - Rev 1 page 33/33