# Power management IC for MPU: 2 buck converters and 4 LDOs

## **Features**

- Input voltage range from 2.8 V to 5.5 V

- 2 buck SMPS converters with adaptive constant on-time (COT) topology

- 2 adjustable general-purpose LDOs

- 1 LDO for DDR3L/DDR4 termination (sink-source) or as a general-purpose LDO

- 1 LDO for USB PHY supply

- 2 MHz switching frequency buck converters with forced PWM

- User programmable non-volatile memory (NVM), enabling scalability to support a wide range of applications

- Immediate output alternate settings toggle via dedicated power control pins

- Programmable output voltages turn ON/OFF sequences

- I<sup>2</sup>C and digital I/O control interfaces

- 2 GPO output controls for external commands

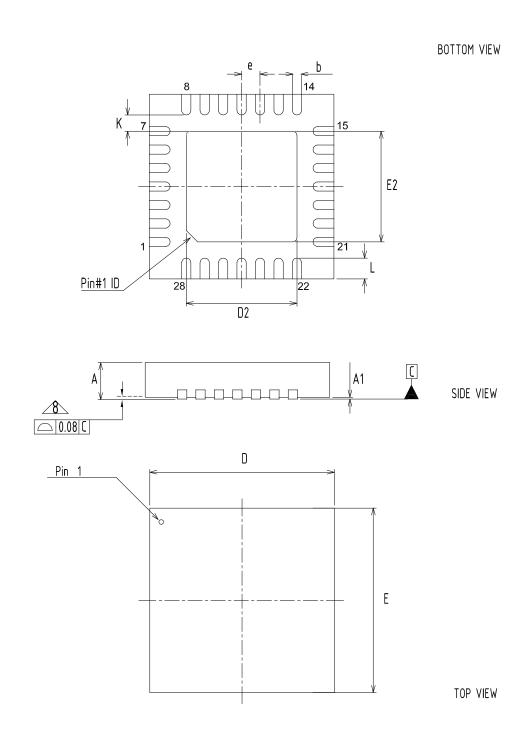

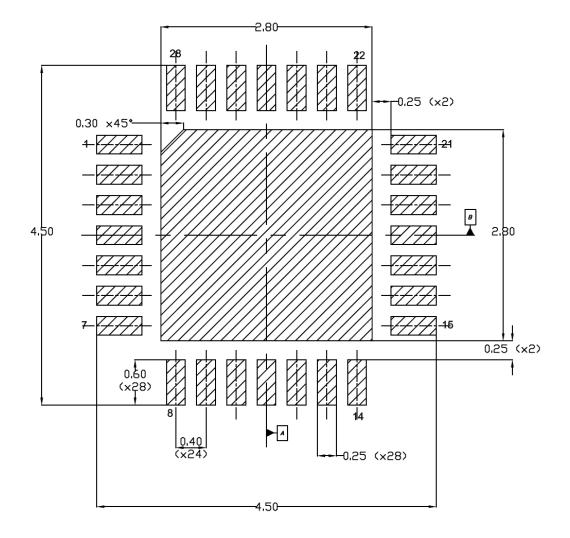

- VFQFPN 28L (4.0 x 4.0 x 1.0 mm)

#### **Maturity status link**

STPMIC1L

| Dev        | vice summary         |

|------------|----------------------|

|            | STPMIC1LAPQR         |

| Order code | STPMIC1LBPQR         |

|            | STPMIC1LDPQR         |

| Packing    | VFQFPN 28L           |

| 1 acking   | (4.0 x 4.0 x 1.0 mm) |

# **Applications**

- · Power management for embedded microprocessor units

- · Wearable and IoT devices

- Portable devices

- Human machine interfaces

- Smart home devices

- Power management unit companion chip for the STM32MP13/15 MPUs

## **Description**

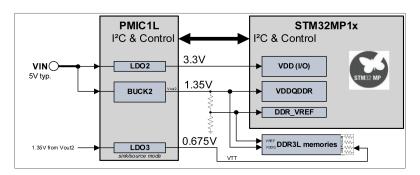

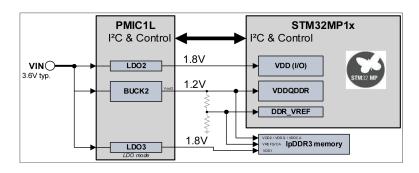

The STPMIC1L is a fully integrated power management IC designed for STM32MP1x MPU series applications requiring low power and high efficiency.

The device integrates advanced low-power features controlled by a host processor via I<sup>2</sup>C and I/O interfaces.

The STPMIC1L regulators are designed to supply power to the application processor as well as to external system peripherals such as DDR, and flash memories. The STPMIC1L supplies the core chipset (the MPU+ DDR+ 1 flash memory), but not other system devices. This is done via discrete regulators controlled by the STPMIC1L GPOs).

Two buck SMPS are optimized to provide excellent transient response and output voltage precision for a wide range of operating conditions. Advanced PWM phase-shift synchronization technique with integrated PLL reduces noise and EMI.

# 1 Device configuration table

The STPMIC1L has a non-volatile memory (NVM) that enables scalability to support a wide range of applications:

- Default output voltage, POWER\_UP/POWER\_DOWN sequences, protection behavior, auto turn-on functionality, and an I<sup>2</sup>C slave address.

- The STPMIC1LA, STPMIC1LB and STPMIC1LD are preprogrammed devices to support the STM32MP1x series application processor versions.

- Straightforward NVM reprogramming via I<sup>2</sup>C to facilitate mass production directly in target applications.

- Possibility to lock NVM content to prevent further reprogramming by writing LOCK NVM bit.

Table 1. Default configuration table

|            |                              |                           |      | Default                      | configuration table       | ;    |                              |                           |      |  |

|------------|------------------------------|---------------------------|------|------------------------------|---------------------------|------|------------------------------|---------------------------|------|--|

|            |                              | STPMIC1LA                 |      |                              | STPMIC1LB                 |      | STPMIC1LD                    |                           |      |  |

|            | Default<br>output<br>voltage | Default output<br>current | Rank | Default<br>output<br>voltage | Default output<br>current | Rank | Default<br>output<br>voltage | Default output<br>current | Rank |  |

| LDO2       | 3.3 V                        | 0.4 A OCP level 1         | 1    | 1.8 V                        | 0.4 A OCP level 1         | 1    | 3.3 V                        | 0.4 A OCP level 1         | 1    |  |

| LDO3       | -                            | OCP level 1               | 0    | -                            | OCP level 1               | 0    | -                            | OCP level 0               | 0    |  |

| LDO4       | 3.3 V                        | 40 mA OCP level           | 5    | 3.3 V                        | 40 mA OCP level           | 5    | 3.3                          | 40 mA OCP level           | 5    |  |

| LDO5       | 3.3 V                        | 0.4 A OCP level 0         | 4    | 2.9 V                        | 0.4 A OCP level 0         | 4    | 3.3 V                        | 0.4 A OCP level 0         | 4    |  |

| BUCK1      | 1.22 V                       | 1.5 A OCP level 1         | 2    | 1.22 V                       | 1.5 A OCP level 1         | 2    | 1.25 V                       | 1 A OCP level 1           | 2    |  |

| BUCK2      | -                            | 1.0 A OCP level 1         | 0    | -                            | 1.0 A OCP level 1         | 0    | 1.25 V                       | 1 A OCP level 1           | 3    |  |

| GPO1       | -                            | -                         | 3    | -                            |                           | 3    | -                            | -                         | 5    |  |

| GPO2       | -                            | -                         | 0    | -                            | -                         | 0    | -                            | -                         | 0    |  |

| VINOK_Rise | 4.0 V                        |                           | -    | 3.3 V                        |                           | -    | - 4.0 V                      |                           | -    |  |

| VINOK_Fall |                              | 3.5 V                     | -    |                              | 2.8 V                     | -    |                              | 3.5 V                     | -    |  |

All output voltages with Rank = 0 are by default programmed with 0 Dec (refer to Table 15 and Table 16).

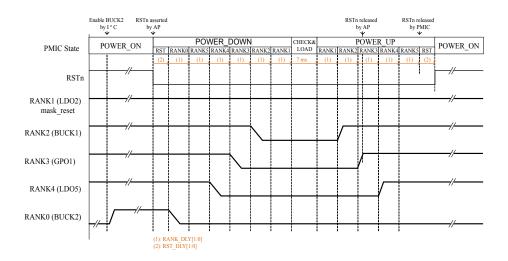

The startup sequence is split into six steps (Rank = 0 to Rank = 5).

Each buck converter or LDO regulator can be programmed to be automatically turned ON in one of these phases. Each rank phase is separated by a delay (1.5 ms, 3 ms, 4.5 ms, or 6 ms) programmed in the NVM:

- Rank = 0: rail not turned ON automatically, no output voltage appears after POWER-UP

- Rank = 1: rail automatically turned ON after 7 ms following a turn ON condition

- Rank = 2: rail automatically turned ON after a further 1.5 ms (by default)

- Rank = 3: rail automatically turned ON after a further 1.5 ms (by default)

- Rank = 4: rail automatically turned ON after a further 1.5 ms (by default)

- Rank = 5: rail automatically turned ON after a further 1.5 ms (by default)

Whatever the STPMIC1L version, the AUTO\_TURN\_ON option is set.

DS14839 - Rev 2 page 2/127

# Typical application schematic

(VIN from 2.8V to 5.5V DC)

BUCK1IN VIN□ VLX1 → VDDCORE BUCK1 CBUCK1IN ҆Ӷvouт1 (SMPS) CVOUT1 PGND1 **BUCK2IN** VLX2 → VDD DDR BUCK2 CVOUT2 (DDR3L, DDR4, IpDDR3, IpDDR4) CBUCK2IN: 工**VOUT2** (SMPS) PGND2 LDO2OUT LDO25IN LDO2 -- VOUT\_LDO2 (to Flash Memory CLDO2OUTor system device) CLDO25IN= LDO5OUT LDO3IN LDO5 VOUT\_LDO5

CLDO5OUT (1.8V or 3.3V to VDD\_DDR □ CLDO3IN: LDO3 LDO3OUT VTT\_DDR4

(to DDR3L/DDR4

terminations or to

lpDDR3/4 VDD1) VIO SYSTEM CONTROL VOUT\_LDO5 (normal, DDRVTT) SCL I2C SDA **INTLDO INTLDO** INTn CINTLDO AGND PWRCTRL1 REGISTER to / from host AP LDO4OUT - VDD33USB LDO4 STATE MACHINE CLDO4OUT (fixed 3.3V to MPU USB PHY) RSTn POWER GPO1 SUPPLIES CONTROL GPO<sub>2</sub> NVM user push button PONKEYn / EN LOGIC VIN VIN \_ CVIN: **GNDLDO** EPGND

Figure 1. Typical application schematic

Note: All BUCKxIN pins must be connected to the same voltage node as VIN.

VIN is the main STPMIC1L supply. All buck converters and linear regulators have dedicated or shared power supply pins. The dedicated VIO supply is for all digital interface pins, except GPOs.

No other supply voltages must be applied before VIN or set higher than VIN.

DS14839 - Rev 2 page 3/127

# 2.1 Recommended external components

**Table 2. Passive components**

| Component                                   | Manufacturer | Part number        | Value            | Size |

|---------------------------------------------|--------------|--------------------|------------------|------|

| CVIN, CLDO2OUT, CLDO4OUT, CLDO5OUT, CINTLDO |              | GRM155R60J475ME47D | 4.7 μF, 6.3 V    | 0402 |

| CLDO25IN                                    |              | GRM155R61E105KA12D | 1 μF, 25 V       | 0402 |

| CBUCK1IN, BUCK2IN                           |              | GRM188R61A106ME69D | 10 μF, 10 V      | 0603 |

| CVOUT1 (0.5 V - 1.5 V) LV                   | Murata       | GRM188R60J226MEA0D | 2 x 22 μF, 6.3 V | 0603 |

| CVOUT1 (1.5 V - 4.2 V) HV                   |              | GRM21BR61A226ME51L | 2 x 22 µF, 10 V  | 0805 |

| CVOUT2                                      |              | GRM188R60J226MEA0D | 2 x 22 μF, 6.3 V | 0603 |

| CLDO3IN, CLDO3OUT                           |              | GRM155R60J106ME05D | 10 μF, 6.3 V     | 0402 |

| LX1                                         | SAMSUNG      | CIGT201610LH1R0MNE | 1 µH             | 0806 |

| LX2                                         | JAMISUNG     | CIGT201610LH1R0MNE | 1 µH             | 0806 |

Note:

All the components above refer to a typical application working in an environment up to +85 °C ambient temperature. The operation of the device is not limited to the choice of these external components.

DS14839 - Rev 2 page 4/127

# 2.2 Pin out and pin description

LD030UT GNDLDO PGND2 LD03IN VOUT2 22 21 RSTn LDO25IN INTn 2 LDO5OUT VIO 3 LDO2OUT **EPGND** GPO1 18 LDO4OUT 4 GPO2 5 AGND PWRCTRL2 6 **INTLDO** 16 15 PWRCTRL1 VIN PGND1 BUCK11N PONKEYn/EN VLX1 SDA

Figure 2. Pin configuration VFQFPN 28L top view

Table 3. Pin description

| Pin name | A/D <sup>(1)</sup> | I/O <sup>(1)</sup> | Location | Description (default configuration)                                     | Not used pin connection |

|----------|--------------------|--------------------|----------|-------------------------------------------------------------------------|-------------------------|

| RSTn     | D                  | I/O                | 1        | Bidirectional reset (active low with internal pull-up)                  | Floating                |

| INTn     | D                  | 0                  | 2        | Interrupt (active low with internal pull-up)                            | Floating                |

| VIO      | Α                  | ı                  | 3        | I/O voltage (for all digital signals except PONKEYn/En and GPO1/2)      | VIO                     |

| GPO1     | D                  | 0                  | 4        | External Control 1                                                      | Floating                |

| GPO2     | D                  | 0                  | 5        | External Control 2                                                      | Floating                |

| PWRCTRL2 | D                  | ı                  | 6        | Power control 2 mode (pull-up and pull-down, pull-up active by default) | VIO or floating         |

| PWRCTRL1 | D                  | ı                  | 7        | Power control 1 mode (pull-up and pull-down, pull-up active by default) | VIO or floating         |

| VOUT1    | Α                  | I                  | 8        | Input feedback signal buck converter 1                                  | Floating                |

| PGND1    | Α                  | -                  | 9        | Power ground buck converter 1                                           | GND                     |

| VLX1     | Α                  | 0                  | 10       | LX node buck converter 1                                                | Floating                |

| BUCK1IN  | Α                  | I                  | 11       | Power input buck converter 1 VIN                                        |                         |

| SDA      | D                  | I                  | 12       | I <sup>2</sup> C serial data                                            | VIO                     |

DS14839 - Rev 2 page 5/127

| Pin name   | A/D <sup>(1)</sup> | I/O <sup>(1)</sup> | Location | Description (default configuration)                                     | Not used pin connection |

|------------|--------------------|--------------------|----------|-------------------------------------------------------------------------|-------------------------|

| SCL        | D                  | I/O                | 13       | I <sup>2</sup> C serial clock                                           | VIO                     |

| PONKEYn/En | D                  | ı                  | 14       | User power ON key / Enable (active low with internal pullup by default) | Floating                |

| VIN        | Α                  | I                  | 15       | Main power input - power input LDO4, VREF                               | VIN                     |

| INTLDO     | Α                  | 0                  | 16       | Internal LDO                                                            | 4.7 μF capacitor        |

| AGND       | Α                  | -                  | 17       | Main analog ground                                                      | GND                     |

| LDO4OUT    | Α                  | 0                  | 18       | Output voltage LDO4                                                     | Floating                |

| LDO2OUT    | Α                  | 0                  | 19       | Output voltage LDO2                                                     | Floating                |

| LDO5OUT    | Α                  | 0                  | 20       | Output voltage LDO5                                                     | Floating                |

| LDO25IN    | Α                  | I                  | 21       | Power input LDO2 and LDO5                                               | VIN                     |

| GNDLDO     | Α                  | -                  | 22       | LDO GND                                                                 | GND                     |

| LDO3OUT    | Α                  | 0                  | 23       | Output voltage LDO3                                                     | Floating                |

| LDO3IN     | Α                  | I                  | 24       | Power input LDO3                                                        | VIN                     |

| BUCK2IN    | Α                  | I                  | 25       | Power input buck converter 2                                            | VIN                     |

| VLX2       | Α                  | 0                  | 26       | LX node buck converter 2                                                | Floating                |

| PGND2      | Α                  | -                  | 27       | Power ground buck converter 2                                           | GND                     |

| VOUT2      | Α                  | I                  | 28       | Input feedback signal buck converter 2                                  |                         |

| EPGND      | Α                  | -                  | ePad     | Exposed pad to be connected to ground                                   | GND                     |

<sup>1.</sup> A: analog; D: digital; I/O: input/Output

DS14839 - Rev 2 page 6/127

# 3 Electrical and timing characteristics

# 3.1 Absolute maximum ratings

Table 4. Absolute maximum ratings

| Parameter                                      | Min.         | Unit |

|------------------------------------------------|--------------|------|

| VIN, BUCKxIN, VLXx, LDO3IN, LDOxIN, PONKEYn/En | -0.5 to +6.5 |      |

| VIO, SDA, SCL, RSTn, PWRCTRLx, INTn            | -0.5 to +4.2 |      |

| INTLDO                                         | -0.5 to +2   | V    |

| VOUT1, LDOxOUT, GPO1, GPO2                     | -0.5 to +5.5 |      |

| VOUT2                                          | -0.5 to +3   |      |

| ESD HBM                                        | ±1000        | V    |

| ESD CDM                                        | ±500         | v    |

Note:

Stressing the device above the absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating section of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

## 3.2 Thermal characteristics

**Table 5. Thermal characteristics**

| Symbol            | Parameter                                                                      | Value       | Unit |

|-------------------|--------------------------------------------------------------------------------|-------------|------|

| Tj                | Absolute maximum junction temperature                                          | -40 to +150 |      |

| T <sub>JAMR</sub> | Absolute maximum junction temperature                                          | -40 to +160 | °C   |

| TA                | Operating ambient temperature                                                  | -40 to +105 |      |

| ΘJC               | Junction-case package thermal resistance on 2s2p std JEDEC board (JESD51-7)    | 6           | °C/W |

| ӨЈА               | Junction-ambient package thermal resistance on 2s2p std JEDEC board (JESD51-7) | 32          | C/VV |

DS14839 - Rev 2 page 7/127

# 3.3 Consumption in typical application scenarios

STPMIC1L  $V_{IN}$  input current consumption with all supply pins connected to  $V_{IN}$  except  $V_{LDO3IN} = V_{OUT2} = 1.25 \text{ V}$ ,  $V_{IN} = 5 \text{ V}$ ,  $V_{IO} = 3.3 \text{ V}$  from LDO2OUT at  $T_i = +25 \,^{\circ}\text{C}$ , unless otherwise specified.

Table 6. Consumption in typical application scenarios

| Application<br>mode | Application description                                                                                  | Conditions                                                                                                                                                                                                                                                                                             | Тур.   | Unit |

|---------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| OFF                 | AP and peripherals are powered OFF, waiting for a turn-on event to start.                                | PMIC in OFF state.  Turn-on from PONKEYn/EN and I <sup>2</sup> C inactive.  All regulators OFF. GPOx deasserted.                                                                                                                                                                                       | 53 (1) |      |

| STANDBY             | AP is in STANDBY mode (suspend to flash). All peripherals are powered OFF.                               | PMIC in POWER_ON state.  IRQ from any source and PWRCTRLx active.  LDO2 ON, VLDO2OUT = 3.3 V (VDDIO).  All other regulators OFF and GPOx deasserted.  All outputs without load.  No activity on I <sup>2</sup> C.                                                                                      | 110    |      |

| STOP                | AP is in LPLV-STOP1 (Core/CPU on-low voltage) DDR3L is in self-refresh. All peripherals are powered OFF. | PMIC in POWER_ON state.  IRQ from any source and PWRCTRLx active.  BUCK1 ON, VOUT1 = 0.9 V (VDDCORE).  BUCK2 ON, VOUT2 = 1.35 V (VDD_DDR).  LDO2 ON, VLDO2OUT = 3.3 V (VDDIO).  All other regulators OFF.  All outputs without load. No activity on I <sup>2</sup> C.                                  | 370    | μА   |

| RUN                 | Application is in RUN (Core, CPU, on-nominal) DDR3L is running.                                          | PMIC in POWER_ON state.  IRQ from any source and PWRCTRLx active.  BUCK1 ON, VOUT1 = 1.25 V (VDDCORE).  BUCK2 ON, VOUT2 = 1.35 V (VDD_DDR).  LDO3 ON in sink/src (VTT_DDR).  LDO2 ON, VLDO2OUT = 3.3 V (VDDIO).  All other regulators OFF.  All outputs without load. No activity on I <sup>2</sup> C. | 650    |      |

<sup>1.</sup> Current consumption, 100  $\mu$ A max at  $T_j$  = -40 °C to +105 °C.

DS14839 - Rev 2 page 8/127

# 3.4 Electrical and timing parameter specifications

All parameters are specified at  $V_{IN} = V_{BUCKxIN} = V_{LDOxIN} = 5$  V, except  $V_{LDO3IN} = V_{OUT2}$ ,  $V_{OUT1} = 1.25$  V,  $V_{OUT2} = 1.35$  V,  $V_{LDO5OUT} = 3.3$  V,  $V_{LDO2OUT} = 3.3$  V,  $V_{LDO3OUT} = 3.3$  V,  $V_{LDO4OUT} = 3.3$  V,  $V_{LDO2OUT}$ ,  $V_{LDO2OUT} = 0.3$  °C to +125 °C, with recommended BOM, unless otherwise specified.

## 3.4.1 General section

Table 7. Electrical and timing parameter specifications (general section)

| Symbol                  | Parameter                            | Test conditions                                                                                              | Min. | Тур.                           | Max. | Unit |

|-------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------|------|--------------------------------|------|------|

| General secti           | on                                   |                                                                                                              |      |                                |      |      |

| V <sub>IN</sub>         | Input voltage range                  |                                                                                                              | 2.8  | 3.6 or 5                       | 5.5  | V    |

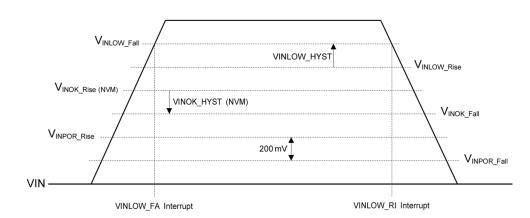

| V <sub>INPOR_Rise</sub> | V <sub>INPOR</sub> rising threshold  |                                                                                                              | 2.2  | 2.3                            | 2.4  | V    |

| V <sub>INPOR_Fall</sub> | V <sub>INPOR</sub> falling threshold |                                                                                                              |      | 2.1                            | 2.2  | V    |

|                         |                                      |                                                                                                              | 3    | 3.1                            | 3.2  |      |

| V <sub>INOK_Rise</sub>  | V <sub>INOK</sub> rising threshold   | Programmable value defined in the NVM register                                                               | 3.2  | 3.3                            | 3.4  | V    |

| *INOK_RISE              | VINOR Horing amounted                | r regionimable value defined in the review register                                                          | 3.35 | 3.5                            | 3.6  |      |

|                         |                                      |                                                                                                              | 3.8  | 4.0                            | 4.1  |      |

|                         |                                      |                                                                                                              |      | 200                            |      |      |

| V <sub>INOK_HYST</sub>  | V <sub>INOK</sub> hysteresis         | Programmable value defined in the NVM register                                                               |      | 300                            |      | mV   |

|                         |                                      |                                                                                                              |      | 400<br>500                     |      |      |

|                         |                                      |                                                                                                              |      |                                |      |      |

| V <sub>INOK_Fall</sub>  | V <sub>INOK</sub> falling threshold  | Defined indirectly by V <sub>INOK_Rise</sub> and V <sub>INOK_HYST</sub>                                      |      | V <sub>INOK_Rise</sub>         |      | mV   |

| VINOK_Fall              | VINOR laming threshold               | settings                                                                                                     |      | V <sub>INOK_HYST</sub>         |      | IIIV |

|                         |                                      | When V <sub>IN</sub> is crossing V <sub>INOK_Fall</sub> , PMIC power-down                                    |      | _                              |      |      |

| tVINOK_Fall             | V <sub>INOK</sub> falling delay      | then cannot restart before t <sub>VINOK_Fall</sub> delay, even if<br>V <sub>IN</sub> >V <sub>INOK_Rise</sub> |      | 100                            |      | ms   |

| V                       | \/ riging throughold                 | Dragrammable value defined in register V                                                                     | +20  | V <sub>INOK_Fall</sub> + 50 to | +80  |      |

| V <sub>INLOW_Rise</sub> | V <sub>INLOW</sub> rising threshold  | Programmable value defined in register V <sub>INLOW_CR</sub>                                                 | +300 | V <sub>INOK_Fall</sub> + 400   | +500 | mV   |

|                         |                                      |                                                                                                              | 90   | 100                            | 110  |      |

| V <sub>INLOW_HYST</sub> | V <sub>INLOW</sub> hysteresis        | Programmable value defined in register V <sub>INLOW CR</sub>                                                 | 180  | 200                            | 220  | mV   |

| VINLOW_HYST             | VINLOW Hysteresis                    | Tregrammable value defined in register vincow_cR                                                             | 270  | 300                            | 330  | 1110 |

|                         |                                      |                                                                                                              | 360  | 400                            | 440  |      |

|                         |                                      | Defined directly by V <sub>INLOW Rise</sub> and V <sub>INLOW HYST</sub>                                      |      | V <sub>INLOW_Rise</sub>        |      |      |

| V <sub>INLOW_Fall</sub> | V <sub>INLOW</sub> falling threshold | settings                                                                                                     |      | +                              |      | mV   |

|                         |                                      |                                                                                                              |      | V <sub>INLOW_HYST</sub>        |      |      |

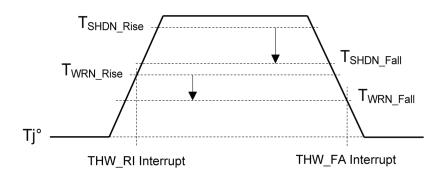

| T <sub>WRN_Rise</sub>   | Warning temperature rising           |                                                                                                              | 115  | 125                            | 135  | °C   |

| T <sub>WRN_Fall</sub>   | Warning temperature falling          |                                                                                                              | 95   | 105                            | 120  | °C   |

| T <sub>SHDN_Rise</sub>  | Shutdown temperature rising          |                                                                                                              | 140  | 150                            | 160  | °C   |

| T <sub>SHDN_Fall</sub>  | Shutdown temperature falling         |                                                                                                              | 105  | 115                            | 130  | °C   |

| t <sub>TSHDN_DLY</sub>  | Shutdown temperature falling delay   |                                                                                                              |      | 3                              |      | s    |

| tocpdb_ldo              | LDO OCP turn-off delay               |                                                                                                              |      | 5                              |      | ms   |

| tocpdb_buck             | BUCK OCP turn-off delay              |                                                                                                              |      | 5                              |      | ms   |

DS14839 - Rev 2 page 9/127

| Symbol                | Parameter                           | Test conditions                            | Min. | Тур.     | Max. | Unit  |

|-----------------------|-------------------------------------|--------------------------------------------|------|----------|------|-------|

| tHICCUP_DLY           |                                     |                                            |      | 0        |      |       |

|                       | History and OFF dates               | Programmable value defined in              |      | 100      |      | mo    |

|                       | Hiccup mode OFF delay               | NVM_BUCKS_IOUT_SHR2 NVM register           |      | 500      |      | ms    |

|                       |                                     |                                            |      | 1000     |      |       |

| 4                     | Watahda a timar                     | Programmable value defined in the register |      | 1 to 256 |      |       |

| t <sub>WD</sub>       | Watchdog timer                      | Timer programming step                     |      | 1        |      | S     |

| NVM <sub>END</sub>    | NVM write cycles endurance          | Recommended maximum writing cycles (1)     |      |          | 10   | Cycle |

| V <sub>NVM_PROG</sub> | NVM min voltage for write operation |                                            | 3.8  |          |      | V     |

<sup>1.</sup> NVM writing procedures must be performed under controlled electrical/environmental values.

DS14839 - Rev 2 page 10/127

# 3.4.2 Digital interface

Table 8. Electrical and timing parameter specifications (digital interface)

| Symbol              | Parameter                                   | Test conditions                                                                                | Min.          | Тур.                      | Max.                      | Unit |

|---------------------|---------------------------------------------|------------------------------------------------------------------------------------------------|---------------|---------------------------|---------------------------|------|

| Digital inter       | face                                        |                                                                                                |               |                           |                           | _    |

| V <sub>IO</sub>     | V <sub>IO</sub> input voltage for IO signal |                                                                                                | 1.7           | 1.8 or 3.3                | 3.6                       | V    |

|                     | PONKEYn/EN input low voltage                |                                                                                                | 0             |                           | 0.3 x V <sub>INTLDO</sub> |      |

| $V_{IL}$            | RSTn, PWRCTRLx input low voltage            |                                                                                                | 0             |                           | 0.3 x V <sub>IO</sub>     | V    |

|                     | SDA, SCL input low voltage                  | I <sup>2</sup> C NXP UM10204 revision 5 compliant (October 2012)                               | 0             |                           | 0.3 x V <sub>IO</sub>     |      |

|                     | PONKEYn/EN input high voltage               |                                                                                                | 0.7 x VINTLDO |                           | V <sub>IN</sub>           |      |

| $V_{IH}$            | RSTn, PWRCTRLx input high voltage           |                                                                                                | 0.7 x VIO     |                           | V <sub>IO</sub>           | V    |

|                     | SDA, SCL input high voltage                 | I <sup>2</sup> C NXP UM10204 revision 5 compliant (October 2012)                               | 0.7 x VIO     |                           | V <sub>IO</sub>           |      |

|                     | PONKEYn/EN input hysteresis                 |                                                                                                |               | 0.1 x V <sub>INTLDO</sub> |                           |      |

| $V_{HYST}$          | RSTn, PWRCTRLx, input hysteresis            |                                                                                                |               | 0.1 x V <sub>IO</sub>     |                           | V    |

|                     | SDA, SCL input hysteresis                   | I <sup>2</sup> C NXP UM10204 revision 5 compliant (October 2012)                               |               | 0.1 x V <sub>IO</sub>     |                           |      |

|                     | RSTn, INTn, GPOx output low voltage         | I <sub>IO</sub> = 4 mA                                                                         | -             |                           | 0.4                       |      |

| V <sub>OL</sub>     | SDA, SCL output low voltage                 | I <sub>IO</sub> = 4 mA, I <sup>2</sup> C NXP UM10204<br>revision 5 compliant (October<br>2012) | -             |                           | 0.4                       | V    |

| V <sub>OH</sub>     | GPOx output high voltage                    | I <sub>IO</sub> = 4 mA                                                                         |               |                           | V <sub>IN</sub> – 0.4     | V    |

| D <sub>-</sub> -    | PWRCTRLx pins pull-down resistor            | Internally connected to GND                                                                    | 60            | 90                        | 140                       | ΚΩ   |

| $R_{PD}$            | PONKEYn/EN pin pull-down resistor           | Internally connected to GND                                                                    | 60            | 100                       | 140                       | ΚΩ   |

| R <sub>PU</sub>     | RSTn, INTn, PWRCTRLx pins pull-up resistor  | Internally connected to V <sub>IO</sub>                                                        | 50            | 80                        | 120                       | ΚΩ   |

|                     | PONKEYn/EN pin pull-up resistor             | Internally connected to V <sub>IN</sub>                                                        | 80            | 120                       | 140                       |      |

| tPONKEYnDB          | PONKEYn/EN pin debounce filter duration     | No debounce filter for EN                                                                      |               | 30                        |                           | ms   |

| t <sub>RSTnAS</sub> | RSTn assertion time (1)                     |                                                                                                | 30            |                           |                           | μs   |

$<sup>1. \</sup>quad \textit{Pulse smaller than $t_{RSTnAS}$ duration. \textit{PMIC RSTn}$ has no debounce filter. \textit{PMIC must detect a pulse equal to or longer than $t_{RSTnAS}$ duration}$

DS14839 - Rev 2 page 11/127

<sup>2.</sup>  $V_{INTLDO} = 1.8 V$

## 3.4.3 LDO2 and LDO5

Table 9. Electrical and timing parameter specifications.

| Symbol                         | Parameter                    | Test conditions                                                                                          | Min. | Тур.               | Max. | Unit  |

|--------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------|------|--------------------|------|-------|

| LDO2, LDO5                     |                              |                                                                                                          |      |                    |      | l     |

| V <sub>LDOIN</sub>             | Main input voltage range     |                                                                                                          | 2.8  |                    | 5.5  |       |

|                                |                              | V <sub>LDOIN</sub> > V <sub>LDOOUT</sub> + V <sub>LDODROP</sub>                                          |      |                    |      | V     |

| V <sub>LDOOUT</sub>            | Output voltage               | Programmable value.                                                                                      |      | 0.9 to 4.0         |      |       |

|                                |                              | Voltage programming step                                                                                 |      | 100                |      | mV    |

|                                |                              | 2.8 V < V <sub>LDOIN</sub> < 5.0 V                                                                       |      |                    |      |       |

| V <sub>LDOOUT</sub> -          | Output voltage accuracy      | V <sub>LDOIN</sub> > V <sub>LDOOUT</sub> + V <sub>LDODROP</sub>                                          | -2   |                    | 2    | %     |

| ACC                            |                              | 100 μA < I <sub>LDOOUT</sub> < 350 mA                                                                    |      |                    |      |       |

|                                |                              | 2.8 V < V <sub>LDOIN</sub> < 5.5 V                                                                       | 50   |                    | 75   |       |

| I <sub>LDOLIM</sub>            | Output current limitation    | I <sub>LDOLIM</sub> programmable in                                                                      | 100  |                    | 150  | mA    |

| ILDOLIM                        | Output current innitation    | NVM_LDOS_IOUT_SHR (Ref.                                                                                  | 200  |                    | 300  | lii/A |

|                                |                              | NVM setting A and B versions)                                                                            | 400  |                    | 600  |       |

|                                |                              | I <sub>LDOOUT</sub> = 0 mA, V <sub>LDOIN</sub> = 5 V                                                     |      |                    |      |       |

| I <sub>LDO2/5Q</sub>           | Total quiescent current      | Measured from the related common input pin, LDO25IN                                                      |      | 9                  |      |       |

| li pooreni i                   |                              | LDO2/5 output disabled                                                                                   |      |                    |      | μΑ    |

| I <sub>LDO2/5IN</sub> _L<br>KG | Input leakage current        | Measured from the related common input pin, LDO25IN                                                      |      | 4 (1)              | 20   |       |

| V <sub>LDODROP</sub>           | Dropout (2)                  | V <sub>LDOOUT</sub> = 2.9 V, I <sub>LDOOUT</sub> = 350 mA                                                |      | 180                | 300  |       |

| V <sub>LDOOUT</sub> -          | Load transient regulation    | $I_{LDOOUT}$ = 1 mA to 180 mA, $t_R$ = $t_F$ =1 $\mu$ s                                                  |      | 35                 |      | mV    |

|                                |                              | V <sub>LDOIN</sub> = 4.5 V to 5 V, t <sub>R</sub> =t <sub>F</sub> =10                                    |      |                    |      |       |

| V <sub>LDOOUT-LI</sub>         | Line transient regulation    | μs,                                                                                                      |      | 10                 |      |       |

|                                |                              | $\Delta I_{LDOOUT} = 0$                                                                                  |      |                    |      |       |

|                                |                              | $\Delta V_{LDOIN}$ = 300 mVPP, f = [0.1:20]<br>kHz, T <sub>j</sub> = 25 °C, I <sub>LDOOUT</sub> = 200 mA |      | 43                 |      |       |

| P <sub>SRRLDO</sub>            | Power supply rejection ratio | $\Delta V_{LDOIN}$ = 300 mVPP, f = [20:100]<br>kHz, T <sub>i</sub> = 25 °C, I <sub>LDOOUT</sub> = 200 mA |      | 37                 |      | dB    |

|                                |                              | 2.8 V < V <sub>LDOIN</sub> < 5.5 V, 0 < I <sub>LDOOUT</sub>                                              |      |                    |      |       |

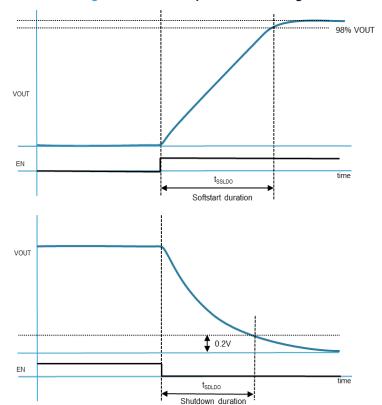

| t <sub>SSLDO</sub>             | Soft-start duration          | < 1 mA                                                                                                   |      | 160 <sup>(3)</sup> |      | μs    |

|                                |                              | $C_{OUT}$ = 4.7 $\mu$ F, $V_{LDOOUT}$ = 3.3 $V$                                                          |      |                    |      |       |

| V                              |                              | 2.8 V < V <sub>LDOIN</sub> <5.5 V, 1.7 V <                                                               |      |                    |      |       |

| V <sub>LDOOUT</sub> -          | Startup overshoot            | V <sub>LDOOUT</sub> < 3.3 V                                                                              |      | 1                  |      | %     |

|                                |                              | I <sub>LDOOUT</sub> < 10 μA                                                                              |      |                    |      |       |

| t <sub>SDLDO</sub>             | Shutdown duration            | Pull-down enabled, V <sub>LDOOUT</sub> = from 3.3 V to 0.2 V, I <sub>LDOOUT</sub> = no load              |      |                    | 1.5  | ms    |

<sup>1.</sup>  $V_{IN} = V_{LDOIN} = 5 \text{ V}, T_j = 25 \text{ }^{\circ}\text{C}$

DS14839 - Rev 2 page 12/127

<sup>2.</sup> Dropout is the smallest difference between a regulator's input and its output voltage, which is required to maintain regulation and enable the regulator to provide rated voltage and current

<sup>3.</sup> Value can be impacted by current limitation and  $V_{OUT}$  and  $C_{OUT}$  values

# 3.4.4 LDO3

Table 10. Electrical and timing parameter specifications (LDO3)

| Symbol                                               | Parameter                                             | Test conditions                                                                                                     | Min.   | Тур.                 | Max.    | Unit             |   |

|------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------|----------------------|---------|------------------|---|

| LDO3 normal m                                        | ode                                                   |                                                                                                                     |        |                      |         |                  |   |

| V <sub>LDOIN</sub>                                   | Main input voltage range                              |                                                                                                                     | 2.8    |                      | 5.5     |                  |   |

|                                                      |                                                       | V <sub>LDOIN</sub> > V <sub>LDOOUT</sub> + V <sub>LDODROP</sub>                                                     |        | 0.9 to 4.0           |         | V                |   |

| $V_{LDOOUT}$                                         | Output voltage                                        | programmable value.                                                                                                 |        | 0.9 10 4.0           |         |                  |   |

|                                                      |                                                       | Voltage programming step                                                                                            |        | 100                  |         | mV               |   |

| V <sub>LDOOUT-ACC</sub>                              | Output voltage accuracy                               | $2.8 \text{ V} < \text{V}_{\text{LDOIN}} < 5.5 \text{ V}, 1.7 \text{ V} < \text{V}_{\text{LDOOUT}} < 3.3 \text{ V}$ | -2     |                      | +2      | %                |   |

| *LDOOUT-ACC                                          | Cutput voltage accuracy                               | 100 μA < I <sub>LDOOUT</sub> < 120 mA                                                                               |        |                      |         | 70               |   |

| I <sub>LDOLIM</sub>                                  | Output current limitation                             | 2.8 V < V <sub>LDOIN</sub> < 5.5 V                                                                                  | 120    |                      | 180     | mA               |   |

| $I_{LDOQ}$                                           | Total quiescent current                               | I <sub>LDOOUT</sub> = 0 mA                                                                                          |        | 7 (1)                | 13      | μA               |   |

| I <sub>LDOIN_LKG</sub>                               | Input leakage current                                 | LDO output disabled, $T_j = 25  ^{\circ}\text{C}$                                                                   |        | 1                    | 3       | μΑ               |   |

| $V_{LDODROP}$                                        | Dropout voltage                                       | $V_{LDOOUT}$ = 3.3 V, $I_{LDOOUT}$ = 100 mA                                                                         |        | 120                  | 200     |                  |   |

| V <sub>LDOOUT-LO</sub>                               | Load transient regulation                             | $I_{LDOOUT}$ = 100 $\mu A$ to 50 mA, $t_R$ = $t_F$ =1 $\mu s$                                                       |        | 20                   |         | mV               |   |

| V <sub>LDOOUT-LI</sub>                               | Line transient regulation                             | $V_{LDOIN}$ = 4.5 V to 5 V, $t_R$ = $t_F$ = 10 $\mu$ s. $\Delta I_{LDOOUT}$ = 0                                     |        | 5                    |         |                  |   |

|                                                      |                                                       | $\Delta V_{LDOIN}$ = 300 mVPP, f = [0.1:20] kHz, T <sub>j</sub> = 25 °C,                                            |        | 45                   |         |                  |   |

| D                                                    | Power supply rejection                                | I <sub>LDOOUT</sub> = 50 mA                                                                                         |        | 45                   |         | ٩D               |   |

| P <sub>SRRLDO</sub>                                  | ratio                                                 | $\Delta V_{LDOIN}$ = 300 mV <sub>PP</sub> , f = [20:100] kHz, T <sub>j</sub> = 25 °C,                               |        | 40                   |         | dB               |   |

|                                                      |                                                       | I <sub>LDOOUT</sub> = 50 mA                                                                                         |        | 40                   |         |                  |   |

| tssldo                                               | Soft-start duration                                   | $2.8 \text{ V} < \text{V}_{\text{LDOIN}} < 5.5 \text{ V}, 0 < \text{I}_{\text{LDOOUT}} < 1 \text{ mA}$              |        | 160 <sup>(2)</sup>   |         | 116              |   |

| SSLDO                                                | Soit-Start duration                                   | $C_{OUT} = 4.7 \mu F, V_{OUT} = 1.8 V$                                                                              |        | 100 (=/              |         | μs               |   |

| $V_{LDOOUT-SO}$                                      | Startup overshoot                                     | $2.8 \text{ V} < \text{V}_{\text{LDOIN}} < 5.5 \text{ V},$                                                          |        | 1                    | 1       |                  | % |

| *LD0001-50                                           | Otartap oversnoot                                     | $1.7 \text{ V} < \text{V}_{\text{LDOOUT}} < 3.3 \text{ V}_{\text{ILDOOUT}} < 10 \mu\text{A}$                        |        | '                    |         | /0               |   |

| tsdldo                                               | Shutdown duration                                     | Pull-down enabled, $V_{LDOOUT}$ = 3.3 V to $V_{LDOOUT}$ = 0.2 V, $I_{LDOOUT}$ = no load                             |        |                      | 1.5     | ms               |   |

| LDO3 sink-sour                                       | ce mode (DDR VTT supply)                              |                                                                                                                     |        |                      |         |                  |   |

| V <sub>LDOIN</sub> =V <sub>OUT6</sub> =<br>specified | 1.35 V, V <sub>IN</sub> = 5.0 V, V <sub>BUCK2II</sub> | $_{ m N}$ = 5.0 V, V <sub>LDOOUT</sub> = V <sub>OUT</sub> 2/2, T <sub>j</sub> = -40 °C to +125 °C, recomb           | mended | I BOM, unl           | ess otl | nerwise          |   |

| V <sub>LDOIN-SS</sub>                                | Input voltage range                                   |                                                                                                                     | 1.1    | 1.2                  | 1.6     | .,               |   |

| V <sub>LDOOUT-SS</sub>                               | Output voltage                                        |                                                                                                                     |        | V <sub>OUT</sub> 2/2 |         | V                |   |

| /LDOOUT-ACC-SS                                       | Output voltage accuracy                               | 1.1 V < V <sub>LDOIN</sub> < 1.6 V, -215 mA < I <sub>LDOOUT</sub> < +215 mA                                         | -1.5   |                      | +1.5    | %                |   |

| I <sub>LDOOUT-SS</sub>                               | Continuous output current                             | 1.1 V < V <sub>LDOIN</sub> < 1.6 V                                                                                  |        |                      | 120     | mA <sub>RM</sub> |   |

| I <sub>LDOLIM-SS</sub>                               | Output current limitation                             | V <sub>LDOIN</sub> = 1.1 V to 5.5 V                                                                                 | ±230   |                      | ±500    | mA               |   |

| I <sub>LDOQ-SS</sub>                                 | Total quiescent current                               | I <sub>LDOOUT</sub> = 0 mA, measured from LDO3IN pin                                                                |        | 4 (1)                | 20      | μA               |   |

| V <sub>LDOOUT-LO-SS</sub>                            | Load transient regulation                             | $I_{LDOOUT} = \pm [0.50] \text{ mA}, t_R = t_F = 250 \text{ ns}$                                                    |        | 30                   |         |                  |   |

| V <sub>LDOOUT-LI-SS</sub>                            | Line transient regulation                             | $V_{LDOIN}$ = $V_{OUT2}$ = 1.35 V ±30 mV, $t_R$ = $t_F$ = 10 $\mu$ s                                                | 5      |                      |         | mV               |   |

| t <sub>SSLDO-SS</sub>                                | Soft-start duration                                   | 1.1 V < $V_{LDOIN}$ < 1.6 V, $ I_{LDOOUT} $ < 1 mA, $C_{OUT}$ = 10 $\mu F$                                          |        | 20                   | 40      | μs               |   |

| t <sub>SU_LDO</sub>                                  | Startup delay (delay before voltage                   | controlled by a PWRCTRLx.                                                                                           |        | 16                   | 20      | μs               |   |

| *30_LDO                                              | starts to rise)                                       | PWRCTRL delay = 0                                                                                                   |        |                      |         | ļ ,              |   |

|                                                      |                                                       |                                                                                                                     |        |                      |         |                  |   |

DS14839 - Rev 2 page 13/127

| Symbol                    | Parameter         | Test conditions                                                                                                |  | Тур. | Max. | Unit |

|---------------------------|-------------------|----------------------------------------------------------------------------------------------------------------|--|------|------|------|

| V <sub>LDOOUT-SO-SS</sub> | Startup overshoot | 1.1 V < V <sub>LDOIN</sub> < 1.6 V, V <sub>LDOOUT</sub> = VOUT2/2, L <sub>DOOUT</sub> = 10<br>μA               |  |      | 4    | %    |

| t <sub>SDLDO-SS</sub>     | Shutdown duration | Pull-down enabled, $V_{LDOOUT} = Vout2/2 \text{ to } V_{LDOOUT} = 0.2 \text{ V, } I_{LDOOUT} = \text{no load}$ |  |      | 1.5  | ms   |

<sup>1.</sup>  $V_{IN} = V_{LDOIN} = 5 V$ ,  $T_j = 25$ °C

## 3.4.5 LDO4

Table 11. Electrical and timing parameter specifications (LDO4)

| Symbol                  | Parameter                                | Test conditions                                                                                      | Min. | Тур.    | Max. | Unit |

|-------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------|------|---------|------|------|

| LDO4                    |                                          |                                                                                                      |      |         |      |      |

| $V_{LDOIN}$             | Main input voltage range                 | $V_{LDOIN}$ from $V_{IN}$                                                                            | 2.8  |         | 5.5  |      |

| V <sub>LDOOUT-ACC</sub> | Output voltage accuracy                  | V <sub>LDOIN</sub> = 3.6 V to 5.5 V<br>100 μA < I <sub>LDOOUT</sub> < 30 mA                          | 3.23 | 3.3     | 3.40 | V    |

| I <sub>LDOLIM</sub>     | Output current limitation                | V <sub>LDOIN</sub> = 3.6 V to 5.5 V                                                                  | 50   | 75      | 200  | mA   |

| I <sub>LDOQ</sub>       | Quiescent current                        | I <sub>LDOOUT</sub> = 0 mA                                                                           |      | 20 (1)  | 25   | μA   |

| V <sub>LDODROP</sub>    | Dropout voltage from V <sub>IN</sub> pin | m V <sub>IN</sub> I <sub>LDOOUT</sub> = 30 mA                                                        |      | 45      | 90   |      |

| V <sub>LDOOUT-LO</sub>  | Load transient regulation                | $I_{LDOOUT}$ = 1 to 30 mA, $t_R$ = $t_F$ =1 $\mu s$                                                  |      | 40      |      | mV   |

| V <sub>LDOOUT-LI</sub>  | Line transient regulation                | $V_{IN}$ = 4.5 V to 5.0 V, $I_{LDOOUT}$ = 0 mA, $\Delta I_{LDOOUT}$ = 0                              |      | 10      |      |      |

|                         | Power supply rejection                   | $\Delta V_{LDOIN}$ = 300 mVPP, f = [0.1:20] kHz, $T_j$ = 25 °C, $_{ILDOOUT}$ = 25 mA                 |      | 55      |      |      |

| P <sub>SRRLDO</sub>     | ratio                                    | $\Delta V_{LDOIN}$ = 300 mVPP, f = [20:100] kHz, T <sub>j</sub> = 25 °C, I <sub>LDOOUT</sub> = 25 mA |      | 40      |      | dB   |

| t <sub>SSLDO</sub>      | Soft-start duration                      | $3.6~V < V_{LDOIN} < 5.5~V,~0 < I_{LDOOUT} < 1~mA,~C_{OUT} = 4.7~\mu F$                              |      | 100 (2) |      | μs   |

| V <sub>LDOOUT-SO</sub>  | Startup overshoot                        | 3.6 V < V <sub>LDOIN</sub> < 5.5 V, I <sub>LDOOUT</sub> <10 μA                                       |      | 1       |      | %    |

| t <sub>SDLDO</sub>      | Shutdown duration                        | Pull-down enabled, $V_{LDOOUT}$ = 3.3 V to $V_{LDOOUT}$ = 0.2 V, $I_{LDOOUT}$ = no load              |      |         | 1.5  | ms   |

<sup>1.</sup>  $V_{IN} = V_{LDOIN} = 3.6 V$ ,  $T_j = 25$ °C.

DS14839 - Rev 2 page 14/127

<sup>2.</sup> Value can be impacted by  $V_{OUT}$  and  $C_{OUT}$  values.

<sup>2.</sup> Value can be impacted by  $C_{OUT}$  values.

# 3.4.6 BUCK1

Table 12. Electrical and timing parameter specifications (BUCK1)

| Symbol                | Parameter                     | V <sub>OUT</sub> range                                            | Test conditions                                                               | Min. | Тур.       | Max.  | Unit |

|-----------------------|-------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------|------|------------|-------|------|

| BUCK1 (LV a           | and HV)                       |                                                                   |                                                                               |      |            |       |      |

| V <sub>BUCKIN</sub>   | Main input voltage range      |                                                                   |                                                                               | 2.8  |            | 5.5   | V    |

|                       |                               | LV                                                                | Programmable value                                                            |      | 0.5 to 1.5 |       | V    |

|                       |                               | LV                                                                | Voltage programming step                                                      |      | 10         |       | mV   |

| V <sub>OUT</sub>      | Output voltage                |                                                                   | V <sub>BUCKIN</sub> > V <sub>OUT</sub> + V <sub>BUCKDROP</sub>                |      | 1.5 to 4.2 |       | V    |

|                       |                               | HV                                                                | Programmable value                                                            |      | 1.5 to 4.2 |       | V    |

|                       |                               |                                                                   | Voltage programming step                                                      |      | 100        |       | m۷   |

| V <sub>OUT-ACC</sub>  | Output voltage error          | LV                                                                | 0.5 V < V <sub>OUT</sub> < 1.5 V                                              | -1.5 |            | 1.5   |      |

| VOUT-ACC              | amplifier accuracy            | HV                                                                | 1.5 V < V <sub>OUT</sub> < 4.2 V                                              | -1.5 |            | 1.5   | %    |

| Vourpeo               | Output load regulation        | HV/LV                                                             | CCM mode                                                                      | -1   |            | 1     | 70   |

| V <sub>OUT-REG</sub>  | (4)                           | HV/LV                                                             | 1 mA < I <sub>OUT</sub> < 1.5 A                                               | -1   |            | •     |      |

|                       |                               | 111/                                                              | 3.0 V < V <sub>BUCKIN</sub> < 5.5 V                                           |      | 40         |       |      |

| V                     | Output voltage ripple         | LV                                                                | 0.5 V < V <sub>OUT</sub> < 1.5 V                                              |      | 10         |       | > (  |

| V <sub>OUT-RIPP</sub> | (2)                           | 107                                                               | 2.8 V < V <sub>BUCKIN</sub> < 5.5 V                                           |      | 15         |       | mVp  |

|                       |                               | HV                                                                | 1.5 V < V <sub>OUT</sub> < 4.2 V,                                             |      | 15         |       |      |

|                       |                               |                                                                   |                                                                               | 500  |            |       |      |

| I <sub>OUT</sub>      | Max output current (4)        |                                                                   | $2.8 \text{ V} < \text{V}_{\text{BUCKIN}} < 5.5 \text{ V}$                    | 1000 |            |       | m/   |

| 1001                  | max output current            |                                                                   | Programmable value in NVM_BUCKS_IOUT_SHR1                                     | 1500 |            |       | 1117 |

|                       |                               |                                                                   |                                                                               | 2000 |            |       |      |

|                       |                               |                                                                   | Depends on NVM_BUCKS_IOUT_SHR1                                                |      | 1.5        |       |      |

| I <sub>BCKLIM</sub>   | Inductor peak current limit   |                                                                   | Max output current steps (0.5 A, 1 A, 1.5 A, 2 A) can                         |      | 2.1        |       | Α    |

|                       | IIIIIL                        | be defined based on the selected inductor per current limit level | be defined based on the selected inductor peak<br>current limit level         |      | 2.8        |       |      |

|                       | Defenses avvitables           |                                                                   |                                                                               |      | 3.3        |       |      |

| f <sub>REFCLK</sub>   | Reference switching frequency |                                                                   |                                                                               |      | 2          |       | MH   |

| I <sub>Q_BCK</sub>    | Total quiescent<br>current    |                                                                   | I <sub>OUT</sub> = 0 mA                                                       |      | 115        | 300   | μA   |

| BUCKIN_LKG            | Input leakage current         |                                                                   | BUCK OFF, T <sub>j</sub> = + 25 °C                                            |      | 0.01       | 1     | μΑ   |

|                       |                               |                                                                   | V <sub>BUCKIN</sub> = 5 V, V <sub>OUT</sub> = 1.25 V, T <sub>J</sub> = +50 °C |      |            |       |      |

|                       |                               |                                                                   | I <sub>OUT</sub> = 10 mA                                                      |      | 81         |       |      |

|                       |                               |                                                                   | I <sub>OUT</sub> = 100 mA                                                     |      | 83         |       | 0,   |

| EFF <sub>BCK</sub>    | Efficiency                    |                                                                   | I <sub>OUT</sub> = 300 mA                                                     |      | 84         |       | %    |

|                       |                               |                                                                   | I <sub>OUT</sub> = 1000 mA                                                    |      | 82         |       |      |

|                       |                               |                                                                   | I <sub>OUT</sub> = 2000 mA                                                    |      | 76         |       |      |

|                       |                               |                                                                   | 3.0 V < V <sub>BUCKIN</sub> < 5.5 V                                           |      |            |       |      |

|                       | Load transient                |                                                                   | 1.2 V < V <sub>OUT</sub> < 1.4 V (typ 1250 mV)                                |      |            |       |      |

| $V_{\text{OUT-LO}}$   | regulation (1)                | LV                                                                | 5 mA < I <sub>OUT</sub> < 1.5 A                                               |      |            | +/-34 | m∨   |

|                       | rogulation                    |                                                                   | $\Delta I_{OUT} = 450 \text{ mA}, t_R/t_F = 1 \mu \text{s}$                   |      |            |       |      |

DS14839 - Rev 2 page 15/127

| Symbol                           | Parameter                                          | V <sub>OUT</sub> range                               | Test conditions                                                                                                                                  | Min. | Тур.              | Max.              | Unit |  |

|----------------------------------|----------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|-------------------|------|--|

|                                  |                                                    |                                                      | 3.0 V < V <sub>BUCKIN</sub> < 5.5 V                                                                                                              |      |                   |                   |      |  |

|                                  | Load transient regulation (1)                      |                                                      | 1.8 V < V <sub>OUT</sub> < 3.3 V                                                                                                                 |      |                   |                   |      |  |

| $V_{\text{OUT-LO}}$              |                                                    | HV                                                   | 5 mA < I <sub>OUT</sub> < 2 A                                                                                                                    |      |                   | 50                | mV   |  |

|                                  |                                                    | $\Delta I_{OUT}$ = 500 mA, $t_R$ = $t_F$ = 1 $\mu s$ |                                                                                                                                                  |      |                   |                   |      |  |

|                                  |                                                    |                                                      | ΔV(in-out)>1.5 V                                                                                                                                 |      |                   |                   |      |  |

| Vou                              | Line transient                                     |                                                      | $\Delta V_{BUCKIN}$ = 600 mV, $t_R$ = $t_F$ = 10 $\mu$ s,                                                                                        |      | 5                 |                   | mV   |  |

| V <sub>OUT-LI</sub>              | regulation                                         |                                                      | I <sub>OUT</sub> = 300 mA, ΔV(in-out) > 1.5 V                                                                                                    |      | 5                 |                   | IIIV |  |

| V                                | Dower up overshoot                                 |                                                      | 2.8 V < V <sub>BUCKIN</sub> < 5.5 V, I <sub>OUT</sub> = 1 mA                                                                                     |      | 10                |                   | m)/  |  |

| V <sub>OUT-OVR</sub>             | Power-up overshoot                                 |                                                      | T <sub>A</sub> = + 25°C, 0.5 V < V <sub>OUT</sub> < 4.2 V                                                                                        |      | 10                |                   | mV   |  |

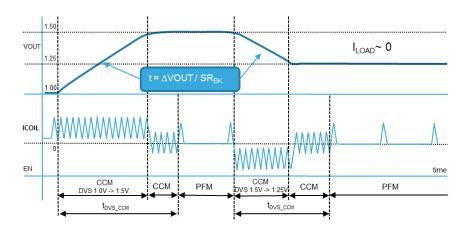

| t <sub>NORM-CCM-</sub>           | Recovery time from                                 |                                                      | V <sub>OUT_Norm</sub> = V <sub>OUT_CCM</sub> ,                                                                                                   |      |                   | 10 (4)            |      |  |

| BCK                              | Normal to Forced<br>CCM mode                       |                                                      | controlled by a PWRCTRLx                                                                                                                         |      |                   | 40 (4)            | μs   |  |

|                                  | Start-up delay (delay                              |                                                      | 2.8 V < V <sub>BUCKIN</sub> < 5.5 V,                                                                                                             |      |                   |                   |      |  |

| tsu_BCK                          | t <sub>SU_BCK</sub> before voltage starts to rise) |                                                      | controlled by a PWRCTRLx                                                                                                                         |      | 25 <sup>(3)</sup> | 40 <sup>(4)</sup> | μs   |  |

|                                  | 0 % 4 4 4 %                                        | LV                                                   |                                                                                                                                                  | 200  |                   | 1500              |      |  |

| t <sub>SS_BCK</sub>              | Soft-start duration                                | HV                                                   |                                                                                                                                                  | 320  |                   | 1500              | μs   |  |

|                                  |                                                    | LV                                                   | Slew rate during start-up                                                                                                                        | 1    |                   | 12.5              |      |  |

|                                  | Output voltage slew                                | HV                                                   | Slew rate during start-up                                                                                                                        | 2.8  |                   | 12.5              | mV/µ |  |

| SR <sub>BCK</sub>                | rate                                               |                                                      | DVS slew rate of a voltage programmed change low to high or high to low, from $V_{OUT}$ = 0.5 V to 1.5 V (LV) or $V_{OUT}$ = 1.5 V to 4.2 V (HV) | 1    | 3.1               |                   | S    |  |

|                                  |                                                    |                                                      | From V <sub>OUT</sub> = 1.5 V to V <sub>OUT</sub> < 0.2 V                                                                                        |      |                   |                   |      |  |

|                                  |                                                    |                                                      | 2.8 V < V <sub>BUCKIN</sub> < 5.5 V, I <sub>OUT</sub> < 1 mA                                                                                     |      |                   |                   |      |  |

|                                  |                                                    | LV                                                   | Slow PD                                                                                                                                          |      |                   | 1.5               |      |  |

| t <sub>SD_BCK</sub> Shutdown dui | Chutalaum dumatia                                  |                                                      | Fast PD                                                                                                                                          |      |                   | 0.3               |      |  |

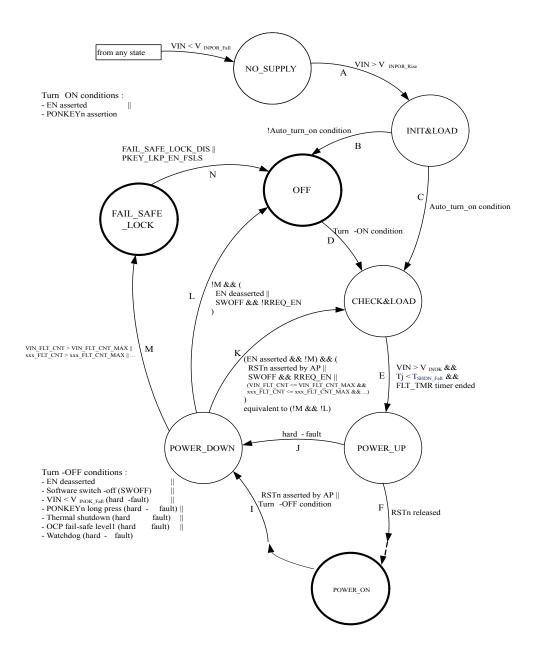

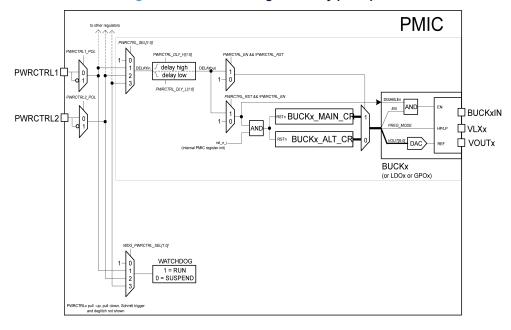

|                                  | Silutuown duration                                 |                                                      | From V <sub>OUT</sub> = 4.2 V to V <sub>OUT</sub> < 0.2 V                                                                                        |      |                   |                   | ms   |  |