# 60 GHz V-band contactless connectivity transceiver with linear-polarization integrated antenna, and tunneling eUSB2, UART, GPIO or I<sup>2</sup>C

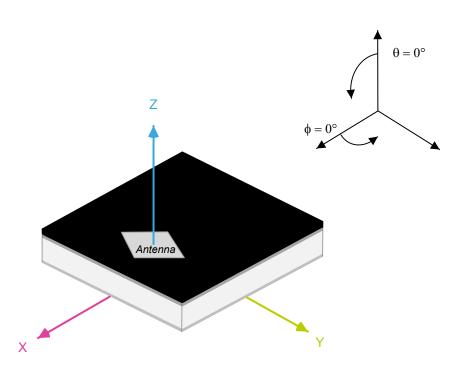

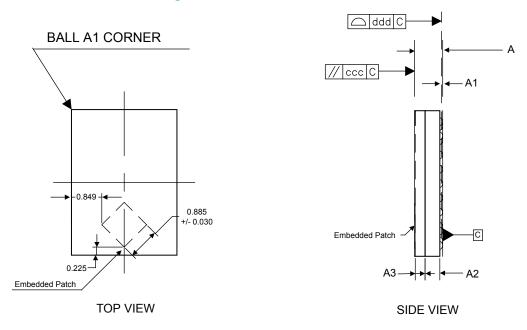

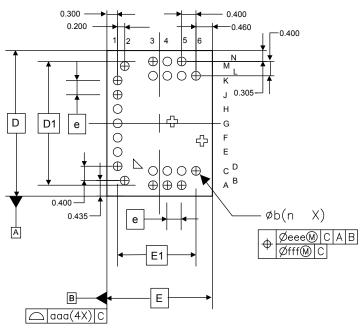

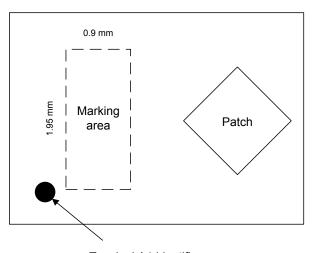

VFBGA23 AiP LP (2.9 mm x 4.1 mm x 0.8 mm)

#### **Features**

- 60 GHz V-Band transceiver for short range contactless connectivity up to 480 Mbit/s

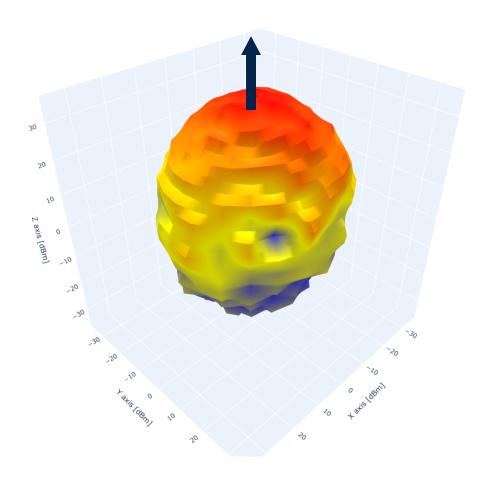

- Compact solution integrating full RF transceiver and dual-linear-polarization antenna, operating in Half-Duplex mode

- RF operational bandwidth: From 60 GHz to 61 GHz

- 42 dB typical total link budget, up to 5 cm free-space propagation loss

- eUSB2, UART, GPIO, or I2C RF tunneling

- Single 1.8 V supply

- Low power consumption (typical values):

- eUSB2 Rx/Tx 110/130 mW

- UART/GPIO/I<sup>2</sup>C 90 mW

- Standby 23 μW

- Optimized BOM without external matching network and clock references. A reference clock may be used at one end of the RF link to comply with specific regional regulation

- Package: VFBGA 2.9 mm x 4.1 mm x 0.8 mm, 23 balls, 0.4 mm pitch

# **Description**

The ST60A3H1 is an RF millimeter-wave transceiver product with a dual-linear-polarization integrated antenna, operating in the 60 GHz V-band from 60 GHz to 61 GHz. The ST60A3H1 has a miniature form factor, optimized bill of materials and low-power operation. The ST60A3H1 is a high-speed RF transceiver compliant with eUSB2, UART, and I²C protocols. The transceiver module contains general-purpose input/outputs (GPIOs) that are also available in tunneling mode. The ST60A3H1 meets the requirements of applications by virtue of its compactness, low-power operation, ease of use and its innovative architecture design for optimized system bill of materials.

## **Applications**

- Contactless test factory automation and after sales services

- Firmware Over-the-Air (FOTA) update

- Contactless data harvesting

- Life proof hole-less personal devices

- Contactless accessories

- Contactless personal equipment docking hub and data transfer

- Industrial contactless connectors

- Board-to-board connection and flex cable replacement

# 1 Introduction

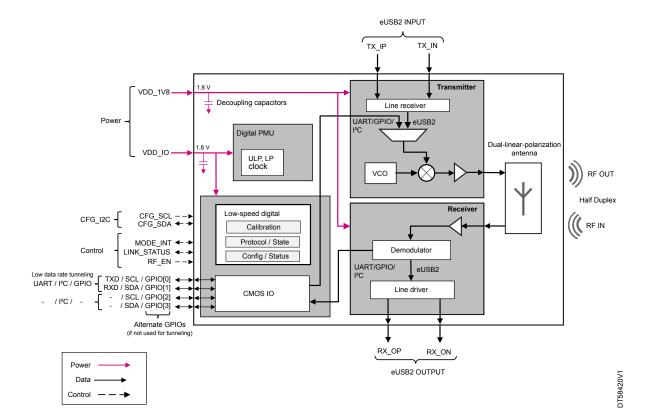

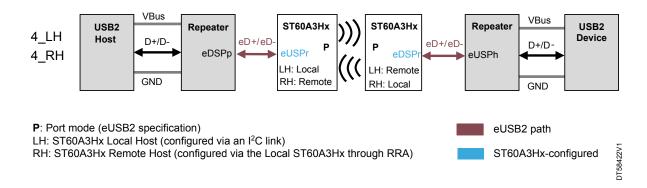

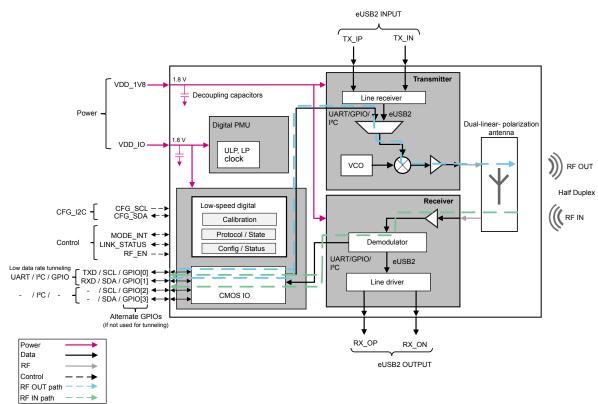

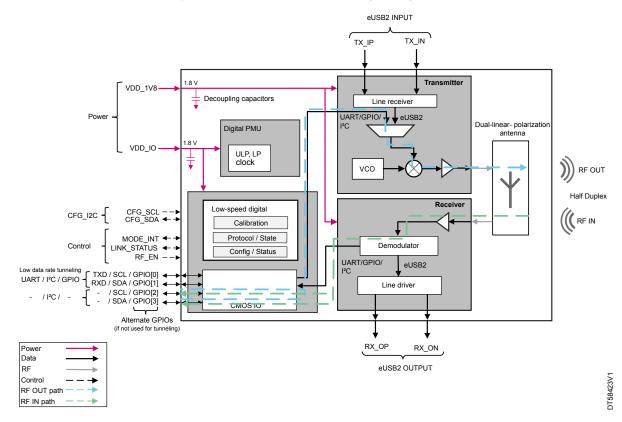

# 1.1 Block diagram

The block diagram in Figure 1 shows a high-level view of the ST60A3H1. For details of the pin functions by usage mode, refer to Section 2: Functional description.

Figure 1. ST60A3H1 block diagram

DS14598 - Rev 4 page 2/74

# 1.2 Acronyms and terms

Table 1. Definition of terms

| Term                        | Definition                                                                                                                     |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| ABB                         | Analog base band                                                                                                               |

| AiP                         | Antenna in package                                                                                                             |

| BER                         | Bit error rate                                                                                                                 |

| CW                          | Continuous wave                                                                                                                |

| CW0, CW1                    | Continuous wave data = 0, continuous wave data = 1                                                                             |

| DC                          | Direct current                                                                                                                 |

| Discovery                   | Process of pairing two ST60A3H1 devices. Achieved during the SEEK phase of the RF_DETECT main FSM state.                       |

| EIRP                        | Effective isotropic radiated power                                                                                             |

| EIS                         | Effective isotropic sensitivity                                                                                                |

| eUSB2                       | Embedded USB2                                                                                                                  |

| FSM                         | Finite state machine                                                                                                           |

| Full detection              | Actively transmitting and listening to pair with an RF partner                                                                 |

| FS                          | eUSB2 full speed                                                                                                               |

| GPIO                        | General-purpose input/output                                                                                                   |

| HS                          | eUSB2 high speed                                                                                                               |

| I <sup>2</sup> C            | Inter-integrated circuit serial communication bus                                                                              |

| Line driver                 | High speed circuit for transmitting the data received over the RF link                                                         |

| Line receiver               | High speed circuit for receiving the data to be sent over the RF link                                                          |

| Link reset                  | Reset over the RF link keeping the configuration                                                                               |

| Link training               | Adjusting the RF receiver parameters to compensate for the channel characteristics                                             |

| LNA                         | Low noise amplifier                                                                                                            |

| Local                       | A locally programmable device partnering with an OTA-configurable device is referred to as the Local partner (see also Remote) |

| LP                          | Low power                                                                                                                      |

| LS                          | eUSB2 low speed                                                                                                                |

| Mastership                  | Having control of OTA/RF link or protocol.                                                                                     |

| MOQ                         | Minimum order quantity                                                                                                         |

| OTA                         | Over the air                                                                                                                   |

| OTP                         | One time programmable (memory)                                                                                                 |

| Passive detection           | Passively listening (only) to pair with an RF partner                                                                          |

| PMU                         | Power management unit                                                                                                          |

| POR                         | Power-on reset (circuitry)                                                                                                     |

| Power-up reset (cold reset) | Full reset including hardware configuration                                                                                    |

| Remote                      | The OTA-configured device is the Remote partner (see also Local)                                                               |

| RRA                         | Remote register access                                                                                                         |

| RSSI                        | Received signal strength indicator                                                                                             |

| SEEK                        | Power optimized search for an RF partner                                                                                       |

| Squelch                     | Suppressing a received signal when below a defined threshold level (eUSB2)                                                     |

DS14598 - Rev 4 page 3/74

| Term      | Definition                                                                                                                                                                 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ST60A3Hx  | Family of ST60A3 RF millimeter-wave transceiver products with or without an integrated antenna                                                                             |

| SW reset  | Warm reset done by software through register programming                                                                                                                   |

| Tunneling | State of a pair of ST60A3H1 devices connected through an RF channel and seamlessly conveying data according to a specific protocol (eUSB2, UART/GPIO, or I <sup>2</sup> C) |

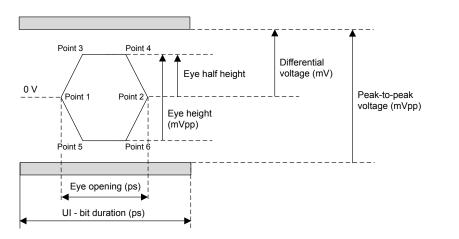

| UI        | Unit interval. UI = 2.08 ns in HS eUSB2                                                                                                                                    |

| ULP       | Ultralow power                                                                                                                                                             |

| VCO       | Voltage controlled oscillator                                                                                                                                              |

# 1.3 Related documents

**Table 2. Document references**

| Number | Reference  | Title                                                                                  |

|--------|------------|----------------------------------------------------------------------------------------|

| [1]    | eUSB2 v1.1 | Embedded USB2 (eUSB2) Physical Layer Supplement to the USB Revision 2.0 Specification. |

| [2]    | USB v2.0   | Universal Serial Bus Revision 2.0 Specification including ECNs and errata.             |

| [3]    | UTMI+ v1.0 | USB 2.0 Transceiver Macrocell Interface Plus (UTMI+) Specification.                    |

| [4]    | ES0650     | ST60A3H1 device errata.                                                                |

DS14598 - Rev 4 page 4/74

# 2 Functional description

This section details the various functional blocks of the ST60A3H1. Refer also to Figure 1. ST60A3H1 block diagram.

#### 2.1 Overview

The ST60A3H1 is a fully integrated transceiver, with a dual-linear-polarization integrated antenna, including full transmit and receive paths, as well as digital control and power management necessary to operate the IC seamlessly into a low footprint application. The I<sup>2</sup>C configuration bus and hardware control pins enable to configure and manage the transitions of the ST60A3H1, which does not require any external RF component.

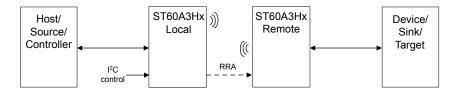

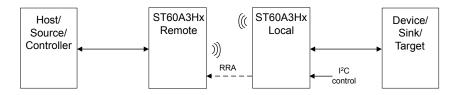

Once its RF is enabled, the ST60A3H1 enters a discovery state during which it looks for a partner. When a partner ST60A3H1 is detected, the RF link is established with optimized parameters, and the two devices enter LOW\_POWER state. In this state, the locally programmable ST60A3H1 device or Local ST60A3H1 is configured by I²C. The partner ST60A3H1 device referred to as the Remote ST60A3H1 is configured either by I²C or overthe-air by the Local ST60A3H1 through Remote register access (RRA). An I²C set of commands sent to the Local device then sets the pair of ST60A3H1 devices into the desired tunneling mode (eUSB2, UART, GPIO or I²C) and data can be transferred.

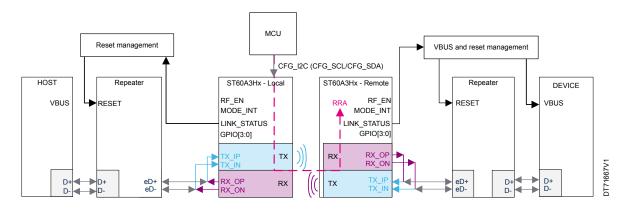

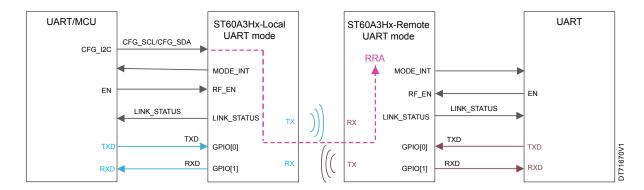

The ST60A3H1 acts as a wireless repeater that seamlessly interfaces for eUSB2, UART, GPIO, and I<sup>2</sup>C protocols. The mastership of any protocol is not correlated with the mastership (Local / Remote) of the RF link. See Figure 2 and Figure 3 below for more details.

Figure 2. ST60A3H1 pair with Local device on Host/Source/Controller side

Figure 3. ST60A3H1 pair with Remote device on Host/Source/Controller side

DT54933V2

DT54934\

DS14598 - Rev 4 page 5/74

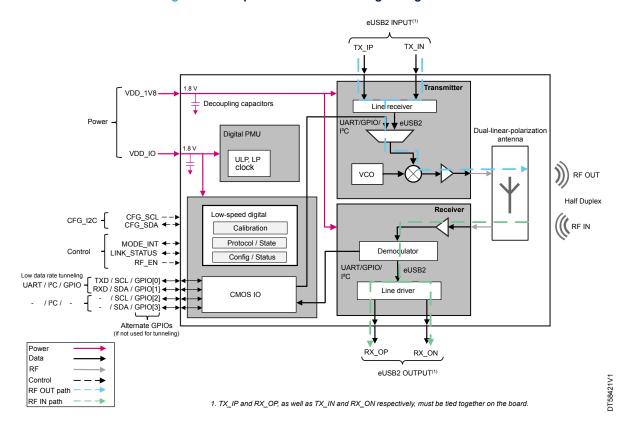

# 2.2 eUSB2 tunneling

eUSB2 tunneling configurations use the TX\_IP, TX\_IN differential pins for data transmission over the RF channel, and the RX\_OP, RX\_ON differential pins for data reception on the RF channel.

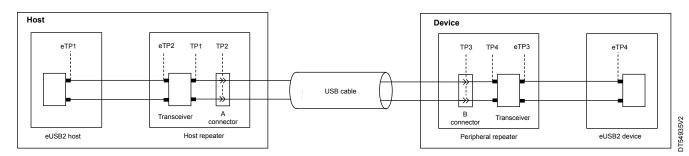

Figure 4 illustrates the data path in eUSB2 tunneling configurations. The four GPIOs that are not used for eUSB2 tunneling can be used as alternate GPIOs.

Figure 4. Data path in eUSB2 tunneling configurations

The electrical characteristics of these lines are configurable:

- DC coupled differential I/Os eUSB2

- Single ended I/Os for eUSB2 Low Speed and Full Speed.

All three eUSB2 speed rates are supported:

- Low Speed (LS) at 1.5 Mbit/s

- Full Speed (FS) at 12 Mbit/s

- High Speed (HS) at 480 Mbit/s

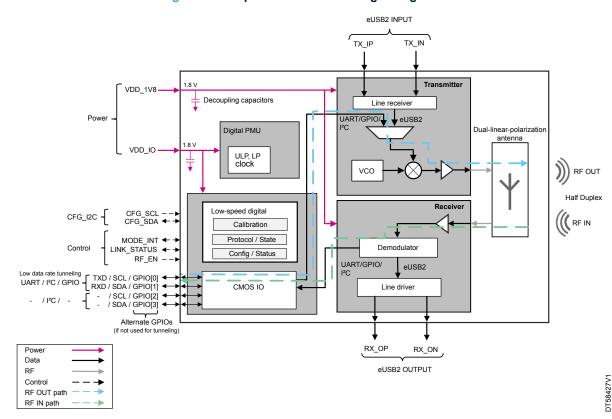

An ST60A3H1 pair, configured to tunnel eUSB2 traffic behaves as an eUSB2 Hybrid Repeater, as defined in appendix B of the eUSB2 specification [1]. A Hybrid Repeater refers to a device hosting an upstream eUSB2 interface and a downstream eUSB2 interface.

Based on the eUSB2 specification [1], a few aspects of the Hybrid Repeater setup that are worth noting are mentioned here: The ST60A3H1 is configured to support the Hybrid Repeater configuration 4, shown below with ST60A3H1 eUSB2 mode (Port only) and eUSB2 port type (eUSPr or eDSPr).

The ST60A3H1 can have two different roles:

- Local Host configured with an I<sup>2</sup>C configuration bus

- Remote Host configured over the air from the Local ST60A3H1.

This leads to the two possible configurations 4 (4\_LH and 4\_RH) presented in Figure 5.

DS14598 - Rev 4 page 6/74

Figure 5. eUSB2 Hybrid Repeater configurations

A typical connection scenario for ST60A3H1 devices configured as an eUSB2 Hybrid Repeater is shown in Figure 6.

Figure 6. ST60A3H1 eUSB2 4\_LH configuration

The main characteristics of the ST60A3H1 eUSB2 implementation are:

- A single ST60A3H1 pair is needed to implement the full eUSB2 channel.

- The ST60A3H1 supports connections to the two eUSB2 port types (eUSPr and eDSPr) as shown in the two possible configurations of Figure 5. eUSB2 Hybrid Repeater configurations.

- The ST60A3H1 implements the 1.2 V Low Speed / Full Speed DC specifications of eUSB2 release 1.1, Table 7-13, setting the supply voltage for eD+ / eD- at a nominal 1.2 V.

The electrical parameters of the High Speed I/Os are provided in Section 5: Electrical characteristics.

As part of a USB2 chain, the ST60A3H1 shows some limitations which may impact the USB2 compliance of the chain. A USB2 system that includes the ST60A3H1 must address these limitations if a USB2 certification is required. See the ST60A3H1 device errata [4] for more detailed information.

DS14598 - Rev 4 page 7/74

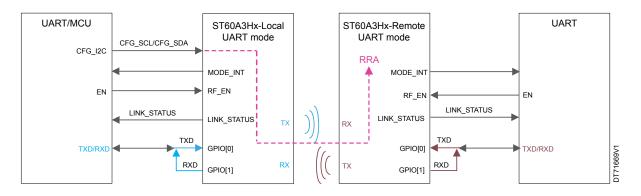

# 2.3 UART tunneling

All UART tunneling configurations rely on the use of CMOS I/Os: GPIO[0] for TXD and GPIO[1] for RXD. The associated logic levels are 0-1.8 V.

Two operating modes are available: Ultralow power (ULP) and Low power (LP). The ULP mode, while offering the lowest power consumption, is limited to a UART maximum data rate of 115200 bit/s, the LP mode supports data rates higher than 115200 bit/s.

The data path is shown in Figure 7. GPIO[2] and GPIO[3] that are not used for UART tunneling can be used as alternate GPIOs.

Figure 7. Data path in UART tunneling configurations

DS14598 - Rev 4 page 8/74

#### 2.3.1 Half-Duplex UART

Half-Duplex UART tunneling allows UART communication supported by a Half-Duplex RF channel:

- RXD and TXD may be connected as shown in Figure 8. In such cases, RXD drive is open drain and relies

on external pull-up resistor.

- It is the application responsibility to ensure that data flow is Half-Duplex.

- Data rate is limited to 6 Mbit/s in LP mode and 115200 bit/s in ULP mode.

Figure 8. ST60A3H1 Half-Duplex UART configuration

Note:

- The Local ST60A3H1 is configured via an I<sup>2</sup>C link

- The Remote ST60A3H1 is configured via the Local ST60A3H1 through RRA.

#### 2.3.2 Full-Duplex UART

Full-Duplex UART (dual simplex is more appropriate) has the following main features:

- Two GPIOs are transferred in opposite directions, offering the direct possibility to plug to a 2-wire UART interface.

- Data rate is limited to 2.4 Mbit/s in LP mode and 115200 bit/s in ULP mode.

Note:

In this setting GPIO[0] is always configured as input (hence connected to the TXD port of a UART interface) and GPIO[1] as output (hence connected to an RXD port of the UART interface). Their roles cannot be switched.

Figure 9. ST60A3H1 Full-Duplex UART configuration

Note:

- The Local ST60A3H1 is configured via an I<sup>2</sup>C link

- The Remote ST60A3H1 is configured via the Local ST60A3H1 through RRA.

DS14598 - Rev 4 page 9/74

# 2.4 GPIO tunneling

The ST60A3H1 can be configured to tunnel one or two GPIOs over the RF channel. GPIO[0] and GPIO[1] are used for this purpose.

The data path is shown in Figure 10. GPIO[2] and GPIO[3] that are not used for GPIO tunneling can be used as alternate GPIOs.

Figure 10. Data path in GPIO tunneling configurations

DT585

DS14598 - Rev 4 page 10/74

RXD1

# 2.4.1 Single-direction GPIO tunneling

Single-direction GPIO tunneling allows data transfer through two GPIOs *in the same direction*, as shown in Figure 11. Some differences between this configuration and the other GPIO tunneling modes are listed below:

- Up to two GPIOs can be transferred (in the same direction).

- Data modulation is optimized leading to a power-efficient solution.

- Only the LP mode is supported. The ULP mode is not available.

- There is no preferred default value, although 1 is the value at power-up reset.

The maximum data rate depends on the number of GPIOs being transferred, and whether the traffic is balanced or unbalanced in the case of two GPIOs. See Table 24. Link parameters for GPIO tunneling.

ST60A3Hx-Local ST60A3Hx-Remote SOURCE/MCU SINK CFG\_SCL/CFG\_SDA CFG\_I2C RRA MODE INT MODE INT RF EN ΕN RF EN FΝ LINK STATUS LINK STATUS LINK\_STATUS LINK\_STATUS RX GPIO[0] RXD0 GPIO[0]

ΤX

GPIO[1]

Figure 11. ST60A3H1 single-direction GPIO configuration

Note:

- The source of the GPIO link is shown here on the ST60A3H1 Local side, though it could also be on the ST60A3H1 Remote side.

- The Local ST60A3H1 is configured via an I<sup>2</sup>C link.

- The Remote ST60A3H1 is configured via the Local ST60A3H1 through RRA.

GPIO[1]

#### 2.4.2 Bidirectional GPIO tunneling

TXD

LP and ULP bidirectional GPIO tunneling configurations are identical to LP and ULP Full-Duplex UART. See Section 2.3.2: Full-Duplex UART.

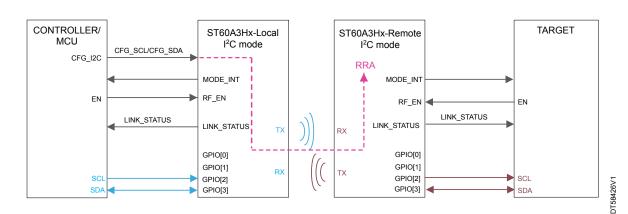

# 2.5 I<sup>2</sup>C tunneling

The ST60A3H1 can be configured to tunnel an I<sup>2</sup>C bus over the RF channel. This must not be confused with the I<sup>2</sup>C configuration port, which is used to configure the device, and under certain considerations, the partner ST60A3H1 device.

I<sup>2</sup>C tunneling wired interface can be multiplexed onto GPIO[0] and GPIO[1], or GPIO[2] and GPIO[3]. Note that it is possible to carry out the tunneling on GPIO[0] and GPIO[1] on one of the two devices, and on GPIO[2] and GPIO[3] on the other.

The data path is shown in Figure 12. The two GPIOs that are not used for I<sup>2</sup>C tunneling can be used as alternate GPIOs.

Note:

Figure 12. Data path in I<sup>2</sup>C tunneling configurations and Figure 13. ST60A3H1 I<sup>2</sup>C configuration show typical configurations with GPIO[2] and GPIO[3] being selected on both devices.

DS14598 - Rev 4 page 11/74

Figure 12. Data path in I<sup>2</sup>C tunneling configurations

A typical configuration (Local as I<sup>2</sup>C controller) is shown in Figure 13.

Figure 13. ST60A3H1 I<sup>2</sup>C configuration

Note:

- The Local ST60A3H1 is configured via an I<sup>2</sup>C link

- The Remote ST60A3H1 is configured via the Local ST60A3H1 through RRA.

DS14598 - Rev 4 page 12/74

The main features of the ST60A3H1 in I<sup>2</sup>C tunneling configuration are:

- A single pair of ST60A3H1 devices implement the I<sup>2</sup>C tunnel

- Supported I<sup>2</sup>C bus speeds: Standard mode, Fast mode, and Fast mode plus at 1 Mbit/s

- 7 and 10-bit addresses

- Supports repeated start condition

- Single controller to multiple target connections:

- The ST60A3H1 connected to the I<sup>2</sup>C controller supports a unique controller.

- The ST60A3H1 connected to the target side can support several devices.

- The target peripheral connected to the ST60A3H1 is not allowed to stretch the clock, regardless of the bus speed.

# 2.6 System control and functional input/outputs

# 2.6.1 I/O multiplexing

The ST60A3H1 input/output multiplexing depends on the protocol in use. There can be up to four configurable alternate GPIOs identified as ALT in the Table 3. Functional I/O multiplexing. Configurable GPIOs are detailed in Section 2.6.2: Alternate GPIOs.

Table 3 lists the multiplexing of each I/O per protocol. The detailed usage of each and every implemented protocol is detailed in dedicated chapters.

DS14598 - Rev 4 page 13/74

| Tunneling mode                                      | CFG_SCL                | CFG_SDA                | GPIO[0]               | GPI0[1]               | GPI0[2]               | GPI0[3]               | MODE_INT  | LINK_STATUS    | RF_EN           | TX_IN,<br>TX_IP                 | RX_ON,<br>RX_OP |

|-----------------------------------------------------|------------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------|----------------|-----------------|---------------------------------|-----------------|

| eUSB2                                               |                        |                        | ALT[0] <sup>(2)</sup> | ALT[1] <sup>(2)</sup> | ALT[2] <sup>(2)</sup> | ALT[3] <sup>(2)</sup> | Interrupt |                | 0: OFF<br>1: ON | Diff and SE I/Os <sup>(3)</sup> |                 |

| UART                                                |                        |                        | TXD                   | RXD                   | ALT[2] <sup>(2)</sup> | ALT[3](2)             |           | RF link status |                 | -                               | -               |

| GPIO                                                | CFG_SCL <sup>(1)</sup> | CFG_SDA <sup>(1)</sup> | GPIO[0]               | GPIO[1]               | ALT[2] <sup>(2)</sup> | ALT[3](2)             |           |                |                 | -                               | -               |

| I <sup>2</sup> C                                    |                        |                        | SCL                   | SDA                   | ALT[2] <sup>(2)</sup> | ALT[3](2)             |           |                |                 | -                               | -               |

| I <sup>2</sup> C with alternate pins <sup>(4)</sup> |                        |                        | ALT[0] <sup>(2)</sup> | ALT[1] <sup>(2)</sup> | SCL                   | SDA                   |           |                |                 | -                               | -               |

<sup>1.</sup> Pull-up resistors must be provided externally on the  $I^2C$  bus.

<sup>2.</sup> ALT indicates a GPIO usable for applicative purpose and configurable through  $I^2C$  and OTA interface.

<sup>3.</sup> Differential and single-ended I/Os.

<sup>4.</sup> I<sup>2</sup>C tunneling can be directed to GPIO[0] and GPIO[1], or GPIO[2] and GPIO[3]. Pull-up resistors must be provided externally on the I<sup>2</sup>C tunneled bus.

#### 2.6.2 Alternate GPIOs

The function of each alternate GPIO is determined by register programming either through the programming interface, or through Remote programming via RRA.

Alternate GPIOs can be configured as input or output.

GPIO[2] and GPIO[3] are software controllable in all operating and configuration modes but I<sup>2</sup>C mode with alternate pins (see Section 2.6.1: I/O multiplexing).

When not used by the functional mode, GPIOs are controlled through configuration registers.

When used by the tunneling protocol, GPIOs are directly driven by the ST60A3H1 state machine. Upon leaving the tunneling mode, GPIOs revert to the state defined by their configuration.

# 2.7 Resets

The ST60A3H1 has several reset levels in order to adapt to different application constraints and needs. The reset levels are as follows:

- Power-up or cold reset

- SW Reset (or warm reset) through register programming

- Entry into RF IDLE state through pin RF EN

- Link reset through register programming or RF loss

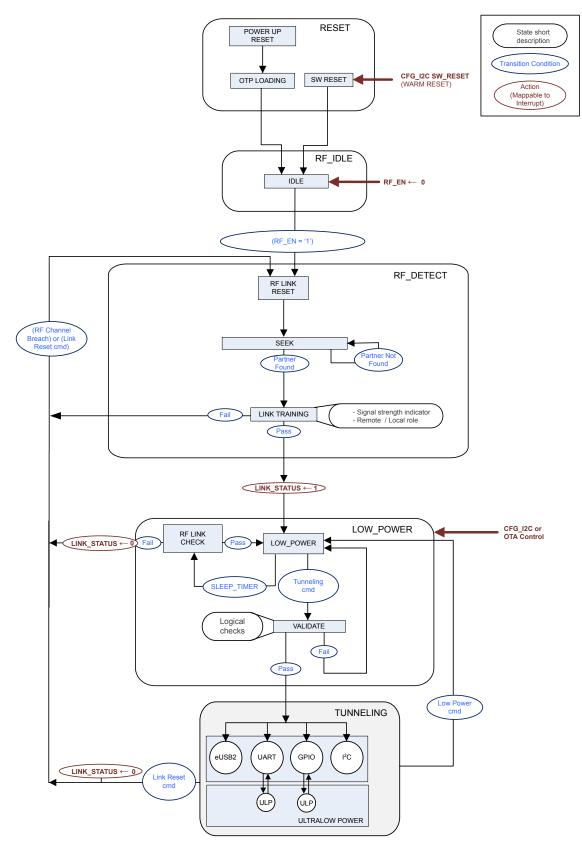

The various reset levels are detailed in the following subsections and summarized in Figure 14.

DS14598 - Rev 4 page 15/74

RESET POWER UP RESET POWER UP OTP LOADING SW RESET CFG\_I2C SW\_RESET ← 1 RF\_IDLE **IDLE**  $RF\_EN \leftarrow 0$ (RF\_EN = '1') RF\_DETECT 1 → CFG\_I2C LINK\_RESET RF\_DETECT INIT LINK\_RESET To RF\_DETECT sub states, Loss of RF channel from any then LOW\_POWER state functional state

Figure 14. ST60A3H1 reset levels

# 2.7.1 Power-up or cold reset

Power-up reset (also referred to as cold reset), is the most comprehensive reset function. It configures the ST60A3H1 through the following steps:

- 1. Power supply is applied.

- 2. All registers are reset.

- 3. OTP memory is read back and loaded into nonresettable registers (shadow registers).

- 4. Register initialization.

DT

DS14598 - Rev 4 page 16/74

#### 2.7.1.1 **Supplies**

The two supplies VDD\_1V8 and VDD\_IO must be tied together on the application board.

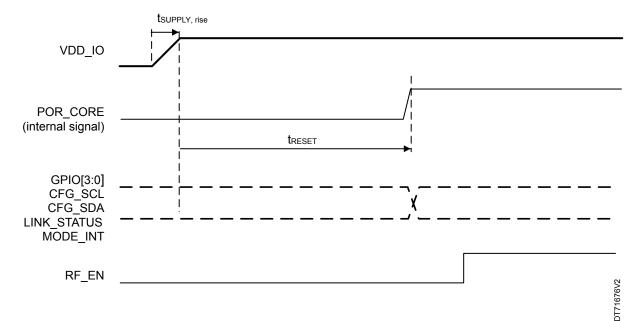

Power on triggers an internal reset after t<sub>RESET</sub>. Power shutdown also triggers an internal reset. VDD\_IO (or respectively VDD\_1V8 since tied together) rising (t<sub>SUPPLY, rise</sub>) and falling (t<sub>SUPPLY, fall</sub>) must respect minimum and maximum timings, defined in Table 8. Reset, ThS and magnetic flux.

The  $I^2C$  configuration interface, as well as the other I/Os except RF\_EN, can be accessed at least  $t_{RESET}$  after VDD\_IO has settled (see Figure 15).

The RF\_EN pin is a switch that activates (or disables) the RF link. By default, its pull-up resistor feature is enabled after reset. It is described in Section 2.7.3: Entry into RF\_IDLE state and can be raised t<sub>RESET</sub> after VDD\_IO has settled (unless it is tied to VDD\_IO, see next).

Some applications require that the device remains always active. Such a requirement is fulfilled by ensuring that the RF\_EN pin is tied to VDD\_IO.

Figure 15. Power on reset and I/Os access

### 2.7.1.2 OTP

At power up, the OTP memory is read-back and loaded into shadow registers.

DS14598 - Rev 4 page 17/74

#### 2.7.1.3 Power-up reset

All digital I/Os, including LINK\_STATUS, are configured as input pins at power-up (refer to the note related to the LINK\_STATUS pin in Section 2.8.3.3: LINK\_STATUS – entry into LOW\_POWER state).

In the absence of physical connections to digital I/Os on the application board, in other words, if any of the pins are left unconnected, internal pull-up and pull-down resistors ensure that the ST60A3H1 boots in a default configuration (see Table 4. Default configuration).

**Table 4. Default configuration**

| Configuration          | CFG_SCL | CFG_SDA | GPIO[0] | GPIO[1] | GPIO[2] | GPIO[3] | MODE_INT | LINK_STATUS |

|------------------------|---------|---------|---------|---------|---------|---------|----------|-------------|

| Default <sup>(1)</sup> | 1       | 1       | 1       | 1       | 1       | 1       | 0        | 0           |

1. Configuration with all '1' is forbidden.

After power-up (cold) reset, the ST60A3H1 boots by default into the following configuration mode:

- Remote role

- Passive detection in RF\_DETECT state

For a Local role with Full detection, the ST60A3H1 must be reconfigured while in RF IDLE state.

#### 2.7.1.4 Register initialization

On exiting cold reset, most registers are initialized to their reset value, others are initialized from shadow registers loaded from OTP.

Note: Software reset behaves similarly in this respect.

#### 2.7.2 Software reset

The ST60A3H1 can be reset without having to perform a power-down/power-up cycle. This is referred to as *warm* or *software reset* (SW\_RESET).

A software (or warm) reset can only be triggered through the I<sup>2</sup>C configuration interface. All state machines and configuration registers are reset to their default values. A software reset does not reload the content of the OTP memory (shadow registers are not reset). All other registers are reinitialized. As a result, the ST60A3H1 is reset to its default configuration mode: Remote role with Passive detection.

The software reset is triggered after the I<sup>2</sup>C transaction has completed to avoid I<sup>2</sup>C interface deadlocks.

Note: The application must not send any transaction on the  $I^2$ C configuration interface for 80  $\mu$ s after a SW\_RESET.

# 2.7.3 Entry into RF\_IDLE state

RF\_IDLE state is entered either from a power-up or software reset, or after setting the RF\_EN pin low. Entering RF\_IDLE terminates the RF link, if any, and resets any ongoing tunneling state machine. In RF\_IDLE state the I²C configuration interface is available, but no over-the-air (OTA) accesses are possible since the RF channel is disabled.

RF\_IDLE state exits when the RF\_EN is set high.

For devices wired as always-active (see Section 2.7.1.1: Supplies), RF\_IDLE state is simply a transition state coming from power-up or software reset that is exited immediately.

Entering RF\_IDLE by toggling RF\_EN low resets some of the registers and forces LINK\_STATUS low.

Note:

- 1. If RF\_IDLE state is entered by toggling RF\_EN low, a wait window of at least SLEEP\_TIMER time must be inserted before the next rising edge of RF\_EN to ensure that RF\_EN = 0 is sampled outside of any potential SLEEP phase.

- 2. The RF\_EN pin has an internal pull-up resistor enabled by default. For optimal power consumption in RF\_IDLE state, which is the lowest power state available when RF\_EN is driven low, the pull-up resistor must be disabled through register programming.

DS14598 - Rev 4 page 18/74

#### 2.7.4 Link reset

An *RF link reset* resets all internal state machines and the corresponding status registers without affecting any configuration registers.

There are two ways to achieve an RF link reset:

- With control registers. This can be done in LOW\_POWER or TUNNELING states. This must be done by

precisely following the procedure below:

- 1. Disable SLEEP\_TIMER

- 2. Wait (SLEEP\_TIMER + 1) x 12 ms

- 3. Issue the LINK\_RESET

- 4. Enable SLEEP\_TIMER

- Broken RF link. The ST60A3H1 periodically checks the RF link integrity when the device is in LOW\_POWER state and during idle periods in TUNNELING state. A breach in the RF connection triggers the devices to re-initialize the RF link.

Whenever a link reset occurs, the interrupt signal, EVT\_LINK\_DISABLED, goes high and the LINK\_STATUS output pin is driven low.

Note:

A SW LINK\_RESET applied outside of LOW\_POWER or TUNNELING states delays the effect of LINK\_RESET until entry into LOW\_POWER state. For instance, a LINK\_RESET command while in RF\_IDLE state is delayed until after RF\_DETECT has completed. A new entry into RF\_DETECT state then takes place.

#### 2.8 Finite state machine

The ST60A3H1 main state machine consists of the following states:

- RESET

- RF IDLE

- RF\_DETECT

- LOW POWER

- TUNNELING states (one per supported protocol)

RESET is described in Section 2.7: Resets.

TUNNELING states are described in the sections dedicated to tunneling modes.

The state machine diagram is detailed in Figure 16.

DS14598 - Rev 4 page 19/74

Figure 16. ST60A3H1 state machine

DT 55314\

DS14598 - Rev 4 page 20/74

#### 2.8.1 RESET state

See Section 2.7: Resets for a complete description.

# 2.8.2 RF\_IDLE state

RF IDLE state serves the following purpose:

- The ST60A3H1 registers are fully accessible for their respective supported mode (read only, read/write or write only).

- It can be skipped by ensuring that the RF\_EN pin is tied to VDD\_IO (always active device). This is however an option only available for a Remote device. For a Local device, RF\_EN must be controlled for configuration purposes.

- All states eventually return to RF\_IDLE state when RF\_EN = 0.

- Power consumption is very limited as all analog and RF blocks are disabled. Optimal power consumption is obtained by disabling the pull-up resistor on the RF EN pin through register programming.

The transition from RF\_IDLE to RF\_DETECT state is ensured by setting RF\_EN = 1. Refer to Section 2.7.3: Entry into RF\_IDLE state for details on the RF\_EN pin.

#### 2.8.3 RF\_DETECT state

RF\_DETECT phases are the following:

- RF LINK RESET

- All internal state machines are reset. Configuration registers, and possible error reports are kept unchanged.

- If RF\_DETECT is re-entered after an error such as loss of RF link, insufficient RF link quality or an

error during a previous pairing attempt, the RF detection procedure is repeated indefinitely.

- SEEK

- This is the actual power optimized search for an RF partner (see Section 2.8.3.1: SEEK phase)

- The SEEK state loops until an RF partner has been found.

- LINK TRAINING

- Once an RF partner has been found, LINK TRAINING is entered for optimal RF link budget.

- The two RF partners exchange internal configuration parameters such as Remote or Local role.

- This phase can lead to an aborted connection.

LINK\_STATUS is raised on exiting RF\_DETECT and entering LOW\_POWER state. EVT\_LINK\_ENABLED replicates LINK\_STATUS (see Section 3: Interrupts and errors).

#### 2.8.3.1 SEEK phase

This section describes the procedure implemented by the ST60A3H1 when searching for an RF partner.

The schemes implemented by the ST60A3H1 for the initial discovery aim at achieving the best power consumption / connection time compromise. Whenever possible most parts of the device are switched off outside specific periods. The parameters driving the initial discovery are configurable with default values such that the average consumption during the detection phase is around a few tens of  $\mu A$  and the average detection time is in the order of 0.5 seconds.

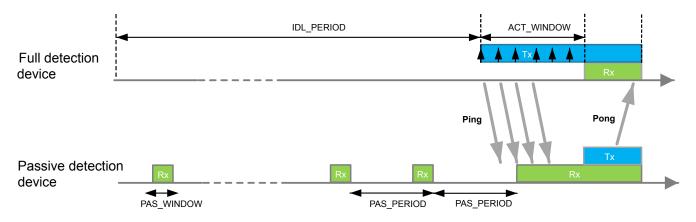

There are two ways of performing initial discovery in RF\_DETECT state:

- Full detection

- Passive detection

Pairing is only possible with one device in Full Detection and the other in Passive Detection. The Passive detection is selected by default for a Remote device at power-up reset. For a Local device with Full detection, the ST60A3H1 must be reconfigured (see Section 2.7.1.3: Power-up reset).

The initial discovery is based on periodic time frames, with the aim of switching off all possible parts of the devices outside active seeking periods.

DS14598 - Rev 4 page 21/74

Figure 17. Full and Passive detections

IDL\_PERIOD: Window during which no active detection takes place

ACT\_WINDOW: Activity window during which Full detection device pings candidate partners PAS\_WINDOW: Window during which Passive detection device seeks for candidate partners

PAS\_PERIOD: Periodicity of passive search

#### **Full detection**

In Full detection, the ST60A3H1 alternates idle periods and active seeking periods.

During idle periods, the device cannot detect a potential RF partner. During active seeking periods, the device periodically transmits messages and listens for the possible reply of a detected RF partner at the end of the period.

- Idle periods:

- This phase covers a time window defined as the IDL\_PERIOD (1000 ms).

- Active periods:

- The ST60A3H1 sends periodic ping messages for relatively long periods referred to as the ACT\_WINDOW (125 ms).

- The prospective partner is informed of the end of the active period. In the case of a hit, the newly found partner acknowledges the detection (pong message).

The periodicity of the Full detection scheme is equal to IDL\_PERIOD + ACT\_WINDOW.

DS14598 - Rev 4 page 22/74

#### **Passive detection**

In Passive detection, the ST60A3H1 periodically turns on the RF Receiver path to detect a potential RF partner.

- Eavesdropping periods:

- Rx is briefly turned on for a duration PAS\_WINDOW (4 μs). Rx activity is repeated with a period corresponding to PAS\_PERIOD (100 ms). PAS\_PERIOD is set to a slightly smaller value than ACT\_WINDOW to ensure that the active and eavesdropping intervals overlap.

- If a partner is detected, the ST60A3H1 acknowledges the detection.

The ST60A3H1 is not allowed to send any ping messages. It only eavesdrops potential connecting partners and acknowledges when found. This allows for an extremely power efficient solution, provided the application ensures that the potential partner is set for Full detection.

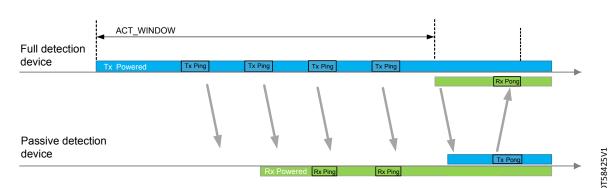

A close-up view of the active window and actual pairing is shown in Figure 18.

Figure 18. Close-up view of pairing phase

DS14598 - Rev 4 page 23/74

#### 2.8.3.1.1 Power consumption and detection time

For a given average detection time, the power consumption optimization is a tradeoff to limit the consumption of the Passive detection device, while limiting the adverse effect on the consumption of the Full detection device. This is achieved by balancing the power consumption due to activity periods (PAS\_WINDOW) and idle periods (PAS\_PERIOD - PAS\_WINDOW) in the Passive detection device. This may be appropriate if one of the two devices has more stringent battery constraints than the other.

#### 2.8.3.2 LINK TRAINING phase

#### 2.8.3.2.1 Signal strength indicator

The link training phase optimizes the internal parameters of the internal receiver parameters of the two partners, with respect to the actual transmitted power and RF path loss.

Its duration is limited and expected to remain less than 200 µs.

The outcome of this phase provides an estimation of the power of the received signal, more commonly called the received signal strength indicator (RSSI). If the signal level is too small, an RSSI\_ERROR interrupt is set.

Note: Insufficient signal strength during this phase may lead the communication to fail, trigger a link reset and report an RF\_DETECT\_ERROR.

#### 2.8.3.2.2 Output-power temperature compensation

Link training is carried out without accounting for the actual temperature and effects on the transmitted power. When link training takes place near the limit of the operating temperature range and temperature compensation of the output power is disabled in LOW\_POWER or TUNNELING states, the optimization of the receiver parameters becomes insufficiently accurate to guarantee a correct jitter and BER. To overcome this issue, the following actions must be performed (see also Section 2.10: Temperature compensation):

- Enable the output-power temperature compensation in LOW POWER

- Before entering TUNNELING, force a LINK RESET

- Enter TUNNELING after returning to LOW\_POWER.

#### 2.8.3.2.3 Logical checks

During the link training phase, the two ST60A3H1 devices exchange the contents of a few configuration registers to inform them of their partner's status and capability. This information embeds the control for over-the-air (OTA) transfers, also referred to as Remote or Local role.

This phase may fail in the case of conflict over the mastership of the OTA link, thus leading to RF\_LINK reset and ERROR report (see Section 3: Interrupts and errors).

#### 2.8.3.3 LINK STATUS – entry into LOW POWER state

Once the two partners have established the RF link, a dedicated status bit is set and the LINK\_STATUS pin is raised. The link is considered up-and-ready when:

- · Two partners have identified each other as a result of SEEK phase

- LINK TRAINING phase has completed successfully

- The two partners have informed each other of their role (Local, Remote) in the OTA connection, and found no incompatibility.

Two devices with the same role (two Local or two Remote devices) report an error.

Until an active tunneling mode is entered, the RF link mastership role is held by the device set for Full detection, the other device being set for Passive detection.

LINK\_STATUS remains high until a disconnection is forced or detected. Nevertheless, the RF link may be breached some time before the ST60A3H1 becomes aware that the link is broken. Disconnection detection occurs:

- When failing to resume the link upon waking-up from a low power state

- When failing to receive an acknowledgement of the RF partner at intervals specified by the protocol in use in low power states (RF LINK CHECK in LOW\_POWER state for instance – see Figure 16. ST60A3H1 state machine).

- When directed to disconnect by the protocol in use

- When directed to disconnect by means of the control interface (RF\_EN)

- On forced LINK\_RESET or SW\_RESET (warm reset) through the I<sup>2</sup>C configuration interface

DS14598 - Rev 4 page 24/74

Successful entry into LOW POWER state raises EVT LOW POWER.

#### LINK STATUS de-assertion due to loss of RF signal

In RF\_DETECT state, there are several retries during pairing. These retries do not affect LINK\_STATUS, because LINK\_STATUS remains low until the FSM reaches the LOW\_POWER state.

In LOW\_POWER state, LINK\_STATUS is de-asserted after a maximum of SLEEP\_TIMER + WATCHDOG\_TIMER.

In TUNNELING state, LINK\_STATUS is de-asserted after a period that depends on the implemented protocol. This is explained in Section 2.9: Sleep timer, Watchdog timer, and high-level Watchdog timer.

Note:

LINK\_STATUS defaults to an input pin with a weak pull-down at reset (see Section 2.7.1: Power-up or cold reset). After reset, and until an RF link is established, it is actively driven low. It is actively driven high when exiting RF\_DETECT and entering LOW\_POWER state. It remains high as long as the RF link is alive.

#### 2.8.4 LOW\_POWER state

LOW\_POWER is the central state once an RF channel has been set, and is the entry point into any of the tunneling modes that the application supports.

LOW POWER is particularly suitable for:

- Reading from and writing to registers of the Remote partner Over-The-Air, a feature referred to as Remote register access (RRA);

- Configuring and entering the tunneling mode.

These two important features are described respectively in Section 2.8.4.1: Over-the-air remote register access (RRA) and Section 2.8.4.5: Entry into TUNNELING state.

When no activity is required due to an RRA or a pending command to enter a tunneling mode, the RF channel enters a SLEEP sub-state with extremely efficient power consumption. The entry into SLEEP and WAKE-UP are also described in Section 2.8.4.2: SLEEP, WAKE-UP and HOUSEKEEPING phases.

#### 2.8.4.1 Over-the-air remote register access (RRA)

It is possible to read and write the registers of the Remote RF partner over the RF link.

After partnering has occurred with another ST60A3H1, the two partnered devices exchange messages across the RF link. The messaging service also allows write or read requests to be pushed across the RF, so that the registers of the RF partner can be remotely read from and written to. RRA accesses are limited to LOW\_POWER state.

In practice, write operations are performed by pushing an 8-bit address and an 8-bit data across the RF link. Read operations are performed indirectly: the requester pushes an 8-bit address across the RF and the partner ST60A3H1 replies by pushing back the 8-bit data. The software checks the completion of a write or read request by reading a Local status bit (REMOTE\_BUSY, which can be mapped to EVT\_RMT\_DONE and can generate an interrupt – note that REMOTE\_BUSY and EVT\_RMT\_DONE toggle on the Local device only).

The application must ensure that REMOTE\_BUSY has gone low before attempting a new Remote write access. A new Remote write access while REMOTE BUSY is high, is ignored.

Accessing register OTA opens up the following possibilities:

- Software can control the GPIO of a Remote ST60A3H1 by writing to / reading from the Remote registers controlling the GPIOs.

- Software can communicate with a Remote partner by writing to / reading from any of the eight notepad

registers for any application specific purpose.

- More generally, software can control most parameters of the Remote device.

Read and write accesses to notepad registers are signaled by EVT\_NOTEPAD\_RD and EVT\_NOTEPAD\_WR respectively (see also Section 2.8.4.1.1: Interrupts and RRA).

Note:

- If SLEEP is enabled when an RRA access is requested, REMOTE\_BUSY could remain high for SLEEP\_TIMER time plus the amount of time to complete the RRA.

- 2. In the unlikely event that OTA access does not complete properly due to a loss of the RF channel, the ST60A3H1 automatically triggers a LINK\_RESET.

DS14598 - Rev 4 page 25/74

#### 2.8.4.1.1 Interrupts and RRA

As already mentioned, the completion of an RRA transaction initiated over the I<sup>2</sup>C interface on the Local device triggers EVT\_RMT\_DONE interrupt.

Read RRAs also raise an EVT\_NOTEPAD\_RD interrupt. If this event is not desired, there are two ways to circumvent the interrupt:

- If EVT\_NOTEPAD\_RD on the Local side is never checked by the application, it is possible to mask EVT\_NOTEPAD\_RD.

- If EVT\_NOTEPAD\_RD on the Local side is used by the application, the sequence of operations required for an RRA read can be modified with the objective of temporarily disabling EVT\_NOTEPAD\_RD.

#### 2.8.4.1.2 Locally only accessible registers

Some registers exposing critical information are not readable by RRA.

Note: RRA read of such a register returns an erroneous value.

#### 2.8.4.1.3 RRA exceptions

There are some exceptions to Remote register access:

- Locally only accessible registers as described in Section 2.8.4.1.2.

- Certain register fields should not be modified by RRA, the write being hazardous and not to be attempted.

- Some registers are dynamically updated by the FSM, therefore the read back value, whether by RRA or locally on the I<sup>2</sup>C interface, changes over time.

#### 2.8.4.1.4 Availability of OTA communication

Hardware-driven OTA accesses can take place during RF\_DETECT (pairing phase), LOW\_POWER, and TUNNELING states. The application must ensure that no concurrent register access occurs through the I<sup>2</sup>C interface.

In normal operating conditions:

- Application-driven OTA register access is limited to LOW\_POWER state

- Configuration of the Remote partner is limited to LOW\_POWER state

OTA register access from the Remote device:

The Remote device is never allowed to carry out an RRA from the I<sup>2</sup>C configuration interface. Any attempt is ignored.

DS14598 - Rev 4 page 26/74

#### 2.8.4.2 SLEEP, WAKE-UP and HOUSEKEEPING phases

#### 2.8.4.2.1 **SLEEP** phase

In the absence of any ongoing activity over the RF channel, and provided SLEEP is enabled, the paired partners enter a SLEEP phase and thus reduce their power consumption to the bare minimum.

SLEEP is the deepest power state of the RF channel:

- All analog and RF blocks are disabled

- The low power digital clock is disabled

- An ultralow power clock (ULP Clock) and a timer are enabled

During the SLEEP phase, requests performed on the Local device through the I<sup>2</sup>C configuration interface are delayed until the device wakes-up. This concerns requests involving OTA read or writes, the tunneling command, and internal traffic ensuring integrity of the RF channel or transitions from SLEEP phase.

On entry to LOW\_POWER and periodically at SLEEP\_TIMER intervals while sitting in LOW\_POWER, the Local device:

- Performs several pending Housekeeping tasks and expects the Remote device for the same (see Section 2.8.4.2.3: HOUSEKEEPING phase).

- OTA writes the power control register to the Remote device. This ensures coherent values of the SLEEP parameter (SLEEP enabled/disabled in LOW POWER state).

- OTA writes SLEEP\_TIMER value to the Remote device.

- Instructs the Remote device to enter SLEEP (if SLEEP is enabled).

If SLEEP is enabled, both devices reset their SLEEP\_TIMER and enter SLEEP when the Remote device acknowledges the request to enter the SLEEP phase. The devices disable most of the analog and RF circuitry upon entry into SLEEP sub-state.

If SLEEP is disabled, both devices still reset their SLEEP\_TIMER without effectively disabling their analog and RF circuitry. They remain idle for the duration of their respective SLEEP\_TIMER. It is recommended that the desired value of the power control register be set while the Local device sits in RF\_IDLE (RF\_EN = 0). However updating its value is possible while the Local device already sits in LOW\_POWER state.

During the SLEEP phase, LINK\_STATUS remains high. LINK\_STATUS goes low only if the RF link integrity engine (see Section 2.8.4.4: RF link integrity) detects a broken link.

#### 2.8.4.2.2 WAKE-UP phase

The purpose of waking-up from SLEEP every so often is twofold:

- It reactivates the link to perform pending tasks

- It checks that the RF channel is still up and available.

On SLEEP\_TIMER completion, each device wakes up independently and activates its TX and RX paths. The Local device sends ping messages while the Remote device attempts to detect ping messages and acknowledges back.

Whenever a device does not detect its RF partner within WATCHDOG\_TIMER the link is declared broken, LINK\_STATUS goes low and a LINK\_RESET is carried out.

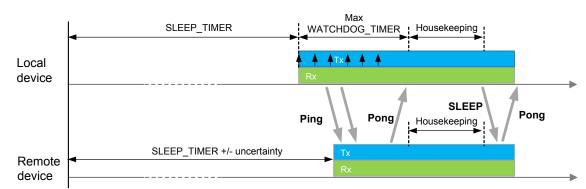

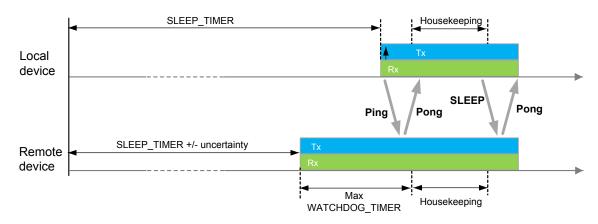

Due to some uncertainty between the timers of the two ends of the RF channel, the Local and Remote devices do not wake-up at the same time. This is depicted in Figure 19 and Figure 20. When a device wakes up it starts its own WATCHDOG\_TIMER. If it has not resumed the connection with its partner within WATCHDOG\_TIMER time, the ST60A3H1 considers that the RF Link is broken and triggers a LINK\_RESET. Providing a WATCHDOG\_TIMER value largely exceeding SLEEP\_TIMER is recommended (defaulting respectively to 250 ms and 110 ms).

An optimization mechanism aimed at limiting the drift between the two timers, and thus optimizing the power consumption is applied (see Section 2.8.4.3: Power consumption).

DS14598 - Rev 4 page 27/74

Figure 19. SLEEP and WAKE-UP phases. Local device wakes up first

Figure 20. SLEEP and WAKE-UP phases. Remote device wakes up first

#### 2.8.4.2.3 HOUSEKEEPING phase

Housekeeping tasks are:

- Pending RRA requests

- Sensing the temperature if this feature is enabled

- Handling output power temperature compensation if such tasks are enabled in LOW\_POWER state.

To allow several consecutive RRA requests without risking returning to SLEEP in between each RRA, the application can disable the SLEEP feature for the duration of the RRA accesses. After the last RRA, the application must re-enable the SLEEP feature for optimal power consumption in LOW\_POWER state.

Once Housekeeping tasks are completed, and only then, the Local device:

- · Executes a pending tunneling command, if any

- Otherwise instructs the Remote device to return to SLEEP (if SLEEP is enabled).

DS14598 - Rev 4 page 28/74

#### 2.8.4.3 Power consumption

The power consumption in LOW\_POWER state depends on two key parameters:

- SLEEP TIMER value

- Enabling of the temperature sensor

Clearly the device that wakes-up first consumes more than that which wakes-up last, since it must sit waiting for its partner while keeping its transmit and receive paths activated. Since it is difficult to predict which of the two partners is ready first, it makes more sense to look at the overall consumption of the two devices.

An optimization mechanism setting the emphasis on the Remote device power consumption is applied. This optimization is particularly beneficial when the SLEEP\_TIMER duration has a large value of the order of 1 s or more. It optimizes the consumption of the Remote device at the slight expense of the Local device consumption.

#### 2.8.4.4 RF link integrity

Two ST60A3H1 devices sitting in LOW\_POWER state regularly check the integrity of the RF link. This verification is done automatically when the low power state machine is enabled and the devices periodically enter SLEEP sub-state and wake-up properly. Failing from waking up indicates a loss of the RF Channel which triggers a LINK RESET.

The link integrity is still verified when the low power mechanism is bypassed (SLEEP disabled). The periodicity of this check is still set by the SLEEP\_TIMER duration.

In order to avoid excessive occurences of LINK\_RESET, the WATCHDOG\_TIMER delays the effective reset of the link if no acknowledgement of a partner is detected immediately after SLEEP\_TIMER duration.

DS14598 - Rev 4 page 29/74

#### 2.8.4.5 Entry into TUNNELING state

Both ST60A3H1 devices must be programmed (Local and Remote) before entering active tunneling mode. Programming is handled by the Local ST60A3H1.

The host connected to the Local ST60A3H1 carries out the configuration of the two devices by writing to specific registers in order to:

- Describe the tunneling configuration of the Local device:

- The protocol that the Local partner is expected to implement

- The role that the Local partner is expected to hold in the protocol (controller/target, source/sink, USP/ DSP) including supplementary information regarding the configuration of the IC in the application

- Describe the tunneling configuration of the Remote device:

- The protocol that the Remote partner is expected to implement

- The role that the Remote partner is expected to hold in the protocol (controller/target, source/sink, USP/DSP) including supplementary information regarding the configuration of the IC in the application

- Trigger the tunneling command (TUNNELING\_CMD). The effect of this command is to:

- OTA copy Local configuration registers into Remote configuration registers

- Check the validity of the configuration

- Enter the desired TUNNELING state

Entry into TUNNELING state fails if the configurations are not compatible. This is the case in particular when protocols do not match or when directions are incompatible (such as two downstream ports connected together in eUSB2). In such a case, the two devices remain in LOW\_POWER state and both trigger the interrupt EVT\_LOW\_POWER\_ERROR.

Executing the tunneling command sets REMOTE\_BUSY bit high until the command is actually executed. Completion of the command can thus be detected by interrupt if EVT\_RMT\_DONE is mapped as an event. A successful entry into TUNNELING state raises EVT\_TUNNELING.

#### 2.8.5 TUNNELING state

TUNNELING state is entered from LOW\_POWER state when a tunneling mode, eUSB2, UART, GPIO or I<sup>2</sup>C is activated.

See Section 2.2: eUSB2 tunneling, Section 2.3: UART tunneling, Section 2.4: GPIO tunneling, and Section 2.5:  $I^2C$  tunneling for an introduction.

#### 2.8.5.1 RF link integrity

In TUNNELING state, the verification of the RF link integrity depends on the protocol in use (eUSB2, UART, GPIO, or I<sup>2</sup>C).

DS14598 - Rev 4 page 30/74

#### 2.8.5.2 Return to LOW POWER

Returning to LOW\_POWER state while in TUNNELING is achieved by:

- Ensuring there is no ongoing or upcoming traffic on the link

- Triggering the low power command (LOW POWER CMD) on the Local ST60A3H1

The low power command execution is delayed until the next period that the link integrity mechanism kicks in. This delay is bounded by SLEEP\_TIMER duration.

Executing the low power command sets REMOTE\_BUSY bit high until the command is actually executed.

It is the application's responsibility to ensure no traffic is ongoing (or if eUSB2 tunneling is active, that the link sits in SUSPEND or LS/FS idle mode) before triggering the low power command. Failing to conform to this specification may lead to unpredictable behavior.

# 2.9 Sleep timer, Watchdog timer, and high-level Watchdog timer

The ST60A3H1 embeds several programmable timers and watchdogs. The three main timers are the Sleep timer, the Watchdog timer (sometimes referred to as the low-level Watchdog timer) and the high-level Watchdog timer. These three timers are controlled by the SLEEP\_TIMER and the WATCHDOG\_TIMER.

The SLEEP TIMER controls:

- The duration of the sleep phases in LOW\_POWER state and ultralow power substates of full-duplex UART/ GPIO tunneling

- The interval at which RF link integrity is checked in LOW\_POWER state, and in UART tunneling (except ULP half-duplex), GPIO tunneling or I<sup>2</sup>C tunneling

The WATCHDOG\_TIMER controls:

- The time period after which a broken RF link is detected in LOW POWER state (low-level Watchdog)

- The high-level Watchdog

Details on the usage of SLEEP\_TIMER and WATCHDOG\_TIMER in LOW\_POWER state are provided in Section 2.9.1: Timer settings in LOW\_POWER state.

# 2.9.1 Timer settings in LOW\_POWER state

The sleep mechanism is detailed in Section 2.8.4.2: SLEEP, WAKE-UP and HOUSEKEEPING phases. For efficient power optimization, SLEEP\_TIMER should be set to a relatively large value, for example 500 ms (default is 110 ms).

The low-level Watchdog timer (not be confused with the high-level Watchdog) controls the time period after which a broken RF link is detected. It is essential to ensure that WATCHDOG\_TIMER is strictly higher than SLEEP\_TIMER, in practice, it is highly recommended to set:

WATCHDOG TIMER > 1.2 × SLEEP TIMER

Therefore, if SLEEP\_TIMER is to be increased from its default value up to 1 s, WATCHDOG\_TIMER should be increased first to follow the same ratio.

Note: SLEEP\_TIMER = 500 ms, already provides good power consumption results (see Section 5.5.3: LOW\_POWER parameters).

If the ST60A3H1 pair does not communicate both ways for a period of WATCHDOG\_TIMER, the device triggers a LINK RESET.

DS14598 - Rev 4 page 31/74

#### 2.9.2 High-level Watchdog

The HL Watchdog is a hardware block that continuously monitors the output of the analog RF Receiver path, operating at a level above all lower level control mechanisms. The HL Watchdog relies on a counter, clocked by the ULP clock therefore always active, that is reset whenever valid activity is detected on the RF receiver path. If the HL Watchdog counter reaches its upper limit, the HL Watchdog triggers a LINK RESET.

Note:

The LINK\_RESET may occur some time after the counter expiration to allow the management of interfaces and specific protocol constraints.

Internal mechanisms in LOW\_POWER and TUNNELING states ensure that under normal conditions the RF link is regularly exercised. The HL Watchdog is thus a last resort mechanism to detect a broken RF link or a deadlock. The HL Watchdog counter is initialized to zero, counting up to:

$(WATCHDOG\_TIMER + 1) \times 8000$  ULP clock cycles

This corresponds to an approximate time-out duration of:

$(WATCHDOG\_TIMER + 1) \times 80 \text{ ms}$

The available range for time-out spans from approximately 80 ms to 20.5 s (default is 2 s).

By default, the HL Watchdog is active only when the main FSM is in the LOW\_POWER and TUNNELING states but it can be disabled for debug or validation purposes.

#### 2.9.2.1 HL Watchdog expiration during eUSB2 tunneling

If the HL Watchdog expires during eUSB2 tunneling:

- The high-speed I/Os are kept under the control of the eUSB2 state machine.

- If the eUSB2 line is in connected state, ESE1 is generated towards the Host.

- After 3 ms, LINK\_RESET is asserted, interrupt signal EVT\_LINK\_DISABLED goes high and LINK\_STATUS is driven low.

#### 2.9.2.2 HL Watchdog expiration during LOW POWER state or during non-eUSB2 tunneling

If the HL Watchdog expires during LOW\_POWER state or non eUSB2 tunneling, LINK\_RESET is immediately asserted, interrupt signal EVT\_LINK\_DISABLED goes high and LINK\_STATUS is driven low.

DS14598 - Rev 4 page 32/74

# 2.10 Temperature compensation

#### 2.10.1 Temperature sensor

In order to compensate the output power for temperature variations, the ST60A3H1 embeds a temperature sensor.

The temperature sensor is activated at regular intervals defined by TEMP\_SENS\_INTRVL to minimize the power consumption.

Applications that do not require any temperature sensing can disable the sensor altogether with TEMP\_SENS\_EN.

Table 5 lists the parameters accessible to the application that controls the temperature sensor. In practice the application must only control TEMP\_SENS\_EN and TEMP\_SENS\_INTRVL; ST60A3H1 internal state machine autonomously uses the temperature measurement for compensation.

The actual temperature in Celsius equals TEMP DATA - 35.

Table 5. Temperature sensor control parameters

| Description                                                | Parameter                  | Available range                                                      |

|------------------------------------------------------------|----------------------------|----------------------------------------------------------------------|

| Enable / disable temperature sensing                       | TEMP_SENS_EN               | -                                                                    |

| Periodicity of temperature measurements in TUNNELING state | TEMP_SENS_INTRVL           | 4 values from 10 ms to 500 ms                                        |

| Periodicity of temperature measurements in LOW_POWER state | SLEEP_TIMER <sup>(1)</sup> | -                                                                    |

| Actual temperature in Celsius shifted by 35                | TEMP_DATA                  | 1 LSB = 1 °C<br>+/- 1 °C accuracy at 27 °C,<br>max +/- 3 °C at 85 °C |

| Measurement completion                                     | TEMP_DATAREADY             | -                                                                    |

| Previous measurement                                       | TEMP_DATA_PRV              | -                                                                    |

<sup>1.</sup> This is the normal case when SLEEP is enabled. When SLEEP is disabled, the periodicity is the minimum of SLEEP TIMER and TEMP SENS INTRVL.

#### 2.10.2 Output-power temperature compensation

Output power varies by +/- 2 dB across the operating temperature range. Power degradation is roughly linear with increasing temperature. Compensation can be applied to overcome this power degradation.

Table 6 lists the parameters accessible to the application for output-power temperature compensation.

Table 6. Output-power temperature compensation control parameters

| Description                                                               | Parameter               |

|---------------------------------------------------------------------------|-------------------------|

| Enable / disable output-power temperature compensation in LOW_POWER state | PWR_TEMP_COMP_LP_EN     |

| Enable / disable output-power temperature compensation in TUNNELING state | PWR_TEMP_COMP_TUNNEL_EN |

#### 2.10.2.1 Compensation during LOW POWER state

This is only performed in the LOW\_POWER state (as part of Housekeeping, and therefore with a periodicity dependent on SLEEP\_TIMER: see Section 2.8.4.2.3) provided that PWR\_TEMP\_COMP\_LP\_EN = 1.

# 2.10.2.2 Compensation during TUNNELING state

This is only performed in the TUNNELING state provided that PWR\_TEMP\_COMP\_TUNNEL\_EN = 1, and is applied when the device is not communicating. Output power is adjusted at most every TEMP\_SENS\_INTRVL and only when the transmitter is not in use, that is:

- eUSB2: at the beginning of RX activity (start of frame) and in L2 state.

- ULP UART: when the link is idle

- All other protocols do not offer reliable opportunities to update power while in TUNNELING mode. Outputpower temperature compensation can only take place in LOW\_POWER state

DS14598 - Rev 4 page 33/74

# 3 Interrupts and errors

Interrupts are mapped to the MODE\_INT pin.

All events and errors can be mapped onto the interrupt pin.

On a LINK\_RESET, the following events are automatically cleared:

- EVT\_NOTEPAD\_WR

- EVT\_NOTEPAD\_RD (see Section 2.8.4.1.1: Interrupts and RRA)

- EVT\_LINK\_ENABLED

- EVT\_RMT\_DONE

The others are left unchanged.

Table 7. Events mappable to MODE\_INT

| Event name          | Reported information                                                      |

|---------------------|---------------------------------------------------------------------------|

| EVT_NOTEPAD_WR      | Indicates Notepad write access                                            |

| EVT_NOTEPAD_RD      | Indicates Notepad read access (see Section 2.8.4.1.1: Interrupts and RRA) |

| EVT LINK ENABLED    | Link is now enabled (automatically or by SW)                              |

| EVI_ENV_ENABLED     | Same logic level as LINK_STATUS                                           |

| EVT_LOW_POWER_ERROR | Validation step of LOW_POWER state has failed                             |

| EVT_RMT_DONE        | Remote access (RRA) done                                                  |

| EVT_RF_DETECT_ERROR | Error during RF Detect                                                    |

| EVT_LINK_DISABLED   | LINK_STATUS switched from 1 to 0 due to a LINK_RESET                      |

| EVT_TEMP_ERROR      | Temperature sensor overflow or error                                      |

| EVT_TUNNELING       | Entering TUNNELING state                                                  |

| EVT_LOW_POWER       | Entering LOW_POWER state                                                  |

| RSSI_COMPLETE       | RSSI is complete                                                          |

| RSSI_ERROR          | RSSI error                                                                |

| EVT_PWR_COMP_ERROR  | Output-power temperature compensation error                               |

DS14598 - Rev 4 page 34/74

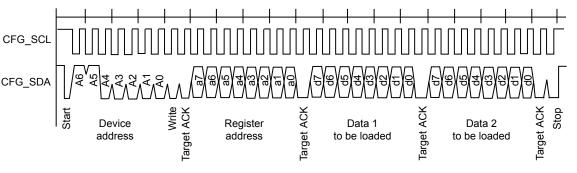

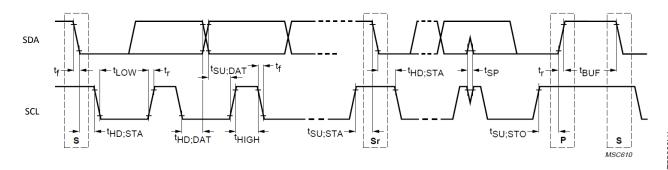

# 4 I<sup>2</sup>C configuration interface

The ST60A3H1 I<sup>2</sup>C configuration interface supports the I<sup>2</sup>C 100 kbit/s, 400 kbit/s and 1 Mbit/s speed rates.

Note:

The ST60A3H1 I<sup>2</sup>C port does not feature any glitch filtering capability. Input and output data on the CFG\_SDA pad are sampled on the clock line CFG\_SCL. It is therefore mandatory that the application ensures a glitch-free CFG\_SCL line.

Accessing registers through the I<sup>2</sup>C configuration interface is subject to caution:

- LOW\_POWER is the state of choice for the complete configuration of a Local device and the future programming of a Remote device before entering TUNNELING state.

- Registers of a Remote device are readable through I<sup>2</sup>C when the RF link is established (LINK\_STATUS=1).

- Although not recommended, registers of a Remote device are writable through I<sup>2</sup>C when the RF link is established (LINK\_STATUS=1). It is the application responsibility to ensure consistency of the device configuration.

More specifically, registers should not be written to when:

- the ST60A3H1 is in RF DETECT state

- the ST60A3H1 is in TUNNELING state, except if the write access corresponds to issuing a forced LINK\_RESET or a low power command

# 4.1 Address selection, read and write accesses

The 7-bit device address allocated to the ST60A3H1 I<sup>2</sup>C configuration interface is fixed to 0x60. Therefore, the first byte (7-bit address and direction bit) used in transactions is:

- 0xC0 for write mode

- 0xC1 for read mode

#### 4.1.1 Write access

The byte sequence is as follows:

- 1. The controller sends the first byte (7-bit device address and direction bit, RW = 0).

- 2. The second byte contains the internal address of the first register to be accessed.

- 3. The next byte is written in the internal register. Any following bytes are written in successive internal registers.

- The transfer lasts until a stop bit is encountered.

- 5. The ST60A3H1, as target, acknowledges every byte transfer.

Figure 21 shows an I<sup>2</sup>C write access example with 7-bit device address set to 0x60.

Figure 21, I<sup>2</sup>C write access

DS14598 - Rev 4 page 35/74

JT55328V2

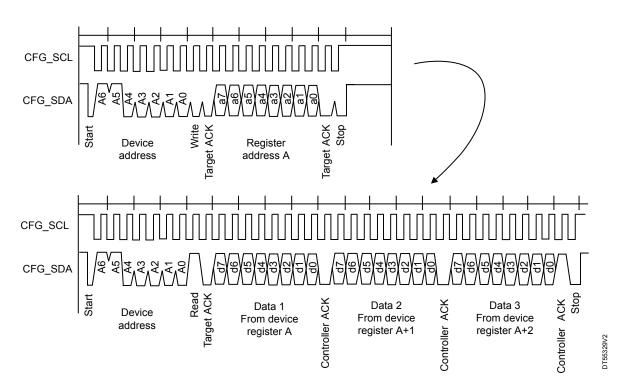

#### 4.1.2 Read access

The byte sequence is as follows:

- 1. The controller sends the first byte (7-bit device address and direction bit, RW = 0).

- 2. The second byte contains the internal address of the first register to be accessed.

- 3. This is terminated with a stop bit.

- 4. The controller restarts the transmission with the ST60A3H1 address and direction bit, RW = 1.

- 5. The ST60A3H1 acknowledges and sends the register content. If the controller acknowledge is low, the target transmits another byte which is the contents of the next address register. This continues until the controller acknowledge is high, then the transmission terminates with a stop bit.

Figure 22 shows an I<sup>2</sup>C read access example with 7-bit device address set to 0x60.

Figure 22. I<sup>2</sup>C read access

# 4.2 Low power and I<sup>2</sup>C access

In cases where the ST60A3H1 is in Low power mode, an I<sup>2</sup>C start wakes up the device from Low power mode, and enables an internal clock.

The internal clock is used to carry out the I<sup>2</sup>C transaction into the relevant register, and to take any action consecutive to the write access. Once the access has completed, the device returns to Low power mode.

DS14598 - Rev 4 page 36/74

#### 5 Electrical characteristics

#### Caution:

All electrical performances are related to default or factory calibrated settings.

All RF parameters, except for Rx blockers, are characterized in free space propagation and line of sight conditions with the ST60A3H1, which is soldered on its specifically optimized validation board. Rx blockers are characterized in conducted mode with the ST60A3H0, which is equivalent to the ST60A3H1 without the integrated antenna.

### 5.1 Reset, ThS and magnetic flux

Table 8. Reset, ThS and magnetic flux

| Symbol                                             | Parameter                                                                                                                                                                        | Min | Тур | Max  | Unit |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>RESET</sub>                                 | Reset time after supply voltage is settled                                                                                                                                       | -   | -   | 2250 | μs   |

| t <sub>DWELL</sub>                                 | Minimum supply dwell time at ground level before rising supply voltage                                                                                                           | -   | -   | 10   | μs   |

| t <sub>SUPPLY, rise</sub>                          | Supply rise time                                                                                                                                                                 | 50  | -   | 1000 | μs   |

| t <sub>SUPPLY, fall</sub>                          | Supply fall time                                                                                                                                                                 | 50  | -   | 1000 | μs   |

| ThS <sub>Accuracy</sub> <sup>(1)</sup>             | Thermal sensor functionality and accuracy in the range 0 to 85 °C                                                                                                                | -7  | -   | 7    | °C   |

| B <sub>MAX_OP_MAGNET</sub> (2)                     | Static magnetic flux density supported in the operational environment                                                                                                            | -   | -   | 10   | mT   |

| B <sub>MAX_OP_WIRELESS_CHARGER<sup>(2)</sup></sub> | Magnetic flux density supported in the operational environment at 326 kHz/360 kHz switching frequency (wireless charger). 33 W measured on coil placed at 15 mm from the device. | -   | -   | 200  | μΤ   |

| B <sub>MAX_OP_NFC</sub> <sup>(2)</sup>             | Magnetic flux density supported in the operational environment at 13.56 MHz switching frequency (NFC). 2.5 W measured on a coil placed at 15 mm from the device.                 | -   | -   | 10   | μΤ   |

<sup>1.</sup> Calibrated at 1.8 V and 30 °C

### 5.2 Absolute maximum ratings (AMR)

Stresses above the absolute maximum ratings listed in Table 9 may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect the device reliability.

Device use conditions are compliant with the JEDEC JESD47 qualification standard.

Table 9. Absolute maximum ratings

| Symbol                         | Parameter                                                                            | Min | Тур | Max | Unit |

|--------------------------------|--------------------------------------------------------------------------------------|-----|-----|-----|------|

| VDD_1V8                        | Analog power supply                                                                  | -   | -   | 2.5 | V    |

| VDD_IO                         | igital and I/O power supply                                                          |     |     |     | V    |

| P <sub>IN</sub>                | Maximum CW input power at Rx antenna input, LNA OFF or LNA ON with dimmer Tx enabled |     | -4  | dBm |      |

| T <sub>STG</sub>               | Storage temperature                                                                  | -40 | -   | 125 | °C   |

| TJ                             | Junction temperature                                                                 | -40 | -   | 125 | °C   |

| RH <sub>s</sub> <sup>(1)</sup> | Storage relative humidity @ 30°C                                                     | -   | -   | 60  | %    |

<sup>1.</sup> Moisture Sensitivity Level 3: 168 hours floor life (≤30°C / 60% RH) after dry pack opening at customer manufacturing.

DS14598 - Rev 4 page 37/74

<sup>2.</sup> The impact of different magnetic fields have been checked (as null or negligeable) on key parameters as well as during link operation.

## 5.3 ESD ratings

Caution: This is an ESD sensitive device; improper handling can cause permanent damage to the part.

Table 10. ESD ratings

| Symbol                     | Parameter                                                                                                     | Conditions <sup>(1)</sup> | Min <sup>(2)</sup> | Unit |

|----------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------|--------------------|------|

| V <sub>ESD_HBM</sub>       | Electrostatic discharge voltage (HBM)                                                                         | JS-001                    | +/- 1500           | V    |

| V <sub>ESD_RCDM_GP</sub>   | Electrostatic discharge voltage (RCDM) for pins GPIO[3:0], CFG_SDA, CFG_SCL, LINK_STATUS, RF_EN, and MODE_INT | JS-002                    | +/- 500            | V    |

| V <sub>ESD_RCDM_</sub> HSO | Electrostatic discharge voltage (RCDM) for pins RX_OP and RX_ON                                               | JS-002                    | +/- 350            | V    |

| V <sub>ESD_RCDM_HSI</sub>  | Electrostatic discharge voltage (RCDM) for pins TX_IP and TX_IN                                               | JS-002                    | +/- 350            | V    |

<sup>1.</sup> For definitions of the ESD classes, see the relevant JEDEC standards, or contact STMicroelectronics customer support.

## 5.4 Normal operating conditions