# ST33KTPM provisioned for device identity and attestation

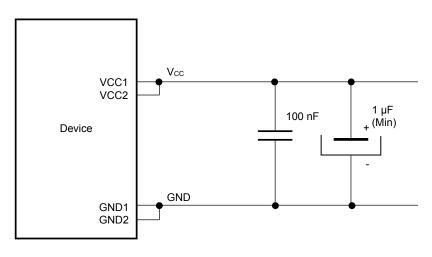

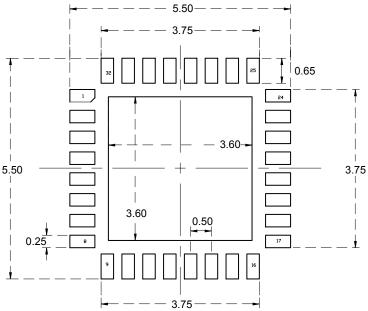

UFQFPN32 (5 × 5 × 0.55 mm)

#### **Product status link**

ST33KTPM-IDevID

#### **Features**

#### **TPM features**

- Flash memory-based trusted platform module (TPM)

- Compliant with Trusted Computing Group (TCG) trusted platform module (TPM) Library specifications 2.0, revision 1.59 errata version 1.5 and TCG PC Client Platform TPM Profile (PTP) for TPM 2.0 version 1.05

- Fault-tolerant firmware loader that keeps the TPM fully functional when the loading process is interrupted

- SP800-193 compliant for protection, detection and recovery requirements

- Targeted certifications:

- Common Criteria EAL4+ in compliance with the TPM 2.0 protection profile (augmented with AVA\_VAN.5, resistant to high-potential attacks)

- FIPS 140-3 with physical security level 3

- TCG certification

- 192 KB NV memory available to store keys and data

- SPI communication bus running at up to 66 MHz

- I<sup>2</sup>C communication bus running at up to 1 Mb/s

#### IDevID and IAK provisioning

ST33KTPM-IDevID devices are provisioned with 2 signing keys ECC NIST P-384 and 2 certificates to support device identity and attestation use cases, compliant with TCG TPM 2.0 Keys for Device identity and Attestation v1.1

#### **Hardware features**

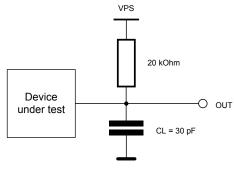

- Highly reliable flash memory with error correction code

- Extended temperature range: -40°C to 105°C

- Electrostatic discharge (ESD) protection up to 4 kV (HBM)

- 1.8 V or 3.3 V supply voltage range

#### Security features

- Active shield

- Monitoring of environmental parameters

- Hardware and software protection against fault injection and side channel attacks

- NIST SP800-90A and AIS20-compliant deterministic random-bit generator (DRBG)

- NIST SP800-90B and AIS31-compliant true random-number generator (TRNG)

- Cryptographic algorithms:

- RSA key generation (1024, 2048, 3072 and 4096 bits)

- RSA signature (RSASSA-PSS, RSASSA-PKCS1v1\_5)

- RSA encryption (RSAES-OAEP, RSAES-PKCS1-v1\_5)

- SHA-1, SHA-2 (256 and 384 bits), SHA-3 (256 and 384 bits)

- HMAC SHA-1, SHA-2, and SHA-3

- AES-128, 192, and 256 bits

- ECC key generation (NIST P-256/384)

- ECC secret sharing (ECDH)

- ECC signature (ECDSA, ECSchnorr, ECDAA)

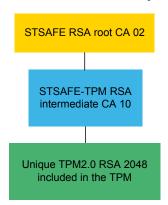

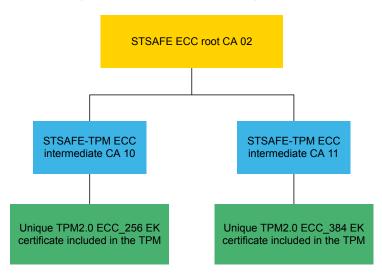

- Device provided with three endorsement keys (EK) and EK certificates (RSA2048, ECC NIST P-256 and ECC NIST P-384)

- Device provisioned with three 2048-bit RSA key pairs to reduce the TPM provisioning time

#### **Product compliance**

- Compliant with Microsoft<sup>®</sup> Windows<sup>®</sup> 10 and 11

- Compliant with Linux<sup>®</sup> drivers

- Compliant with Intel<sup>®</sup> vPro<sup>®</sup> technology

- Compliant with TCG test suite for TPM 2.0

- Compliant with the open-source TCG TPM 2.0 TSS implementation

DS15011 - Rev 1 page 2/97

# 1 Description

The ST33KTPM-IDevID is a trusted platform module provisioned with keys and certificates to support use cases like device identity and attestation. The ST33KTPM-IDevID is compliant with TCG TPM 2.0 keys for device identity and attestation 1.1.

The IDevID key and X509 certificate provide the device identity defined by IEEE 802.1AR and are compatible with cloud system authentication such as AWS IoT, and Microsoft Azure, and can also be used in TLS 1.3 session to authenticate client.

The ST33KTPM-IDevID comes also with bundle files including device leaf certificates for a specific reel that are made available through authenticated download. This improves the supply chain security as the ST33KTPM-IDevID devices identified can be activated thanks to the bundle files after reception of reels, or can be revoked in case of lost shipment. This also facilitates the loading of leaf certificates in the cloud system before getting access to the physical platforms embedding ST33KTPM-IDevID devices.

The ST33KTPM-IDevID is based on product ST33KTPM2X compliant with the *TCG TPM* library specifications 1.59. It offers a target serial peripheral interface (*SPI*) or a target *I*<sup>2</sup>*C* interface, both compliant with the TCG PC client TPM profile specifications and PC client platform TPM profile (*PTP*) version 1.05.

ST33KTPM-IDevID devices are certified Common Criteria, TCG, and FIPS140-3.

It offers resilience services during the TPM firmware upgrade process, and self-recovery of TPM firmware and critical data upon failure detection.

The ST33KTPM-IDevID operates in the -40°C to 105°C extended temperature range.

The ST33KTPM-IDevID generic parts are loaded with X509 certificates signed by an STSAFE-TPM certification authority described in the provisioning profile. Upon customer request, STMicroelectronics can support a customer-specific provisioning profile and assign a dedicated certification authority linked to a specific ordering code.

ST33KTPM-IDevID devices with generic profile are based on ST33KTPM2X product offered in UFQFPN32 Ecopack2 package.

ST33KTPM-IDevID devices with customer profile are based either on ST33KTPM2X product offered in UFQFPN32 Ecopack2 package or on ST33KTPM2I product offered in WLCSP Ecopack2 package.

DS15011 - Rev 1 page 3/97

# 2 Datasheet scope

# 2.1 ST33KTPM-IDevID product

This datasheet describes the ST33KTPM-IDevID product based on the product ST33KTPM2X provisioned with a generic provisioning profile.

A unique 3-letter ID printed on the package (Area L) defines each provisioning profile. Provisioning profiles can be generic or customer specific. The description of the provisioning is defined in a separate application note including the reference to the provisioning profile ID (refer to [AN6324]).

This datasheet includes the ordering code of ST33KTPM-IDevID devices with generic provisioning profiles.

The ordering codes of ST33KTPM-IDevID devices with customer-specific profiles are defined in documents with restricted access to those customers. These documents are provided by your sales contact.

The procedure to download bundles files is described in the application note [AN6350], "Online certificate distribution for STSAFE-TPM products".

DS15011 - Rev 1 page 4/97

# 3 UFQFPN32 pin and signal description

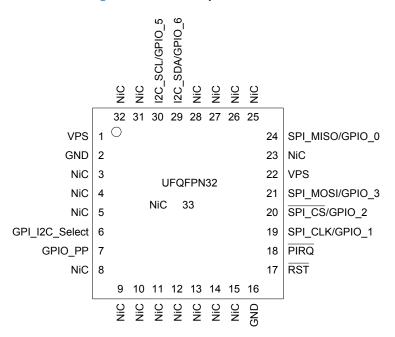

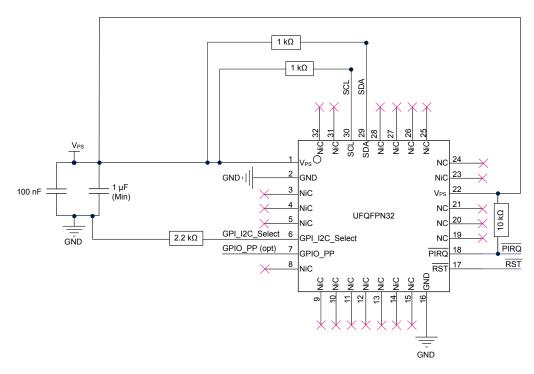

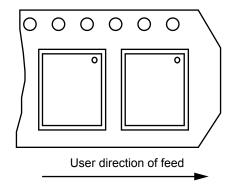

The figure below gives the pinout of the UFQFPN32 package in which the devices are delivered. Table 1 describes the associated signals.

Figure 1. UFQFPN32 pinout

F70357V2

DS15011 - Rev 1 page 5/97

Table 1. UFQFPN32 pin descriptions

| Signal         | Туре             | GPIO<br>configuration<br>during reset | Description                                                                                                                                                                                                                                                                |

|----------------|------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPS            | Input            | _                                     | <b>Power supply</b> . This pin must be connected to 1.8 V or 3.3 V DC power rail supplied by the motherboard.                                                                                                                                                              |

| GND            | Input            | _                                     | <b>Ground</b> , has to be connected to the main motherboard ground.                                                                                                                                                                                                        |

| RST            | Input            | VWPD                                  | Reset, active low, used to re-initialize the device. Must not be unconnected. External pull-up resistor is required if it cannot be driven.                                                                                                                                |

| SPI_MISO       | Output           | VWPD                                  | SPI master input, slave output (output from slave)                                                                                                                                                                                                                         |

| SPI_MOSI       | Input            | VWPD                                  | SPI master output, slave input (output from master)                                                                                                                                                                                                                        |

| SPI_CLK        | Input            | VWPD                                  | SPI serial clock (output from master)                                                                                                                                                                                                                                      |

| SPI_CS         | Input            | VWPD                                  | SPI chip (or slave) select, internal pull-up (active low; output from master)                                                                                                                                                                                              |

| PIRQ           | Output           | VWPD                                  | IRQ, active low, open drain, used by the TPM to generate an interrupt                                                                                                                                                                                                      |

| GPIO_PP        | Input            | VWPD                                  | <b>Physical presence</b> ( <i>PP</i> ), active high, internal very weak pull down. Used to indicate physical presence to the <i>TPM</i> . The <i>GPIO</i> function could be modified by activating the <i>GPIO</i> s mapped with the <i>NV</i> storage index feature.      |

| GPI_I2C_Select | Input            | WPU                                   | This pin must be connected to an external pull-down resistor to activate the <i>I</i> <sup>2</sup> <i>C</i> protocol during product boot time. It can remain unconnected for the <i>SPI</i> protocol.                                                                      |

|                |                  |                                       | This pin is internal weak pull-up by default and becomes internal floating after <i>I</i> <sup>2</sup> <i>C</i> activation.                                                                                                                                                |

| NiC            | _                | _                                     | <b>Not internally connected</b> : not connected to the die. May be left unconnected but no impact on <i>TPM</i> if connected.                                                                                                                                              |

| GPIO_X         | Input/<br>output | VWPD                                  | The <i>GPIO</i> function could be modified by activating the <i>GPIO</i> s mapped with the <i>NV</i> storage index feature. <i>GPIO</i> availability is dependent of bus interface (for example, GPIO_5 and GPIO_6 are available with the <i>SPI</i> interface activated). |

| I2C_SDA/GPIO_6 | Input/<br>output | VWPD                                  | <b>Bidirectional </b> <i>I</i> <b>°C serial data</b> (open drain without a weak pull-up resistor) / General-purpose input/output if <i>SPI</i> is activated <sup>1</sup>                                                                                                   |

| I2C_SCL/GPIO_5 | Input            | VWPD                                  | Input I <sup>2</sup> C serial clock (open drain without a weak pull-up resistor) / General-purpose input/output if SPI is activatedGeneral-purpose input/output <sup>1</sup>                                                                                               |

<sup>1.</sup> The GPIO function could be modified by activating the GPIOs mapped with the NV storage index feature.

Note:

The UFQFPN32 package has a central pad (PIN33) on the bottom, which is not connected to the die. This pin does not impact the TPM, be it connected or not.

DS15011 - Rev 1 page 6/97

# 4 Serial peripheral interface (SPI) and TPM registers

The *SPI* interface implemented in this device complies with the *TCG* PC Client-specific *TPM* Platform specifications [PTP 2.0 r1.05] for the *TPM* 2.0 library.

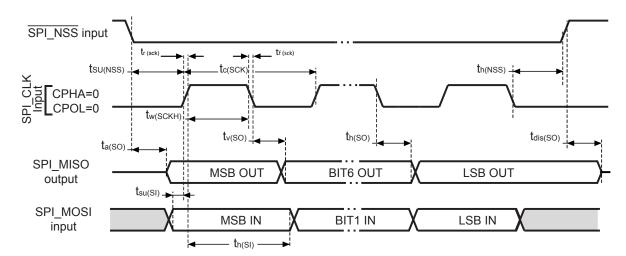

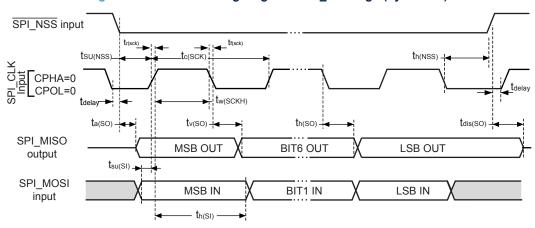

The SPI supports only one clock mode (CPOL=0, CPHA=0).

Data is transferred serially between master and slave; the most significant bit (MSB) first, least significant bit (LSB) last.

Addresses and commands are transferred msb first for the entire field, e.g. the 24-bit address is transferred by sending b23 first, then b22 all the way up to b0.

The TPM drives data on the falling edge of the SPI clock.

The TPM samples data on the rising edge of the SPI clock.

The *TPM* always decodes a 24-bit address in the 0xD4\_xxxx range when the *TPM* SPI\_CS pin is asserted.

The ST33KTPM-IDevID supports an interrupt interface line directly from the *TPM* to the main platform *MCU*. This interrupt is supported using a dedicated *GPIO* (SPI\_PIRQ, active low). The device detects a change in the *TPM* status when the *TPM* triggers a falling edge on pin SPI\_PIRQ.

#### 4.1 SPI communication protocol flow control

#### 4.1.1 SPI communication

The *TPM* flow control mechanism operates on a transaction basis and can transfer data of various sizes. The *TPM* can transfer or receive 1 up to 32 bytes of data per transaction.

Because the *SPI* does not support any acknowledge signal, a specific way to synchronize between the host and the *TPM* has been defined.

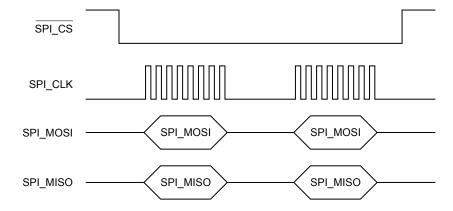

In order to synchronize the start of a command, the *SPI* master must set low the *SPI\_CS* pin when sending a command and set the *SPI\_CS* pin back to high at the end of the transaction.

An *SPI* start of frame is detected when the <u>SPI\_CS</u> signal goes low. This causes the *TPM* to drive the SPI\_MISO signal low. An end of frame is detected when the <u>SPI\_CS</u> line goes to the high voltage level.

The transmit sequence begins when the  $\overline{TPM}$  receives the SPI\_CLK signal, the  $\overline{SPI_CS}$  signal goes low and the most significant bit of the data is present on the SPI\_MOSI pin.

Figure 2. SPI transmit sequence

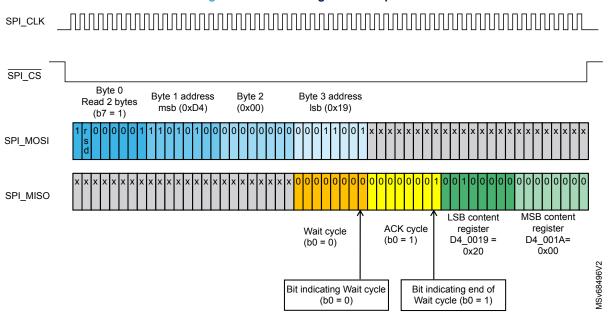

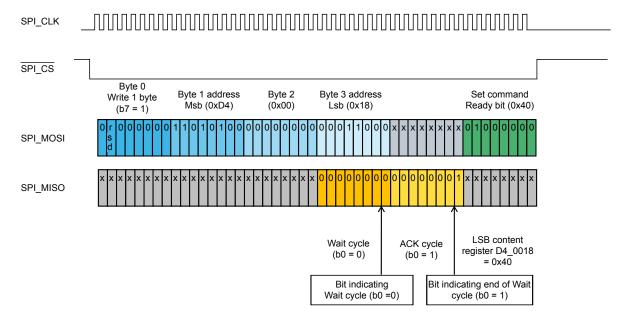

The *TPM* host initiates every command by transmitting a single byte on the SPI\_MOSI pin that tells the *TPM* if it is a read or write operation in a register. This byte also contains the size of the transfer including the 1st byte. The command processing continues with the transfer of three more bytes containing the address of the targeted register.

At this time, depending on the targeted register, the *TPM* is able to insert 1 or more Wait states before acknowledging the transfer. A Wait state is a Low state (0) sent on the SPI\_MISO pin by the *TPM*. An Acknowledgment is a byte, whose last bit is '1', sent on the SPI\_MISO pin by the *TPM*.

In the case of a register read command, the *TPM* sends on the SPI\_MISO pin the number of requested bytes from the requested register.

DS15011 - Rev 1 page 7/97

In the case of a register write command, the *TPM* reads on the SPI\_MOSI pin the number of bytes previously declared and modifies accordingly the *TPM* state machine.

Table 2. SPI bit protocol

| Bit transfer order on SPI_MISO/SPI_MOSI pins | Byte on SPI_MISO/SPI_MOSI pins                                           | Usage                                                                                                                                                                                                                                           | Notes                                                                                                                                                                 |

|----------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFU                                          | 67 for 64B transactions 11 for 8B transactions                           | Reserved for future use for larger register sizes                                                                                                                                                                                               | -                                                                                                                                                                     |

| 57-63 – last bits on wire                    | _                                                                        | Data[30:24]                                                                                                                                                                                                                                     | -                                                                                                                                                                     |

| 56                                           | 7                                                                        | Data[31]                                                                                                                                                                                                                                        | msb of 4 <sup>th</sup> LSB                                                                                                                                            |

| 49-55                                        |                                                                          | Data[22:16]                                                                                                                                                                                                                                     | -                                                                                                                                                                     |

| 48                                           | 6                                                                        | Data[23]                                                                                                                                                                                                                                        | msb of 3 <sup>rd</sup> LSB                                                                                                                                            |

| 41-47                                        | _                                                                        | Data[14:8]                                                                                                                                                                                                                                      | -                                                                                                                                                                     |

| 40                                           | 5                                                                        | Data[15]                                                                                                                                                                                                                                        | msb of 2 <sup>nd</sup> LSB                                                                                                                                            |

| 33-39                                        |                                                                          | Data[6:0]                                                                                                                                                                                                                                       | -                                                                                                                                                                     |

| 32                                           | 4                                                                        | Data[7]                                                                                                                                                                                                                                         | msb of 1st LSB                                                                                                                                                        |

|                                              | e in this window. See Protocol flow in the bit transfers where flow cont | control for SPI read access and Protocol flow or rol can be performed.                                                                                                                                                                          | ontrol for SPI write access                                                                                                                                           |

| 31                                           | 3                                                                        | Addr[0]                                                                                                                                                                                                                                         | lsb of address                                                                                                                                                        |

| 9-30                                         | 1-3                                                                      | Addr[22] down to Addr[1]                                                                                                                                                                                                                        | -                                                                                                                                                                     |

| 8                                            | 1                                                                        | Addr[23]                                                                                                                                                                                                                                        | msb of address                                                                                                                                                        |

| 2-7                                          | 0                                                                        | bits[5:0] Size of transfer where bit[5] of this field is the 3 <sup>rd</sup> bit transferred on the wire, and bit [0] is the 8 <sup>th</sup> bit on the wire. This field is 0's based count of the bytes. Any byte count from 1 to 64 is legal. | Bit [5:0] decode '11_1111' = 64 bytes 'etc. for 63 down to 6 bytes '00_0100' = 5 bytes '00_0011' = 4 bytes '00_0010' = 3 bytes '00_0001' = 2 bytes '00_0000' = 1 byte |

| 1                                            |                                                                          | Reserved; bit[6]                                                                                                                                                                                                                                |                                                                                                                                                                       |

| 0 – first bit on wire                        |                                                                          | Byte0, bit[7] Read/Write                                                                                                                                                                                                                        | 1=read, 0 = write                                                                                                                                                     |

#### 4.1.2 Protocol flow control for SPI read access

Following the standard specification, depending on the targeted register, the *TPM* is authorized to insert 1 Wait state before acknowledging the read access. A Wait state is a Low state (0) sent on the SPI\_MISO pin by the *TPM*. An Acknowledgment is a byte, whose last bit is '1', sent on the SPI\_MISO pin by the *TPM*.

The ST TPM uses only one wait state for SPI read access.

On read access, if the data are not available, the ST *TPM* uses the dedicated bits defined by the standard specification:

- stsValid (bit 7 in the Status register): This bit indicates whether TPM\_STS\_x.dataAvail and TPM\_STS\_x.Expect are valid. They are valid when stsValid = 1.

- tpmRegValidSts (bit 7 in the Access register): This bit indicates whether all other bits in this register contain valid values. All values are valid when tpmRegValidSts = 1.

The host should repeat read access and consider that the *TPM* is out of order only after TIMEOUT\_B (2 seconds) of no data availability.

DS15011 - Rev 1 page 8/97

Figure 3. SPI Read register example

#### 4.1.3 Protocol flow control for SPI write access

Following the standard specification, the *TPM* is authorized to insert 1 or more Wait states before acknowledging the write access. A Wait state is low state (0) sent on the SPI\_MISO pin by the *TPM*. An Acknowledgment is a byte, whose last bit is '1', sent on the SPI\_MISO pin by the *TPM*.

Figure 4. SPI write register example

DS15011 - Rev 1 page 9/97

# 4.2 Register space addresses

The following table shows *TPM* register space starting from the base address 0xD4\_0000.

# 4.2.1 FIFO interface

Table 3. List of FIFO register space addresses

| Locality 0        | Register<br>name           | Locality 1                        | Register<br>name           | Locality 2        | Register<br>name           | Locality 3         | Register<br>name           | Locality 4        | Register<br>name                                                        | Register description                                                                                                                        |

|-------------------|----------------------------|-----------------------------------|----------------------------|-------------------|----------------------------|--------------------|----------------------------|-------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000            | TPM_ACCESS_0               | 0x1000                            | TPM_ACCESS_1               | 0x2000            | TPM_ACCESS_2               | 0x3000             | TPM_ACCESS_3               | 0x4000            | TPM_ACCESS_4                                                            | Used to gain ownership of the TPM for this particular Locality                                                                              |

| 0x000B-<br>0x0008 | TPM_INT_<br>ENABLE_0       | 0x100B-<br>0x1008                 | TPM_INT_<br>ENABLE_1       | 0x200B-<br>0x2008 | TPM_INT_<br>ENABLE_2       | 0x300B-<br>0x30008 | TPM_INT_<br>ENABLE_3       | 0x400B-<br>0x4008 | TPM_INT_<br>ENABLE_4                                                    | Interrupt Configuration<br>Register                                                                                                         |

| 0x000C            | TPM_INT_<br>VECTOR_0       | 0x100C                            | TPM_INT_<br>VECTOR_1       | 0x200C            | TPM_INT_<br>VECTOR_2       | 0x300C             | TPM_INT_<br>VECTOR_3       | 0x400C            | TPM_INT_<br>VECTOR_4                                                    | SIRQ vector to be used<br>by the TPM (SIRQ pin<br>not available)                                                                            |

| 0x0013-<br>0x0010 | TPM_INT_<br>STATUS_0       | 0x1013-<br>0x1010                 | TPM_INT_<br>STATUS_1       | 0x2013-<br>0x2010 | TPM_INT_<br>STATUS_2       | 0x3013-<br>0x3010  | TPM_INT_<br>STATUS_3       | 0x4013-<br>0x4010 | TPM_INT_<br>STATUS_4                                                    | Shows which interrupt has occurred                                                                                                          |

| 0x0017-<br>0x0014 | TPM_INTF_<br>CAPABILITY_0  | 0x1017-<br>0x1014                 | TPM_INTF_<br>CAPABILITY_1  | 0x2017-<br>0x2014 | TPM_INTF_<br>CAPABILITY_2  | 0x3017-<br>0x3014  | TPM_INTF_<br>CAPABILITY_3  | 0x4017-<br>0x4014 | TPM_INTF_<br>CAPABILITY_4                                               | Provides the information<br>about supported<br>interrupts and the<br>characteristic of the<br>burstCount register of the<br>particular TPM. |

| 0x001A-<br>0x0018 | TPM_STS_0                  | 0x101A-<br>0x1018                 | TPM_STS_1                  | 0x201A-<br>0x2018 | TPM_STS_2                  | 0x301A-<br>0x3018  | TPM_STS_3                  | 0x401A-<br>0x4018 | TPM_STS_4                                                               | Status Register. Provides status of the TPM                                                                                                 |

| -                 | -                          | -                                 | -                          | -                 | -                          | -                  | -                          | 0x4020            | TPM_HASH_END                                                            | This signals the end of the hash operation in Locality 4.                                                                                   |

| 0x00027-          | TPM DATA FIFO 0            | 0x1027-                           | TPM DATA FIFO 1            | 0x2027-           | TPM DATA FIFO 2            | 0x3027-            | TPM DATA FIFO 3            | 0x4027-           | TPM_HASH_DATA /                                                         | ReadFIFO or WriteFIFO, depending on the current bus cycle (read or write). These four addresses are                                         |

| 0x0024            |                            | 0x1024   TPM_DATA_FIFO_1   0x2024 |                            | 0x3024            | 0x3024 TPW_DATA_           |                    | 0x4024                     | TPM_DATA_FIFO_4   | aliased to one inside the TPM. In Locality 4, it is the HASH_DATA FIFO. |                                                                                                                                             |

| -                 | -                          | -                                 | -                          | -                 | -                          | -                  | -                          | 0x4028            | TPM_HASH_START                                                          | This signals the start of the hash operation in Locality 4.                                                                                 |

| 0x0037-<br>0x0034 | TPM_DATA_CSUM_E<br>NABLE_0 | 0x1037-<br>0x1034                 | TPM_DATA_CSUM_E<br>NABLE_1 | 0x2037-<br>0x2034 | TPM_DATA_CSUM_E<br>NABLE_2 | 0x3037-<br>0x3034  | TPM_DATA_CSUM_E<br>NABLE_3 | 0x4037-<br>0x4034 | TPM_DATA_CSUM_E<br>NABLE_4                                              | Activation of the data checksum                                                                                                             |

| 0x003F-<br>0x0038 | TPM_DATA_CSUM_0            | 0x103F-<br>0x1038                 | TPM_DATA_CSUM_1            | 0x203F-<br>0x2038 | TPM_DATA_CSUM_2            | 0x303F-<br>0x3038  | TPM_DATA_CSUM_3            | 0x403F-<br>0x4038 | TPM_DATA_CSUM_4                                                         | Checksum data locations                                                                                                                     |

| Locality 0        | Register             | Locality 1        | Register             | Locality 2        | Register             | Locality 3        | Register             | Locality 4        | Register             | Register description                                                                                                                                                                                     |

|-------------------|----------------------|-------------------|----------------------|-------------------|----------------------|-------------------|----------------------|-------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Locality 0        | name                 | Locality I        | name                 | Locality 2        | name                 | Locality 3        | name                 | Locality 4        | name                 | Register description                                                                                                                                                                                     |

| 0x0080-<br>0x0083 | TPM_XDATA_<br>FIFO_0 | 0x1080-<br>0x1083 | TPM_XDATA_<br>FIFO_1 | 0x2080-<br>0x2083 | TPM_XDATA_<br>FIFO_2 | 0x3080-<br>0x3083 | TPM_XDATA_<br>FIFO_3 | 0x4080-<br>0x4083 | TPM_XDATA_<br>FIFO_4 | Extended ReadFIFO or WriteFIFO, depending on the current bus cycle (read or write). Transactions to this address may be any size from 1B to maxTransferCapability identified in the capability register. |

| 0x00BF-<br>0x0084 | Reserved             | 0x10BF-<br>0x1084 | Reserved             | 0x20BF-<br>0x2084 | Reserved             | 0x30BF-<br>0x3084 | Reserved             | 0x40BF-<br>0x4084 | Reserved             | -                                                                                                                                                                                                        |

| 0x0F03-<br>0x0F00 | TPM_DID_VID_0        | 0x1F03-<br>0x1F00 | TPM_DID_VID_1        | 0x2F03-<br>0x2F00 | TPM_DID_VID_2        | 0x3F03-<br>0x3F00 | TPM_DID_VID_3        | 0x4F03-<br>0x4F00 | TPM_DID_VID_4        | Vendor and device ID                                                                                                                                                                                     |

| 0x0F04            | TPM_RID_0            | 0x1F04            | TPM_RID_1            | 0x2F04            | TPM_RID_2            | 0x3F04            | TPM_RID_3            | 0x4F04            | TPM_RID_4            | Revision ID                                                                                                                                                                                              |

| 0x0F7F-<br>0x0F05 | Reserved             | 0x1F7F-<br>0x1F05 | Reserved             | 0x2F7F-<br>0x2F05 | Reserved             | 0x3F7F-<br>0x3F05 | Reserved             | 0x4F7F-<br>0x4F05 | Reserved             | -                                                                                                                                                                                                        |

# ST33KTPM-IDevID Serial peripheral interface (SPI) and TPM registers

# 4.2.2 Command response buffer interface

Table 4. List of CRB register space addresses

| Locality 0        | Register                       | Locality 1        | Register<br>name               | Locality 2        | Register<br>name               | Locality 3         | Register<br>name               | Locality 4         | Register<br>name               |

|-------------------|--------------------------------|-------------------|--------------------------------|-------------------|--------------------------------|--------------------|--------------------------------|--------------------|--------------------------------|

| 0x0003-<br>0x0000 | TPM_LOC_STATE_0                | 0x1003-<br>1000   | TPM_LOC_STATE_1                | 0x2000-<br>0x2003 | TPM_LOC_STATE_2                | 0x3000-<br>0x3003  | TPM_LOC_STATE_3                | 0x4000-<br>0x4003  | TPM_LOC_STATE_4                |

| 0x000B-<br>0x0008 | TPM_LOC_CTRL_0                 | 0x100B-<br>1008   | TPM_LOC_CTRL_1                 | 0x200B-<br>0x2008 | TPM_LOC_CTRL_2                 | 0x300B-<br>0x30008 | TPM_LOC_CTRL_3                 | 0x400B-<br>0x4008  | TPM_LOC_CTRL_4                 |

| 0x000F-<br>0x000C | TPM_LOC_STS_0                  | 0x100F-<br>100C   | TPM_LOC_STS_1                  | 0x200F-<br>0x200C | TPM_LOC_STS_2                  | 0x300F-<br>0x300C  | TPM_LOC_STS_3                  | 0x400F-<br>0x400C  | TPM_LOC_STS_4                  |

| 0x002F-<br>0x0010 | Reserved                       | 0x102F-<br>1010   | Reserved                       | 0x202F-<br>0x2010 | Reserved                       | 0x302F-<br>0x3010  | Reserved                       | 0x402F-<br>0x4010  | Reserved                       |

| 0x0037-<br>0x0030 | TPM_INTERFACE_<br>IDENTIFIER_0 | 0x1037-<br>1030   | TPM_INTERFACE_<br>IDENTIFIER_1 | 0x2037-<br>0x2030 | TPM_INTERFACE_<br>IDENTIFIER_2 | 0x3037-<br>0x3030  | TPM_INTERFACE_<br>IDENTIFIER_3 | 0x4037-<br>0x4030  | TPM_INTERFACE_<br>IDENTIFIER_4 |

| 0x003F-<br>0x0038 | TPM_CRB_CTRL_EXT_0             | 0x103F-<br>0x1038 | Reserved                       | 0x203F-<br>0x2038 | Reserved                       | 0x303F-<br>0x3038  | Reserved                       | 0x403F-<br>0x4038  | Reserved                       |

| 0x0043-<br>0x0040 | TPM_CRB_CTRL_REQ_0             | 0x1043-<br>0x1040 | TPM_CRB_CTRL_REQ_1             | 0x2043-<br>0x2040 | TPM_CRB_CTRL_REQ_2             | 0x3043-<br>0x3040  | TPM_CRB_CTRL_REQ_3             | 0x4043-<br>0x4040  | TPM_CRB_CTRL_REQ_4             |

| 0x0047-<br>0x0044 | TPM_CRB_CTRL_STS_0             | 0x1047-<br>0x1044 | TPM_CRB_CTRL_STS_1             | 0x2047-<br>0x2044 | TPM_CRB_CTRL_STS_2             | 0x3047-<br>0x3044  | TPM_CRB_CTRL_STS_3             | 0x4047-<br>0x4044  | TPM_CRB_CTRL_STS_4             |

| 0x004B-<br>0x0048 | TPM_CRB_CTRL_<br>CANCEL_0      | 0x104B-<br>0x1048 | TPM_CRB_CTRL_<br>CANCEL_1      | 0x204B-<br>0x2048 | TPM_CRB_CTRL_<br>CANCEL_2      | 0x304B-<br>0x3048  | TPM_CRB_CTRL_<br>CANCEL_3      | 0x404B-<br>0x14048 | TPM_CRB_CTRL_<br>CANCEL_4      |

| 0x004F-<br>0x004C | TPM_CRB_CTRL_START_0           | 0x104F-<br>0x104C | TPM_CRB_CTRL_START_1           | 0x204F-<br>0x204C | TPM_CRB_CTRL_ START_2          | 0x304F-<br>0x304C  | TPM_CRB_CTRL_ START_3          | 0x404F-<br>0x404C  | TPM_CRB_CTRL_START_4           |

| 0x0057-<br>0x0050 | TPM_CRB_CTRL_INT_0             | 0x1057-<br>0x1050 | TPM_CRB_CTRL_INT_1             | 0x2057-<br>0x2050 | TPM_CRB_CTRL_INT_2             | 0x3057-<br>0x3050  | TPM_CRB_CTRL_INT_3             | 0x4057-<br>0x4050  | TPM_CRB_CTRL_INT_4             |

| 0x005B-<br>0x0058 | TPM_CRB_CTRL_CMD_<br>SIZE_0    | 0x105B-<br>0x1058 | TPM_CRB_CTRL_CMD_<br>SIZE_1    | 0x205B-<br>0x2058 | TPM_CRB_CTRL_CMD_<br>SIZE_2    | 0x305B-<br>0x3058  | TPM_CRB_CTRL_CMD_<br>SIZE_3    | 0x405B-<br>0x4058  | TPM_CRB_CTRL_CMD_<br>SIZE_4    |

| 0x005F-<br>0x005C | TPM_CRB_CTRL_CMD_<br>LADDR_0   | 0x105F-<br>0x105C | TPM_CRB_CTRL_CMD_<br>LADDR_1   | 0x205F-<br>0x205C | TPM_CRB_CTRL_CMD_<br>LADDR_2   | 0x305F-<br>0x305C  | TPM_CRB_CTRL_CMD_<br>LADDR_3   | 0x405F-<br>0x405C  | TPM_CRB_CTRL_CMD_<br>LADDR_4   |

| 0x0063-<br>0x0060 | TPM_CRB_CTRL_CMD_<br>HADDR_0   | 0x1063-<br>0x1060 | TPM_CRB_CTRL_CMD_<br>HADDR_1   | 0x2063-<br>0x2060 | TPM_CRB_CTRL_CMD_<br>HADDR_2   | 0x3063-<br>0x3060  | TPM_CRB_CTRL_CMD_<br>HADDR_3   | 0x4063-<br>0x4060  | TPM_CRB_CTRL_CMD_<br>HADDR_4   |

| 0x0067-<br>0x0064 | TPM_CRB_CTRL_RSP_<br>SIZE_0    | 0x1067-<br>0x1064 | TPM_CRB_CTRL_RSP_<br>SIZE_1    | 0x2067-<br>0x2064 | TPM_CRB_CTRL_RSP_<br>SIZE_2    | 0x3067-<br>0x3064  | TPM_CRB_CTRL_RSP_<br>SIZE_3    | 0x4067-<br>0x4064  | TPM_CRB_CTRL_RSP_<br>SIZE_4    |

| 0x006F-<br>0x0068 | TPM_CRB_CTRL_RSP_<br>ADDR_0    | 0x106F-<br>0x1068 | TPM_CRB_CTRL_RSP_<br>ADDR_1    | 0x206F-<br>0x2068 | TPM_CRB_CTRL_RSP_<br>ADDR_2    | 0x306F-<br>0x3068  | TPM_CRB_CTRL_RSP_<br>ADDR_3    | 0x406F-<br>0x4068  | TPM_CRB_CTRL_RSP_<br>ADDR_4    |

| 0x007F-<br>0x0070 | Reserved                       | 0x107F-<br>0x1070 | Reserved                       | 0x207F-<br>0x2070 | Reserved                       | 0x307F-<br>0x3070  | Reserved                       | 0x407F-<br>0x4070  | Reserved                       |

| 0x0880-<br>0x0080 | TPM_CRB_DATA_<br>BUFFER_0      | 0x1880-<br>0x1080 | TPM_CRB_DATA_<br>BUFFER_1      | 0x2880-<br>0x2080 | TPM_CRB_DATA_<br>BUFFER_2      | 0x3880-<br>0x3080  | TPM_CRB_DATA_<br>BUFFER_3      | 0x4880-<br>0x4080  | TPM_CRB_DATA_<br>BUFFER_4      |

| 0x0FFF-<br>0x0881 | Reserved                       | 0x1FFF-<br>0x1881 | Reserved                       | 0x2FFF-<br>0x2881 | Reserved                       | 0x3FFF-<br>0x3881  | Reserved                       | 0x4FFF-<br>0x4881  | Reserved                       |

# 4.3 Register descriptions

Detailed descriptions of each register can be found in *TCG* PC client specific platform *TPM* profile for [PTP 2.0 r1.05].

#### 4.4 Additional information

- The *TPM* implements a PIRQ but does not implement an SIRQ pin.

- Any write operation to the TPM ACCESS x register with more than one field set to a '1' is not accepted.

- Interface capability:

- TPM STS x.burstCount is dynamic.

- Interrupt detection mode "Level low" is supported (other modes "Level high" and "Edge" are not supported).

- Interrupts localityChange and dataAvailable are supported (Interrupt stsValid and commandReady are not supported).

- Transaction size:

- The TPM accepts transactions to offset 0x0024-0x0027 which are of lengths from 1 to 32 bytes (legacy FIFO).

- The TPM accepts transactions to offset 0x0081-0x0083 which are of lengths from 1 to 32 bytes (extended FIFO).

- Vendor and device ID for the TPM

- TPM\_DID\_VID\_X = 0x0003104A; // DID = 0x0003 and VID = 0x104A (ID of STMicroelectronics defined by [Vendor Registry])

- Revision ID for the TPM

- TPM RID X = 0x03; // 0xFFFFFF = reserved

- TPM\_RID\_X is a counter incremented by 1 when the HWINTF library version is updated in future products. TPM\_RID\_X identifies the HWINTF library (*TPM* bus interface driver) version in the register level.

- TPM\_DATA\_CSUM\_ENABLE and TPM\_DATA\_CSUM are available in the *SPI* interface as already defined in [PTP 2.0 r1.05] for *I*<sup>2</sup>*C* interface. They are managed only on the current active locality.

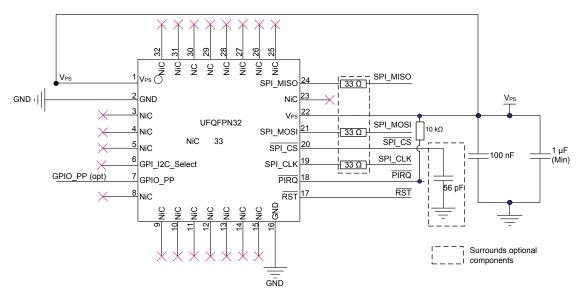

#### 4.5 Recommendations

For optimized performance results, the use of an extended data FIFO with 32-byte burst is mandatory. When the falling edge occurs on the  $\overline{\text{SPI\_CS}}$  signal, SPI\_CLK must be at the low logic level as defined in Figure 12.

If the device does not show this behavior, add a 56 pF capacitor (example value) on the SPI\_CS line to slow the falling edge on SPI\_NSS or SPI\_CS.

DS15011 - Rev 1 page 13/97

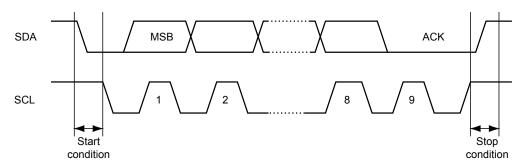

# 5 I<sup>2</sup>C interface protocol

#### 5.1 TCG PC client options

The implemented protocol is compliant with the *PTP* specification (see [PTP 2.0 r1.05] for details) with the following options:

- Bus speed is limited to 1 Mbits/s.

- 10-bit target address is NOT supported.

- Target address reconfiguration is supported in the range of 0x08 to 0x77.

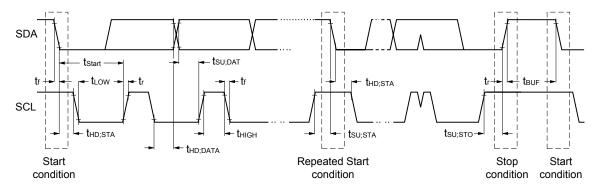

- Clock stretching is used.

- 1.8 V and 3.3 V are supported.

- Five localities are supported.

- Guard time is lower than 20 μs.

- The supported interrupts are "locality change" and "data available".

- Burst count is dynamic. The maximum burst is 256 bytes.

- Data checksum is supported.

- Default I<sup>2</sup>C address used: 0x2E.

#### 5.2 Platform constraints

This section explains the constraints on the ST33KTPM-IDevID TPM device.

#### 5.2.1 I<sup>2</sup>C bus activities

As there is no line to select an  $I^2C$  device, all the bus activities wake up the ST33KTPM-IDevID TPM device when it is in idle mode, and delay its response when it is in execution mode only if this is the TPM address.

To avoid loading the  $I^2C$  bus and the ST33KTPM-IDevID, it is necessary to adapt the TPM response availability check to leave enough time for the device to process the commands. To do so, prefer interrupts on "data available" events when possible. If not possible, a polling mechanism with an incremental delay can also be used.

#### 5.2.2 TPM acknowledgement

Sometimes, the ST33KTPM-IDevID TPM device is in low-power mode and cannot process an  $I^2C$  transaction immediately. In this case, the transaction is not acknowledged. The host has to repeat it until the TPM device acknowledges the transaction.

When the ST33KTPM-IDevID *TPM* device is in low power mode, it requires about 80µs to wake up. For a clock at 1 MHz, the three first *TPM* accesses are *NACK* (with a guard time equal to 20 µs).

#### 5.2.3 Clock stretching

In the case of a DRTM or H-CRTM sequence, the ST33KTPM-IDevID *TPM* uses clock stretching to control the hash data flow. Clock stretching is activated on the second frame following the hash data or the end of the hash. The duration can be up to 2 ms for the end of the hash.

DS15011 - Rev 1 page 14/97

# 6 Integration requirements

# 6.1 Integration information

- The duration of TPM\_HASH\_DATA exceeds 250 µs if SHA-384 and dual-bank management are implemented.

- In Windows<sup>®</sup> 10 or 11, for using a 3072-bit or 4096-bit *RSA* key, update the following, if it exists in the registry editor:

#### For a 3072-bit RSA key:

[HKEY\_LOCAL\_MACHINE\SYSTEM\CurrentControlSet\Services\TPM] "TimeoutCommandCreate"=dword:0057E40

For a 4096-bit RSA key:

[HKEY\_LOCAL\_MACHINE\SYSTEM\CurrentControlSet\Services\TPM] "TimeoutCommandCreate"=dword:00AFC80 .

• In linux, refer to tpm.h, under directory drivers/char/tpm, TPM2\_DURATION\_LONG\_LONG (300000 ms by default), must be increased when using a 3072-bit or 4096-bit RSA key. The value is defined in Table 2.

Interrupt mode with Windows® could be activated under three conditions:

- PIRQ signal connected and driven by Host controller

- UEFI activate TPM Interrupt mode

- Add in Windows<sup>®</sup> registry editor (create item if does not exist):

[HKEY\_LOCAL\_MACHINE\SYSTEM\CurrentControlSet\Services\TPM]

"EnableInterruptSupport"=dword:00000001

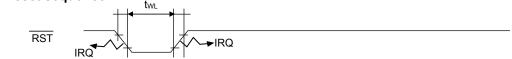

# 6.2 TPM Interrupt signal usage (PIRQ) driver implementation

PIRQ is the TPM interrupt signal.

The *TPM* host drivers should enable the PIRQ before using it with the TPM\_INT\_ENABLE\_x or TPM\_CRB\_INT\_ENABLE\_x registers defined in [PTP 2.0 r1.05].

Once an interrupt is asserted, the *TPM* do not assert another interrupt until it receives a TPM\_EOI (End\_Of\_Interrupt), even if new events that could cause an interrupt occur.

When an event occurs that causes the *TPM* to signal an interrupt (PIRQ signal falling edge), the *TPM* host must read the appropriate fields in the TPM\_INT\_STATUS\_x or TPM\_CRB\_INT\_STS\_x register to determine the cause (for instance localityChangeIntOccured or dataAvailIntOccured), and take appropriate action.

After that event, the *TPM* host runs TPM\_EOI through the TPM\_INT\_STATUS\_x or the TPM\_CRB\_INT\_STS\_x register.

The TPM interrupt enablement sequence is:

Table 5. TPM interrupt enable sequence

| Step number | Description                                                                                                                               |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|             | The host driver reads the TPM_INT_ENABLE register to get the interrupt polarity.                                                          |  |  |  |  |

|             | This SPI frame gives:                                                                                                                     |  |  |  |  |

|             | MOSI: 0x83 0xD4 0x00 0x08 0x00 0x00 0x00 0x00 0x00                                                                                        |  |  |  |  |

| Cton 1      | MISO: 0x00 0x00 0x00 0x00 0x01 0x08 0x00 0x00                                                                                             |  |  |  |  |

| Step 1      | TISREAD: locality 0: register 008 (TPM_INT_ENABLE_0): bytes number: 4:                                                                    |  |  |  |  |

|             | Data 08:00:00:00:                                                                                                                         |  |  |  |  |

|             | Bit 3 set : typePolarity : Low level                                                                                                      |  |  |  |  |

|             | Default value for this register                                                                                                           |  |  |  |  |

|             | The host driver writes the TPM_INT_ENABLE register to enable the globalIntEnable and dataAvailIntEnable bits, and the interrupt polarity. |  |  |  |  |

| Step 2      | This SPI frame gives:                                                                                                                     |  |  |  |  |

|             | MOSI: 0x03 0xD4 0x00 0x08 [Flowcontrol] 0x09 0x00 0x00 0x80                                                                               |  |  |  |  |

|             | MISO: 0x00 0x00 0x00 0x00 [Flowcontrol] 0xFF 0xFF 0xFF 0xFF                                                                               |  |  |  |  |

DS15011 - Rev 1 page 15/97

| Step number | Description                                                                                                     |  |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|             | TISWRITE: locality 0: register 008 (TPM_INT_ENABLE_0): bytes number: 4:                                         |  |  |  |  |  |

|             | Data 09:00:00:80:                                                                                               |  |  |  |  |  |

|             | Bit 3 set : typePolarity : Low level                                                                            |  |  |  |  |  |

|             | Bit 0 set : dataAvailIntEnable : Enabled                                                                        |  |  |  |  |  |

|             | Bit 31 set : globalIntEnable : Interrupts controlled by individual bits                                         |  |  |  |  |  |

|             | The host driver reads the TPM_INT_ENABLE register to check whether the write operation has been executed.       |  |  |  |  |  |

|             | This SPI frame gives:                                                                                           |  |  |  |  |  |

|             | MOSI: 0x83 0xD4 0x00 0x08 0x00 0x00 0x00 0x00 0x00                                                              |  |  |  |  |  |

|             | MISO: 0x00 0x00 0x00 0x00 0x01 0x09 0x00 0x00                                                                   |  |  |  |  |  |

|             | TISREAD: locality 0: register 008 (TPM_INT_ENABLE_0): bytes number: 4:                                          |  |  |  |  |  |

| Step 3      | Data 09:00:00:80:                                                                                               |  |  |  |  |  |

|             | Bit 3 set : typePolarity : Low level                                                                            |  |  |  |  |  |

|             | Bit 0 set : dataAvailIntEnable : Enabled                                                                        |  |  |  |  |  |

|             | Bit 31 set : globalIntEnable : Interrupts controlled by individual bits                                         |  |  |  |  |  |

|             | [TPM state is in Command execution see figure 3 [PTP 2.0 r1.05]]                                                |  |  |  |  |  |

|             | Interrupt PIRQ is in Low level                                                                                  |  |  |  |  |  |

|             | Check interrupt cause.                                                                                          |  |  |  |  |  |

|             | MOSI: 0x80 0xD4 0x00 0x10 0x00 0x00                                                                             |  |  |  |  |  |

|             | MISO: 0x00 0x00 0x00 0x00 0x01 0x01                                                                             |  |  |  |  |  |

| Step 4      | TISREAD: locality 0: register 010 (TPM_INT_STATUS_0): bytes number: 1:                                          |  |  |  |  |  |

|             | Data 01:                                                                                                        |  |  |  |  |  |

|             | Bit 0 : dataAvailIntOccured : interrupt corresponds to "Data available": <i>TPM</i> answer is ready to be read. |  |  |  |  |  |

|             | [Get TPM answer]                                                                                                |  |  |  |  |  |

|             | Send TPM_EOI                                                                                                    |  |  |  |  |  |

|             | This SPI frame gives:                                                                                           |  |  |  |  |  |

|             | MOSI: 0x00 0xD4 0x00 0x10 [Flowcontrol] 0x01 0x01                                                               |  |  |  |  |  |

| Step 5      | MISO: 0x00 0x00 0x00 0x00 [Flowcontrol] 0x01 0xFF                                                               |  |  |  |  |  |

|             | TISWRITE : locality 0: register 010 (TPM_INT_ENABLE_0): bytes number: 1:                                        |  |  |  |  |  |

|             | Data 01:                                                                                                        |  |  |  |  |  |

|             | Bit 0 set : dataAvailIntOccured : Writing a 1 to this field clears the dataAvailIntOccured interrupt.           |  |  |  |  |  |

DS15011 - Rev 1 page 16/97

# 7 TPM 2.0 library

# 7.1 Supported commands

The commands supported in the library mode TPM 2.0 are compliant with [TPM 2.0 P1 r159], [TPM 2.0 P2 r159], [TPM 2.0 P3 r159], [TPM 2.0 P4 r159], and [PTP 2.0 r1.05].

Table 6. Summary of supported commands

|                         | Commands                 | Support          |

|-------------------------|--------------------------|------------------|

|                         | _TPM_INIT                | Х                |

| O'ana ala               | _TPM_HashStart           | X                |

| Signals                 | _TPM_HashData            | Х                |

|                         | _TPM_HashEnd             | Х                |

| Startup                 | TPM2_Startup             | Х                |

|                         | TPM2_Shutdown            | X                |

|                         | TPM2_IncrementalSelfTest | X                |

| Testing                 | TPM2_SelfTest            | X                |

|                         | TPM2_GetTestResult       | X                |

| Cassian commanda        | TPM2_StartAuthSession    | X                |

| Session commands        | TPM2_PolicyRestart       | X                |

|                         | TPM2_Create              | X                |

|                         | TPM2_Load                | X                |

|                         | TPM2_LoadExternal        | X                |

|                         | TPM2_ReadPublic          | X                |

| Object commands         | TPM2_ActivateCredential  | X                |

|                         | TPM2_MakeCredential      | X                |

|                         | TPM2_Unseal              | X                |

|                         | TPM2_CreateLoaded        | X                |

|                         | TPM2_ObjectChangeAuth    | X                |

|                         | TPM2_Duplicate           | X                |

| Duplicate commands      | TPM2_Rewrap              | X                |

|                         | TPM2_Import              | X                |

|                         | TPM2_RSA_Encrypt         | X                |

|                         | TPM2_RSA_Decrypt         | X                |

| Asymmetric primitives   | TPM2_ECDH_KeyGen         | X                |

| Asymmetric primitives   | TPM2_ECDH_ZGen           | X                |

|                         | TPM2_ECC_Parameters      | X                |

|                         | TPM2_ZGen_2Phase         | Х                |

|                         | TPM2_EncryptDecrypt      | X <sup>(1)</sup> |

| Summetrie primitives    | TPM2_EncryptDecrypt2     | X <sup>(1)</sup> |

| Symmetric primitives    | TPM2_Hash                | X                |

|                         | TPM2_HMAC                | X                |

| Random number generator | TPM2_GetRandom           | Х                |

DS15011 - Rev 1 page 17/97

|                                      | Commands                       | Support |

|--------------------------------------|--------------------------------|---------|

| Random number generator              | TPM2_StirRandom                | X       |

|                                      | TPM2_HMAC_Start                | X       |

|                                      | TPM2_MAC_Start                 | -       |

|                                      | TPM2_HashSequenceStart         | X       |

| Hash/HMAC/Event sequences            | TPM2_SequenceUpdate            | X       |

| ,                                    | TPM2_SequenceComplete          | X       |

|                                      | TPM2_EventSequenceComplete     | X       |

|                                      | TPM2_Certify                   | X       |

|                                      | TPM2_CertifyCreation           | X       |

|                                      | TPM2_Quote                     | X       |

| Attestation commands                 | TPM2_GetSessionAuditDigest     | X       |

|                                      | TPM2_GetCommandAuditDigest     | X       |

|                                      | TPM2_GetTime                   | X       |

|                                      | TPM2_CertifyX509               | X       |

|                                      | TPM2_Commit                    | X       |

| Anonymous attestation                | TPM2_ECC_Ephemeral             | X       |

|                                      | TPM2_VerifySignature           | X       |

| Signature verification               | TPM2_Sign                      | X       |

| Command audit                        | TPM2_SetCommandCodeAuditStatus | X       |

|                                      | TPM2_PCR_Extend                | X       |

|                                      | TPM2_PCR_Event                 | X       |

|                                      | TPM2_PCR_Read                  | X       |

| Integrity collection (PCR)           | TPM2_PCR_Allocate              | X       |

|                                      | TPM2_PCR_SetAuthPolicy         | -       |

|                                      | TPM2_PCR_SetAuthValue          | -       |

|                                      | TPM2_PCR_Reset                 | X       |

|                                      | TPM2_PolicySigned              | X       |

|                                      | TPM2_PolicySecret              | X       |

|                                      | TPM2_PolicyTicket              | X       |

|                                      | TPM2_PolicyOR                  | X       |

|                                      | TPM2_PolicyPCR                 | X       |

|                                      | TPM2_PolicyLocality            | X       |

|                                      | TPM2_PolicyNV                  | X       |

| Enhanced authorization (EA) commands | TPM2_PolicyCounterTimer        | X       |

|                                      | TPM2_PolicyCommandCode         | X       |

|                                      | TPM2_PolicyPhysicalPresence    | Х       |

|                                      | TPM2_PolicyCpHash              | Х       |

|                                      | TPM2_PolicyNameHash            | Х       |

|                                      | TPM2_PolicyDuplicationSelect   | X       |

|                                      | TPM2_PolicyAuthorize           | Х       |

|                                      | TPM2_PolicyAuthValue           | X       |

page 18/97

|                                      | Commands                        | Support |

|--------------------------------------|---------------------------------|---------|

|                                      | TPM2_PolicyPassword             | Х       |

|                                      | TPM2_PolicyGetDigest            | Х       |

| Enhanced authorization (EA) commands | TPM2_PolicyTemplate             | Х       |

|                                      | TPM2_PolicyAuthorizeNV          | X       |

|                                      | TPM2_PolicyNvWritten            | X       |

|                                      | TPM2_CreatePrimary              | Х       |

|                                      | TPM2_HierarchyControl           | X       |

|                                      | TPM2_SetPrimaryPolicy           | X       |

|                                      | TPM2_Change_PPS                 | Х       |

| Hierarchy commands                   | TPM2_Change_EPS                 | X       |

|                                      | TPM2_Clear                      | X       |

|                                      | TPM2_ClearControl               | X       |

|                                      | TPM2_HierarchyChangeAuth        | Х       |

|                                      | TPM2_DictionaryAttackLockReset  | Х       |

| Dictionary attack functions          | TPM2_DictionaryAttackParameters | Х       |

|                                      | TPM2_PP_Commands                | Х       |

| Miscellaneous management functions   | TPM2_SetAlgorithmSet            | -       |

|                                      | TPM2_FieldUpgradeStart          | _(2)    |

| Field upgrade                        | TPM2_FieldUpgradeData           | _(3)    |

|                                      | TPM2_FirmwareRead               | -       |

|                                      | TPM2_ContextSave                | Х       |

|                                      | TPM2_ContextLoad                | Х       |

| Context management                   | TPM2_FlushContext               | Х       |

|                                      | TPM2_EvictControl               | Х       |

|                                      | TPM2_ReadClock                  | Х       |

| Clocks and timers                    | TPM2_ClockSet                   | Х       |

|                                      | TPM2_ClockRateAdjust            | Х       |

|                                      | TPM2_GetCapability              | Х       |

| Capability commands                  | TPM2_SetCapability              | _(4)    |

|                                      | TPM2_TestParms                  | Х       |

|                                      | TPM2_NV_DefineSpace             | Х       |

|                                      | TPM2_NV_UndefineSpace           | Х       |

|                                      | TPM2_NV_UndefineSpaceSpecial    | Х       |

|                                      | TPM2_NV_ReadPublic              | Х       |

|                                      | TPM2_NV_Write                   | Х       |

| Nonvolatile storage                  | TPM2_NV_Increment               | Х       |

|                                      | TPM2_NV_Extend                  | Х       |

|                                      | TPM2_NV_SetBits                 | Х       |

|                                      | TPM2_NV_WriteLock               | Х       |

|                                      | TPM2_NV_GlobalWriteLock         | Х       |

|                                      | TPM2_NV_Read                    | Х       |

DS15011 - Rev 1 page 19/97

|                      | Commands                               | Support          |

|----------------------|----------------------------------------|------------------|

|                      | TPM2_NV_ReadLock                       | Х                |

| Nonvolatile storage  | TPM2_NV_ChangeAuth                     | X                |

|                      | TPM2_NV_Certify                        | Х                |

|                      | TPM2_VendorCmdSetMode                  | Х                |

|                      | TPM2_VendorCmdSetCommandSet            | Х                |

|                      | TPM2_VendorCmdSetCommandSetLock        | Х                |

|                      | TPM2_VendorCmdRestoreEK                | Х                |

| Barriston areas de   | TPM2_VendorCmdFieldUpgradeStart        | Х                |

| Proprietary commands | TPM2_VendorCmdFieldUpgradeData         | Х                |

|                      | TPM2_VendorCmdGPIOConfig               | X <sup>(1)</sup> |

|                      | TPM2_VendorCmdGetRandom2               | Х                |

|                      | TPM2_VendorCmdGetRandom800_90B         | Х                |

|                      | TPM2_VendorCmdChangeObjectDeletionAuth | X <sup>(1)</sup> |

- 1. Commands deactivated by default. See TPM command support configuration.

- 2. Handled by TPM2\_VendorCmdFieldUpgradeStart

- 3. Handled by TPM2\_VendorCmdFieldUpgradeData.

- 4. TPM command defined in Appendix B: Referenced documents

#### 7.2 **Cryptographic support**

Table 7. Cryptographic algorithm support table

| Algorithm Name    | Value   | Support | Comment                          |

|-------------------|---------|---------|----------------------------------|

| TPM_ALG_ERROR     | 0x0000  | -       | -                                |

| TPM_ALG_RSA       | 0x0001  | Х       | 1024, 2048, 3072 and 4096 bits   |

| TPM_ALG_SHA       | 0x0004  | Х       | -                                |

| TPM_ALG_SHA1      | 0x0004  | Х       | -                                |

| TPM ALG HMAC      | 0x0005  | X       | SHA-1, SHA-256, SHA-384, SHA-512 |

| TFW_ALG_TIMAC     | 0.00003 | ^       | SHA3-256 and SHA3-384            |

| TPM_ALG_AES       | 0x0006  | X       | 128, 192, 256 bits               |

| TPM_ALG_MGF1      | 0x0007  | X       | -                                |

| TPM_ALG_KEYEDHASH | 0x0008  | Х       | -                                |

| TPM_ALG_XOR       | 0x000A  | Х       | -                                |

| TPM_ALG_SHA256    | 0x000B  | Х       | -                                |

| TPM_ALG_SHA384    | 0x000C  | Х       | -                                |

| TPM_ALG_SHA512    | 0x000D  | X       | -                                |

| TPM_ALG_NULL      | 0x0010  | Х       | -                                |

| TPM_ALG_SM3_256   | 0x0012  | -       | -                                |

| TPM_ALG_SM4       | 0x0013  | -       | -                                |

| TPM_ALG_RSASSA    | 0x0014  | X       | -                                |

| TPM_ALG_RSAES     | 0x0015  | Х       | -                                |

| TPM_ALG_RSAPSS    | 0x0016  | Х       | -                                |

| TPM_ALG_OAEP      | 0x0017  | Х       | -                                |

page 20/97

| Algorithm Name         | Value  | Support | Comment                               |

|------------------------|--------|---------|---------------------------------------|

| TPM_ALG_ECDSA          | 0x0018 | Х       | -                                     |

| TPM_ALG_ECDH           | 0x0019 | X       | -                                     |

| TPM_ALG_ECDAA          | 0x001A | X       | -                                     |

| TPM_ALG_SM2            | 0x001B | -       | -                                     |

| TPM_ALG_ECSCHNORR      | 0x001C | X       | -                                     |

| TPM_ALG_ECMQV          | 0x001D | -       | -                                     |

| TPM_ALG_KDF1_SP800_56A | 0x0020 | X       | -                                     |

| TPM_ALG_KDF2           | 0x0021 | -       | -                                     |

| TPM_ALG_KDF1_SP800_108 | 0x0022 | X       | -                                     |

| TPM_ALG_ECC            | 0x0023 | X       | ECC crypto support summary            |

| TPM_ALG_SYMCIPHER      | 0x0025 | X       | -                                     |

| TPM_ALG_CAMELLIA       | 0x0026 | -       | -                                     |

| TPM_ALG_SHA3_256       | 0x0027 | X       | -                                     |

| TPM_ALG_SHA3_384       | 0x0028 | X       | -                                     |

| TPM_ALG_SHA3_512       | 0x0029 | -       | -                                     |

| TPM_ALG_SHAKE128       | 0x002A | -       | -                                     |

| TPM_ALG_SHAKE256       | 0x002B | -       | -                                     |

| TPM_ALG_SHAKE256_192   | 0x002C | -       | -                                     |

| TPM_ALG_SHAKE256_256   | 0x002D | -       | -                                     |

| TPM_ALG_SHAKE256_512   | 0x002E | -       | -                                     |

| TPM_ALG_CMAC           | 0x003F | -       | -                                     |

| TPM_ALG_CTR            | 0x0040 | Х       | -                                     |

| TPM_ALG_OFB            | 0x0041 | Х       | -                                     |

| TPM_ALG_CBC            | 0x0042 | Х       | -                                     |

| TPM_ALG_CFB            | 0x0043 | X       | -                                     |

| TPM_ALG_ECB            | 0x0044 | Х       | -                                     |

| TPM_ALG_CCM            | 0x0050 | -       | -                                     |

| TPM_ALG_GCM            | 0x0051 | -       | -                                     |

| TPM_ALG_KW             | 0x0052 | -       | -                                     |

| TPM_ALG_KWP            | 0x0053 | -       | -                                     |

| TPM_ALG_EAX            | 0x0054 | -       | -                                     |

| TPM_ALG_EDDSA          | 0x0060 | -       | -                                     |

| TPM_ALG_EDDSA_PH       | 0x0061 | -       | -                                     |

| TPM_ALG_LMS            | 0x0070 | -       | For hybrid signature in field upgrade |

| TPM_ALG_XMSS           | 0x0071 | -       | -                                     |

| TPM_ALG_KEYEDXOF       | 0x0080 | -       | -                                     |

| TPM_ALG_KMACXOF128     | 0x0081 | -       | -                                     |

| TPM_ALG_KMACXOF256     | 0x0082 | -       | -                                     |

| TPM_ALG_KMAC128        | 0x0090 | -       | -                                     |

| TPM_ALG_KMAC256        | 0x0091 | -       | -                                     |

DS15011 - Rev 1 page 21/97

| Table 8. | <b>ECC</b> | crypto | support | summary |

|----------|------------|--------|---------|---------|

|----------|------------|--------|---------|---------|

| Name                | Value  | Support | Comments               |

|---------------------|--------|---------|------------------------|

| TPM_ECC_NONE        | 0x0000 | -       | -                      |

| TPM_ECC_NIST_P192   | 0x0001 | -       | -                      |

| TPM_ECC_NIST_P224   | 0x0002 | -       | -                      |

| TPM_ECC_NIST_P256   | 0x0003 | X       | -                      |

| TPM_ECC_NIST_P384   | 0x0004 | X       | -                      |

| TPM_ECC_NIST_P521   | 0x0005 | -       | -                      |

| TPM_ECC_BN_P256     | 0x0010 | X       | Curve to support ECDAA |

| TPM_ECC_BN_P638     | 0x0011 | -       | Curve to support ECDAA |

| TPM_ECC_SM2_P256    | 0x0020 | -       | -                      |

| TPM_ECC_BP_P256_R1  | 0x0030 | -       | -                      |

| TPM_ECC_BP_P384_R1  | 0x0031 | -       | -                      |

| TPM_ECC_BP_P512_R1  | 0x0032 | -       | -                      |

| TPM_ECC_CURVE_25519 | 0x0040 | -       | Curve to support EdDSA |

| TPM_ECC_CURVE_448   | 0x0041 | -       | Curve to support EdDSA |

#### 7.3 PCR banks

The default configuration supports two banks of 24 PCRs:

- One for SHA256 PCRs

- One for SHA384 PCRs

TPM2\_PCR\_Allocate can be used to change the default bank configuration. It is possible to allocate two banks of 24 PCRs for each maximum hash size (one bank for SHA-384 and one bank for SHA-512).

If TPM2\_PCR\_Allocate attempts to allocate more than two banks, the *TPM* device returns the TPM\_RC\_NO\_RESULT error.

# 7.4 Dictionary attack mitigation

All information about DAM is available in [TPM 2.0 P1 r159], section 19.8.2 Lockout Mode Configuration Parameters.

maxTries (NV) – The TPM is in Lockout mode as long as failedTries equals this value. When a new owner is installed, maxTries is set to its default value as specified in the relevant platform-specific specification.

**recoveryTime** (NV) – This value indicates, in seconds, the rate at which failedTries is decremented. This can be set to a large value ( $2^{32}$  - 1) which essentially inhibits automatic exit from Lockout mode. When a new owner is installed, this value is set to its default value as specified in the relevant platform-specific specification.

**lockoutRecovery** (*NV*) – This value indicates the delay in seconds between attempts to use lockoutAuth. The time delay only applies after an authorization failure using lockoutAuth. A value of zero indicates that a system reboot (TPM2 Startup(TPM SU CLEAR)) is required between lockout attempts.

The parameters maxTries, recoveryTime, and lockoutRecovery are set with

TPM2\_DictionaryAttackParameters(). This command requires authorization with lockoutAuth.

The DAM parameters have the following values:

- maxTries = 32 (dec)

- recoveryTime = 7200 (dec) seconds (2 hours)

- lockoutRecovery = 86400 (dec) seconds (24 hours)

DS15011 - Rev 1 page 22/97

# 7.5 Resource availability and capability

Table 9. Resource availability and capability