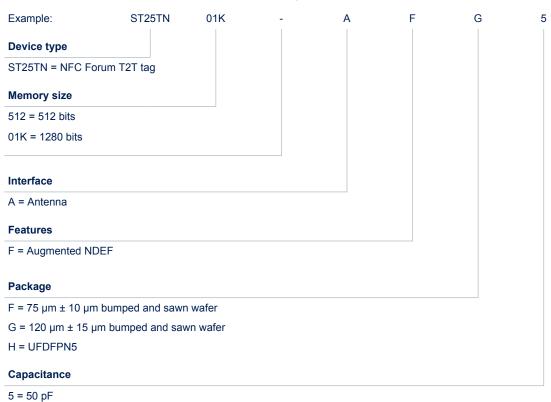

Datasheet

## NFC Forum Type 2 tag IC with up to 1.6 Kbits of EEPROM

UFDFPN5 (1.7 × 1.4 mm)

Wafer

#### Product status link

ST25TN512

ST25TN01K

#### **Features**

#### Includes ST state-of-the-art patented technology

#### **Contactless interface**

- Full compliancy with NFC Forum Type 2 tag and ISO/IEC 14443 type A specifications

- Power supplied by 13.56 MHz transmitter field

- Data transfer at 106 kbit/s

- Anticollision support for management of several tags in the field simultaneously

- Natively supported by Android<sup>™</sup> and iOS<sup>™</sup> phones

- Internal tuning capacitance 50 pF

#### Memory

- Up to 208 bytes (1664 bits) dedicated to user content

- · Accessible by blocks of four bytes

- NFC Forum NDEF format support

- Augmented NDEF (contextual automatic NDEF message)

- 100 000 Write cycles at + 85 °C

- Data retention during 40 years at + 55 °C

#### Product identification and protection

- 7 bytes unique identifier

- TruST25 digital signature

- TruST25 Link

- 3-digit unique tap code

- NFC Forum T2T permanent write locks at block level

#### **Privacy protection**

Configurable kill mode for permanent deactivation of the tag

#### Temperature range

• -40 °C/ +85 °C

#### **Delivery forms**

- 5-pin package ECOPACK2 (RoHS compliant)

- · Bumped and sawn inkless wafer

# 1 Description

ST25TN512 and ST25TN01K devices are NFC Forum Type 2 tag IC with TruST25 digital signature, Augmented NDEF, and privacy features.

The RF interface is compliant with ISO/IEC 14443-2 and 14443-3 Type A standards, and NFC Forum Type 2 tag specification. Thanks to its internal tuning capacitance and harvesting of operating power from RF field provided by the NFC poller, it simply operates with an antenna and without additional component.

The embedded electrically erasable programmable memory (EEPROM) can be written with a NDEF message conforming to NFC Forum specification offering native tap with all NFC-enabled phones.

The Augmented NDEF feature allows the tag to answer dynamic NDEF message without modification of the EEPROM by the user.

The TruST25 digital signature helps fighting against counterfeiting. TruST25 Link is a technology enabling offline NFC tag identification through reader + tag applications using ST devices.

The kill feature guarantees user privacy by permanently muting the tag with a simple software procedure. In this document, the term ST25TN refers interchangeably to ST25TN512 or ST25TN01K.

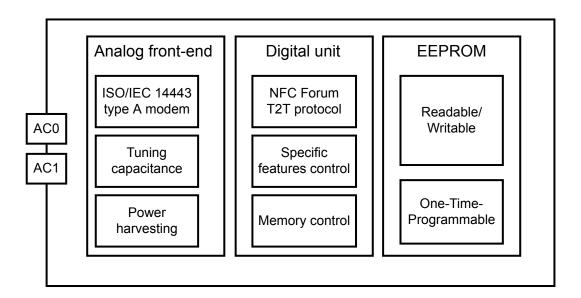

## 1.1 Block diagram

Figure 1. ST25TN block diagram

DS13433 - Rev 5 page 2/36

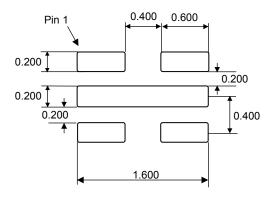

## 1.2 Package connections

The ST25TN is available in the following delivery forms:

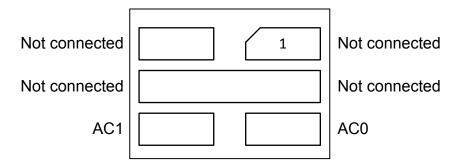

UFDFPN5 package

Figure 2. UFDFPN5 bottom view (pads side) connections

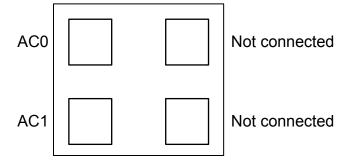

Bumped and sawn inkless wafer

Figure 3. Bumped wafer connection

## 1.3 Signal descriptions

Table 1. Signal description

| Name          | Description                                                                    |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| AC0           | These inputs are used exclusively to connect the device to an external coil.   |  |  |  |  |  |

| AC1           | It is advised not to connect any other DC or AC path to AC0 or AC1.            |  |  |  |  |  |

| ACT           | When correctly tuned, the coil is used both to power and interact with ST25TN. |  |  |  |  |  |

| Not connected | Other pads and bumps are not connected to the internal IC.                     |  |  |  |  |  |

DS13433 - Rev 5 page 3/36

# 2 Power supply

The power supply is provided exclusively by the RF field at 13.56MHz at the coil. For proper operation, the following constraints must be met:

### 2.1 Power on

In accordance with ISO/IEC 14443-3, to ensure a proper boot of the RF circuitry, the RF field must be turned on without any modulation for a minimum duration  $t_{BOOT\_RF}$  (see Section 8.2: RF characteristics). Before this time, the device ignores all received RF commands.

### 2.2 Power off

In accordance with ISO/IEC 14443-3, to ensure a proper reset of the RF circuitry, the RF field must be turned off (100% modulation) for a minimum duration  $t_{RF\ OFF}$  (see Section 8.2: RF characteristics).

DS13433 - Rev 5 page 4/36

# 3 Memory overview

The memory is organized in blocks with 4 bytes per block. ST25TN01K and ST25TN512 have 64 blocks (256 bytes) always readable including both memory available for user data and memory reserved for system and configuration.

The following address space is available to standard READ/WRITE commands:

Table 2. ST25TN memory overview

|                        | Block<br>address          | Data Bytes within the block <sup>(1)</sup> |                       |               |            |  |  |

|------------------------|---------------------------|--------------------------------------------|-----------------------|---------------|------------|--|--|

| Dec                    | Hex                       | Byte0                                      | Byte1                 | Byte2         | Byte3      |  |  |

| 0                      | 00h                       |                                            | Device identification |               |            |  |  |

| 1                      | 01h                       |                                            | Device identii        | ication       |            |  |  |

| 2                      | 02h                       | Internal                                   | SYSBLOCK              | Static        | Lock Bytes |  |  |

| 3                      | 03h                       |                                            | Capability conta      | iner (CC)     |            |  |  |

| 4 to 43 <sup>(2)</sup> | 04h to 2Bh <sup>(2)</sup> | User memory                                |                       |               |            |  |  |

| 44                     | 2Ch                       |                                            | Dynamic Lock area     |               | SysLock    |  |  |

| 45                     | 2Dh                       |                                            | Product identi        | fication      |            |  |  |

| 46                     | 2Eh                       |                                            | Augmented NDEF        | configuration |            |  |  |

| 47                     | 2Fh                       |                                            | Kill passw            | ord           |            |  |  |

| 48                     | 30h                       |                                            | Kill keyho            | ole           |            |  |  |

| 49 to 59               | 31h to 3Bh                |                                            | Internal              |               |            |  |  |

| 60                     | 3Ch                       |                                            |                       |               |            |  |  |

| 61                     | 3Dh                       |                                            | Augmented ND          | EE fields     |            |  |  |

| 62                     | 3Eh                       |                                            | Augmented NDEF fields |               |            |  |  |

| 63                     | 3Fh                       |                                            |                       |               |            |  |  |

<sup>1.</sup> The bytes in this table are represented with the LSB on the left.

Table 3. ST25TN512 user memory

|          | Block<br>ddress |                        | Data Bytes wi | thin the block |  |  |  |

|----------|-----------------|------------------------|---------------|----------------|--|--|--|

| Dec      | Hex             | Byte0 Byte1 Byte2 Byte |               |                |  |  |  |

| 4 to 19  | 04h to 13h      | User memory            |               |                |  |  |  |

| 20 to 43 | 14h to 2Bh      | Reserved               |               |                |  |  |  |

The user memory can expanded by application over other functions. More details on how to achieve it are provided in "AN5677 - Extending the user memory of ST25TN512 and ST25TN01K devices".

DS13433 - Rev 5 page 5/36

<sup>2.</sup> For ST25TN512, the zone of blocks address from 4 to 43 is split according to Table 3. ST25TN512 user memory.

## 4 Device and product identification

ST25TN embeds several readable fields allowing the identification of the product model, version, size, and serial number.

All the fields are accessible through the standard READ command.

## 4.1 Device identification: unique identifier (UID)

Each ST25TN device is uniquely identified by a 7-byte Unique identifier (UID) compliant with ISO/IEC 14443-3 double-size UID.

Byte 0 of the UID is the IC manufacturer code 02h registered by STMicroelectronics according to ISO/IEC 7816-5.

**Block** Bits Name **Function Access Factory value** address b7-b0 UID\_0 02h 0 b15-b8 UID\_1 b23-b16 UID\_2 READ: always b7-b0 UID\_3 UID WRITE: never Unique serial number b15-b8 UID\_4 1 b23-b16 UID\_5 b31-b24 UID\_6

Table 4. Device identification (UID)

Table 5. BCC

| Block<br>addres | Bits    | Name  | Function                                                                                                   | Access                       | Factory value                          |

|-----------------|---------|-------|------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------|

| 0               | b31-b24 | BCC_1 | Block Check Character as defined in ISO/IEC 14443-3 and NFC Forum Digital Protocol Technical Specification | READ: always<br>WRITE: never | = 88h xor UID_0 xor UID_1<br>xor UID_2 |

## 4.2 Product identification: SYSBLOCK, PC, REV, KID

The product identification is done using standard READ command in the system area. To be compatible with several STMicroelectronics Type 2 tag sizes, an application must first read the value of SYSBLOCK to know the location of the system area, and then read PC/REV/KID in the system area.

Table 6. System area identification (SYSBLOCK)

| Block<br>address | Bits   | Name     | Function                                                                                                                                                                                                   | Access                       | Factory<br>value |

|------------------|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|

| 2                | b15-b8 | SYSBLOCK | Block address of the beginning of the system area.  To be compatible with several STMicroelectronics Type 2 tag sizes, an application must use this value plus 1 to read the product identification block. | READ: always<br>WRITE: never | 2Ch              |

DS13433 - Rev 5 page 6/36

Table 7. Product identification (PC, REV, KID)

| Block<br>address | Bits      | Name         | Function                                                       | Access                                     | Factory value |

|------------------|-----------|--------------|----------------------------------------------------------------|--------------------------------------------|---------------|

| "Value read in   | b15-b0 PC | Product code | READ: always                                                   | 9091h for ST25TN512<br>9090h for ST25TN01K |               |

| SYSBLOCK" + 1    | b23-b16   | REV          | Product version                                                | WRITE: never                               | 13h           |

|                  | b31-b24   | KID          | Key ID used to generate TruST25 signature during manufacturing |                                            | 05h           |

DS13433 - Rev 5 page 7/36

### 5 Device features

### 5.1 Capability container (CC)

The block 3 has a specific behavior conforming to NFC Forum Type 2 tag specification for capability container (CC bytes).

The content of CC bytes after manufacturing is described in Section 7: Memory content at delivery .

The modifications of CC can be prevented according to Section 5.2: Access restriction. When it is not locked the following applies:

- The bits of block 3 are one-time-programmable (OTP):

- they can only be set to 1 and cannot be changed back to 0. Upon reception of a valid WRITE command to a block address 3, the device only sets the bits at 1, ignore the other bits and answers ACK.

- Writing into block 3 is tearing-proof:

- even in case of tearing, the bits are never erased.

#### 5.2 Access restriction

It is possible protect the write access of blocks with a lock mechanism. The lock is irreversible: a locked block can never be unlocked and is never writable again. The lock mechanism is compliant with NFC Forum T2T specification with some extensions providing finer grain locking options.

#### 5.2.1 Generic lock mechanism

The blocks to lock are configured using "lock bits" of Static lock bytes, Dynamic lock area (DynLock\_Area) and SysLock byte shown in Table 2. ST25TN memory overview with the memory mapping detailed in the following table.

| Block<br>address (hex) | Bits         | Name       | Function                                                                        | Factory<br>value |

|------------------------|--------------|------------|---------------------------------------------------------------------------------|------------------|

| 02h                    | b31-b24      | STATLOCK_1 | Static lock bytes to prevent modification of the beginning of                   | 00h              |

| 0211                   | b23-b16 STAT |            | memory                                                                          | 00h              |

|                        | b31-b24      | SYSLOCK    | System lock bits to prevent modification of the system configuration blocks     | E2h              |

| 2Ch                    | b23-b16      | DYNLOCK_2  |                                                                                 | 00h              |

|                        | b15-b8       | DYNLOCK_1  | Dynamic lock bits to prevent modification of the remaining bytes of user memory | 00h              |

|                        | b7-b0        | DYNLOCK_0  |                                                                                 | 00h              |

Table 8. Memory lock bytes in memory map

In all these bytes, each lock bit configures the write access of a given memory region. When a lock bit is set to 1, the content of the target memory region cannot be modified anymore and becomes read-only.

The lock bits are One-Time-Programmable (OTP): they can only be set to 1 and cannot be changed back to 0. Upon reception of a valid WRITE command to a block with lock bits, the device only sets the bits at 1, ignore the other bits and answers ACK.

Writing into a block with lock bits is tearing-proof: even in case of tearing, the lock bits are never erased.

The mapping of which lock bit locks which memory region is described in Table 10 and Table 9. The specificities of Static Lock bytes, DynLock\_Area and SysLock byte are described in dedicated sections below.

The following table details which bit locks which block(s).

DS13433 - Rev 5 page 8/36

Table 9. Lock bit mapping

|               |     | Locked Memory |             |                 |                       |                |       |

|---------------|-----|---------------|-------------|-----------------|-----------------------|----------------|-------|

| Locking bit   |     |               | ock<br>nber |                 | Byte                  | s              |       |

| Register      | Bit | Hex           | Dec         | Byte0           | Byte1                 | Byte2          | Byte3 |

|               | b0  |               |             |                 |                       |                |       |

|               | b1  |               |             | See Table 10. I | ock bit mapping for S | TATLOCK_0[0:2] |       |

|               | b2  |               |             |                 |                       |                |       |

| STATLOCK_0    | b3  | 03h           | 3           |                 | CC                    |                |       |

| O I/ (1200K_0 | b4  | 04h           | 4           |                 |                       |                |       |

|               | b5  | 05h           | 5           |                 |                       |                |       |

|               | b6  | 06h           | 6           |                 |                       |                |       |

|               | b7  | 07h           | 7           |                 |                       |                |       |

|               | b0  | 08h           | 8           |                 |                       |                |       |

|               | b1  | 09h           | 9           |                 |                       |                |       |

|               | b2  | 0Ah           | 10          |                 |                       |                |       |

| STATLOCK_1    | b3  | 0Bh           | 11          |                 |                       |                |       |

| STATEOUR_T    | b4  | 0Ch           | 12          |                 |                       |                |       |

|               | b5  | 0Dh           | 13          |                 |                       |                |       |

|               | b6  | 0Eh           | 14          |                 |                       |                |       |

|               | b7  | 0Fh           | 15          |                 |                       |                |       |

|               | b0  | 10h           | 16          |                 |                       |                |       |

|               | bu  | 11h           | 17          |                 |                       |                |       |

|               | b1  | 12h           | 18          |                 |                       |                |       |

|               | D1  | 13h           | 19          |                 |                       |                |       |

|               | b2  | 14h           | 20          |                 | User me               | mory           |       |

|               | 02  | 15h           | 21          |                 |                       |                |       |

|               | b3  | 16h           | 22          |                 |                       |                |       |

| DYNLOCK_0     | 55  | 17h           | 23          |                 |                       |                |       |

| DINEOUK_0     | b4  | 18h           | 24          |                 |                       |                |       |

|               | D-T | 19h           | 25          |                 |                       |                |       |

|               | b5  | 1Ah           | 26          |                 |                       |                |       |

|               |     | 1Bh           | 27          |                 |                       |                |       |

|               | b6  | 1Ch           | 28          |                 |                       |                |       |

|               |     | 1Dh           | 29          |                 |                       |                |       |

|               | b7  | 1Eh           | 30          |                 |                       |                |       |

|               | 57  | 1Fh           | 31          |                 |                       |                |       |

|               | b0  | 20h           | 32          |                 |                       |                |       |

|               |     | 21h           | 33          |                 |                       |                |       |

| DYNLOCK_1     | b1  | 22h           | 34          |                 |                       |                |       |

|               | D1  | 23h           | 35          |                 |                       |                |       |

|               | b2  | 24h           | 36          |                 |                       |                |       |

DS13433 - Rev 5 page 9/36

|             | Locked Memory |     |             |              |                        |             |         |  |  |  |

|-------------|---------------|-----|-------------|--------------|------------------------|-------------|---------|--|--|--|

| Locking bit |               |     | ock<br>nber | Bytes        |                        |             |         |  |  |  |

| Register    | Bit           | Hex | Dec         | Byte0        | Byte0 Byte1 Byte2 Byte |             |         |  |  |  |

|             | b2            | 25h | 37          |              |                        |             |         |  |  |  |

|             | b3            | 26h | 38          |              |                        |             |         |  |  |  |

|             | DS            | 27h | 39          |              |                        |             |         |  |  |  |

| DYNLOCK_1   | b4            | 28h | 40          |              | User memory            |             |         |  |  |  |

|             | 04            | 29h | 41          |              |                        |             |         |  |  |  |

|             | b5            | 2Ah | 42          | 2            |                        |             |         |  |  |  |

|             | DS            | 2Bh | 43          |              |                        |             |         |  |  |  |

|             | b0            | 2Ch | 44          | DYNLOCK_0    | DYNLOCK_1              | DYNLOCK_2   | SYSLOCK |  |  |  |

|             | b1            | 2Dh | 45          |              | Product ider           | ntification |         |  |  |  |

| SYSLOCK     | b2            | 2Eh | 46          |              | ANDEF con              | figuration  |         |  |  |  |

|             | b3            | 2Fh | 47          |              | KILL_F                 | PWD         |         |  |  |  |

|             | b4            | 30h | 48          |              | Kill key               | hole        |         |  |  |  |

|             | b6            | 3Ch | 60          |              |                        |             |         |  |  |  |

| DANI OCK 3  | טט            | 3Dh | 61          | ANDEF_CUSTOM |                        |             |         |  |  |  |

| DYNLOCK_2   | b7            | 3Eh | 62          |              |                        |             |         |  |  |  |

|             | U7            | 3Fh | 63          | ANDEF_       | CUSTOM                 | ANDEF_SEP   | -       |  |  |  |

DS13433 - Rev 5 page 10/36

#### 5.2.2 Static lock bytes

This section describes specificities on top of the generic lock mechanism described Section 5.2.1: Generic lock mechanism.

The static lock bits are stored at block address 2, which contains both read-only and writable bits. Upon reception of a valid WRITE command for this block, the device updates only the writable bits of the block and answers ACK.

The low significant bits 0 to 2 of STATLOCK\_0 are special because they allow to disable the locking of some blocks by locking the value of some STATLOCK\_0 and STATLOCK\_1 bits as shown in Table 10.

| Locking bit |     | Locked memory |     |  |

|-------------|-----|---------------|-----|--|

| Name        | bit | Name          | bit |  |

|             | b0  | STATLOCK_0    | b3  |  |

|             |     |               | b4  |  |

|             |     | STATLOCK_0    | b5  |  |

|             | h1  | STATLOCK_U    | b6  |  |

|             | b1  |               | b7  |  |

|             |     | STATLOCK_1    | b0  |  |

| STATLOCK_0  |     | STATLOCK_T    | b1  |  |

|             |     |               | b2  |  |

|             |     |               | b3  |  |

|             | b2  | STATLOCK_1    | b4  |  |

|             | 02  | STATLOCK_T    | b5  |  |

|             |     |               | b6  |  |

|             |     |               | b7  |  |

Table 10. Lock bit mapping for STATLOCK\_0[0:2]

- If bit b0 of STATLOCK\_0 is set to 1 and bit b3 of STATLOCK\_0 is reset to 0, the block 3 (CC file) is always

writable.

- If bit b1 of STATLOCK\_0 is set to 1 and some bits of STATLOCK\_0[7:4] or STATLOCK\_1[1:0] are reset to 0, the corresponding block(s) between 4 and 9 included is always writable.

- If bit b2 of STATLOCK\_0 is set to 1 and some bits of STATLOCK\_1[7:2] are reset to 0, the corresponding block(s) between 0Ah and 0Fh included is always writable.

The remaining system lock bits have a granularity of 1 block: Each bit locks the value of 1 block (4 bytes) with bit b3 of STATLOCK 0 locking the value of block address 3 and so forth as described in Table 9. Lock bit mapping.

#### 5.2.3 Dynamic lock bits

This section describes specificities on top of the generic lock mechanism described in Section 5.2.1: Generic lock mechanism.

Dynamic Lock Bits have a granularity of 2 blocks (8 bytes) per bit: Each bit locks the value of 2 blocks (8 bytes), starting at block address 10h and up to the end of the memory as shown in Table 9. Lock bit mapping.

The dynamic lock bits DYNLOCK\_1[6:7] and DYNLOCK\_2[0:1] that would apply to a block in the system area protected by SYSLOCK bits are ignored by the device whatever their value.

Note:

For ST25TN01K: with the factory CC programming defining a T2T\_Area\_Size of 160 bytes, the position of the first Dynamic lock byte is the first byte after the T2T\_Area. Since the granularity of dynamic lock bits matches the default granularity defined in NFC Forum Type 2 Tag specification, there is no need for a Lock Control TLV in T2T\_AREA to define the position and number of dynamic lock bits.

#### 5.2.4 System lock bits

This section describes specificities on top of the generic lock mechanism described in Section 5.2.1: Generic lock mechanism.

DS13433 - Rev 5 page 11/36

System lock bits have a granularity of 1 block: Each bit locks the value of 1 block (4 bytes), starting at block address 2Ch, as shown in Table 9. Lock bit mapping.

## 5.3 Privacy: Kill feature

It is possible to permanently kill the RF interface of the device: When the device is in KILLED state, all incoming RF commands are ignored. There is no way to revert a killed device back to normal operation.

This feature may be used to comply with GDPR or another privacy requirement.

#### 5.3.1 Kill command

The Kill command is a Write of the kill password to the address 30h = 48.

Table 11. Kill command format

| TBD     | Byte 1 | Byte 2        | Byte 3        | Byte 4 | Byte 5 | Byte 6 | Byte 7 | Byte 8 |

|---------|--------|---------------|---------------|--------|--------|--------|--------|--------|

| Field   | Code   | Block address | Kill password |        |        |        | CR     | C_A    |

| Content | A2h    | 30h           | 4 bytes       |        |        |        | 2 by   | ytes   |

The Kill command may be disabled by locking the "kill keyhole" block using the locking mechanism described in Section 5.2: Access restriction.

When the Kill command is disabled (block 30h is locked), the device answers NACK0 to a WRITE command in block 30h.

When the Kill command is enabled (block 30h is not locked) and the data value in the Write command matches the kill password stored in the device, the device answers ACK and set an internal non-volatile bit "Killed" to the value 1. Then, it enters Killed state on the next and each boot as described in Figure 4. State machine.

#### 5.3.2 Kill password

Table 12. KILL\_PWD

| Block address<br>(Hex) | Name     | Function      | Factory value |

|------------------------|----------|---------------|---------------|

| 2Fh                    | KILL_PWD | Kill password | 0000000h      |

The kill password (KILL\_PWD) can be freely written without password presentation unless the block is locked by corresponding SYSLOCK bit. Once corresponding SYSLOCK bit is set, the password cannot be modified anymore.

The kill password can never be read-out: Upon a READ command, the device always returns 00000000h for the bytes of block address 2Fh whatever the actual values of these bytes.

Warning: the kill password adds security only if it is locked, otherwise it can be modified without knowledge of the previous password.

DS13433 - Rev 5 page 12/36

## 5.4 Augmented NDEF

The augmented NDEF feature (ANDEF) allows the device to respond smart NDEF messages thanks to:

- Automatic insertion of a custom field such as UID

- Automatic insertion of unique tap code (UTC) without modification of the EEPROM by the user

When the feature is enabled, memory data at byte addresses ranging from ANDEF\_START to ANDEF\_END is replaced by the content of a virtual memory ANDEF\_MEM in the response to READ command as shown in following figure

| Disak                     | Block data |           |              |       |                                                     |       |            |       |  |  |  |  |

|---------------------------|------------|-----------|--------------|-------|-----------------------------------------------------|-------|------------|-------|--|--|--|--|

| Block<br>address<br>(dec) | \          | when ANDE | F is disable | d     | when ANDEF is enabled, ANDEF_START=77, ANDEF_END=82 |       |            |       |  |  |  |  |

| (uec)                     | Byte0      | Byte1     | Byte2        | Byte3 | Byte0                                               | Byte1 | Byte2      | Byte3 |  |  |  |  |

| 00                        | В0         | B1        | B2           | В3    | B0                                                  | B1    | B2         | В3    |  |  |  |  |

|                           |            |           |              |       |                                                     |       |            |       |  |  |  |  |

| 18                        | B72        | B73       | B74          | B75   | B72                                                 | B73   | B74        | B75   |  |  |  |  |

| 19                        | B76        | B77       | B78          | B79   | B76                                                 | Α0    | <b>A</b> 1 | A2    |  |  |  |  |

| 20                        | B80        | B81       | B82          | B83   | А3                                                  | A4    | A5         | B83   |  |  |  |  |

| 21                        | B84        | B85       | B86          | B87   | B84                                                 | B85   | B86        | B87   |  |  |  |  |

|                           |            |           |              |       |                                                     |       |            |       |  |  |  |  |

Table 13. Effect of ANDEF feature on READ data response

#### In the above table:

- Bx is byte x of EEPROM memory

- Ax is byte x of the virtual memory ANDEF\_MEM

The values ANDEF\_START and ANDEF\_END depend on the ANDEF configuration as defined in Table 14. ANDEF\_CFG.

- ANDEF\_START = ANDEF\_BLOCK \* 4 + ANDEF\_BYTE

- ANDEF\_END = ANDEF\_START + ANDEF\_CUSTOM\_EN \* 14 + ANDEF\_UTC\_EN \* 3 + ANDEF\_SEP\_EN

1

- ANDEF\_SEP\_EN = 1 if both ANDEF\_CUSTOM\_EN is 1 and ANDEF\_UTC\_EN is 1, otherwise ANDEF\_SEP\_EN = 0

DS13433 - Rev 5 page 13/36

#### 5.4.1 ANDEF configuration

The following fields configure ANDEF behavior:

Table 14. ANDEF\_CFG

| Block<br>address<br>(hex) | Bits               | Name        | Function                                                                                | Factory value |

|---------------------------|--------------------|-------------|-----------------------------------------------------------------------------------------|---------------|

|                           | b5-b0              | ANDEF_BLOCK | Block address for the beginning of ANDEF_MEM                                            | 0Fh           |

|                           | b7-b6              | RFU         | -                                                                                       | 0             |

|                           | b8 ANDEF CUSTOM EN |             | 1b: ANDEF_CUSTOM is appended in ANDEF_MEM 0b: ANDEF_CUSTOM is not appended in ANDEF_MEM | 0             |

| 2Eh                       | b9                 | RFU         | -                                                                                       | 0             |

|                           | b10 ANDEF UTC EN   |             | 1b: ANDEF_UTC is appended in ANDEF_MEM  0b: ANDEF_UTC is not appended in ANDEF_MEM      | 0             |

|                           |                    |             | -                                                                                       | 0             |

|                           | b15-b14            | ANDEF_BYTE  | Byte number into ANDEF_BLOCK for the beginning of ANDEF_MEM                             | 0             |

ANDEF feature is disabled when both ANDEF\_CUSTOM\_EN and ANDEF\_UTC\_EN are reset to the value 0. ANDEF CFG is always readable.

Modifications of ANDEF\_CFG can be prevented according to Section 5.2: Access restriction.

#### 5.4.2 ANDEF custom

Table 15. ANDEF\_CUSTOM

| Block<br>address<br>(hex) | Bits   | Name Function |                                  | Factory value                     |

|---------------------------|--------|---------------|----------------------------------|-----------------------------------|

| 3Ch-3Eh                   | b31-b0 | ANDEF CUSTOM  | Field inserted in ANDEF_MEM when | ASCII coding of the device UID in |

| 3Fh                       | b15-b0 | ANDEF_COSTOM  | ANDEF_CUSTOM_EN is 1             | hexadecimal representation        |

ANDEF\_CUSTOM is initialized at factory with ASCII coding of the device UID in hexadecimal representation. Consequently, several ST25TN with the same content in T2T\_AREA can answer different NDEF messages, each one with a device-specific content.

ANDEF\_CUSTOM is always readable.

Modifications of ANDEF\_ CUSTOM can be prevented according to Section 5.2: Access restriction.

Since memory is not locked at manufacturing, it is possible to replace the ANDEF\_CUSTOM with another custom message.

## 5.4.3 ANDEF unique tap code

ANDEF\_UTC is an ASCII value generated once every time the device is powered.

The value is unique to each user tap of the tag, and predictable.

The size of ANDEF\_UTC is 3 bytes.

A typical usage of UTC is to embed it in the URI record of a NDEF message. In this case, when a user taps the tag with a smartphone, its web browser natively opens a URL including the unique tap code, which can be processed as an element of tag authentication by the web server.

More details on ANDEF\_UTC are provided in "AN5628 – Unique tap code for ST25TN512 and ST25TN01K devices". Contact your STMicroelectronics sales office to get this document.

DS13433 - Rev 5 page 14/36

## 5.4.4 ANDEF separator

A separator is inserted between ANDEF\_CUSTOM and ANDEF\_UTC when both ANDEF\_CUSTOM\_EN and ANDEF\_UTC\_EN are set to 1. The value of this separator can be customized by writing ANDEF\_SEP described in the following table.

Table 16. ANDEF\_SEP

| Blocks<br>address<br>(Hex) | Bits Name |           | Function                                                                       | Factory value            |

|----------------------------|-----------|-----------|--------------------------------------------------------------------------------|--------------------------|

| 3Fh                        | b23-b16   | ANDEF_SEP | Field inserted in ANDEF_MEM when both ANDEF_CUSTOM_EN = 1 and ANDEF_UTC_EN = 1 | 78h<br>ASCII code of 'x' |

ANDEF\_SEP is always readable.

Modifications of ANDEF SEP can be prevented according to Section 5.2: Access restriction.

## 5.5 TruST25 digital signature

ST25TN supports the TruST25 digital signature feature, which allows the user to verify the authenticity of the device, thanks to a unique digital signature.

TruST25 solution encompasses secure industrialization processes and tools deployed by STMicroelectronics to generate, store, and check the signature in the device.

More details on TruST25 digital signature are provided in "AN5660 – TruST25 digital signature for ST25TN512 and ST25TN01K devices". Contact your STMicroelectronics sales office to get this document.

#### 5.6 TruST25 Link

TruST25 Link is based on a patented technology enabling offline NFC tag identification through reader and tag applications using ST devices.

More details on the TruST25 Link are provided in AN6296. Contact your STMicroelectronics sales office to get this document.

DS13433 - Rev 5 page 15/36

## Device operation

## 6.1 NFC Type 2 tag overview

NFC Type 2 tag specification is based on NFC-A technology specification which is aligned with ISO/IEC 14443-2 and 14443-3 Type A. Since both specifications use different wording for the same concept, both wordings are often provided in this document. For example "SAK/SEL\_RES" designates ISO/IEC 14443 "SAK" and its NFC Forum equivalent "SEL RES".

The tag (also named PICC) always waits to receive a command from an initiator (named Poller or PCD) before sending a response.

Commands are transmitted using OOK (100% ASK) modulation of a 13.56MHz carrier wave transmitted by the Poller. Responses are transmitted using retro-modulation of the same carrier wave.

Both commands and responses are transmitted at 106kbps.

Type 2 tags and Type 4 tags share the same activation, anticollision and selection process allowing one-to-one communication in presence of several tags.

Type 2 tags are distinguished from Type 4 tags by their SAK/SEL\_RES response to ATQA/SEL\_REQ command. ST25TN512 and ST25TN01K SAK value is described in section "SAK/SEL\_RES" response.

On top of the communication protocol, Type 2 tag specification defines

- some commands to access directly the memory,

- · a memory layout,

- · a memory lock mechanism,

- · and memory content to layout a NDEF.

ST25TN implements the commands, the memory layout, and the memory lock mechanism. The memory content is managed by application.

DS13433 - Rev 5 page 16/36

#### State machine 6.2

ST25TN follows the following state machine, compliant with ISO/IEC 14443-3 type A anticollision and select sequences and NFC Forum T2 tag specification. The equivalence between ISO/IEC 14443 command names and NFC Forum command names is provided in Table 17. Commands overview.

POWER\_OFF Killed = 0Killed = 1 HALT(3) IDLE(3) KILLED(3) **WUPA REQA WUPA** > ANTICOLLISION READY 1(3) - other SELECT CL1 READ from block 0-15 (2) **←** other **ANTICOLLISION** READY 2(3) SELECT CL2 READ from block 0-15 **READ** (2) **←** other<sup>(1)</sup> ACTIVE(3) WRITE HLTA

Figure 4. State machine

- (1) "other" includes any erroneous command for which the device answers NACK.(2) The device returns in HALT state if it was previously in HALT state after POWER\_OFF state, otherwise it returns to IDLE state.(3) In all states, the device returns to POWER\_OFF state when it is not powered anymore.

DS13433 - Rev 5 page 17/36

## 6.3 Timings

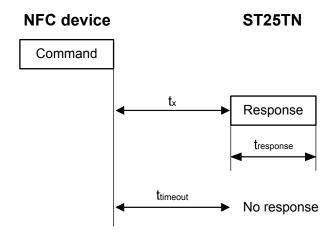

The timing of commands is provided in each command section, rounded at 1  $\mu$ s, using the following generic representation with drawing not to scale:

Figure 5. Generic representation of command timing

- t<sub>x</sub> is the time between the end of the command and the beginning of the response. It is not FDT

- t<sub>response</sub> includes SOF and EOF of the response

- t<sub>timeout</sub> is equal to the maximum value of t<sub>x</sub>

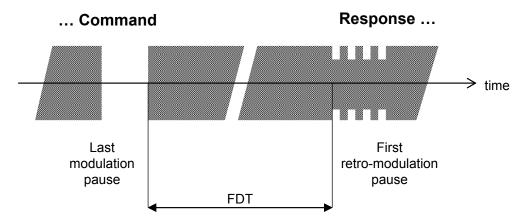

ISO/IEC 14443-3 and NFC Forum digital specification define the frame delay time (FDT) starting at the end of the last pulse of the command such that:

- FDT =  $(n_{FDT} * 128 + 84) / f_c$  in case the last bit of the command is a logic '1' and

- FDT =  $(n_{FDT} * 128 + 20) / f_c$  in case the last bit of the command is a logic '0' where  $f_c$  is the frequency of the carrier wave and ' $n_{FDT}$ ' is an integer.

Figure 6. Frame delay time (FDT)

The values of  $t_x$ ,  $t_{response}$ ,  $t_{timeout}$  and  $n_{FDT}$  are provided for each command with its description.

DS13433 - Rev 5 page 18/36

### 6.4 Commands

### 6.4.1 Commands overview

**Table 17. Commands overview**

| Туре                       | Na          | me                | Code               | Function               |

|----------------------------|-------------|-------------------|--------------------|------------------------|

|                            | SENS_REQ    | REQA              | 26h <sup>(1)</sup> |                        |

|                            | ALL_REQ     | WUPA              | 52h <sup>(1)</sup> |                        |

| ISO/IEC 14443-3 Type A     | SDD_REQ_CL1 | Anticollision CL1 | 93h xxh            | Device initialization, |

| and                        | SEL_REQ_CL1 | Select CL1        | 93h 70h            | anticollision,         |

| NFC Forum NFC-A technology | SDD_REQ_CL2 | Anticollision CL2 | 95h xxh            | and selection          |

|                            | SEL_REQ_CL2 | Select CL2        | 95h 70h            |                        |

|                            | SLP_REQ     | HLTA              | 50h 00h            |                        |

| NFC Forum Type 2 tag       | RE          | AD                | 30h                | Read 4x Blocks of data |

| ivi o i orum Type z tag    | WF          | RITE              | A2h                | Write 1x Block of data |

<sup>1.</sup> Code on 7 bits.

The commands used for device initialization, anti-collision and selection are described in ISO/IEC 14443-3 for Type A and alternatively in NFC Forum Digital specification for NFC-A technology.

Other commands supported by the device are described hereafter.

## 6.4.2 READ

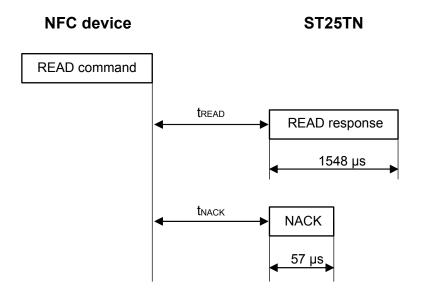

Figure 7. READ command outline

Table 18. READ command format

| Byte    | 1            | 2             | 3     | 4    |  |

|---------|--------------|---------------|-------|------|--|

| Field   | Command code | Block address | CRC_A |      |  |

| Content | 30h          | 1 byte        | 2 by  | /tes |  |

Block address is the address of the first block to read.

DS13433 - Rev 5 page 19/36

• CRC\_A is Cyclic redundancy check defined in NFC Forum digital specification for NFC-A technology. The following responses may be issued upon reception of a READ command code:

Table 19. Possible responses to the READ command

| Condition upon reception of READ command code                                                     | Response                                 |

|---------------------------------------------------------------------------------------------------|------------------------------------------|

| Wrong number of bytes of payload                                                                  | No response                              |

| Parity or CRC_A error                                                                             | NACK1 (see Section 6.5.2: NACK response) |

| Block address is outside the valid address range.  ST25TN valid address range is [0;3Fh] = [0;63] | NACK0 (see Section 6.5.2: NACK response) |

| Successful read                                                                                   | READ response                            |

#### Table 20. READ response format

| Byte    | 1           | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9    | 10   | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 |

|---------|-------------|---|---|---|---|---|---|---|------|------|----|----|----|----|----|----|----|----|

| Field   | DATA        |   |   |   |   |   |   |   | CRO  | C_A  |    |    |    |    |    |    |    |    |

| Content | nt 16 bytes |   |   |   |   |   |   |   | 2 by | rtes |    |    |    |    |    |    |    |    |

- DATA is the content of 16 bytes of memory starting from the block address requested in the command. For example upon reception of the command "30h, 00h", the bytes of blocks 00h, 01h, 02h and 03h are returned.

- DATA may differ from the content of addressed memory in the following cases:

- ANDEF feature described in Section 5.4.1: ANDEF configuration is enabled

- The content of blocks "KILL\_PWD" (2Fh) and "Kill keyhole" (30h) can't be read-out and are replaced with value 00h

- CRC\_A is Cyclic Redundancy Check defined in NFC Forum digital specification for NFC-A technology. If a command READ is received while the device is in state READY1 or READY2, the following specific behavior apply:

- The valid block address range is limited to [0:15]

- DATA in response roll-over to the content of block 0 after the block 15.

- The normal content of memory is always returned even if ANDEF is enabled in this region.

Table 21. READ timings

| Symbol                 | Typical | Max  | Unit |

|------------------------|---------|------|------|

| t <sub>READ</sub>      | 70.5    | 4734 | μs   |

| t <sub>NACK</sub>      | -       | 4734 | μs   |

| n <sub>FDT, READ</sub> | 9       | 501  | -    |

The timings showed in Figure 7. READ command outline and Table 21. READ timings are explained in Section 6.3: Timings.

DS13433 - Rev 5 page 20/36

#### 6.4.3 WRITE

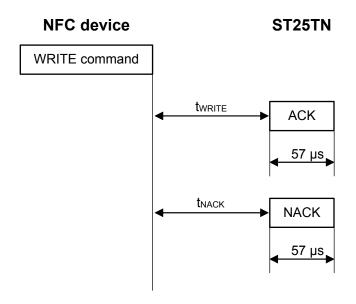

Figure 8. WRITE command outline

Table 22. WRITE command format

| Byte    | 1            | 2             | 3       | 4 | 5 | 6 | 7    | 8    |

|---------|--------------|---------------|---------|---|---|---|------|------|

| Field   | Command code | Block address | s DATA  |   |   |   | CRO  | C_A  |

| Content | A2h          | 1 byte        | 4 bytes |   |   |   | 2 by | rtes |

- Block address is the address of the block to modify.

- DATA is the data to write.

- CRC\_A is Cyclic Redundancy Check defined in NFC Forum digital specification for NFC-A technology.

The following responses may be issued upon reception of a WRITE command code:

Table 23. Possible responses to the WRITE command

| Condition upon reception of WRITE command code                                                                                                                                                            | Response                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Wrong number of bytes of payload                                                                                                                                                                          | No response                              |

| Parity or CRC_A error                                                                                                                                                                                     | NACK1 (see Section 6.5.2: NACK response) |

| Block address is outside the valid address range.<br>ST25TN01K valid address range is [0-3Fh] ([0-63])                                                                                                    | NACK0 (see Section 6.5.2: NACK response) |

| Block address targets a read-only block.  Read-only blocks includes the system read-only blocks and the blocks locked. The only exception is the block address 2, which is always considered as writable. | NACK0 (see Section 6.5.2: NACK response) |

| After writing EEPROM, the hardware check if is not OK                                                                                                                                                     | NACK5 (see Section 6.5.2: NACK response) |

| EEPROM successfully written                                                                                                                                                                               | ACK (see Section 6.5.1: ACK response     |

**Table 24. WRITE timings**

| Symbol             | Typical | Max  | Unit |

|--------------------|---------|------|------|

| t <sub>WRITE</sub> | 4163    | 4734 | μs   |

DS13433 - Rev 5 page 21/36

| Symbol                  | Typical | Max  | Unit |

|-------------------------|---------|------|------|

| t <sub>NACK</sub>       | -       | 4734 | μs   |

| n <sub>FDT, WRITE</sub> | 443     | 501  | -    |

The timings of Figure 8. WRITE command outline and Table 24. WRITE timings are explained in Section 6.3: Timings.

## 6.5 Standard responses

If a command has an unknown command code the device doesn't answer.

Any error with or without answer changes the device state back to IDLE or HALT as described in Figure 4. State machine.

#### 6.5.1 ACK response

ACK response is 4 bits equal to Ah conforming to T2 Tag specification to indicate a successful operation.

### 6.5.2 NACK response

NACK response is 4 bits conforming to T2 Tag specification to indicate an error.

The following NACK values are used:

Table 25. NACK responses

| Name  | Value (4 bits) | Meaning               |

|-------|----------------|-----------------------|

| NACK0 | Oh             | Invalid argument      |

| NACK1 | 1h             | Parity or CRC_A error |

| NACK5 | 5h             | EEPROM write error    |

### 6.5.3 ATQA/SENS\_RES response

Upon reception of REQA (SENS\_REQ) or WUPA (ALL\_REQ) command, the device issues the following ATQA (SENS\_RES) response indicating a double UID size (7 bytes):

Table 26. ATQA/SENS\_RES response

| Byte    | 1                             | 2                    |

|---------|-------------------------------|----------------------|

| Field   | UID size & Anticollision info | Platform information |

| Content | 44h                           | 00h                  |

In little endian representation, the corresponding 16 bits value is 0x0044.

DS13433 - Rev 5 page 22/36

## 6.5.4 SAK/SEL\_RES response

Upon reception of SELECT (SEL\_REQ) command with complete matching UID bits, the device issues the following SAK (SEL\_RES) response indicating UID complete and PICC compliant with Type 2 tag platform and not ISO/IEC 14443-4.

Table 27. SAK/SEL\_RES response

| Byte    | 1                        | 2 3 |     |

|---------|--------------------------|-----|-----|

| Field   | Select acknowledge CRC_A |     |     |

| Content | 00h                      | FEh | 51h |

DS13433 - Rev 5 page 23/36

# 7 Memory content at delivery

ST25TN is programmed during manufacturing to comply with NFC Forum INITIALIZED state so that it is readily usable by any NFC Forum compatible device.

Augmented NDEF fields are programmed during manufacturing so that only generic configuration as described in Section 5.4.1: ANDEF configuration is required to benefit from Augmented NDEF.

Table 28. Initial memory content

| Block | Byte        | Name         | Parameter                                | Value                                                                                       | Description                  |

|-------|-------------|--------------|------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------|

| 03h   | 0           | CC_0         | Magic number                             | E1h                                                                                         | Indicates that this is a T2T |

|       | 1           | CC_1         | Version                                  | 10h                                                                                         | T2T current specification    |

|       | 2 CC_2 Size |              | 08h: for ST25TN512<br>14h: for ST25TN01K | T2T_Area_Size = 64 bytes : for<br>ST25TN512<br>T2T_Area_Size = 160 bytes :<br>for ST25TN01K |                              |

|       | 3           | CC_3         | Access condition                         | 00h                                                                                         | read/write access granted    |

|       | 0           |              | TLV Type                                 | 03h                                                                                         | NDEF                         |

| 04h   | 1           | TOT ADEA     | TLV Length                               | 00h                                                                                         | Empty NDEF                   |

| 0411  | 2           | T2T_AREA     | TLV Type                                 | FEh                                                                                         | Terminator TLV               |

|       | 3           |              | TLV Type                                 | 00h                                                                                         | NULL TLV                     |

|       |             |              |                                          |                                                                                             |                              |

| 3Ch   | 0           |              |                                          |                                                                                             |                              |

|       |             | ANDEF_CUSTOM | Source for custom field in               | ASCII coding of hexadecimal representation                                                  | Unique to each IC            |

|       | 0           | ,            | ANDEF_MEM                                | of UID                                                                                      | ornque to eden to            |

| 3Fh   | 1           |              |                                          |                                                                                             |                              |

|       | 2           | ANDEF_SEP    | Source for fields separator in ANDEF_MEM | 78h                                                                                         | ASCII code of 'x'            |

DS13433 - Rev 5 page 24/36

## 8 Device parameters

## 8.1 Maximum ratings

Stressing the device above the rating listed in Table 29 may cause permanent damage to the device. These are stress ratings only and operation of the device, at these or any other conditions above those indicated in the operating sections of this specification, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect the device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Table 29. Absolute maximum ratings

| Symbol             | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |      | Max. | Unit   |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|--------|

| T <sub>A</sub>     | Ambient operating temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | - 40 | 85   | °C     |

| Т                  | Change to manage | UFDFPN5 | -65  | 150  |        |

| T <sub>STG</sub>   | Storage temperature  Sawn Wafer <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         | 15   | 25   | °C     |

| tsтg               | Sawn wafer <sup>(1)</sup> storage duration counted from ST production date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |      | 9    | months |

| T <sub>LEAD</sub>  | Lead temperature during soldering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |      | 2)   | °C     |

| V <sub>MAX_1</sub> | Max input voltage peak-to-peak amplitude between AC0 and AC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |      | 8.5  | V      |

|                    | Electrostatic discharge voltage on all pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |      |      |        |

| V <sub>ESD</sub>   | Human body model of ANSI/ESDA/JEDEC JS-001-2012 with C = 100 pF, R = 1500 $\Omega$ , R2 = 500 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |      | 2000 | V      |

<sup>1.</sup> Sawn wafer on UV tape kept in its original packing form.

DS13433 - Rev 5 page 25/36

Compliant with JEDEC Std J-STD-020D (for small body, Sn-Pb or Pb assembly), the ST ECOPACK 7191395 specification, and the European directive on Restrictions on Hazardous Substances (RoHS) 2002/95/EU.

#### 8.2 RF characteristics

This section summarizes the operating and measurement conditions, and the RF characteristics of the device.

The parameters in the RF characteristics table that follow are derived from tests performed under the Measurement Conditions summarized in the relevant tables.

Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parameters.

Table 30. RF characteristics

| Symbol                | Parameter                                                                                             | Condition <sup>(1)(2)</sup>                                                  | Min                 | Тур   | Max               | Unit |

|-----------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------|-------|-------------------|------|

| f <sub>C</sub>        | Frequency of external operating field (carrier)(3)                                                    | -                                                                            | 13.553              | 13.56 | 13.567            | MHz  |

| MI <sub>CARRIER</sub> | Carrier Modulation Index <sup>(3)(4)</sup>                                                            | -                                                                            | 90                  | -     | 100               | %    |

| t <sub>Boot_RF</sub>  | Time from field activation (unmodulated carrier) to the beginning of first PCD command <sup>(3)</sup> | -                                                                            | -                   | -     | 1                 | ms   |

| t <sub>RF_OFF</sub>   | Time between RF OFF and chip reset <sup>(3)</sup>                                                     | -                                                                            | -                   | -     | 0.1               | ms   |

| t <sub>1</sub>        | ISO/IEC 14443-2 pause A length <sup>(3)</sup>                                                         | f <sub>C</sub> = 13.56 MHz                                                   | 27.5/f <sub>C</sub> | -     | 41/f <sub>C</sub> | μs   |

| t <sub>2</sub>        | ISO/IEC 14443-2 pause A low time(3)                                                                   | f <sub>C</sub> = 13.56 MHz                                                   | 6/f <sub>C</sub>    | -     | t <sub>1</sub>    | μs   |