## NFC reader for industrial and consumer applications

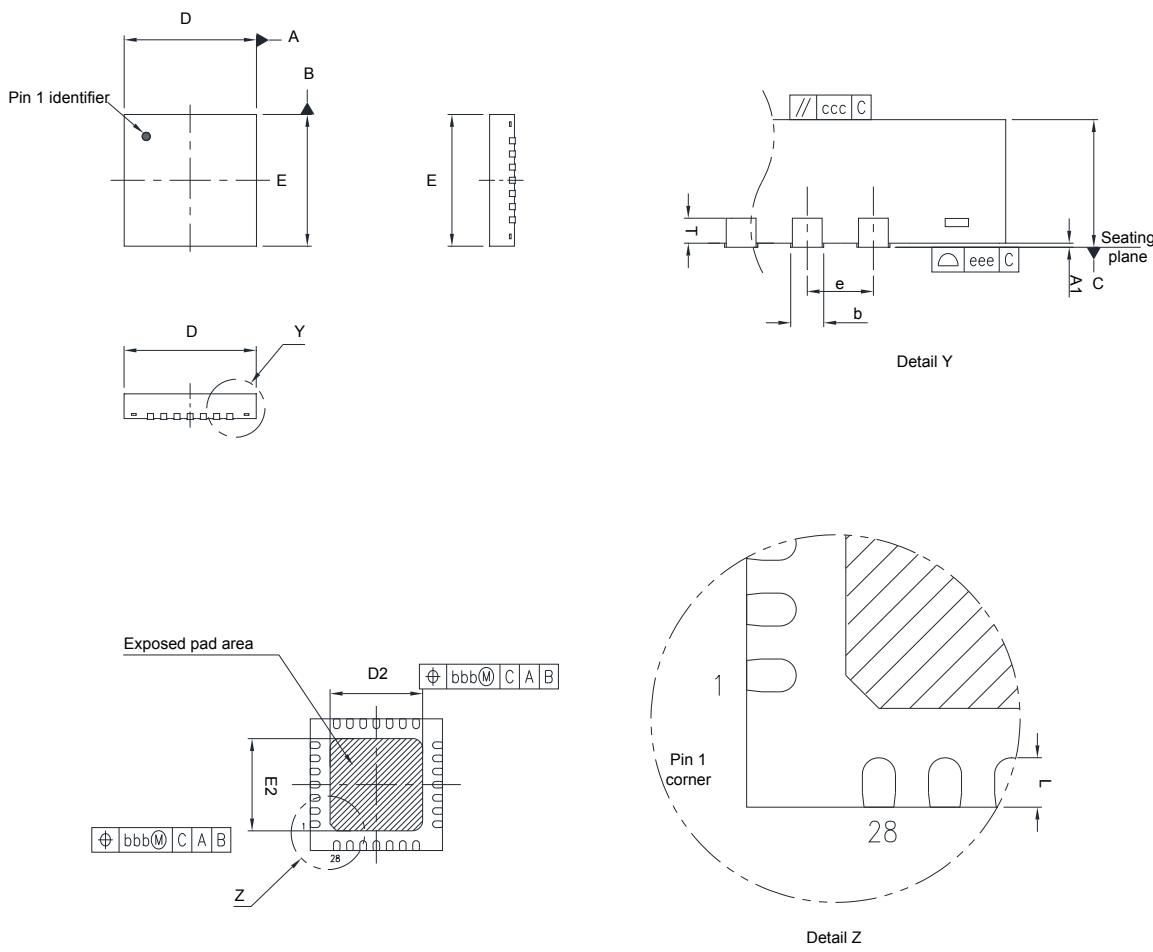

UFQFPN28

(4 x 4 mm)

### Features

#### Operating modes

- Reader/writer

- Card emulation

#### RF communication - Reader/writer

- NFC-A/ISO/IEC 14443A up to 848 kbit/s

- NFC-B/ISO/IEC 14443B up to 848 kbit/s

- NFC-V/ISO/IEC 15693 up to 212 kbit/s

- NFC-F/FeliCa™ up to 424 kbit/s

- Low-level modes to implement MIFARE Classic®-compliant and other custom protocols (Kovio BC, CTS, B')

| Product status |

|----------------|

| ST25R210       |

#### RF communication - card emulation

- NFC-A/ISO/IEC 14443A 106 kbit/s

- NFC-F/FeliCa™ 212/424 kbit/s

#### Key characteristics

- Passive P2P mode

- NFC Forum universal device

- Low-power inductive card detection

- I/Q demodulator with baseband channel summation

- Dynamic power output (DPO) controls the field strength to stay within given limits (software feature)

- Active wave shaping (AWS) reduces both over- and undershoots

- Noise suppression receiver (NSR) allows reception in a noisy environment

- Serial peripheral interface (SPI) up to 10 Mbit/s

- Possibility to drive one differential or two independent single-ended antennas

- TruST25 Link

#### Electrical characteristics

- Wide supply voltage range: 2.7 to 5.5 V

- Wide peripheral communication supply range: 1.65 to 5.5 V

- Wide ambient temperature range: -40 to +105 °C

- Quartz oscillator capable of operating with 27.12 MHz crystal with fast startup

## Application

The ST25R210 is suitable for a wide range of applications, among them:

- Access control

- Aliro ready

- NFC Forum-compliant NFC universal device

- WPC Qi out-of-band (OOB) communication and card protection NFC Reader

- WPC Ki power transmitter (PTx) communications unit

- ISO/IEC 14443 and ISO15693 compliant general-purpose NFC device

- FeliCa™ reader/writer

## 1 Description

Delivering high-end performance in a compact 4 x 4 mm package, the multipurpose NFC reader enables the convenience of contactless interaction and features for various end applications. It is specifically optimized for consumer and industrial end products.

The ST25R210 product is a universal NFC device supporting NFC initiator, NFC target, NFC reader, and NFC card emulation operations. The high output power, up to 1.6 W, facilitates easy integration into applications with small antennas. The reader offers an excellent read range and features improved low-power card detection (LPCD), which increases the detection range in inductive wake-up mode. During this low-power wake-up mode, the system detects the approach or removal of tags. The IC includes an RC oscillator and a programmable timer to automatically scan for cards or other NFC-enabled devices, such as smartwatches or phones, when in wake-up mode.

The device high sensitivity, supported by ST noise suppression receiver (NSR) technology, ensures successful reads even in noisy environments.

The ST25R210 product integrates an advanced analog front-end (AFE) and a highly integrated data framing system for NFC-A/B (ISO14443A/B), including higher bit rates, NFC-F (Felica™), NFC-V (ISO15693) up to 212 kbps, and NFC-A/NFC-F for card emulation mode.

The ST25R210 device achieves long-range and low-power card detection by measuring the I and Q channels, which represent the real and imaginary parts of the antenna signal. This approach minimizes power consumption. It operates across a wide power supply range (2.7 to 5.5 V), an ambient temperature range (-40 to +105°C), and a wide peripheral I/O voltage range (1.65 to 5.5 V). With its combination of high RF output power, low-power modes, and wide supply range, the device is ideal for all NFC applications.

The ST25R210 device is available in a compact 4 x 4 mm 28-pin UQFPN28 package, enabling the integration of NFC technology into small devices.

## 2 Functional overview

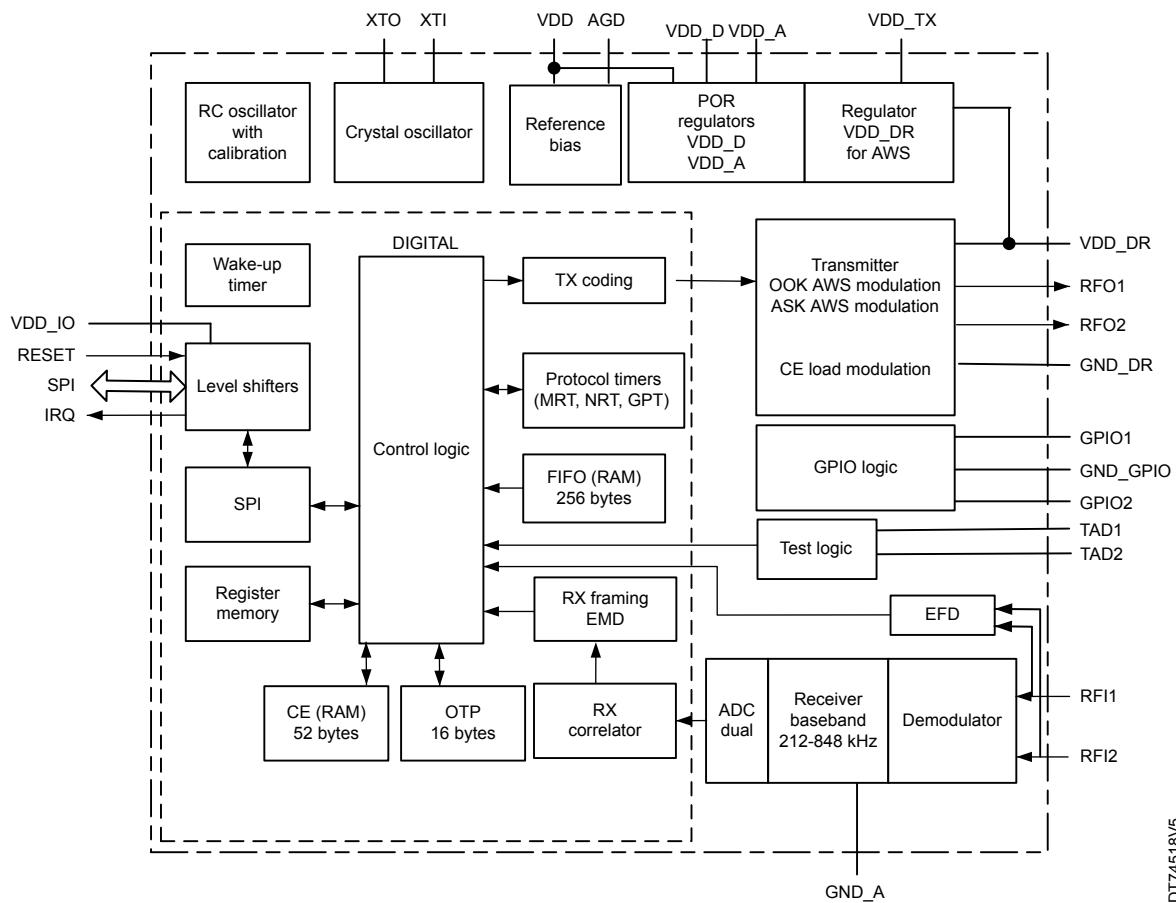

### 2.1 Block diagram

The block diagram is shown in the following figure.

Figure 1. ST25R210 block diagram

DT74518V5

## 2.1.1 Transmitter

The transmitter incorporates the drivers, which drive the external antenna through pins RFO1 and RFO2. Both single-ended and differential antenna configurations are supported. The transmitter block also generates the OOK or AM modulation of the transmitted RF signal during [Reader operation](#) and [Passive load modulation \(PLM\)](#) during card emulation (CE) operation.

## 2.1.2 Receiver

The receiver detects card modulation superimposed on the 13.56 MHz carrier signal. The receiver chain incorporates several features that enable reliable operation in challenging and noisy conditions. The same receiver is also used for card emulation operation.

The receiver is connected to the antenna via the pins RFI1 and RFI2. The output of the receiver is connected to the framing block that decodes the demodulated and digitized subcarrier signal.

## 2.1.3 Quartz crystal oscillator

The quartz crystal oscillator operates with 27.12 MHz crystals. At oscillator startup, the transconductance of the oscillator is increased to achieve a fast startup. Since the startup time varies with crystal type, temperature, and other parameters, the oscillator amplitude is monitored, and an I\_osc interrupt is sent when stable oscillator operation is reached.

## 2.1.4 Power supply regulators

Integrated power supply regulators ensure a high-power supply rejection ratio for the complete system. Different voltage regulators supply separate blocks to decouple from noise sources.

## 2.1.5 POR and bias

This block provides bias currents and reference voltages to all other blocks. It also incorporates a power on reset (POR) circuit, which provides a reset at power-up and at low supply levels.

## 2.1.6 RC oscillator and wake-up timer

The RC oscillator allows the wake-up timer to run and periodically trigger a measurement of the surroundings for low-power card detection mode.

## 2.1.7 Tx coding

This block encodes the transmit frames according to the selected RF communication mode and bit rate. It generates the start of frame (SOF), end of frame (EOF), cyclic redundancy check (CRC), and parity bits automatically. The data to be transmitted is taken from the FIFO.

## 2.1.8 Rx framing

This block decodes received frames according to the selected RF communication mode and bitrate. The SOF, EOF, CRC, and parity bits are automatically checked and removed by this block, except for the CRC. The received data is then placed in the first-in first-out (FIFO) buffer.

## 2.1.9 Control logic

This block drives all activity of the device based on the commands received through the serial interface and the configurations present on the registers.

## 2.1.10 FIFO

A 256-byte FIFO is available for exchanging data through the transmitter and receiver. Depending on the mode, it contains either data that has been received or must be transmitted.

## 2.1.11 SPI

A 4-wire SPI is available for communication between the device and the host.

## 2.1.12 External field detector (EFD)

The external field detector signals the presence of an external NFC field during card emulation.

## 2.1.13 RC oscillator

The RC oscillator provides a low frequency clock to the wake-up timer and digital logic block.

## 2.1.14 Wake-up timer

The wake-up timer periodically transitions the chip from power-down mode to ready mode during wake-up mode.

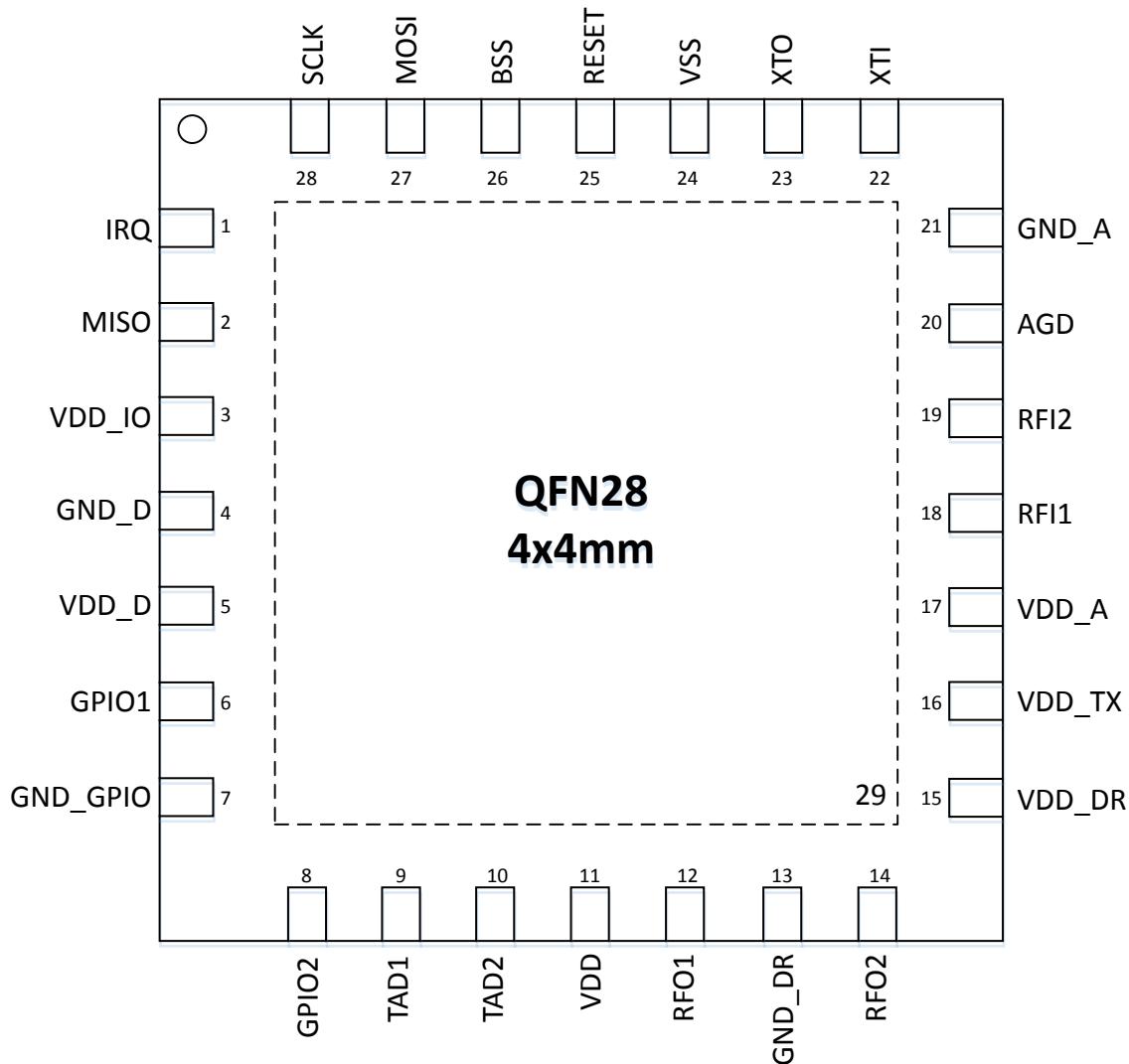

## 3 Pin and signal description

Figure 2. QFN28 pinout (top view)

DT79916V1

Table 1. QFN28 pin assignment

| Package | Pin name | Type <sup>1</sup> | Description                                                                                                                                       |

|---------|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| QFN28   |          |                   |                                                                                                                                                   |

| 1       | IRQ      | DO                | Interrupt request output                                                                                                                          |

| 2       | MISO     | DO_T              | Serial peripheral interface data output                                                                                                           |

| 3       | VDD_IO   | S                 | External peripheral communication supply                                                                                                          |

| 4       | GND_D    | S                 | Digital ground                                                                                                                                    |

| 5       | VDD_D    | AOS               | Regulated supply for digital block                                                                                                                |

| 6       | GPIO1    | ADO               | GPIO to switch between reader operation and CE operation matching network or digital output. When not being used, it must be kept unconnected.    |

| 7       | GND_GPIO | S                 | GPIO ground                                                                                                                                       |

| 8       | GPIO2    | ADO               | GPIO to switch between reader operation and CE operation matching network or digital output. When not being used, it must be kept to unconnected. |

| 9       | TAD1     | ADIO              | Analog/Digital test pin. When not being used, it must be kept not connected.                                                                      |

| 10      | TAD2     | ADIO              | Analog/Digital test pin. When not being used, it must be kept not connected.                                                                      |

| 11      | VDD      | S                 | External main positive supply                                                                                                                     |

| 12      | RFO1     | AO                | Antenna driver output                                                                                                                             |

| 13      | GND_DR   | S                 | Antenna driver ground, driver VSS. It must be connected to thermal pad via the shortest possible connection.                                      |

| 14      | RFO2     | AO                | Antenna driver output                                                                                                                             |

| 15      | VDD_DR   | AOS               | Regulated supply for antenna driver                                                                                                               |

| 16      | VDD_TX   | S                 | External main positive supply for driver                                                                                                          |

| 17      | VDD_A    | AOS               | Regulated supply for analog                                                                                                                       |

| 18      | RFI1     | AI                | Receiver input                                                                                                                                    |

| 19      | RFI2     | AI                | Receiver input                                                                                                                                    |

| 20      | AGD      | AIO               | Analog reference voltage                                                                                                                          |

| 21      | GND_A    | S                 | Analog ground                                                                                                                                     |

| 22      | XTI      | AI                | Crystal oscillator input                                                                                                                          |

| 23      | XTO      | AO                | Crystal oscillator output                                                                                                                         |

| 24      | VSS      | S                 | Ground, die substrate potential                                                                                                                   |

| 25      | RESET    | DI                | Reset input                                                                                                                                       |

| 26      | BSS      | DI                | Serial peripheral interface enable (active low)                                                                                                   |

| 27      | MOSI     | DI                | Serial peripheral interface data input                                                                                                            |

| 28      | SCLK     | DI                | Serial peripheral interface clock                                                                                                                 |

| 29      | EP / VSS | S                 | Ground, die substrate potential, via exposed die pad                                                                                              |

1. S: Power supply pin, AIO: analog I/O, AI: analog input, AO: analog output, ADIO: analog/digital input/output, AOS: analog output / supply input, DI: digital input, DO: digital output, DO\_T: digital output/tri-state.

## 4 Device description

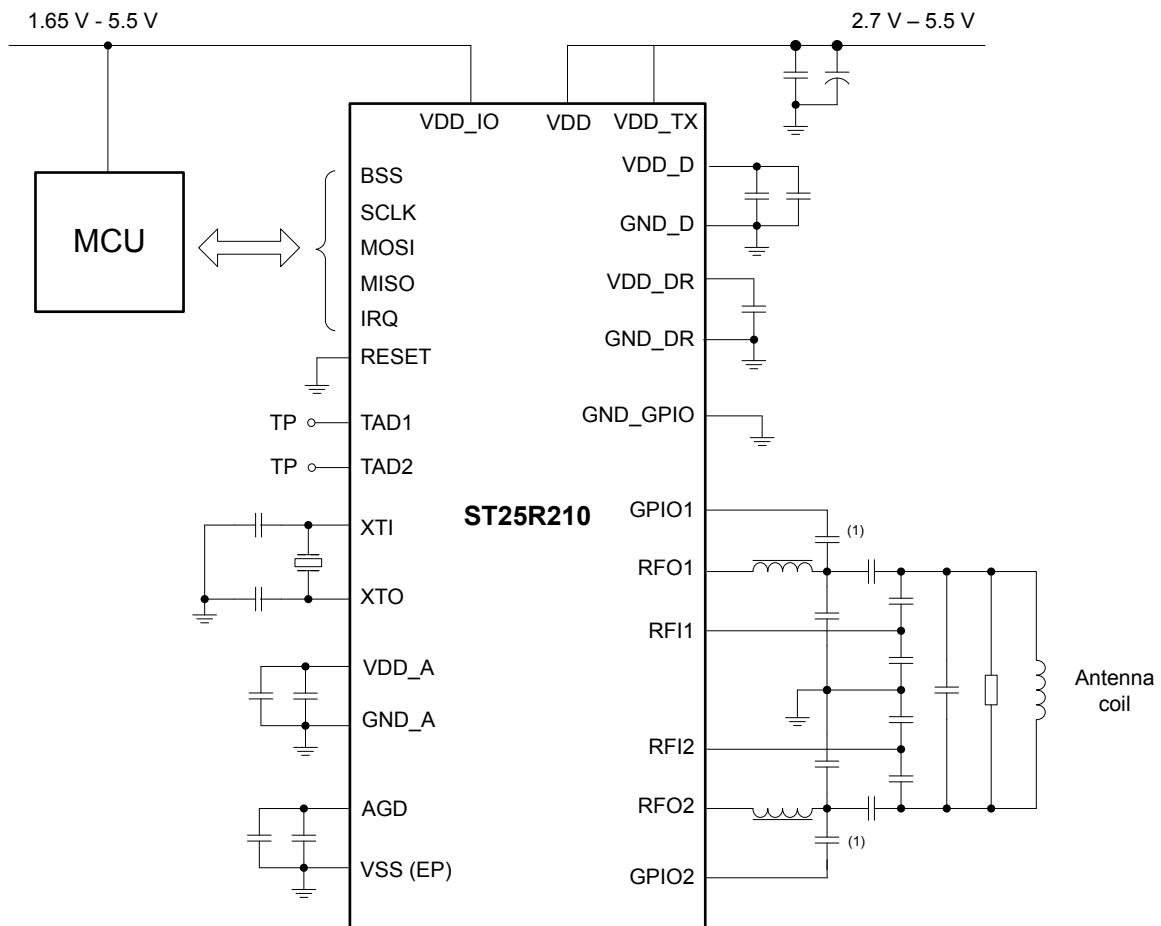

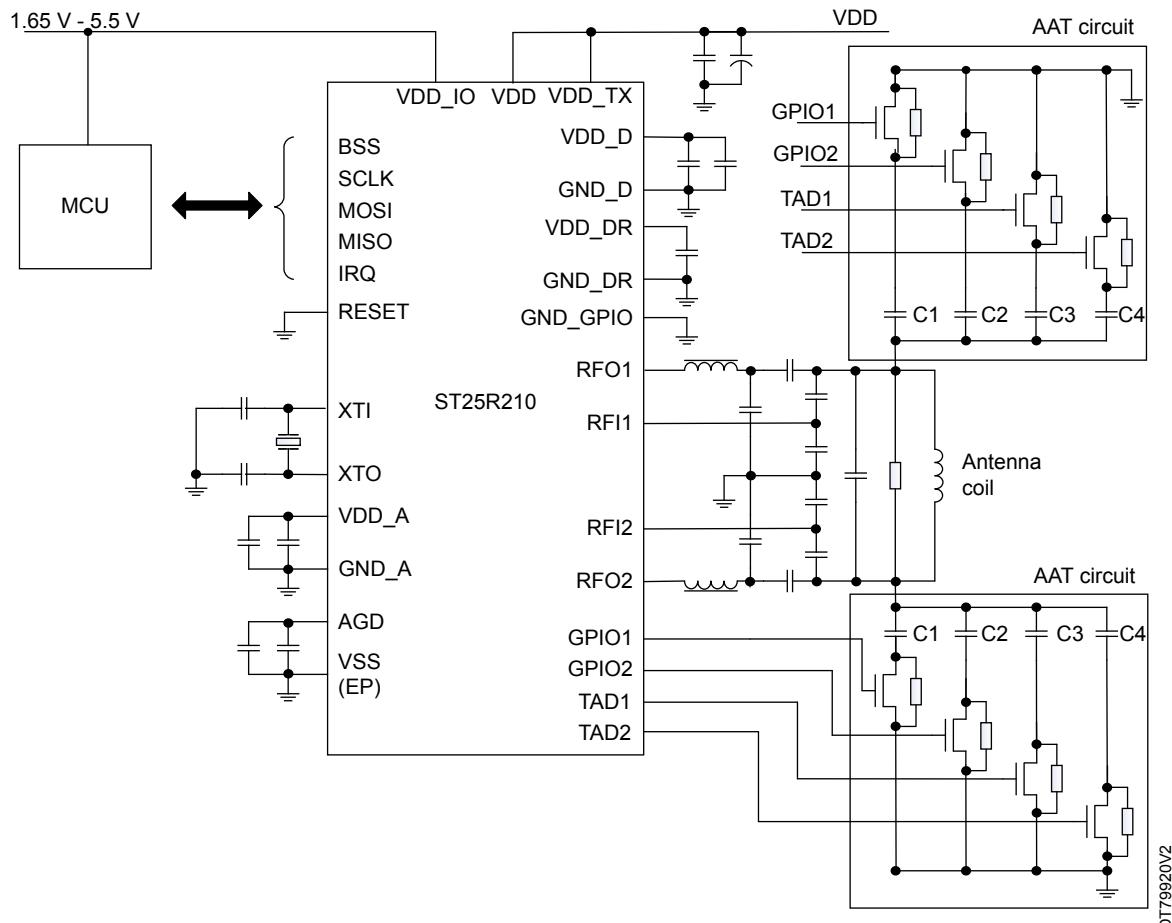

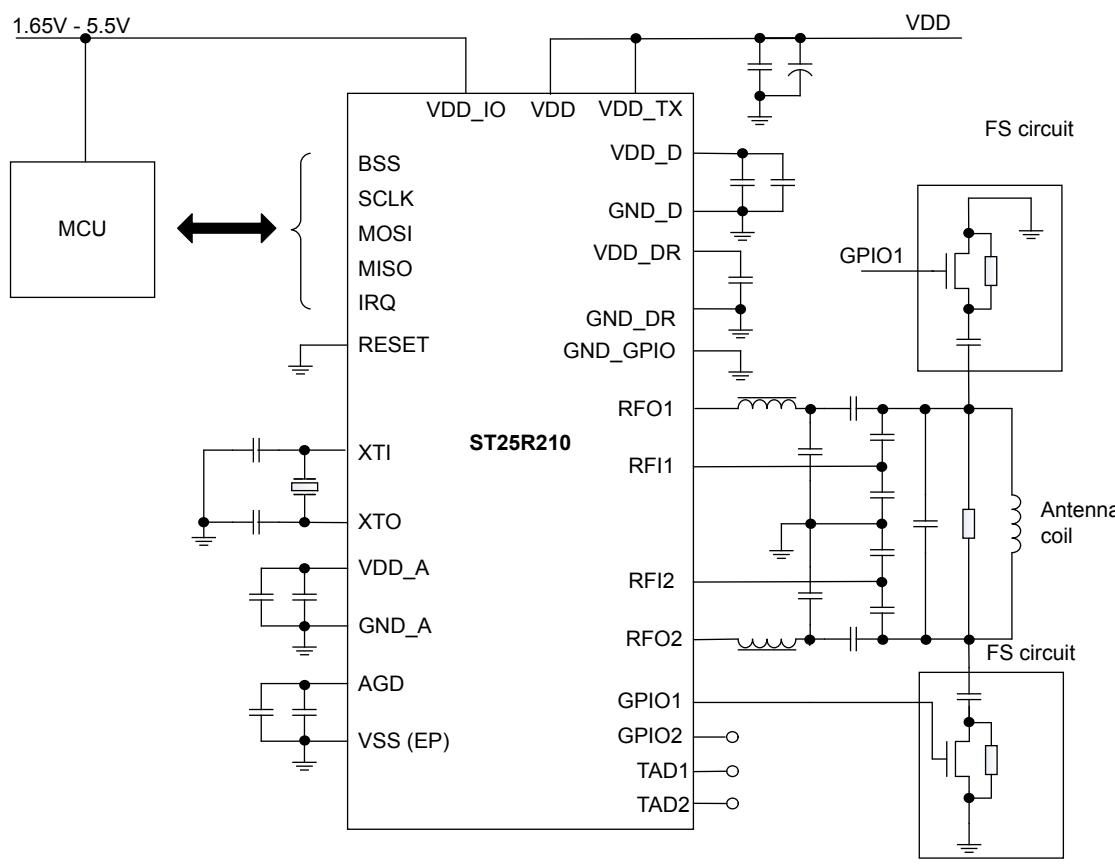

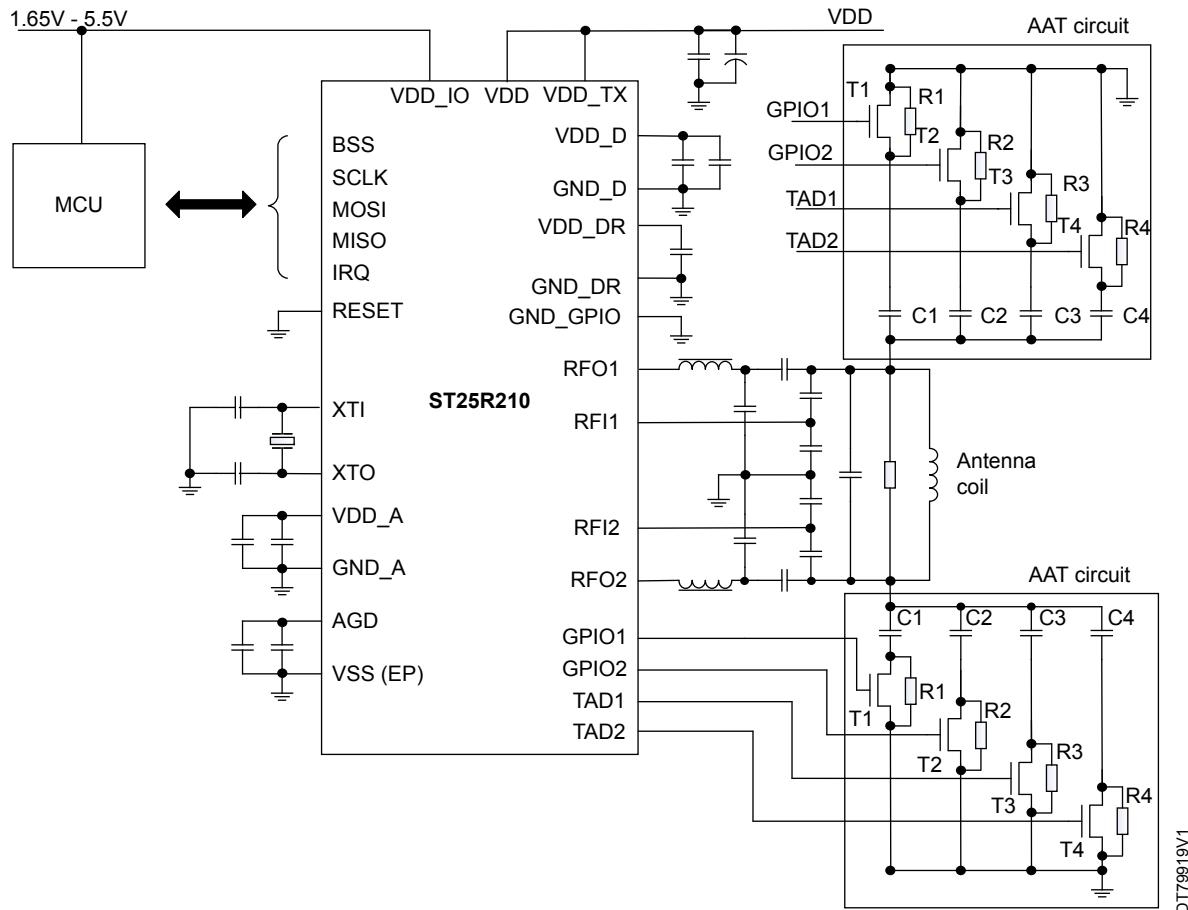

### 4.1 System diagram

The minimum system configuration is shown below for a differential antenna configuration.

Figure 3. Minimum system configuration

1.: Only required for CE operation. If only RW operation is required, the capacitor can be d.n.p. and the pin left open.

DT79917V4

Table 2. Recommended capacitor values

| Pin    | Capacitor 1 <sup>(1)</sup> | Capacitor 2 <sup>(2)</sup> | Comment |

|--------|----------------------------|----------------------------|---------|

| VDD    | 10nF                       | 2.2µF                      | -       |

| VDD_TX | 10nF                       | 2.2µF                      | -       |

| VDD_IO | 100nF                      | d.n.p.                     | -       |

| VDD_DR | 47nF                       | d.n.p.                     | -       |

| VDD_D  | 10nF                       | 2.2µF                      | -       |

| VDD_A  | 10nF                       | 2.2µF                      | -       |

| AGD    | 10nF                       | 1.0µF                      | -       |

1. Capacitor 1 should be placed as close as possible to the associate pin.

2. Capacitor 2 should be placed as close as possible to Capacitor 1.

Note: **d.n.p.** means "do not populate" (not to be placed on the PCB).

## 5 Application information

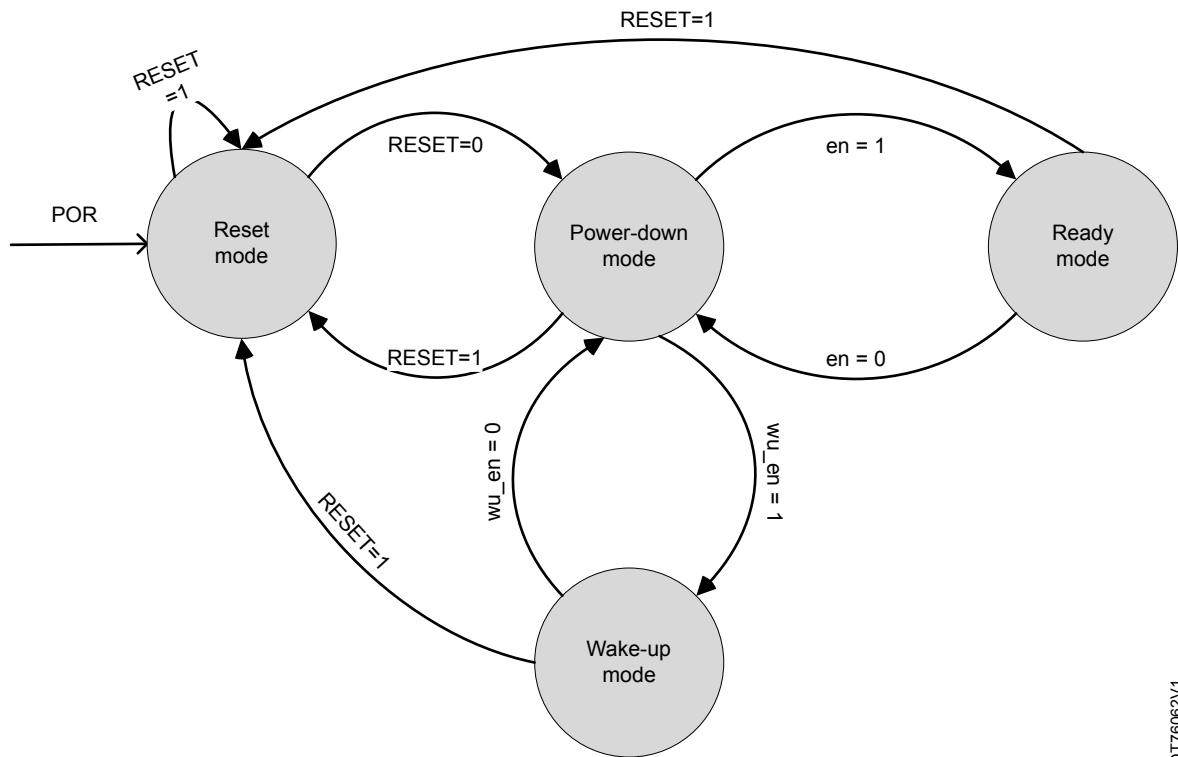

### 5.1 Operation modes

The device supports four operating modes.

#### 5.1.1 Reset mode (RESET)

When the device is supplied with VDD, VDD\_TX, and VDD\_IO, and the RESET pin is high, the device is in reset mode.

All blocks are deactivated, no clock is present, and current consumption is minimized.

#### 5.1.2 Power-down mode (PD)

If the RESET pin is low at power-up or after the RESET pin state changes from high to low, the device enters power-down mode. In this mode, the AFE static power consumption is very low, but SPI communication is possible, in addition to register access to those in the PD domain.

The following blocks are active in PD mode:

- VDD\_D regulator (1 V) in low-power mode

- Registers in the PD domain

- SPI block and IRQ logic

#### 5.1.3 Wake-up mode (WU)

Wake-up mode is controlled through the wu\_en bit. In this mode, the device senses changes in antenna properties at regular time intervals and triggers an IRQ if a change is detected.

The following blocks are active in WU mode:

- VDD\_D regulator (1 V) in low-power mode

- Registers in PD domain

- RC oscillator

- WU timer

- SPI block and IRQ logic

#### 5.1.4 Ready mode (RD)

Ready mode is controlled by the en bit. In this mode the regulators and crystal oscillator are enabled, and the device is ready to transmit or receive.

The following blocks are active in RD mode:

- VDD\_D regulator (1 V) in normal power mode

- All registers (both in PD and RD domain)

- Main logic

- VDD\_A and VDD\_DR regulators

- Crystal oscillator

- SPI block and IRQ logic

When RD mode is reached, the device issues an I\_osc interrupt.

The following diagram shows the transition from one state to another:

Figure 4. Transition from one state to another

DT76062v1

## 5.2 Power-on sequence

Once powered and once the RESET pin is low, the device enters the PD mode. The content of all registers is set to its default state. The device can be set into any other operation mode except RESET by changing the configuration in the [Operation register](#).

Changing from PD mode to RD mode and preparing for communication comprises:

- Apply the appropriate configuration on registers: operation and general configuration registers

- Set en = 1 in the operation register and wait for the device to get ready with the oscillator stabilized (notified by the l\_osc interrupt and osc\_ok status)

- The adjust regulator direct command should be executed when the carrier is enabled. When coming from RD mode with disabled VDD\_DR and disabled field, execute the following:

- Set vdddr\_en to 1

- Wait at least 10  $\mu$ s

- Set tx\_en and rx\_en to 1

- Execute adjust regulator direct command

- Additionally, the direct command calibrate RC must be issued.

Once the above-mentioned points are done, the device is ready for communication.

## 5.3 Transmitter

The transmitter contains two identical push-pull driver blocks connected to the RFO1 and RFO2 pins. These drivers are differentially driving the external antenna LC tank via the antenna matching network. It is also possible to operate only one of the two drivers by setting the single bit in the [General configuration register](#) and selecting which RFO/RFI to be used on rfo2 bit.

### 5.3.1 Output resistance

Each driver is composed of eight segments having binary weighted output resistance. The MSB segment typical ON resistance is  $2 \times RRFO$ . When all segments are turned on, the output resistance is defined by  $RRFO$ . Usually, all segments are turned on to define the normal transmission (unmodulated) level. It is also possible to switch off certain segments when driving the unmodulated level to drive the circuitry with a higher impedance driver.

The `d_res` bits in the [Tx driver configuration register](#) define the resistance during the normal transmission. The default setting is the minimum available resistance.

When using the single driver mode, the number of external components and therefore the cost of the antenna LC tank components is halved, but also the output power is reduced. In single mode it is possible to connect two antenna LC tanks to the two RFO outputs and multiplex between them by controlling the `rfo2` bit in the [General configuration register](#).

To transmit data, the transmitter output level needs to be modulated. AM and OOK modulation principles are supported. The type of modulation is defined by setting the `tr_am` bit in the [Tx modulation register 1](#).

### 5.3.2 Driver Tx modulation

During the OOK modulation (for example, NFC-A or NFC-V), the transmitter drivers stop driving the carrier frequency. Therefore, the amplitude of the antenna LC tank oscillation decays. The time constant of the decay is defined by the LC tank Q factor.

AM modulation (for example, NFC-B) is done via a reduction of the `VDD_DR` regulator-regulated voltage that supplies the drivers during the modulation state.

The AM modulation level is set by the `am_mod` bits in the [Tx modulation register 1](#).

AM modulation must be enabled and the modulation index must be set correctly for the following protocols:

- NFC-B

- FeliCa

Depending on the applicable standard, the modulation index is set in a range between 8% and 97% in the [Tx modulation register 1](#). The modulation scheme, AM modulation or OOK modulation, can be selected by the `tr_am` bit in the [Tx protocol register 1](#).

### 5.3.3 Passive load modulation

The ST25R210 enables passive load modulation using three different methods:

- Internal driver load modulation

- Load modulation with an external NMOS transistor

- Load modulation via the EMI filter switching

The driver load modulation is selected by the `lm_dri` bit for internal driver load modulation in [CE modulation register 2](#), and the external NMOS modulation is selected by the `lm_trim` or the `lm_gpio` option bits.

Normally, the internal driver is used for the generation of the passive load modulation. In case higher load modulation is required, the device also supports external passive load modulation through an NMOS transistor. Advanced antenna tuning (AAT) and the frequency shift circuit (FSC) use NMOS transistors to switch the matching between reader and card emulation operation.

Both the `lm_trim` or `lm_gpio` option bits enable the load modulation through an external NMOS transistor and a capacitor. In addition, `lm_gpio` can be used to perform the load modulation via the EMI capacitor switching.

The following table provides an overview about the passive load modulation capabilities:

Table 3. Modulation scheme

| Bit                  | LM through driver <sup>(1)</sup> | LM through AAT circuit<br>(1-4 bits) <sup>(2)</sup> | LM through frequency shift<br>circuit<br>(1-bit) <sup>(2)</sup> | LM through EMI capacitor<br>switching <sup>(2)</sup> |

|----------------------|----------------------------------|-----------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|

| <code>lm_dri</code>  | Yes                              | Yes                                                 | Yes                                                             | Yes                                                  |

| <code>lm_trim</code> | -                                | -                                                   | Yes                                                             | -                                                    |

| <code>lm_gpio</code> | -                                | Yes                                                 | Yes                                                             | Yes                                                  |

1. Main mechanism to fine-tune the passive LM strength. Based on antenna size and matching, an additional mechanism might be required to pass the ISO 10373-6 loading effect or NFC Forum Delta Vov Ratio (DVR). Also, the `ce_res` and `cem_res` bits need to be configured accordingly.

- Additional circuit that can be used for statically switching the matching between reader and card mode or increase/decrease passive LMA in combination with  $Im\_dri$ .

Also, the gpio\_en, tad\_en, trim\_ce, gpio\_ce, trim\_rw and gpio\_rw bits need to be configured accordingly. If the antenna has too strong coupling with the reference antenna, one of the three methods (AAT, FSC, EMI capacitor switching) can be implemented to switch between reader operation antenna tuning and card emulation antenna tuning.

#### 5.3.3.1 LM through driver

The driver load modulation is based on the change of the driver impedance. The ce\_res value depends on the matching and the antenna configuration. It is typically chosen to fulfill the loading effect test. The ce\_res bits must be set before entering passive target mode.

During the non-modulated and the modulated states the driver output impedance is defined, respectively, by the ce\_res and the cem\_res option bits. During the unmodulated state, the output impedance is defined by ce\_res option bits. During modulation the output impedance is defined by the cem\_res option bits. Once defined, the ce\_res option bits should be kept at the same value during card emulation operation.

Typically, a low driver impedance during the modulated state and a high driver impedance for the non-modulated state is used. It is also possible to reverse the modulation by switching the ce\_res and cem\_res settings.

#### 5.3.3.2 LM through AAT

To increase the load modulation amplitude, the AAT circuit can be used. This circuit may not be only used to switch between reader and card emulation antenna matching, it can also be used to tune the antenna to a certain matching impedance in reader or card emulation operation.

Figure 5. AAT circuit example

Setting the `lm_gpio` option bits to ones, the `GPIO1` and `GPIO2` pins are driven by the digital signal of the load modulation signal. The value of the `gpio_ce` and `gpio_rw` bits sets if the polarity is positive or inverse for the external load modulation. The capacitors of the AAT circuit should be binary-weighted; therefore, `GPIO1` and `GPIO2` can achieve different LM strength.

#### 5.3.3.3 LM through frequency shift circuit

The frequency shift circuit (FSC) allows switching between reader operation matching and card emulation operation matching to lower the loading effect in card emulation operation. To switch between the two static matchings, the same principle as for AAT can be chosen, but the number of trimming elements can be reduced to one transistor and one capacitor per RFO. It is recommended to connect the FSC to one of the GPIO pins. If the FSC is connected to one GPIO the corresponding `lm_gpio` bit can be set. If the FSC is connected to one of the TAD pins, the `lm_trim` should not be used. Using the `lm_gpio` or the `lm_trim` bits, the matching switches from card emulation to reader/writer mode matching in or out of phase with the digital signal of the load modulation (848 kHz subcarrier or 424 / 212 kHz modulation signal).

Figure 6. Frequency shift circuit example

#### 5.3.3.4 LM through EMI capacitor switching

An example of a circuit capable of switching the EMI capacitor can be found in the Figure 1.

The capacitor connected between the EMI filter and `GPIO1`, and EMI filter and `GPIO2` pin is pulled to GND through an internal MOS transistor. Since this capacitor can build a series resonating circuit with parasitic components (bond wires, PCB traces), special care must be taken when selecting the component value. During reader-writer operation, this MOS transistor needs to be enabled (`gpio_en` = 0x0 and `gpio_rw` = 0x3), and in card emulation operation, the MOS transistor needs to be disabled (`gpio_en` = 0x0 and `gpio_ce` = 0x0). By setting the `gpio_en` bits to 0, the push-pull driver used for the AAT circuit is disabled, and the internal MOS transistor is selected. By setting the `gpio_rw` bits to 1 the internal MOS transistor is low ohmic. Setting the `lm_gpio` option bits to ones, the `GPIO1` and `GPIO2` pins are driven by the digital signal of the load modulation signal.

## 5.4

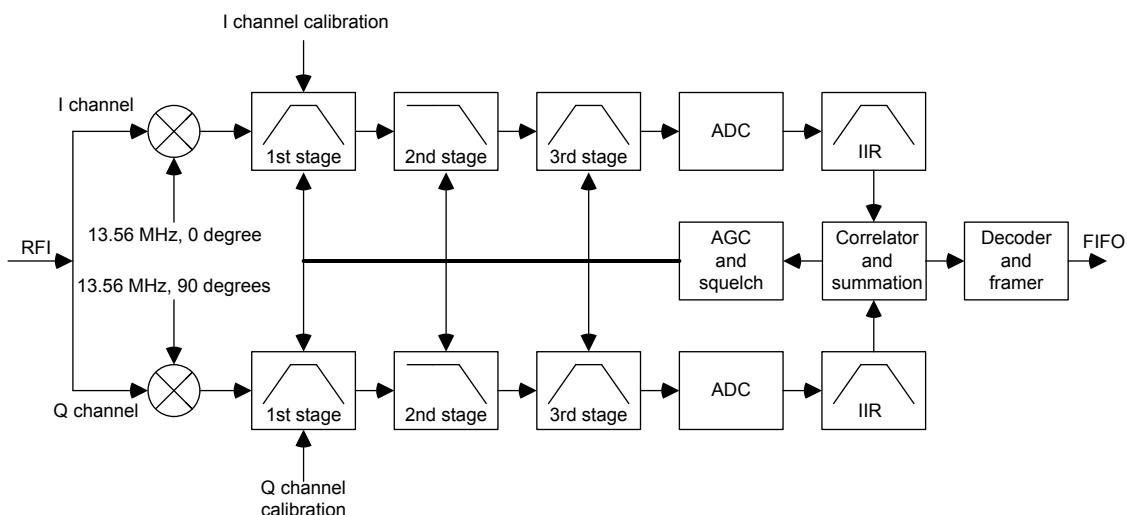

## Receiver

The receiver performs the demodulation of the tag subcarrier modulation that is superimposed on the 13.56 MHz carrier frequency. It performs an I/Q demodulation, amplification, band-pass filtering, and digitization of the subcarrier signals. It also performs RSSI measurements, automatic gain control (AGC), and squelch functions. The reception chain has two separate channels for the I and Q demodulation. I and Q channels result in mixing the 13.56 MHz carrier signal coming from the antenna with a local 13.56 MHz clock generated by the crystal oscillator. The I and Q mixing clock are 90 degrees phase-shifted. The reception framing is done automatically by the receiver logic. The receiver is switched on when the rx\_en bit in the [Operation register](#) is set to 1.

Figure 7. Receiver block diagram

DT76065V1

## 5.4.1

## Demodulation stage

The I/Q demodulation made up of two mixer circuits, each driven by local oscillator signals that are phase-shifted by 90° relative to each other and derived from the crystal oscillator. The outputs of the two mixers are connected to two equal baseband reception chains and to the decoding logic.

## 5.4.2

## Filter and gain stages

The receiver chain has band pass filtering characteristics. This band pass filter consists of three stages. Each stage has a static gain and an AGC controlled attenuation. The filtering is optimized to pass the subcarrier frequencies while rejecting the carrier frequency, low frequency noise, and DC component. The first and third stages have a selectable first order high pass filter and a fixed first order low pass filter. The high pass filter characteristics of the first and third stages can be controlled via the hpf\_ctrl bits in the [Rx analog settings register 1](#). The low pass filter characteristics are fixed for both stages. The second stage consists of a second order fixed low pass filter.

The maximum gain of the first and the second stage is 20 dB and can be reduced in 3 dB steps by the AGC. The gain of the third stage is 6 dB if gain\_boost is enabled by setting the gain\_boost bit to 1 in the [Rx analog settings register 1](#), which increases the max gain by an additional 3 dB. The total gain of the filter and gain stage is 49 dB including the gain boost. A default gain reduction for the AGC can be configured via the afe\_gain\_rw bits in the [Rx analog settings register 2](#).

The same filter blocks can also be used for other operation modes. In all modes, the starting gain is set through the corresponding gain reduction. The gain in wake-up mode can be configured by the afe\_gain\_td in Rx analog settings 2 register. The gain in card emulation operation can be configured by the afe\_gain\_ce bits in the [Rx analog settings register 3](#).

The chip features a secondary filter stage after the analog to digital converter. It consists of an infinite impulse response (IIR) low pass filter and an IIR high pass filter. Its coefficient can be configured in the [Rx digital settings register 1](#) by setting the lpf\_coef and hpf\_coef bits.

#### 5.4.3 Analog-to-digital converter

The analog-to-digital converter digitizes the signal coming from the filter and the gain stages. In wake-up mode, the ADC output is stored in the I-channel WU ADC display register and the Q-channel WU ADC display register.

#### 5.4.4 Correlator system

The correlation system is designed to maximize the receiver sensitivity and the selectivity to the subcarrier frequencies found in a tag's reply. To achieve this, the subcarrier signal coming from the tag is compared to a local subcarrier clock. The best signal to noise ratio is achieved if these two signals match. I and Q channel signals are combined via the summation block to remove the need for a channel selection while simultaneously improving the performance. The same topology is used to achieve NFC-A and NFC-B 106-848 kbit/s, FeliCa 212 kbit/s and 424 kbit/s, and NFC-V single subcarrier 26 kbit/s, 52 kbit/s 106 kbit/s and 212 kbit/s demodulation.

The correlator has two main modes of operation - Manchester and BPSK (binary phase shift keying). Manchester refers to the Manchester code subcarrier modulation used in NFC-A 106 kbit/s and NFC-V single subcarrier protocols. BPSK refers to the subcarrier modulation used in the remaining protocols and data rates. In BPSK mode, the local subcarrier clock follows the phase of the input subcarrier signal. The bit information is coded into the phase of the input subcarrier, so a comparison between the input phase and clock phase returns the bit data. In Manchester mode, the local subcarrier clock does not follow the phase of the input subcarrier signal as the bit information is coded into subcarrier presence (amplitude). The correlator comprises an additional circuitry, used by both modes, for symbol recognition and subcarrier presence detection.

The iir\_coef1 and iir\_coef2 bits in the [Correlator settings register 2](#) adjust the correlator internal filter.

#### 5.4.5 Automatic gain control

The automatic gain control configures the gain reduction in the filter and gain stage to input an optimal signal into the correlator. It can be enabled in the [Rx digital settings register 1](#) by setting the agc\_en bit to 1. As long as the input signal is larger than the threshold defined by the agc\_thr bits in the [Correlator settings register 2](#), the gain is reduced in 3 dB steps. In reader operation, the AGC is only active at the start of reception. In card emulation operation, the AGC is operating during the reception when activated via the agc\_en bit set to 1. There are two special cases where the AGC is behaving differently. In NFC-F CE reception, the AGC freezes after the subcarrier has been detected. In NFC-A reception, the AGC freezes when the bit ce\_agc\_freeze is set to 1. The result of the gain reduction after the AGC is complete can be read in the afe\_gain bits of the [Analog display register 2](#). It displays the actual gain reduction during the last reception.

#### 5.4.6 Squelch

The squelch is reducing the receiver gain based on the noise level. Due to the high starting gain of the receiver, noise could be decoded and corrupt the communication between reader and card. The squelch enables the reception in noisy environments if the signal level is above the noise level.

Automatic squelch is enabled by the sq\_en option bit in the [Mask receive timer configuration register 1](#). It is activated automatically after the end of the transmission. The delay can be configured in the [Mask receive timer configuration register 1](#) by setting the sq\_del bits. The squelch is terminated when the mask receive timer (MRT) reaches the value defined in the [Mask receive timer configuration register 2](#) or the squelch timer defined in the [Squelch timer configuration register](#) is expired.

This mode is primarily intended to suppress the noise generated by the tag processing before the tag response (covered by MRT) and environmental noise.

After the squelch time is expired, the determined gain setting is applied for the next reception.

The gain setting acquired by the squelch is cleared by sending a direct command clear Rx gain.

If the card response starts during the squelch, the gain is reduced to ignore the modulation. Such scenarios are happening, for example, during the ISO10373-6 EMD recovery tests.

#### 5.4.7 RSSI

The RSSI is an indication of the estimated signal level at the input of the IC. It is used for diagnostic and observational purposes. The RSSI is calculated from the amplitude of the signal at the input of the correlator. The measurements take place in intervals that start when the receiver is enabled and end when the receiver is disabled. The information about the I and Q RSSI measurements is reset only when the receiver is opened for a valid reception (when issuing the rx\_start interrupt) or when a direct command to clear the Rx gain is issued. The RSSI information can be read after a tag reply without any timing constraints. The result takes the AGC gain reduction into account. The result of the measurement can be read from the [RSSI display register 1](#) and the [RSSI display register 2](#).

#### 5.4.8 **Digitizing stage**

The digitizing stage produces a digital representation of the subcarrier signal from the receiver. This digital signal is processed by the receiver framing logic.

#### 5.4.9 **ADC to CE memory recording**

The envelope of the carrier signal can be sampled and stored in the card emulation memory. This feature can be used to measure the rising and falling edge of the modulation signal in reader operation. The feature can be enabled by setting the trigger to falling, rising, or both edges using the `adc_cemem` bit in the test register ADC to CE memory. The sampling rate can be selected by setting the bit `adc_cemem_rate` to 13.56 MHz or 6.78 MHz, which allows recording 3.83  $\mu$ s or 7.67  $\mu$ s.

The input source can be selected by setting the bit `adc_cemem_src` to ADC or correlator input. The input source ADC returns a 6-bit result which is saturated to a value of 63. The input source correlator returns an 8-bit result which is saturated to a value of 250. The input gain can be configured by the bits `afe_gain_ce` in the [Rx analog settings register 3](#).

## 5.5

## Antenna tuning

The ST25R210 supports antenna tuning through an external NMOS transistor and external multilayer ceramic capacitor (MLCC). The following figure shows the minimum configuration when using four tuning capacitors for each RFO channel. Per channel four NMOS transistor, four MLCC capacitor and four resistors are used.

Figure 8. Antenna tuning schematic

The external MLCC capacitors should be connected to the parallel capacitor on one side and to the drain of the NMOS transistor on the other side. The source of the NMOS transistor is connected to GND. Both the capacitor and the NMOS transistor are connected in parallel to the parallel capacitor of the matching network. By driving the gate of the transistor T1 to high the capacitor C1 is added in parallel to the parallel capacitor of the matching network. This causes a change of the resonance frequency of the NFC antenna. The R1 resistor is discharging the capacitor slowly if the NMOS transistor is high ohmic. The value of the resistor can be very high (~1 MΩ). The capacitors C1 to C4 are binary weighted. Typical values are 5.6 pF, 12 pF, 27 pF, and 56 pF, which allow increasing the parallel capacitor by 0pF to 100.6 pF in 16 steps. The values of C1 to C4 may be adapted based on the desired tuning range of AAT.

The gates of the NMOS transistors can be connected to the GPIO1, GPIO2, TAD1, and TAD2 pins. The pins need to be configured to push-pull configuration. By setting the gpio\_en and tad\_en bits to 1 in the [CE modulation register 2](#), the push-pull mode is enabled.

The state of the push-pull output can be defined in the [GPIO control register](#) for reader operation and the card emulation operation. The outputs are automatically changed based on the GPIO control register content depending on if the reader is in for reader operation and card emulation operation.

## 5.6

### RC oscillator

The RC oscillator is used to support the low-power WU mode and it runs at a nominal frequency of 26.48 kHz. It is enabled when the device enters the WU mode, and disabled when the device goes to PD or RD mode. Additionally, it may be enabled by executing the direct command to start the wake-up timer.

## 5.7

### Quartz crystal oscillator

The quartz crystal oscillator operates at 27.12 MHz. This operation is enabled when the option bit en is set to 1.

An I\_osc interrupt is sent to inform the microcontroller when the oscillator amplitude is sufficiently high, meaning that the frequency is stable. The oscillator is based on an inverter stage supplied by a controlled current source. A feedback loop controls the bias current to regulate the amplitude on XTI pin to approximately 1 V<sub>PP</sub>. The amplitude of the XTI signal depends on the parameters of the crystal. Depending on these parameters, the XTI signal can be greater than 1 V<sub>PP</sub> at the lowest possible drive level. It must be ensured that V<sub>Osc\_PP</sub> in the Table 1 is not exceeded.

Division by two ensures that the 13.56 MHz signal has a duty cycle of 50%.

The oscillator is additionally enabled when the transition to RD mode is triggered in card emulation operation by detecting an external magnetic field or when the wake-up timer expires and a wake-up measurement is performed.

The status of the oscillator can be observed by checking the bit osc\_ok. This bit is set to one when the oscillator frequency is stable.

## 5.8

### Timers

The ST25R210 contains several timers, which eliminate the need to run counters in the controller, thus reducing the effort of the controller's code implementation and improve the portability of the code to different controllers.

Every timer has one or more associated configuration registers in which the timeout duration and different operating modes are defined. These configuration registers must be set while the corresponding timer is not running. Any modification of timer configuration while the timer is active may result in unpredictable behavior. All timers are stopped by the direct command stop all activities.

#### 5.8.1

##### Mask receive timer (MRT)

In reader operation, this timer blocks the receiver and the reception process in the framing logic by keeping the rx\_on signal low after the end of the Tx during the time the tag reply is not expected. While the mask receive timer is running, the squelch is automatically turned on when enabled. The MRT does not produce an IRQ.

The MRT timeout is configured in the [Mask receive timer configuration register 2](#) and is automatically started at the end of the data transmission (at the end of EOF). The MRT can be triggered by the start mask receive timer direct command. In this case, the squelch is enabled according to the [Squelch timer configuration register](#). The MRT also starts in the PD mode when card emulation operation is enabled. After the initiator field has been detected, the regulator, the crystal oscillator, the receiver, and the MRT are enabled. After the MRT expires, the receiver starts to detect the start of the initiator message.

#### 5.8.2

##### No-response timer (NRT)

The purpose of this timer is to observe whether a response is detected during a configured time starting at the end of the transmission. The I\_nre flag in the [IRQ status register 2](#) is signaling an interrupt event resulting from this timer timeout. The NRT value is defined by writing the [NRT and GPT configuration register 2](#) and the [NRT and GPT configuration register 3](#). Operation options are defined by setting the nrt\_emv and nrt\_step bits in the [NRT and GPT configuration register 1](#). The NRT is automatically started at the end of the transmission. The nrt\_step bit configures the time step of the no-response timer. Two steps are available, 64/f<sub>C</sub> (4.72 µs) and 4096/f<sub>C</sub> covering, respectively, the range up to 309 ms and up to 19.8 s. The nrt\_emv bit controls the timer operation mode.

When this bit is set to 0 (default mode), the I\_nre interrupt is produced if the NRT expires before a start of a response is detected. The rx\_on bit is set low to disable the receiver. In the opposite case, when the start of a tag reply is detected before the timeout, the timer is stopped, and no IRQ is produced.

When this bit is set to 1, the timer unconditionally produces an IRQ when it expires. This means that the IRQ is independent from whether or not a tag reply was detected. When a tag reply is processed during a timeout, no other action is taken and the reply is normally received. In the opposite case, when no tag response is processed, the receiver is disabled.

The NRT can also be started using a start no-response timer direct command. The purpose of this command is to extend the no-response timer timeout beyond the range defined in the no-response timer control registers. If this command is sent while the timer is running, it is reset and restarted.

The NRT can be terminated using stop no-response timer or stop all activities direct command. The timer is terminated and no IRQ is sent. It is expected to be used in the nrt\_emv mode, when the incoming reception does not stop the no-response timer.

### 5.8.3

#### General-purpose timer (GPT)

The GPT value is defined by writing the [NRT and GPT configuration register 4](#) and the [NRT and GPT configuration register 5](#). It can be used to survey the duration of the reception process (triggered by the start of reception, after SOF) or to time out the PCD to PICC response time (triggered by the end of reception, after EOF). The trigger source can be configured through the gptc bit in the [NRT and GPT configuration register 1](#). The possible trigger configurations can be seen in [Table 57. General purpose timer trigger source](#).

The GP timer can also be started by sending the start general-purpose timer direct command. If this command is sent while the timer is running, it is reset and restarted.

### 5.8.4

#### Wake-up timer (WUT)

This timer is primarily used in the wake-up mode.

It can also be triggered by sending the start WUT direct command. When this command is sent, the RC oscillator, which is used as the clock source for the wake-up timer, is started. When the timer expires, an IRQ with the l\_wut flag is sent.

As the RC oscillator is the clock source for the WUT, it can run during PD mode. The other timers, which are based on the crystal oscillator, cannot be used in PD or WU mode.

Note: The tolerance of WUT is defined by the tolerance of the RC oscillator. During WU mode, a calibration mechanism can be enabled to compensate the RC inaccuracies, as detailed in [Section 5.9.5: Wake-up timer calibration](#).

### 5.9

#### Wake-up mode

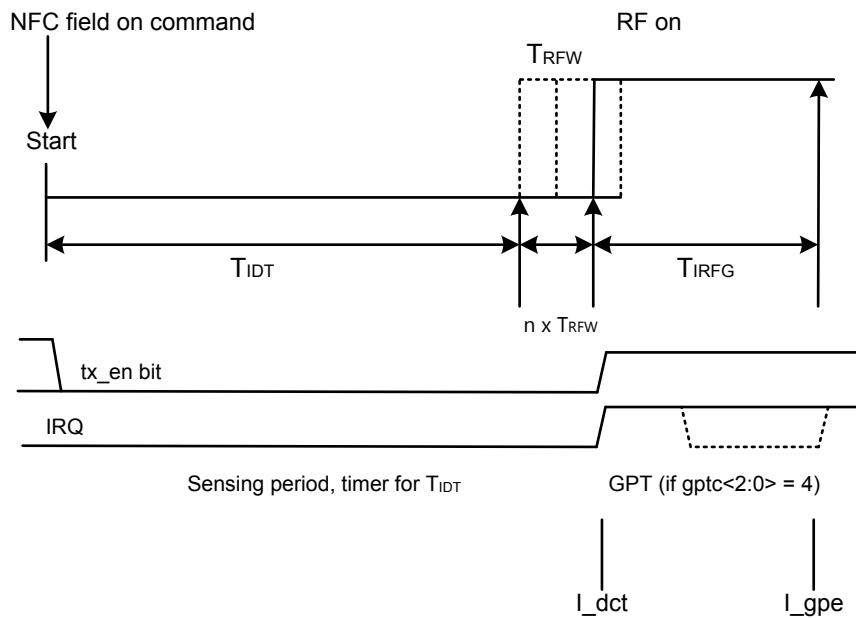

Once in PD mode, the wu\_en bit sets the ST25R210 into wake-up mode (WU), which is used to perform low-power card detection. An integrated low-power 26.48 kHz RC oscillator and configurable wake-up timer (WUT) are used to trigger periodic measurements.

Usually, the presence of a card is detected by the RF/NFC polling. In this process, the reader field is periodically turned on, and the host checks whether a card is present using RF commands. This procedure consumes considerable energy since the reader emits a field for long periods before a command can be issued due to guard time fulfillment.

Low-power detection of card presence is performed by detecting a change in the reader environment, produced by an approaching detuning element. When a change is detected, an interrupt is sent to the host. The host can then perform the regular RF/NFC polling afterward.

In wake-up mode, the ST25R210 performs periodic measurements and sends an IRQ to the host when a difference to the configured reference value is detected.

The device monitors the I and Q channels to assess a variation in the antenna surroundings.

The latest measurement value is shown in i\_adc and q\_adc, and the current reference is defined on i\_ref and q\_ref. ADC values are provided in 8-bit signed values using two's complement representation. The delta/difference to the reference that triggers a wake-up interrupt is defined in i\_diff and q\_diff.

Besides periodic execution via the wake-up timer, the measurement and processing of the measured data can be triggered by the trigger wake-up event direct command. This mechanism allows synchronization with external events.

### 5.9.1

#### Card detection

The presence of a card close to the reader antenna coil produces a change of the antenna LC tank signal. The reader field activation time required to perform the measurement is extremely short, compared to the activation time required to send a protocol activation command.

The power level during the measurement can be lower than that during normal operation as the card does not have to be powered to produce a coupling effect. The emitted power can be configured by changing the RFO driver resistance.

An IRQ is sent when the difference between a measured value and reference value is larger than the configured delta/diff value. There are two possibilities how to define the reference value, controlled by the bit iq\_aaref:

- The ST25R210 can automatically calculate the reference based on previous measurements (auto-averaging)

- The host determines the reference value and sets it on i\_ref and q\_ref

### 5.9.2 Automatic averaging

In case auto-averaging is enabled (iq\_aaref = 1) the reference value is recalculated after every measurement. The last measurement value, the old reference value, and the weight are used in this calculation.

The following formula is used to calculate the new reference value:

$$\text{new\_reference} = \text{old\_reference} - (\text{old\_reference} - \text{measured\_value}) / \text{weight}$$

The i\_iirqm and q\_iirqm bits define whether a measurement that causes an interrupt is taken into account for the average value calculation.

The influence that the new measurement has over the reference can be configured by a weight defined in i\_aaw and q\_aaw bits.

### 5.9.3 Calibration

The wake-up mode has an additional calibration step that can be executed manually or automatically. The skip\_cal and skip\_recal bits control the automatic calibration behavior.

When starting the wake-up mode, if skip\_cal = 0, a calibration step is performed automatically on the first WUT timeout.

While the wake-up mode is running and skip\_recal = 0, if reference  $\pm$  delta/diff is larger than 63, a recalibration is performed.

### 5.9.4 Wake-up IRQ

The device allows configuring the conditions when a wake-up IRQ is sent to the host.

This behavior is defined by i\_tdi\_en and q\_tdi\_en bits and the following three conditions can be used:

- I\_wui/q IRQ when the latest measurement is above the upper limit:  $i/q_{\text{adc}} > i/q_{\text{ref}} + i/q_{\text{diff}}$

- I\_wui/q IRQ when the latest measurement is in between the upper and lower limit:  $i/q_{\text{ref}} - i/q_{\text{diff}} \leq i/q_{\text{adc}} \leq i/q_{\text{ref}} + i/q_{\text{diff}}$

- I\_wui/q IRQ when the latest measurement is below the lower limit:  $i/q_{\text{adc}} < i/q_{\text{ref}} - i/q_{\text{diff}}$

If the bits i\_tdi\_en = 0, the I channel is not used during WU, and the same applies for the Q channel when q\_tdi\_en = 0.

During WU mode the ST25R210 produces additional IRQs that may be masked, or used for diagnostics:

- I\_wut IRQ when the WUT timer expires, indicating that the device temporarily enables itself in RD mode and performs a measurement

- I\_wutme IRQ when the device has concluded the WU measurement event, and goes back to WU mode

### 5.9.5 Wake-up timer calibration

The WUT uses the RC oscillator as its clock source. The RC oscillator is process and temperature dependent, which may result in a deviated WU period from the target defined by the wut bits. A wake-up timer duration of 100 ms  $\pm$  5ms can only be guaranteed with a wake-up timer calibration.

In applications where an accurate WU period is required, a calibration mechanism can be enabled to minimize the RC variations. It is not recommended to use the wake-up timer calibration on a wake-up timer period of less than 100 ms. When the WU mode is started, and WUT calibration is enabled by setting wut\_cal = 1, the wake-up timer is calibrated based on the crystal oscillator.

Therefore, the crystal oscillator is kept enabled for a certain calibration duration. The calibration is executed in wake-up mode whenever the wake-up timer expires and the chip transitions from PD to RD mode. A longer calibration duration results in increased accuracy of the WUT period.

The calibration duration of the WUT calibration step is defined by the wut\_cal\_len bits.

The below table shows the calibration time and the achieved target accuracy based on the selected wut\_cal\_len.

| Wut_cal_len <1:0> | Calibration duration (ms) | Target accuracy (%) |

|-------------------|---------------------------|---------------------|

| 0                 | 0.781                     | 3.33                |

| 1                 | 1.562                     | 1.67                |

| 2                 | 3.125                     | 0.83                |

| 3                 | 6.248                     | 0.43                |

As an example, using a wut\_cal\_len = 0 and a wake-up timer period of 100 ms, the expected timer period is between 96.7 ms and 103.33 ms. Since this calibration is performed every time the wake-up timer expires, temperature and other effects are neglected. The calibration is based on the crystal quartz oscillator and is therefore dependent on its frequency. An accurate and stable oscillator frequency is mandatory for the calibration. The bit rc\_vdig\_lp increases the accuracy of the wake-up timer calibration. Use it together with the wut\_cal\_len setting greater than or equal to two.

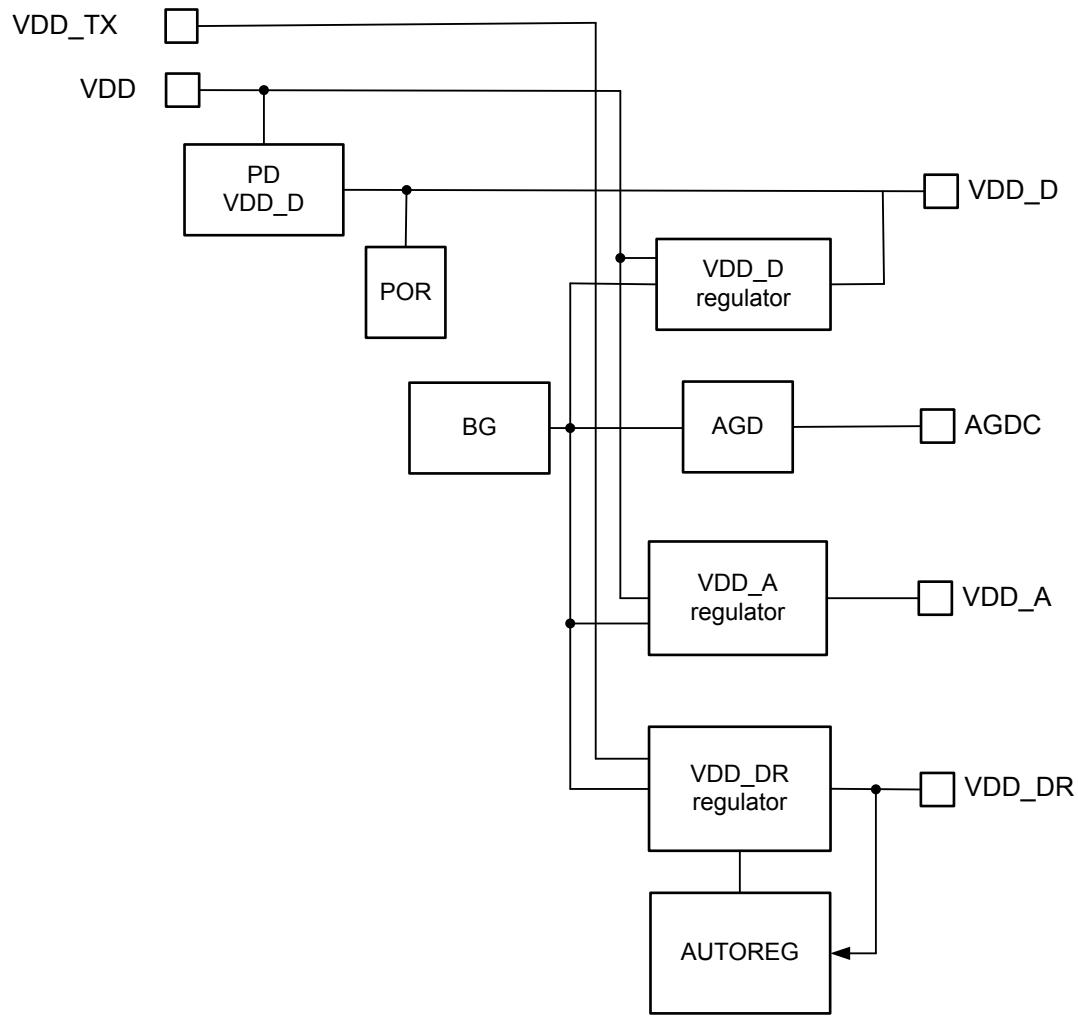

## 5.10 Power supply system

The ST25R210 features three positive supply pins, VDD, VDD\_TX and VDD\_IO:

- VDD is the main power supply pin. It supplies the ST25R210 blocks through two regulators (VDD\_A, VDD\_D)

- VDD\_TX is the transmitter supply pin. It supplies the transmitter via the VDD\_DR regulator. VDD / VDD\_TX range from 2.7 to 5.5 V is supported. VDD and VDD\_TX must be connected to the same power supply.

- VDD\_IO is used to define supply level for the digital communication pins (BSS, MISO, MOSI, SCLK, IRQ, MCU\_CLK). Digital communication pins interface to the ST25R210 logic through level shifters, therefore the internal supply voltage can be lower than VDD\_IO. VDD\_IO range from 1.65 to 5.5 V is supported.

The following figure details the building blocks of the ST25R210 power supply system.

**Figure 9. Power supply system**

*Note:*

- *BG: Bandgap reference*

- *AUTOREG: Automatic regulator adjustment*

The power supply system contains three regulators, a power-down support block (POR), a block generating the analog reference voltage (AGD) and a block performing the automatic power supply adjustment procedure. The three regulators provide supply to the analog (VDD\_A), logic (VDD\_D), and the transmitter (VDD\_DR) blocks. VDD\_D, VDD\_DR, and VDD\_A pins are not intended for supplying power to the chip. The VDD\_A, VDD\_D, and VDD\_DR regulators must be used for supplying power to the chip.

A decoupling capacitor pair of 10 nF in parallel with 2.2  $\mu$ F must be connected to the  $V_{DD}$  and  $V_{DD\_TX}$  supply, shown in Figure 1.

The decoupling capacitors should be placed close to the VDD\_TX pin. The PCB trace between the VDD\_TX pin and the decoupling capacitor should not be longer than 3 mm, with no vias in between. The trace width should be wider than 0.25 mm. Another decoupling capacitor pair is recommended to be placed at the VDD pin.

## 5.10.1

## Power-down block

In the power-down mode, the regulators are disabled to save power. In this mode, a low-power power-down support block maintains the VDD\_D voltage level.

## 5.10.2 VDD\_A regulator

The VDD\_A regulator supplies the analog part of the receiver and the crystal oscillator. Its nominal voltage is 3.0 V. Below 3.0 V output voltage, the VDD\_A regulator follows the VDD\_DR voltage setting. A decoupling capacitor pair of 10 nF in parallel with 2.2  $\mu$ F must be connected and placed close to the IC with good connectivity to the positive and negative supply pins of VDD\_A. The 10nF decoupling capacitor should be placed as close as possible to the positive and negative supply pins.

## 5.10.3 VDD\_D regulator

The VDD\_D regulator supplies the digital logic. Its nominal voltage is 1.15 V. A decoupling capacitor pair of 10 nF in parallel with 2.2  $\mu$ F must be connected and placed close to the IC with good connectivity to the positive and negative supply pins of VDD\_D. The 10nF decoupling capacitor should be placed as close as possible to the positive and negative supply pins.

## 5.10.4 VDD\_DR regulator

The VDD\_DR regulator is supplying the TX driver via the VDD\_TX pin. The decoupling capacitor connected to the VDD\_DR pin should be 47 nF. The decoupling capacitor should be placed as close as possible to the positive and negative supply pins. To avoid oscillations on the output this decoupling capacitor should be directly connected with the shortest possible traces to the VDD\_DR and GND\_DR pin. Its LDO dropout voltage can be configured between 200 mV and 550 mV using the regd bits in the [Tx driver configuration register](#). The LDO drop is based on the IC internal measurement thus the VDD\_DR voltage measured outside of the IC, at its pins, can vary.

The regulator can also be configured to an absolute voltage. The reg\_s bit in the VDD\_DR regulator configuration register switches between the automatic adjustment based on the configured LDO drop (reg\_s = 0) and the manual one defined by an absolute voltage. The absolute voltage can be configured by setting reg\_s bit set to one and configuring rege bits according to [Table 14. Regulated voltages](#).

The regulator features an internal current limiter. The limiter threshold is set above the 500mA current limit. Its threshold is dependent on internal mechanisms to achieve the maximum output current without damaging the ST25R210. When the current limiter is operating, the i\_lim bit in the [Analog display register 1](#) is set. Although the limiter is active, the ST25R210 can still operate normally for a short period of time. As a result of the limiter being active, the VDD\_DR voltage is being reduced. Nevertheless, the device should be designed not to exceed the limits specified in the absolute maximum ratings section.

Besides the definition of a static voltage in unmodulated state, the VDD\_DR regulator is used to generate AM modulation and shaping of the OOK modulation in modulated state.

Further details about the shaping of the modulation signal can be found in [Section 5.11: Active wave shaping](#).

## 5.11

## Active wave shaping

The ST25R210 supports active wave shaping of the modulation signal. The supported modes of operations are

- Field on and off transitions

- OOK modulation

- AM modulation

During the OOK modulation, the driver is stopped during the modulated state (also called pause). When in AM modulation operation, the driver switches between two voltage levels.

The device supports two AM modulation methods which can be combined with each other:

- Resistance am modulation (res\_am)

- Regulator shaped modulation (rgs\_am)

Both can be enabled in the [Tx modulation register 1](#). When using the regulator shape modulation, the VDD\_DR voltage level changes between the modulated and the unmodulated voltage level (modulation state change). The unmodulated voltage level is defined by the am\_mod bits. The transition between the modulated and the unmodulated voltage level follows an exponential filter curve. The time constant of this filter curve can be modified for the falling and rising edge of the modulation signal individually. The filter can be modified in the [AWS configuration register 2](#) by setting the am\_fall and am\_rise bits. The value of the filter should be in conjunction with the Q-factor of the reader antenna. A too high value can cause non-standard compliant wave shape timings. For example ISO/IEC 14443-2 t3 and t4 could be too slow. A too low value could cause over- or undershoots. The filter curve defined by am\_fall and am\_rise bits is generated by an RC network inside of the ST25R210. By enabling the dig\_aws\_en bit, the same signal is generated by a digital logic, reducing the device to device variation.

The resistive am modulation (res\_am) allows switching between the unmodulated driver resistance (d\_res) and the modulated driver resistance (md\_res). The switch between d\_res to md\_res is occurring at the modulation state change after a certain number of carrier clock cycles defined in the tdres1 (falling edge) and tdres2 (rising edge) bits. The tdres1 bits can be configured in the [AWS timing register 1](#), the tdres2 bits can be configured in the [AWS timing register 3](#).

When res\_am is used in combination with OOK modulation (tr\_am=0), then the driver is being stopped after a certain number of carrier cycles defined in tentx1 bits. The tentx1 bits can be configured in the [AWS timing register 1](#). The usage of tentx1 different from 0 can be beneficial when enabling also rgs\_am in the OOK modulation scheme.

The ST25R210 also features two voltage sinking mechanisms.

- Dynamic passive sink

- Active sink

The voltage sink is used to reduce the energy stored in the VDD\_DR decoupling capacitor while transitioning from the modulated state to the unmodulated state. The sinks can only be enabled when the regulator is used for shaping (rgs\_am = 1).

The dynamic passive sink is enabled during the modulated state. It is drawing an additional continuous current during the modulation. This sink can be activated in combination with very high ohmic matchings to reduce the energy stored in the VDD\_DR capacitor. It can be delayed by a certain number of carrier cycles by setting the tpasssinkx1 (falling edge modulation signal) and tpasssinkx2 (rising edge of the modulation signal) bits. The tpasssinkx1 bits can be configured in the [AWS timing register 2](#) and the tpasssinkx2 bits can be configured in the [AWS timing register 4](#).

The active sink can be enabled by setting the act\_sink\_en bit to 1 in the [AWS configuration register 1](#). In addition, the offset measurement must be enabled by setting the sink\_offset\_en and dyn\_sink\_offset bits in the [AWS configuration register 1](#) to 1. This configuration enables the active sink during the modulation pulse. It is only drawing additional current out of the VDD\_DR capacitor, if the VDD\_DR voltage is above the offset. The offset is following the reference signal defined by am\_fall and am\_rise. Using the bits tsinkoff1 in [AWS timing register 2](#) and tsinkoff2 in the [AWS timing register 4](#) can delay the operation of the active sink after the modulation state change. It is recommended to keep tsinkoff1 and tsinkoff2 at a value of 0 for accurate shaping of the modulation pulse during the complete modulation pulse.

The internal current limiter can be temporarily disabled during the modulation by setting the bit dyn\_ilim\_aws = 1. Due to the active and passive sink, the current consumption could increase during the modulation of the carrier. It is recommended to activate the internal short circuit protection by setting the sc\_prot\_en bit to 1. Both bits can be found in the [AWS configuration register 1](#).

Additional overshoots or undershoots can be reduced by configuring the over- and undershoot protection. The bit pattern can be defined using the bits ov\_pattern defined in the [Overshoot protection register](#) and un\_pattern defined in the undershoot protection register. To enable the over- and undershoot protection both bits, ov\_pattern and un\_pattern must be different from 0 and res\_am = 1. The driver then switches from d\_res to md\_res during the configured carrier cycles after the modulation state change.

## 5.12

### Reader operation

The ready mode must be entered by setting the en bit in the [Operation register](#). In this mode the oscillator is started and the regulators are enabled. When the oscillator operation is stable, the l\_osc interrupt is sent, and the osc\_ok bit indicates it.

The operation mode and data rate must then be configured by writing to the [Tx protocol register 1](#) and the [Tx protocol register 2](#). The receiver and transmitter operation options related to operation mode must be defined too. If the selected operation mode uses AM modulation for the reader-to-tag communication, the modulation depth must be configured.

Before sending any command to a card, the VDD\_DR regulator must be enabled by setting the vdddr\_en bit and waiting 10  $\mu$ s. Then, the transmitter and the receiver must be enabled by setting the rx\_en and tx\_en bits. A guard time for each technology is defined by the NFC standards (for example 5 ms for ISO/IEC 14443) requiring that the reader field must be turned on for some time before the first command is sent. A general-purpose timer can be used to count this time or NFC field on command with a defined time by the NFC field on guard timer register.

Preparation and execution of a transceiver sequence:

- Execute the stop all activities direct command

- Execute the [Clear Rx gain](#) direct command

- Configure the timers accordingly

- Define the number of transmitted bytes in the [Tx frame configuration register 1](#) and [Tx frame configuration register 2](#)

- Write the bytes to be transmitted in the FIFO

- Send the transmit data or the transmit next slot (NFC-V) direct command

When all the data is transmitted, the [I\\_txe](#) interrupt is generated to inform the microcontroller that the transmission is finished (IRQ due to the end of transmission)

After the transmission is executed, the ST25R210 receiver automatically starts to observe the RFI inputs to detect a card response. The RSSI monitoring and AGC (if enabled) are started. The framing block processes the subcarrier signal from the receiver and fills the FIFO with data. When the reception is finished, and all the data is in the FIFO, the [I\\_rxe](#) interrupt is sent to the microcontroller (IRQ due to end of receive), and the [FIFO status register 1](#) and [FIFO status register 2](#) display the number of bytes in the FIFO so the microcontroller can proceed with the data download.

If an error or a collision bit are detected during reception, the [I\\_rxe](#) interrupt with the appropriate flag is sent, and the microcontroller can take appropriate action.

When the data packet is longer than the FIFO size, the above mentioned procedure changes.

The FIFO is prepared with the data before the transmission starts. The [I\\_wl](#) interrupt is sent during the transmission to signal when the remaining number of bytes is lower than the water level (IRQ due to FIFO water level). The microcontroller then adds more data in the FIFO. When all the data are transmitted the [I\\_txe](#) interrupt is sent to inform the microcontroller that the transmission is finished.

The situation during the reception is similar. When the FIFO is loaded with more data than the received water level, the [I\\_wl](#) interrupt is sent, and the microcontroller reads the data from the FIFO. When the reception is finished, the [I\\_txe](#) interrupt is sent to the microcontroller (IRQ due to end of receive) the [FIFO status register 1](#) and [FIFO status register 2](#) display the number of the bytes in the FIFO still to be read.

## 5.13

### Card emulation operation

The ST25R210 CE operation is activated by setting the [ce\\_en](#) bit in the [Operation register](#). There are various target or listening modes implemented depending on the setting of the [om](#) bits, refer to [Table 41. Operation modes](#).

The device supports:

- PICC type A according to ISO/IEC 14443.

- NFCIP-1 passive target in bitrates  $f_C/128$ ,  $f_C/64$ , and  $f_C/32$

- NFC Forum listen mode NFC-A and NFC-F

Active target and active communication mode are not supported.

There are various options available, including bitrate detection, automatic responses, and power savings, which are described below.

#### 5.13.1

##### Low-power field detection

The external field detector is enabled by setting [ce\\_en](#) = 1. The power consumption of the application can be optimized by starting the card emulation from the PD mode ([en](#) = 0) while waiting for an external field from a peer/reader.

Upon detection of an external field ([I\\_eon](#)), the ST25R210 temporarily enables the oscillator and the receiver. The host can confirm it by setting the [en](#) and [rx\\_en](#) option bits in [Table 38. Protocol register 1](#). From this point on, either bit rate detection or fixed CE communication can be performed.

This temporary enable of the oscillator can be observed with the [tmp\\_on](#) bit in [Table 91. Static status register 1](#). Oscillator gets disabled on field off ([I\\_eof](#)) and [tmp\\_on](#) goes to 0.

The external field detector (EFD) is automatically enabled when in CE mode ([ce\\_en](#) = 1) and during the execution of the NFC field on command. The status of the EFD can be observed through the bit [efd\\_on](#), and when the EFD is active ([efd\\_on](#) = 1), its output can be monitored by the bit [efd\\_out](#). EFD activation ([efd\\_at<3:0>](#)) and deactivation ([efd\\_dt<3:0>](#)) thresholds can be configured individually in the external field detector register.

#### 5.13.2

##### Fixed card emulation

Fixed communication mode is active when one of the target modes with [om](#) = 1 or [om](#)=3 is selected. ST25R210 only receives and answers in the selected technology.

### 5.13.3 Bit rate detection

The card emulation can also be started from the bit rate detection mode. There are three different modes selectable by om in protocol register 1.

In these modes, the ST25R210 accepts frames in different technologies for at least the first frame.

Once the reception of the first frame starts, the bit rate detection mode signals an l\_nfct interrupt, indicating that the bit rate has been identified and the host can retrieve the related information by reading nfc\_rate on card emulation status register 1.

When the first frame has been fully received, the host can exit the bit rate detection mode by setting the corresponding mode on om bits in the protocol definition register to the corresponding fixed listen communication mode.

The difference between the om = 0xD, 0xE, and 0xF is the conditions when it gets rearmed:

- All modes re-arm bit rate detection on setting om to 0x0 and back to a bit rate mode.

- Single bit rate detection (0xE) rearms additionally on field reset.

- Normal bit rate detection (0xF) rearms additionally on field reset and when bit ce\_state moves to the IDLE state.

### 5.13.4 CE communication

Communication can be performed by the host (through FIFO) or by using automatic responses as detailed in the [CE configuration register 1](#).

These automatic responses can include for NFC-A, the complete collision resolution including SEL\_RES and SAK.

For NFC-F, only the SENSF\_REQ is handled by sending SENSF\_RES.

To enable slow hosts to perform emulation of T4T, handling of higher commands such as RATS, SLP\_REQ, and S(DESELECT) can be enabled (not fully standard compliant, CID = 15 handling).

When receiving automatically handled frames, the ST25R210 signals this by sending l\_rxe\_cea instead of normal l\_rxe interrupts.

While in card emulation, the state machine moves through a limited set of states corresponding to NFC Forum activity. These states can be observed in the [Card emulation status register 1](#).

The ce\_state in the same register can also be written by the host to move the state machine to for example SLEEP\_A mode after the reception of a directly received SLP\_REQ.

The content of the automatic responses is defined by the content of CE memory.

### 5.13.5 CE memory

The CE memory is used to store data for NFC-A (0x58) and NFC-F (0x5A) automatic card responses.

**Table 4. CE memory address space**

| Location | Description | Data usage                                                                            | Comment |

|----------|-------------|---------------------------------------------------------------------------------------|---------|

| 0-6      | NFCID1(4/7) | 4 bytes: locations 0-3<br>7 bytes: locations 0-6                                      | NFC-A   |

| 7,8      | SENS_RES2:1 | SENS_RES (ATQA)                                                                       |         |

| 9        | SEL_RES CL1 | Response to SEL_REQ(SAK) CL1                                                          |         |

| 10       | SEL_RES CL2 | Response to SEL_REQ(SAK) CL2                                                          |         |

| 11-30    | ATS         | Response to RATS, first byte is length (TL)                                           |         |

| 31,32    | NFC_SC      | Additional System code (SC) besides FFFFh in SENSF_REQ to which the device answers    | NFC-F   |

| 33-51    | SENSF_RES   | Response to SENSF_REQ, last two bytes may not be transmitted based on RC in SENSF_REQ |         |

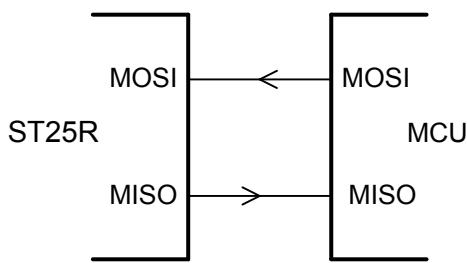

## 5.14 Host interface

### 5.14.1 Communication with an external microcontroller

The device communicates with a microcontroller via an SPI interface where it acts as a target device, relying on the microcontroller to initiate all communication.

To notify the microcontroller of completed commands or external events the device signals an interrupt on the IRQ pin.

A RESET pin is available to reset the device logic and put the device registers to default state.

### 5.14.2 Interrupt interface

There are three interrupt registers implemented in the device. When an interrupt condition is met, the source of the interrupt bit is set and the IRQ pin transitions to high.

The microcontroller can read the interrupt registers to distinguish between different interrupt sources. After a particular interrupt register is read, its content is reset to 0.

*Note: There can be more than one interrupt bit set if the microcontroller does not immediately read the interrupt registers after the IRQ signal is set and another event causing an interrupt occurs. In this case, the IRQ pin transitions to low after the last bit causing the interrupt is read.*

If an interrupt from a certain source is not required, it can be disabled by setting the corresponding bit in the mask interrupt registers. In the case of masking a certain interrupt source the IRQ line is not set high, but the interrupt status bit is still set in the IRQ status registers.

By reading the IRQ status registers the masked interrupt bits are also retrieved and cleared.

In case an interrupt is masked and set to high due to a previous IRQ event and then the host unmasks this IRQ source, the IRQ line is immediately set to high. This notifies the host system that there are some interrupt events not yet read out.

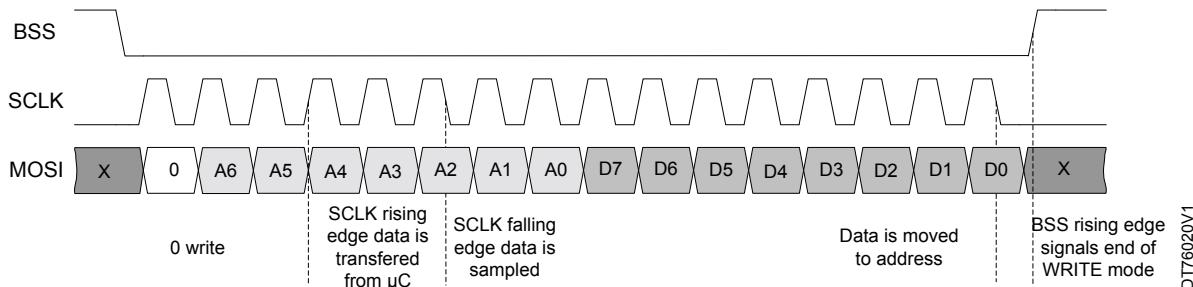

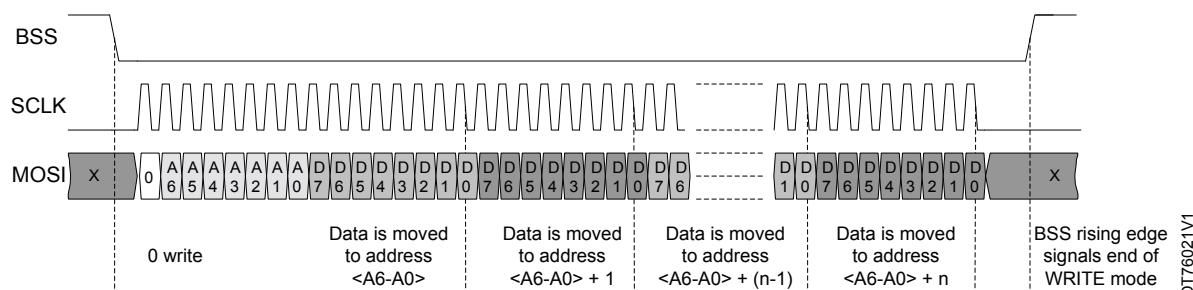

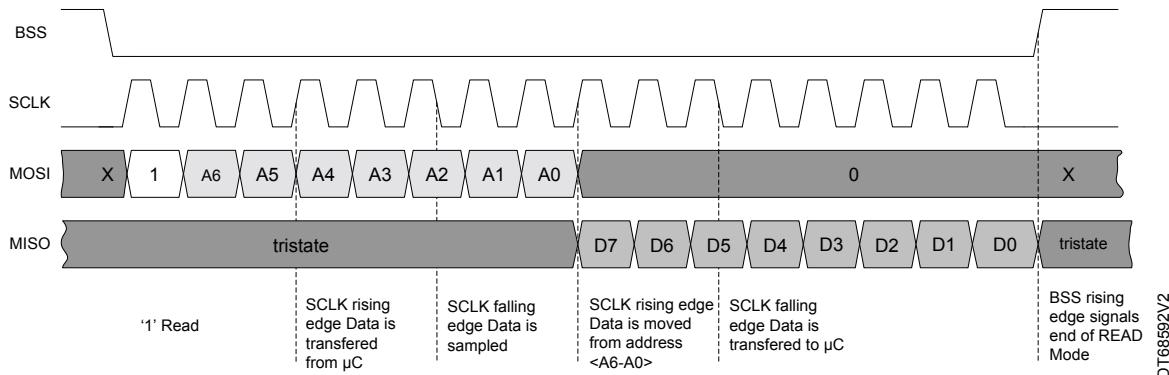

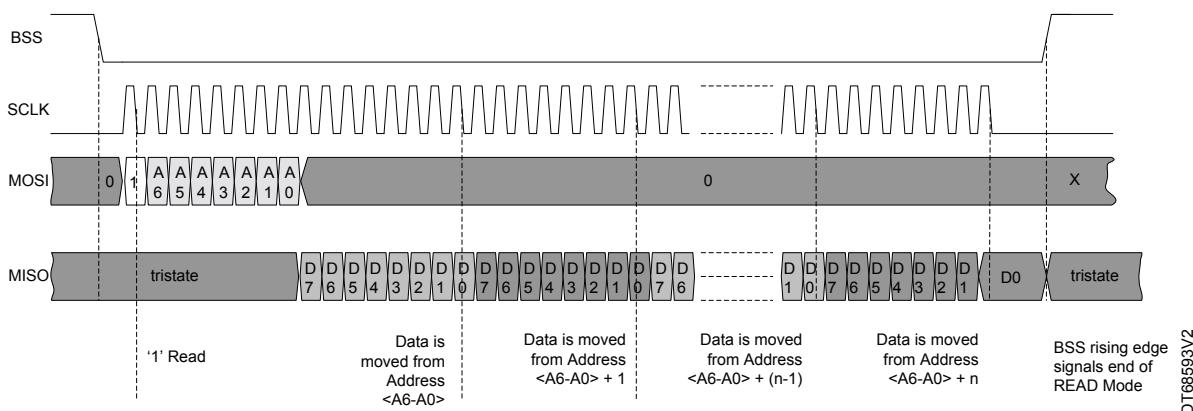

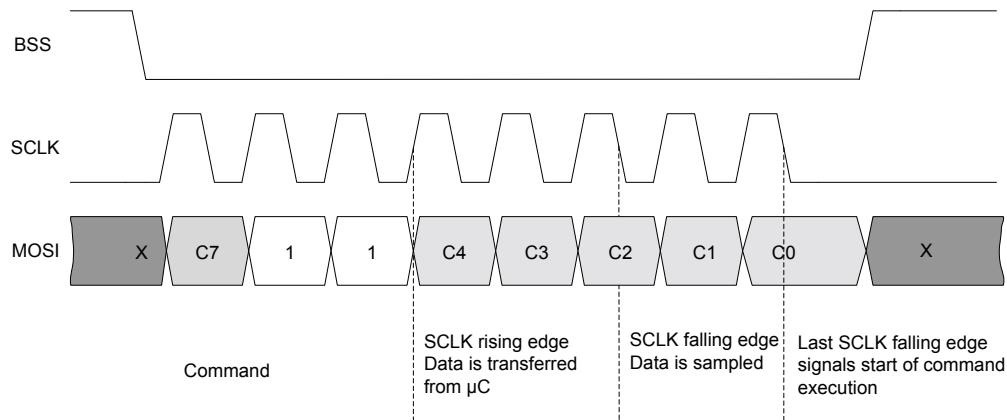

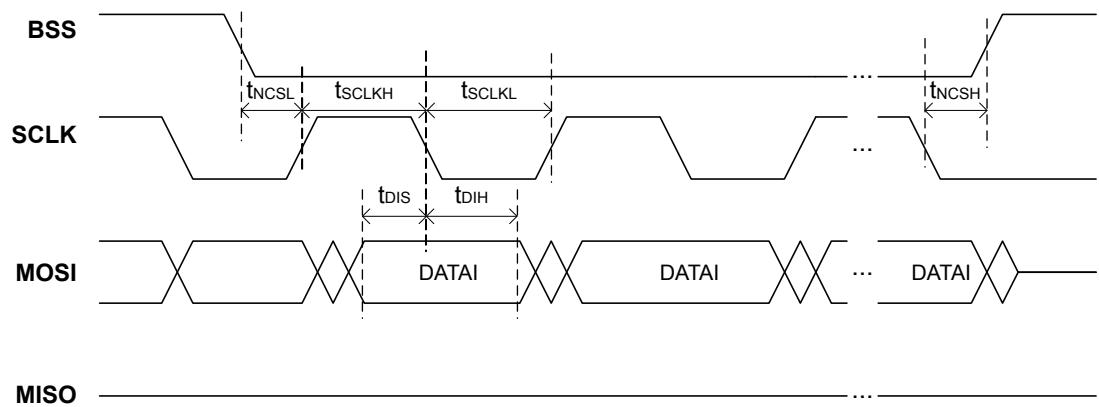

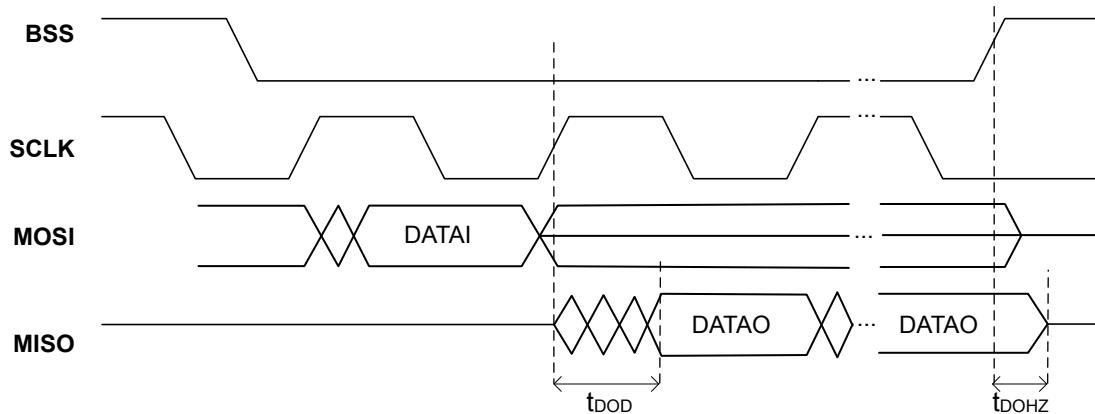

5.14.2.1 **Serial peripheral interface (SPI)**

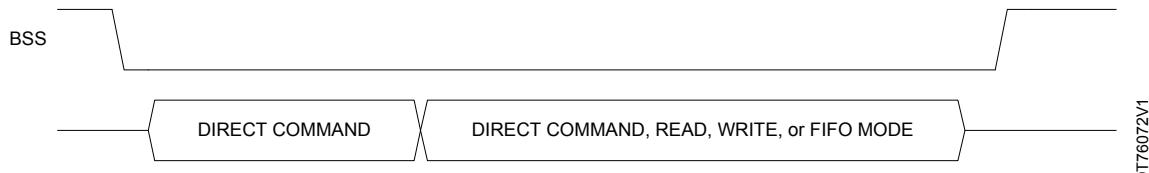

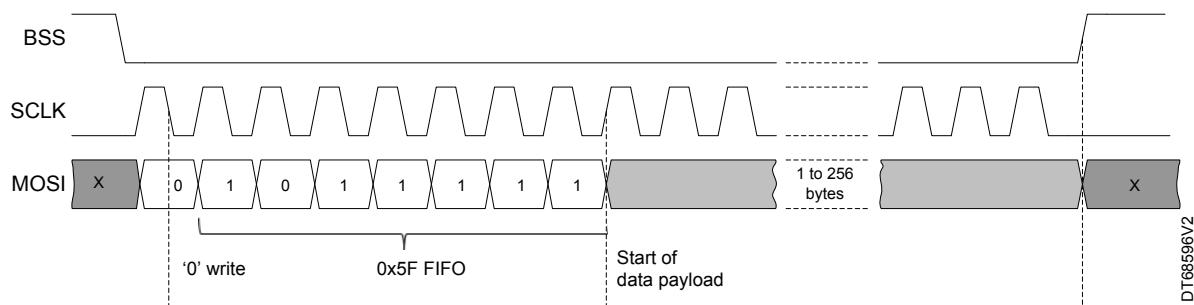

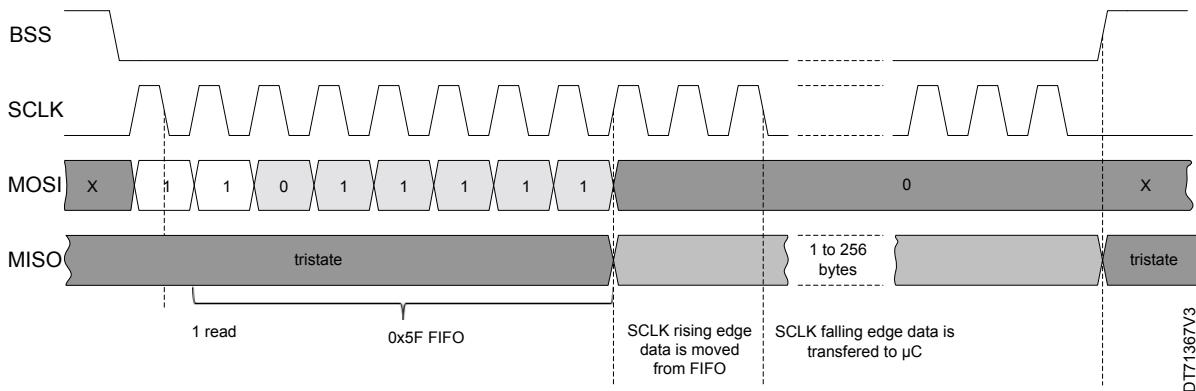

The device has a standard SPI with clock polarity of 0, a clock phase of 1, and an active low target select signal. SPI speeds up to 10 Mbit/s are supported. The communication starts with the controller pulling BSS low. The MOSI pin is sampled on the falling edge of SCLK, and the state of the MISO pin is updated on the rising edge of the SCLK signal. Data is transferred byte-wise, the most significant bit first. Read and write commands support an address auto increment to reduce communication time.

**Table 5. SPI signal lines**

| Name | Signal                       | Signal Level | Description                    |

|------|------------------------------|--------------|--------------------------------|

| BSS  | Digital input                | CMOS         | SPI enable (active low)        |

| MOSI | Digital input                | CMOS         | Serial data input              |

| SCLK | Digital input                | CMOS         | Clock for serial communication |

| MISO | Digital output with tristate | CMOS         | Serial data output             |

MISO output is mostly in a tristate condition and is only driven when output data is available.

While the MISO output is in a tristate condition, it is possible to switch on a 10 k $\Omega$  internal pull-down resistor by activating the option bits miso\_pd1 and miso\_pd2 in the [General configuration register](#).

**Figure 10. SPI data signals with a host**

DT76019V1

The following addressing scheme is used:

- Bit 7 indicates the direction of the operation (0-Write /1-Read)

- 88 addressable registers (0x00 - 0x57)

- 32 command codes (0x60 - 0xF9)

- FIFO access (0x5F)

- Test register access (0xFC)

- CE memory access (0x58)

**Table 6. SPI operation modes**

| Mode            | Mode pattern (com. bits) |    |    |    |    |    |    |    | Related data                                                             |

|-----------------|--------------------------|----|----|----|----|----|----|----|--------------------------------------------------------------------------|

|                 | R/W                      | B6 | B5 | B4 | B3 | B2 | B1 | B0 |                                                                          |

| Register write  | 0                        | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Data byte (or more bytes in case of auto-incrementing) A<6:0> = 0x57 max |

| Register read   | 1                        | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Data byte (or more bytes in case of auto-incrementing) A<6:0> = 0x57 max |

| Commands        | C7                       | 1  | 1  | C4 | C3 | C2 | C1 | C0 | -                                                                        |

| Test            | 1                        | 1  | 1  | 1  | 1  | 1  | 0  | 0  | Address and data byte (or more bytes in case of auto incrementing)       |

| CE memory write | 0                        | 1  | 0  | 1  | 1  | 0  | 0  | 0  | Write CE memory                                                          |

| CE memory read  | 1                        | 1  | 0  | 1  | 1  | 0  | 0  | 0  | Read CE memory                                                           |

| Mode       | Mode pattern (com. bits) |    |    |    |    |    |    |    | Related data                   |

|------------|--------------------------|----|----|----|----|----|----|----|--------------------------------|

|            | R/W                      | B6 | B5 | B4 | B3 | B2 | B1 | B0 |                                |