# Automotive power management IC for highly integrated processors

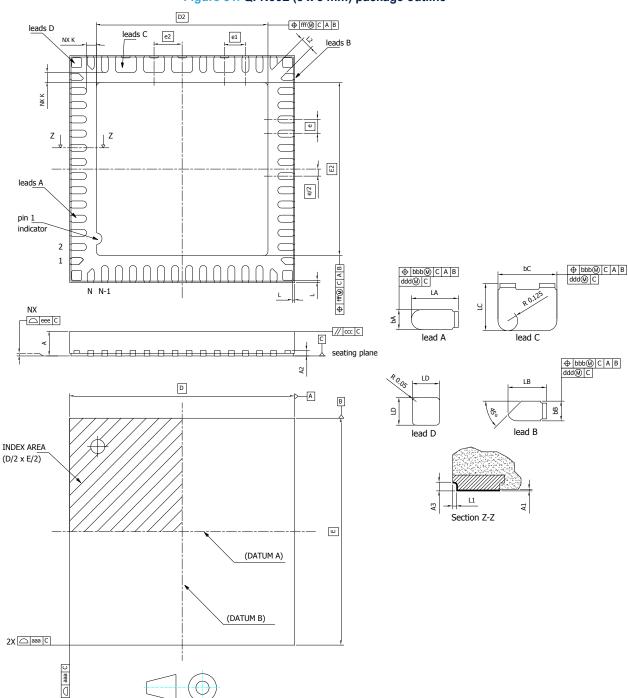

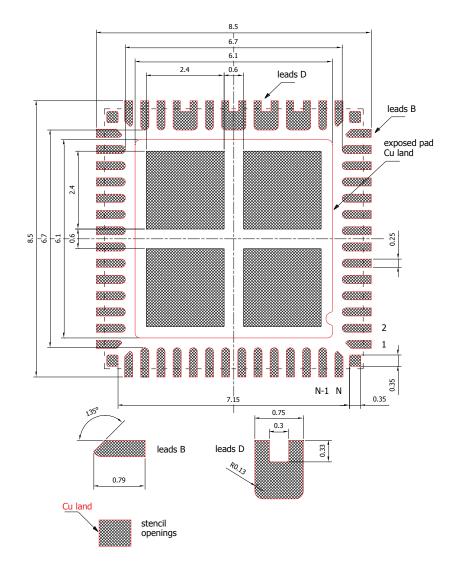

VFQFN56 + 4L 8x8x0.9 mm

## **Maturity status link**

SPSB100G

# Device summary SPSB100GTR SPSB100GBTR

#### **Features**

- AEC-Q100 grade 1 qualified

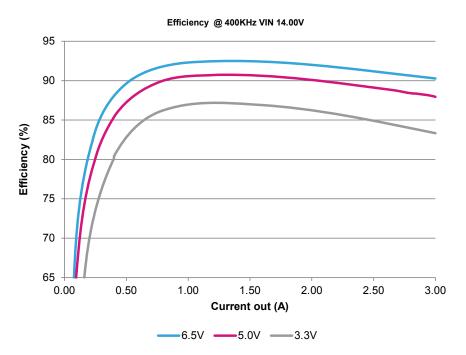

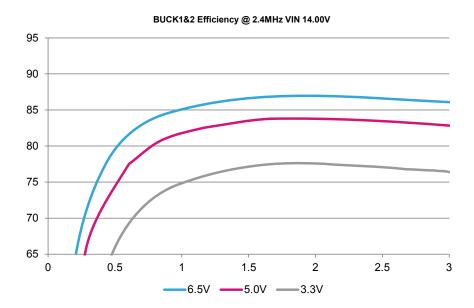

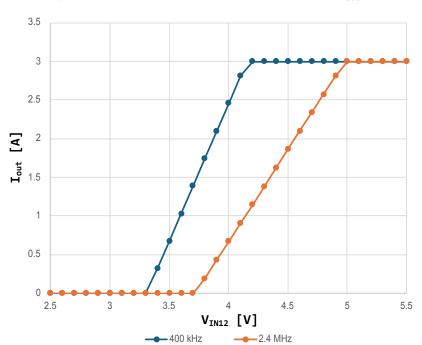

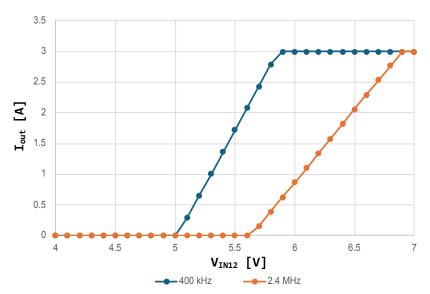

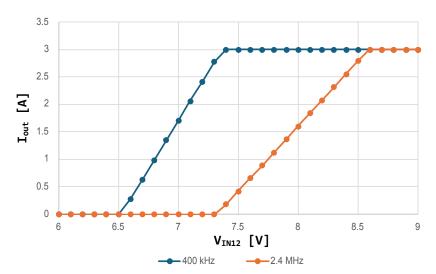

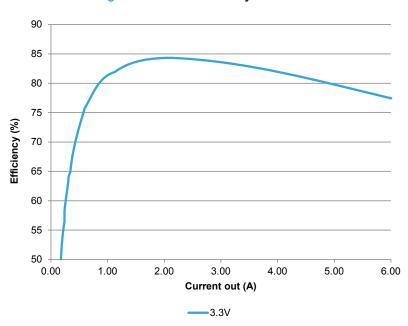

- Two configurable (6.5 V, 5 V, 3.3 V) buck converters and typ peak switching current limit of 3.0 A @ 2.4 MHz or 400 kHz

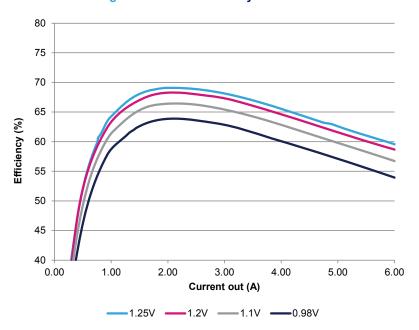

- One configurable (3.3 V, 1.25 V, 1.2 V, 1.1 V, 0.98 V) buck converter and typ peak switching current limit up to 6.0 A @ 2.4 MHz, with fine-tuning configurability around 0.98 V (0.95 V to 1.01 V)

- Overcurrent detection and limitation for all bucks

- Integrated soft-start on buck stages

- Boost controller 6 9 V with a max current capability of 3.5 A @ 400 kHz, for sustaining permanently low battery conditions and deep cranking pulses with boost modes

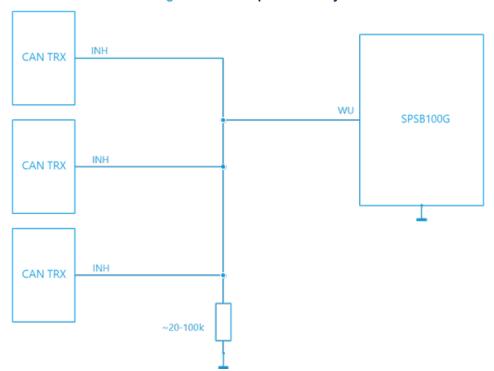

- One 5 V voltage regulator (120 mA) for CAN-FD supply

- One configurable (5 V or 3.3 V) low drop voltage tracker of buck regulator (10 mA)

- One high-side driver for contact monitoring ( $R_{ON}$  = 55  $\Omega$ ) with open-load and overcurrent diagnosis

- Dedicated interrupt pin for failure communication

- Device can operate in low-power mode

- Very low quiescent current in deep sleep state

- MCU reset generator

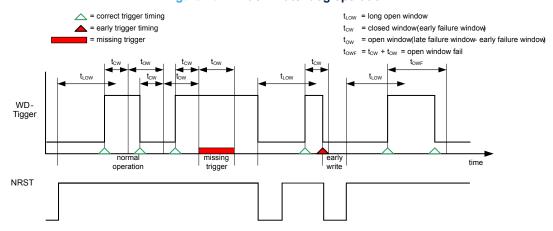

- Configurable window watchdog with an extended long open window up to 9 s, with maskable function and enable/disable function through NVM bits

- 1 CAN-FD transceiver (ISO 11898-2/2016 compliant), which can be deactivated via SPI, with local failure and bus failure diagnosis

- Device contains temperature warning and protection

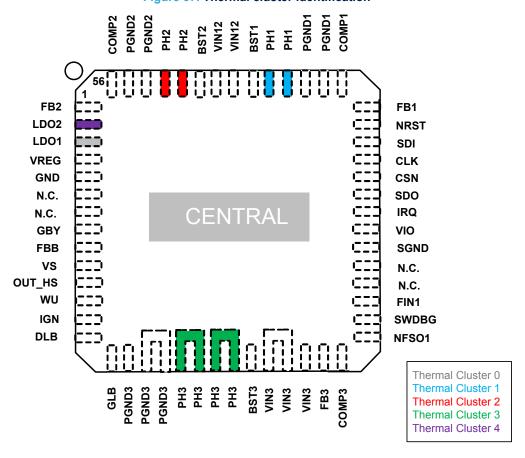

- Thermal clusters

- A/D conversion of supply voltages and internal temperature sensors

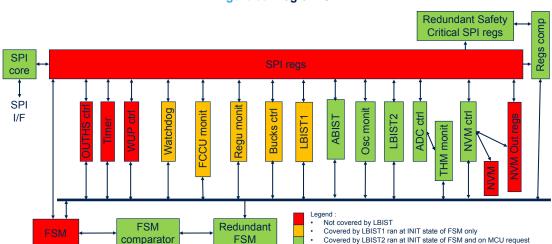

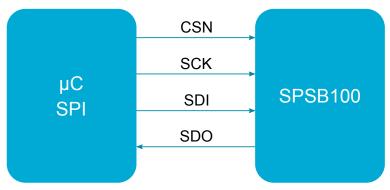

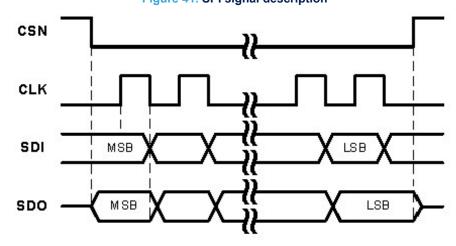

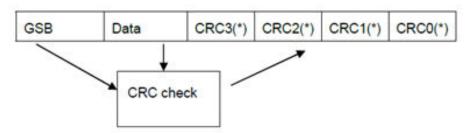

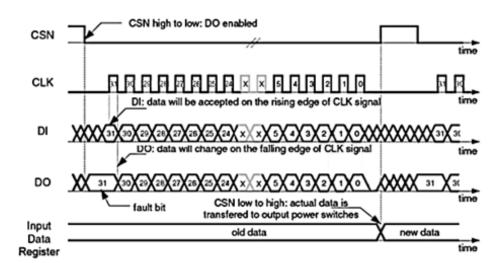

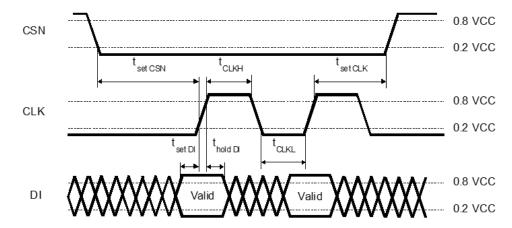

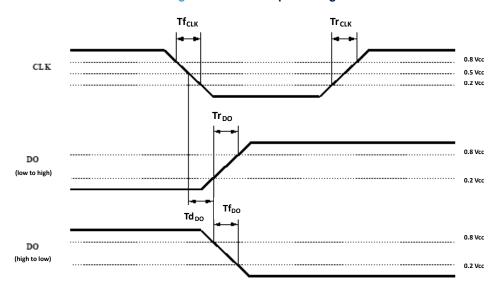

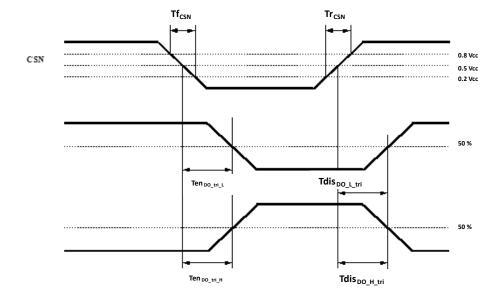

- STMicroelectronics standard serial peripheral interface (32-bit / ST\_SPI) including 4-bit CRC

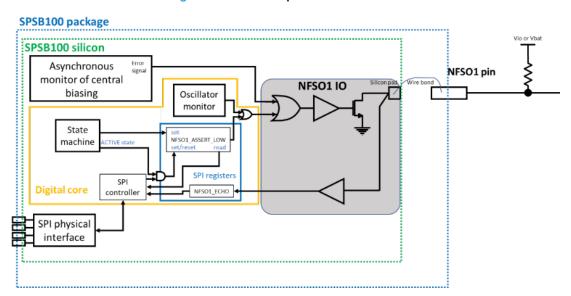

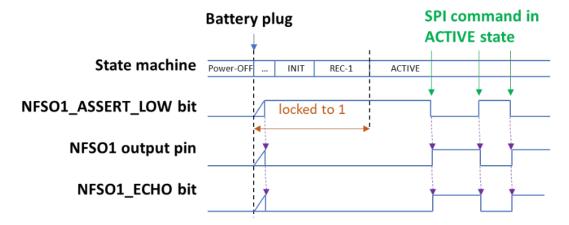

- · One fail-safe output

- · One input pin supporting static and dynamic error signal reporting

- Programmable periodic system wake-up feature

- Programmable periodic system wake-up feature extended up to 180 days (Very Long Duration Timer)

- Documentation available for customers that need support when dealing with ASIL requirements as per ISO26262

# **Description**

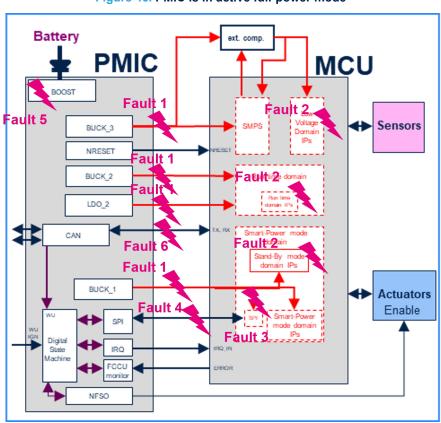

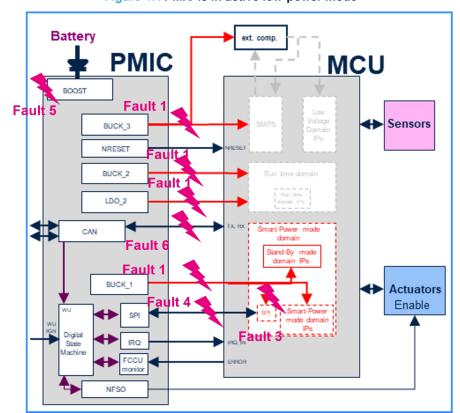

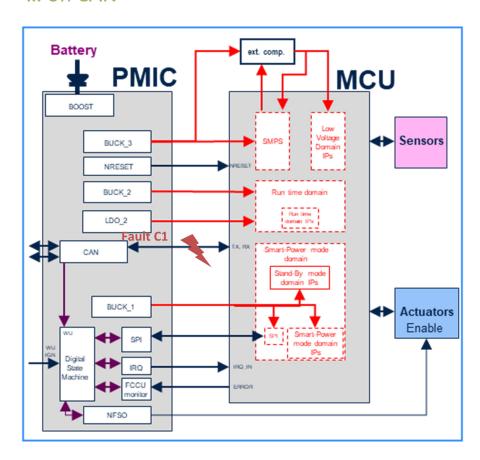

The SPSB100G is a fully integrated automotive power management system IC, specifically designed for highly integrated application processors (e.g. Stellar G and P MCU families), offering low-power mode and high-current capability. The device comes with enhanced system power supply functionality and a CAN-FD physical communication layer (available only on the SPSB100G version).

It combines three switch-mode power supplies together with two integrated linear voltage regulators. The device further integrates two wake-up inputs and advanced fail-safe functionalities. The device also embeds a Long Duration Timer up to 180 days.

The boost controller is intended to sustain cold cranking pulses, start-stop, and weak battery conditions.

Different combinations make it possible to supply the system microcontroller, the integrated CAN-FD transceiver (only for the SPSB100G version), and external peripheral loads and sensors in several adjustable voltage and current ranges. The SPSB100G and the SPSB100GB are delivered out of STMicroelectronics factory with default values (rails, power-up and -down sequences) stored in the USER-NVM space as reported in System Supply Configuration 1, but can be also re-programmed by customers based on different application needs.

The STMicroelectronics standard SPI interface allows for control and diagnosis of the device and enables generic software development.

The device offers a set of features to support applications that need to fulfill functional safety requirements as defined by Automotive Safety Integrity Level (ASIL).

DS14964 - Rev 1 page 2/239

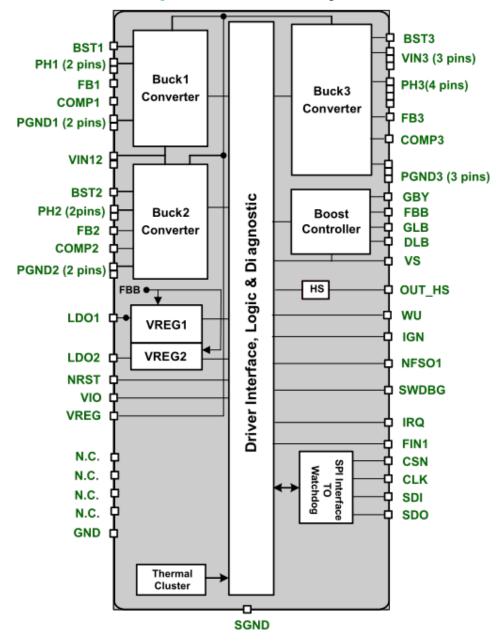

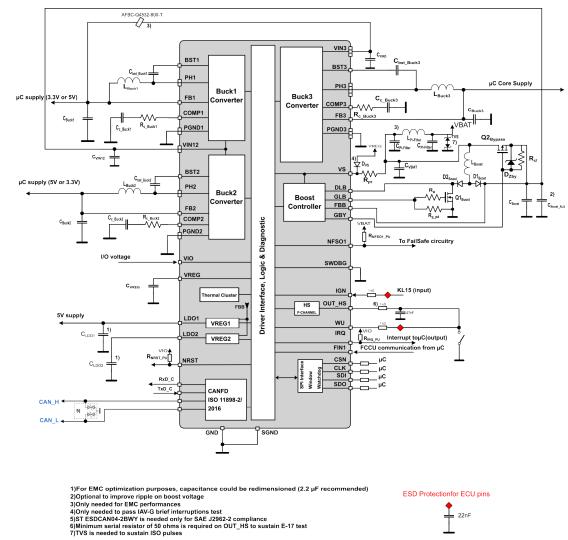

# 1 Block diagrams

BST3 BST1 VIN3 (3 pins) PH1 (2 pins) Buck1 PH3( FB3 FB1 PH3(4 pins) Buck3 Converter COMP1 Converter PGND1 (2 pins) COMP3 VIN12 PGND3 (3 pins) BST2 GBY Driver Interface, Logic & Di agnostic PH2 (2pins) **FBB** Buck2 Boost GLB Controller Converter DLB COMP2 VS PGND2 (2 pins) HS OUT\_HS WU VREG1 LD01 🗘 (CAN Sup.) IGN VREG2 LDO2 NFSO1 NRST **SWDBG** VIO VREG IRQ FIN1 RxD\_C SPI Interface TO CAN FD CSN TxD\_C ISO 11898-2 CLK CAN\_H /2016 SDI CAN\_L SDO CANGND Thermal Cluster SGND

Figure 1. SPSB100G block diagram

DS14964 - Rev 1 page 3/239

Figure 2. SPSB100GB block diagram

DS14964 - Rev 1 page 4/239

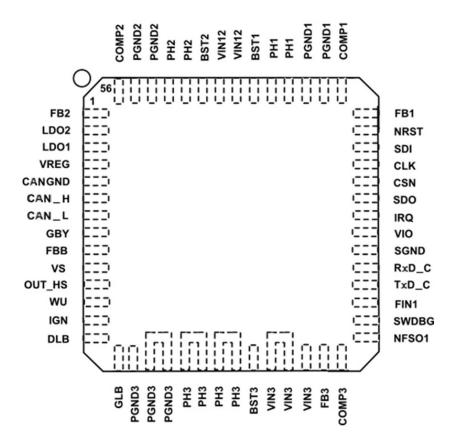

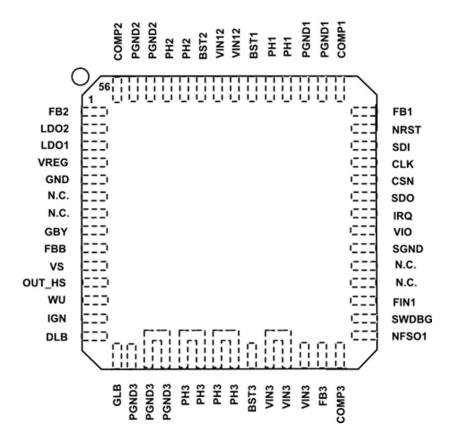

# 1.1 Pin description

Figure 3. SPSB100G pin connection (top view)

DS14964 - Rev 1 page 5/239

Figure 4. SPSB100GB pin connection (top view)

**Table 1. Pin configuration**

| Pin number | Pin SPSB100G | Pin SPSB100GB       | Description                                                                    | I/O type |

|------------|--------------|---------------------|--------------------------------------------------------------------------------|----------|

| 1          | FB2          | FB2                 | BUCK2 feedback voltage (to internal voltage monitors)                          | I        |

| 2          | LDO2         | LDO2                | 5 V/3.3 V voltage regulator - tracker of buck output                           | 0        |

| 3          | LDO1         | LDO1                | 5 V voltage regulator 1 output (for CAN-FD supply)                             | 0        |

| 4          | VREG         | VREG                | Internal 3.3 V regulator output for buck bootstrap                             | 0        |

| 5          | CANGND       | GND                 | CAN ground / Drain source monitoring ground                                    |          |

| 6          | CAN_H        | N.C. <sup>(1)</sup> | CAN high level voltage I/O                                                     | I/O      |

| 7          | CAN_L        | N.C. <sup>(1)</sup> | CAN low level voltage I/O                                                      | I/O      |

| 8          | GBY          | GBY                 | Gate driver of external MOS bypass<br>BOOST                                    | 0        |

| 9          | FBB          | FBB                 | BOOST feedback pin and supply for LDO1 & LDO2, OUT_HS, VREG, WU and IGN blocks |          |

| 10         | VS           | VS                  | Sensing boost input                                                            | I        |

| 11         | OUT_HS       | OUT_HS              | High-side driver output to supply contacts                                     | 0        |

| 12         | WU           | WU                  | Wake-up input for static or cyclic monitoring of external contact              | I        |

DS14964 - Rev 1 page 6/239

| Pin number | Pin SPSB100G                 | Pin SPSB100GB                | Description                                                                                      | I/O type |

|------------|------------------------------|------------------------------|--------------------------------------------------------------------------------------------------|----------|

| 13         | IGN                          | IGN                          | Wake-up input for static or cyclic monitoring of external contact with KL15 feature              | I        |

| 14         | DLB                          | DLB                          | Drain monitoring of external low-side MOS of BOOST                                               | 1        |

| 15         | GLB                          | GLB                          | Gate driver of external low-side MOS of BOOST                                                    | 0        |

| 16         | PGND3                        | PGND3                        | BUCK3 power ground                                                                               |          |

| 17         | PGND3, 2 <sup>nd</sup> pin   | PGND3, 2 <sup>nd</sup> pin   | BUCK3 power ground                                                                               |          |

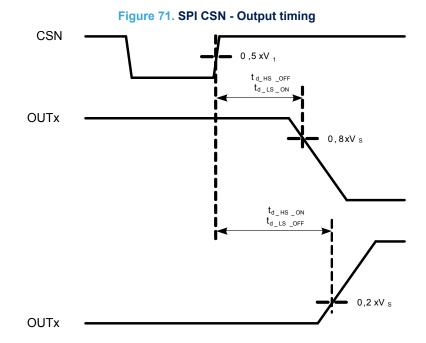

| 18         | PGND3, 3 <sup>rd</sup> pin   | PGND3, 3 <sup>rd</sup> pin   | BUCK3 power ground                                                                               |          |

| 19         | PH3                          | PH3                          | Switching node BUCK3                                                                             | I/O      |

| 20         | PH3, 2 <sup>nd</sup> pin     | PH3, 2 <sup>nd</sup> pin     | Switching node BUCK3                                                                             | 0        |

| 21         | PH3, 3 <sup>rd</sup> pin     | PH3, 3 <sup>rd</sup> pin     | Switching node BUCK3                                                                             | 0        |

| 22         | PH3,4 <sup>th</sup> pin      | PH3,4 <sup>th</sup> pin      | Switching node BUCK3                                                                             | 0        |

| 23         | BST3                         | BST3                         | Boot-strap capacitor to supply BUCK3 high-side MOS gate-driver circuitry                         |          |

| 24         | VIN3                         | VIN3                         | Input voltage BUCK3                                                                              | I        |

| 25         | VIN3,<br>2 <sup>nd</sup> pin | VIN3,<br>2 <sup>nd</sup> pin | Input voltage BUCK3                                                                              | 1        |

| 26         | VIN3,<br>3 <sup>rd</sup> pin | VIN3,<br>3 <sup>rd</sup> pin | Input voltage BUCK3                                                                              | 1        |

| 27         | FB3                          | FB3                          | BUCK3 feedback voltage (to internal voltage monitors)                                            | I        |

| 28         | COMP3                        | COMP3                        | BUCK3 error amplifier compensation network                                                       |          |

| 29         | NFSO1                        | NFSO1                        | Fail safe output (active low, open drain)                                                        | 0        |

| 30         | SWDBG                        | SWDBG                        | Debug input to deactivate the window watchdog (active high) and enter pin for NVM emulation mode | I        |

| 31         | FIN1                         | FIN1                         | FCCU sequence input                                                                              | I        |

| 32         | TxD_C                        | N.C. (1)                     | CAN transmit data input                                                                          | I        |

| 33         | RxD_C                        | N.C. (1)                     | CAN receive data output                                                                          | 0        |

| 34         | SGND                         | SGND                         | Signal ground (analog and digital reference)                                                     |          |

| 35         | VIO                          | VIO                          | I/O power supply (3.3 V or 5 V)                                                                  | I        |

| 36         | IRQ                          | IRQ                          | Interrupt (open-drain)                                                                           | 0        |

| 37         | SDO                          | SDO                          | SPI serial data output                                                                           | 0        |

| 38         | CSN                          | CSN                          | SPI chip select not input                                                                        | I        |

| 39         | CLK                          | CLK                          | SPI serial clock input                                                                           | I        |

| 40         | SDI                          | SDI                          | SPI serial data Input                                                                            | I        |

| 41         | NRST                         | NRST                         | Reset output to microcontroller, internal pull-up (open-drain)                                   | Ο        |

| 42         | FB1                          | FB1                          | BUCK1 feedback voltage (to internal voltage monitors)                                            | I        |

| 43         | COMP1                        | COMP1                        | BUCK1 error amplifier compensation network                                                       |          |

DS14964 - Rev 1 page 7/239

| Pin number | Pin SPSB100G               | Pin SPSB100GB              | Description                                                                 | I/O type |

|------------|----------------------------|----------------------------|-----------------------------------------------------------------------------|----------|

| 44         | PGND1                      | PGND1                      | BUCK1 power ground                                                          |          |

| 45         | PGND1, 2 <sup>nd</sup> pin | PGND1, 2 <sup>nd</sup> pin | BUCK1 power ground                                                          |          |

| 46         | PH1                        | PH1                        | Switching node BUCK1                                                        | I/O      |

| 47         | PH1, 2 <sup>nd</sup> pin   | PH1, 2 <sup>nd</sup> pin   | Switching node BUCK1                                                        | 0        |

| 48         | BST1                       | BST1                       | Bootstrap capacitor to supply BUCK1 high-<br>side MOS gate-driver circuitry |          |

| 49         | VIN12                      | VIN12                      | Input voltage BUCK1 and BUCK2                                               | I        |

| 50         | VIN12                      | VIN12                      | Input voltage BUCK1 and BUCK2                                               | I        |

| 51         | BST2                       | BST2                       | Bootstrap capacitor to supply BUCK2 high-<br>side MOS gate-driver circuitry |          |

| 52         | PH2                        | PH2                        | Switching node BUCK2                                                        | I/O      |

| 53         | PH2, 2 <sup>nd</sup> pin   | PH2, 2 <sup>nd</sup> pin   | Switching node BUCK2                                                        | 0        |

| 54         | PGND2,                     | PGND2,                     | BUCK2 power ground                                                          |          |

| 55         | PGND2, 2 <sup>nd</sup> pin | PGND2, 2 <sup>nd</sup> pin | BUCK2 power ground                                                          |          |

| 56         | COMP2                      | COMP2                      | BUCK2 error amplifier compensation network                                  |          |

<sup>1.</sup> For the SPSB100GB version, it is recommended to connect the N.C. pins to ground.

DS14964 - Rev 1 page 8/239

# 2 Maximum ratings

# 2.1 Operating range

Within the operating range, the part operates as specified and without any parameter deviations. The device may not operate properly if maximum operating conditions are exceeded.

Once taken beyond the operative ratings and returned back to within the specified range, the part recovers with no damage or degradation.

Additional supply voltage and temperature conditions are given separately at the beginning of each electrical specification table.

All voltages are related to the potential at the CANGND pin internally connected to the substrate.

| Symbol            | Parameter                    | Min. | Тур. | Max. | Unit |

|-------------------|------------------------------|------|------|------|------|

| Vs (1) (2)        | Global                       | 3    |      | 29   | V    |

| F <sub>BB</sub>   | Boost output                 | 7.7  |      | 29   | V    |

| VIN <sub>12</sub> | Buck1 & Buck2 supply pin     | 7.7  |      | 29   | V    |

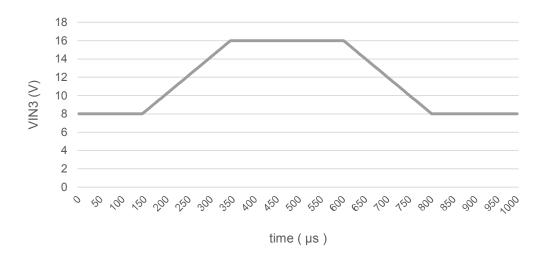

| VIN <sub>3</sub>  | Buck3 supply pin             | 3    |      | 7    | V    |

| VIO               | Digital interface supply pin | 3    |      | 5.5  | V    |

**Table 2. Operating conditions**

# 2.1.1 Supply voltage ranges

All SPI communication, logic and oscillator parameters work down to  $V_S = V_{PORVS\_F}$  and are specified accordingly:

- SPI thresholds

- · Oscillator frequency (delay times correctly elapsed)

- Internal register status correctly kept (reset at default values for V<sub>S</sub> < V<sub>PORVS</sub> <sub>F</sub>)

- Reset threshold correctly detected

# 2.2 Absolute maximum ratings

Maximum ratings are absolute ratings; exceeding any one of these values may cause permanent damage to the integrated circuit.

All voltages are related to the potential at the substrate ground pin.

Table 3. Absolute maximum ratings

| Symbol              | Parameter                                                                   | Condition                                          | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------------|----------------------------------------------------|------|------|------|------|

| V <sub>S_LD</sub>   | DC supply voltage                                                           | Load dump 400 ms max.                              | -0.3 |      | 40   | V    |

| V <sub>S_rev</sub>  | DC supply voltage for reverse battery                                       | Reverse battery with limited current at max. 30 mA | -1.0 |      |      | V    |

| V <sub>FBB_LD</sub> | Boost output voltage range<br>Supply for LDO1&2, OUT_HS, IGN & WU<br>blocks | Load dump 400 ms max.                              | -0.3 |      | 40   | V    |

| $V_{GLB}$           | Boost gate driver voltage range                                             | $V_{GLB} < V_{FBB} + 0.3 V$                        | -0.3 |      | 13.4 | V    |

| $V_{DLB}$           | Boost external drain voltage range                                          |                                                    | -0.3 |      | 40   | V    |

| $V_{GBY}$           | Bypass gate driver voltage range                                            | $V_{GBY} < V_{FBB} + 0.3 V$                        | -0.3 |      | 40   | V    |

DS14964 - Rev 1 page 9/239

<sup>1.</sup>  $V_S$  operating range from 3 V up to 6 V is intented as a transitory time during cranking conditions.

<sup>2.</sup> The device is compatible to Jump start events up to 29 V maximum V<sub>S</sub> voltage.

| Symbol                          | Parameter                                                 | Condition                                                     | Min. | Тур. | Max. | Unit |

|---------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|------|------|------|------|

| V <sub>REG</sub>                | 3.3 V regulator output for bucks bootstrap                |                                                               | -0.3 |      | 4.6  | V    |

| V <sub>IN12_LD</sub>            | Buck1&2 input voltage range                               | $V_{\rm IN12}$ < $V_{\rm FBB}$ + 0.3 V, load dump 400 ms max. | -0.3 |      | 40   | V    |

| V <sub>FB1</sub>                | Buck1 feedback voltage range                              | V <sub>FB1</sub> < V <sub>FBB</sub> + 0.3 V                   | -0.3 |      | 20   | V    |

| V <sub>FB2</sub>                | Buck2 feedback voltage range                              | V <sub>FB2</sub> < V <sub>FBB</sub> + 0.3 V                   | -0.3 |      | 20   | V    |

| V <sub>PH1</sub> (1)            | Buck1 phase output voltage range                          |                                                               | -0.3 |      | 40   | V    |

| V <sub>PH2</sub> <sup>(1)</sup> | Buck2 phase output voltage range                          |                                                               | -0.3 |      | 40   | V    |

| V <sub>BST1</sub>               | Buck1 bootstrap voltage range                             | V <sub>BST1</sub> < V <sub>PH1</sub> + 4.6 V                  | -0.3 |      | 40   | V    |

| V <sub>BST2</sub>               | Buck2 bootstrap voltage range                             | V <sub>BST2</sub> < V <sub>PH2</sub> + 4.6 V                  | -0.3 |      | 40   | V    |

| V <sub>COMP1</sub>              | Buck1 compensation voltage range                          |                                                               | -0.3 |      | 4.6  | V    |

| V <sub>COMP2</sub>              | Buck2 compensation voltage range                          |                                                               | -0.3 |      | 4.6  | V    |

| V <sub>IN3</sub>                | Buck3 input voltage range                                 |                                                               | -0.3 |      | 20   | V    |

| V <sub>FB3</sub>                | Buck3 feedback voltage range                              |                                                               | -0.3 |      | 20   | V    |

| V <sub>PH3</sub> <sup>(1)</sup> | Buck3 output phase voltage range                          |                                                               | -0.3 |      | 20   | V    |

| V <sub>BST3</sub>               | Buck3 bootstrap voltage range                             | V <sub>BST3</sub> < V <sub>PH3</sub> + 4.6 V                  | -0.3 |      | 20   | V    |

| V <sub>COMP3</sub>              | Buck3 compensation voltage range                          |                                                               | -0.3 |      | 4.6  | V    |

| V <sub>LDO1</sub>               | Stabilized supply voltage 1                               | V <sub>LDO1</sub> < V <sub>FBB</sub> + 0.3 V                  | -0.3 |      | 6.5  | V    |

| V <sub>LDO2</sub>               | Stabilized supply voltage 2                               | V <sub>LDO2</sub> < V <sub>FBB</sub> + 0.3 V                  | -0.3 |      | 20   | V    |

| V <sub>IO</sub>                 | I/O supply voltage                                        |                                                               | -0.3 |      | 20   | V    |

| V <sub>SDI</sub>                | Logic input                                               |                                                               | -0.3 |      | 20   | V    |

| V <sub>CLK</sub>                | Logic input                                               |                                                               | -0.3 |      | 20   | V    |

| V <sub>CSN</sub>                | Logic input                                               |                                                               | -0.3 |      | 20   | V    |

| V <sub>SDO</sub>                | Logic output                                              |                                                               | -0.3 |      | 20   | V    |

| V <sub>RXD_C</sub>              | Logic output                                              |                                                               | -0.3 |      | 20   | V    |

| V <sub>NRST</sub>               | Open-drain output (with internal pull-up)                 |                                                               | -0.3 |      | 20   | V    |

| V <sub>IRQ</sub>                | Open-drain output (with internal pull-up)                 |                                                               | -0.3 |      | 20   | V    |

| V <sub>TXD_C</sub>              | Logic input                                               |                                                               | -0.3 |      | 20   | V    |

| V <sub>SWDBG</sub>              | Debug input pin voltage range                             |                                                               | -0.3 |      | 20   | V    |

| V <sub>FIN1</sub>               | FIN1 input voltage range                                  |                                                               | -0.3 |      | 20   | V    |

| V <sub>NFSO1</sub>              | Open-drain output (without internal pull-up)              |                                                               | -0.3 |      | 40   | V    |

| V <sub>WU_LD</sub>              | DC WU input voltage                                       | Load dump 400 ms max.                                         | -0.3 |      | 40   | V    |

| V <sub>IGN_LD</sub>             | DC IGN input voltage                                      | Load dump 400 ms max.                                         | -0.3 |      | 40   | V    |

| I <sub>Input</sub>              | Current injection into FBB related input pins WU, IGN (2) |                                                               | -20  |      | 20   | mA   |

| V <sub>CAN_H</sub>              | CAN bus I/O                                               |                                                               | -27  |      | 40   | V    |

| V <sub>CAN_L</sub>              | CAN bus I/O                                               |                                                               | -27  |      | 40   | V    |

| V <sub>OUT_HS</sub>             | Output voltage                                            | V <sub>OUT_HS</sub> < F <sub>BB</sub> + 0.3 V                 | -0.3 |      | 40   | V    |

| I <sub>OUT_HS</sub>             | Current injection OUT_HS (2)                              |                                                               | -20  |      | 20   | mA   |

DS14964 - Rev 1 page 10/239

| Symbol                                    | Parameter                                     | Condition | Min.  | Тур. | Max. | Unit |

|-------------------------------------------|-----------------------------------------------|-----------|-------|------|------|------|

| I <sub>SGND</sub> (3)                     | Maximum current at SGND (3)                   |           | -1.25 |      | 1.25 | Α    |

| I <sub>VIN12</sub>                        | Maximum current at VIN12 (3) (for each pin)   |           | -5    |      | 5    | Α    |

| I <sub>PGND1,</sub><br>I <sub>PGND2</sub> | Maximum current at PGND1&2 (3) (for each pin) |           | -5    |      | 5    | Α    |

| I <sub>PH1,</sub> , I <sub>PH2</sub>      | Maximum current at PH1&2 (3) (for each pin)   |           | -5    |      | 5    | Α    |

| I <sub>VIN3</sub>                         | Maximum current at VIN3 (3) (for each pin)    |           | -5    |      | 5    | Α    |

| I <sub>PGND3</sub>                        | Maximum current at PGND3 (3) (for each pin)   |           | -5    |      | 5    | Α    |

| I <sub>PH3</sub>                          | Maximum current at PH3 (3) (for each pin)     |           | -5    |      | 5    | Α    |

| $V_{PGND}$                                | PGND versus CANGND                            |           | -0.3  |      | 0.3  | V    |

| $V_{GND}$                                 | SGND versus CANGND                            |           | -0.3  |      | 0.3  | V    |

- 1. Transients on this pin can be tolerated for a duration < 100 ns, not exceeding -3 V.

- 2. Guaranteed by design.

- 3. Values for the absolute maximum DC current through the bond wires. This value does not consider maximum power dissipation or other limits. Guaranteed by design.

## 2.3 ESD robustness

**Table 4. ESD protection**

| Symbol           | Parameter | Condition                                | Min.          | Тур. | Max.        | Unit |

|------------------|-----------|------------------------------------------|---------------|------|-------------|------|

| Pins             | All pins  | HBM <sup>(1)</sup>                       | -2            |      | 2           | kV   |

| Power output pin | OUT_HS    | HBM <sup>(2)</sup>                       | -4            |      | 4           | kV   |

| Transceiver      | CAN_H     | HBM <sup>(2)</sup>                       | -8            |      | 8           | kV   |

| Transceiver      | CAN_H     | Direct ESD (3)                           | -6            |      | 6           | kV   |

| Transceiver      | CAN_L     | HBM <sup>(2)</sup>                       | -8            |      | 8           | kV   |

| Transceiver      | CAN_L     | Direct ESD (3)                           | -6            |      | 6           | kV   |

| Pins (4)         | All pins  | CDM (values for corner pins in brackets) | -500 / (-750) |      | 500 / (750) | V    |

- 1. HBM (Human Body Model, 100 pF, 1.5 k $\Omega$ ) according to AEC-Q100-002.

- 2. HBM with all non-zapped pins grounded.

- 3. Direct ESD Test according to ISO 10605 (150 pF, 330  $\Omega$ ) and IEC62228-3.

- 4. CDM (Charged Device Model) according to AEC-Q100-011.

# 2.4 Temperature ranges and thermal data

Table 5. Temperature ranges and thermal data

| Symbol           | Parameter                      | Condition | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------|-----------|------|------|------|------|

| T <sub>amb</sub> | Operating temperature          |           | -40  | -    | 125  | °C   |

| T <sub>j</sub>   | Operating junction temperature |           | -40  | -    | 175  | °C   |

| T <sub>stg</sub> | Storage temperature            |           | -55  | -    | 150  | °C   |

DS14964 - Rev 1 page 11/239

| Symbol                 | Parameter                                                                                       | Condition                      | Min. | Тур. | Max. | Unit |

|------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|------|------|------|------|

| T <sub>W</sub>         | Thermal overtemperature warning threshold                                                       |                                | 140  | -    | 160  | °C   |

| T <sub>SD</sub>        | Thermal shut-down junction temperature                                                          |                                | 165  | -    | 185  | °C   |

| T <sub>SDC</sub>       | Central thermal shut-down junction temperature                                                  |                                | 175  | -    | 195  | °C   |

| T <sub>SDhys</sub>     | Thermal shut-down temperature hysteresis                                                        |                                | 0    | 5    | 10   | °C   |

| T <sub>F_TJ</sub>      | Thermal warning/shut-down filter time                                                           | Covered by scan                | 60   | 75   | 90   | μs   |

| T <sub>F_TSDC</sub>    | Central thermal shut-down filter time                                                           | Covered by scan                | 25.6 | 32   | 38.4 | μs   |

| R <sub>Th j-amb</sub>  | Thermal resistance junction-to-<br>ambient                                                      | JEDEC 2s2p board<br>(JESD51-7) | 25   |      |      | °C/W |

| R <sub>Th j-Cbot</sub> | Thermal resistance junction-to-<br>Case bottom with uniform power<br>dissipation on silicon die | JEDEC 2s2p board               | 0.5  |      |      | °C/W |

All parameters are guaranteed in the junction temperature range from -40 to +150  $^{\circ}$ C (unless otherwise specified). The device is still operational and functional up to 175  $^{\circ}$ C.

The SPSB100G embeds a multitude of junctions housed in a relatively small piece of silicon. The devices contain, among all the described features, two voltage regulators (one of which can operate as a voltage tracker) and three buck converters with internal power stages and one high-side driver. For this reason, using the thermal impedance of a single junction (i.e. the voltage regulator or major power dissipation contributor) does not allow prediction of the thermal behavior of the whole device, and therefore it is not possible to assess whether a device is thermally suitable for a given activation profile and load characteristics. Thermal information is provided as temperature readings by different clusters located close to the most dissipative junctions. Some representative and realistic case thermal profiles are described below:

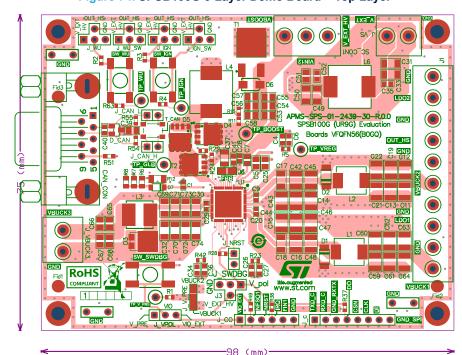

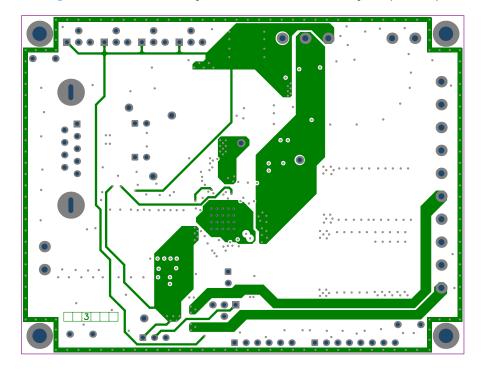

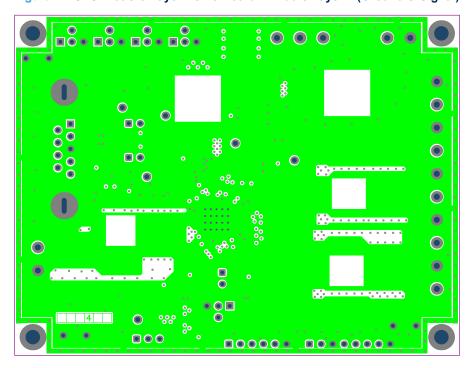

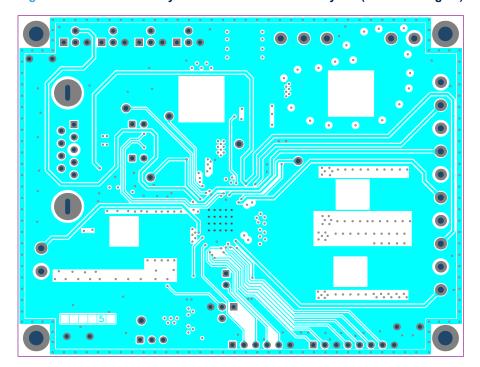

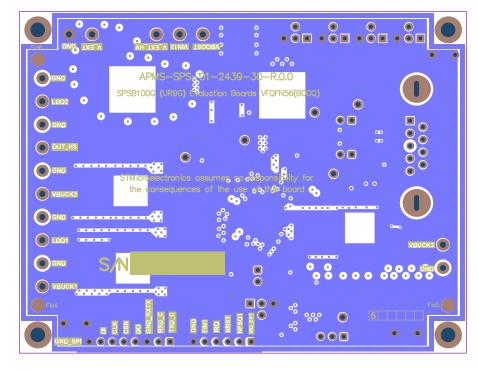

Figure 5. VFQFN56+4L printed circuit board, 4 layers - top layer

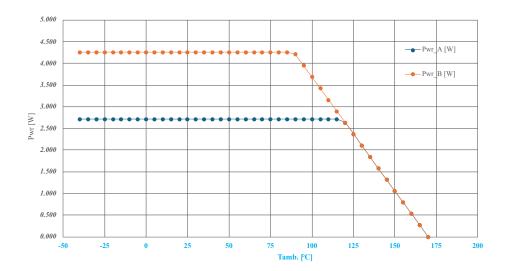

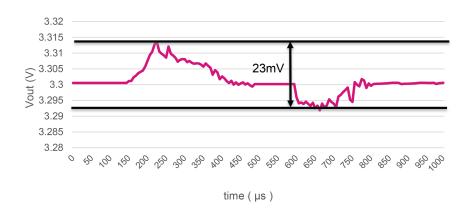

Two typical application scenarios related to system configuration 1 and differentiated based on the selected Buck1,2 frequencies are described below:

$V_{bat} = 16 \text{ V}, R_{thja} = 25^{\circ}\text{C/W}, T_{jmax} = 170 ^{\circ}\text{C}$

Case A

DS14964 - Rev 1 page 12/239

- LDO1 (5 V): output load 100 mA

- LDO2 (5 V): output load 5 mA

- OUT\_HS: I<sub>LOAD</sub> = 20 mA

- Buck1 (3.3 V): output load 1 A at 400 kHz

- Buck2 (5.0 V): output load 1 A at 400 kHz

- Buck3 (0.98 V): output load 2 A at 2.4 MHz

## Case B

- LDO1 (5 V): output load 100 mA

- LDO2 (5 V): output load 5 mA

- OUT\_HS: I<sub>LOAD</sub> = 20 mA

- Buck1 (3.3 V): output load 1 A at 2.4 MHz

- Buck2 (5.0 V): output load 1 A at 2.4 MHz

- Buck3 (0.98 V): output load 2 A at 2.4 MHz

Note:

- 1. Buck3 load current is already considered in the power dissipation calculation, so 1 A is referred to Buck1 external load current.

- 2. Selecting the switching frequency at 2.4 MHz for Buck1 and Buck2 will lower the regulators efficiency. In applications where high output power requirements significantly affect total power dissipation, using a 400 kHz switching frequency for Buck1 and Buck2 is recommended to reduce global power losses and simplify the thermal management design.

The curves below illustrate the range of ambient temperature within which the total power dissipation for use cases A and B can be sustained. The ambient temperature at which the curves drop indicates the point where the maximum total power dissipation must be reduced to prevent activation of the over-temperature.

Figure 6. Cases A and B power dissipation management vs. ambient temperature with Buck1 and Buck2 at 400 kHz and 2.4 MHz

DS14964 - Rev 1 page 13/239

# 3 Functional description

# 3.1 Supply configurations

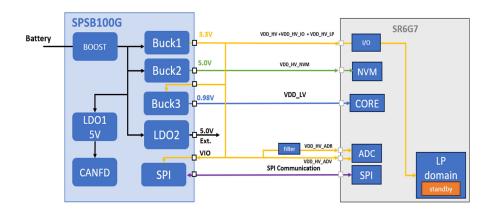

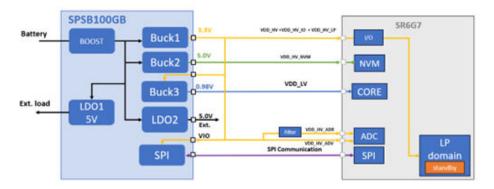

The battery supplies the boost controller. F<sub>BB</sub>, the boost output, supplies internal regulated voltages of analog and digital blocks, the wake-up blocks, the OUT\_HS output, and fail-safe block. Buck1, Buck2, and Buck3 have independent supply pins in order to allow different supply configurations according to the application. Below, we describe the two main configurations where it is required to provide direct supply to the microcontroller core.

#### 3.1.1 System supply configuration 1

Figure 7. SPSB100G direct supply of the microcontroller core

Figure 8. SPSB100GB direct supply of the microcontroller core

In the above configurations, only differentiated for the SPSB100G and SPSB100GB (without transceiver), the Buck3 is supplied by Buck1 and is configured to provide a 0.98 V high-current supply to the MCU CORE. Buck1 and Buck2 are supplied by the boost and supply the 3.3 V and the 5 V. Boost always supplies LDO1 and LDO2, both providing 5 V.

The configuration 1 setting description can be found in chapter 10.3.

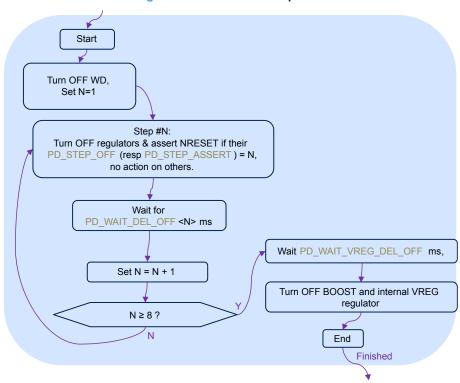

The power-up and power-down sequence associated with this supply configuration are as follows:

DS14964 - Rev 1 page 14/239

#### Power-up sequence:

- Step 1: turn ON Buck1 at 3.3 V, wait PG (BUCK1\_PG\_OK flag)

- Step 2: turn ON Buck3 at 0.98 V, wait PG (BUCK3 PG OK flag)

- Step 3: turn ON Buck2 at 5 V, wait PG (BUCK2 PG OK flag)

- Step 4: turn ON LDO2 in tracker of Buck2, wait PG (LDO2\_PG\_OK flag)

- Step 5: turn ON LDO1, wait 0 ms

- Step 6: deassert NRST, wait 0 ms

#### Power-down sequence:

- Step 1: ASSERT NRST, wait 2 ms

- Step 2: turn OFF LDO2 and LDO1, wait 2 ms

- Step 3: turn OFF Buck3, wait 2 ms

### 3.1.2 Digital interface supply: VIO

The VIO pin supplies the SPI interface as well as the IRQ, FIN1, NRST, RxD C, TxD C pins.

The VIO pin can be supplied from one of the SPSB100G bucks, or from an external regulator.

Digital pin functionalities are guaranteed when  $V_{IO} > V_{VIO\_UV\_R}$  (VIO\_UV flag not raised).

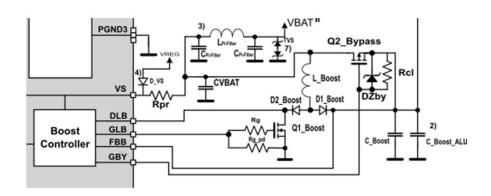

## 3.2 Boost controller

The boost, or step-up controller, generates an output voltage that supplies the SPSB100G device and the buck converters only during a transitory time at power-up to reach a normal operating range (12 V battery range), or during low battery conditions, to sustain cranking.

In case the  $V_S$  voltage exceeds the  $V_{TH\_BYPASS\_Rx}$  threshold, the converter will be deactivated and battery supplies the buck converters via a separate bypass MOSFET.

The live bit BOOST\_ENA\_STATUS reflects the state of the boost.

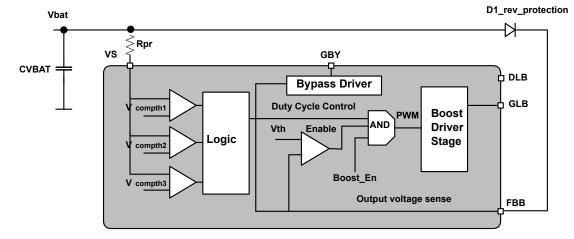

The block diagram of the boost is shown in the figure below:

Q2\_Bypas L\_Boost D1 Boost Vbat V\_Boost KI-Rpr vs GBY D2 Boost CVBAT **Bypass Driver** GLB **Duty Cycle Control** Q1 Boost C Boost Boost ΔND Driver Vth Enable Logic Stage Rg\_p Boost En Output voltage sense FBB

Figure 9. Boost controller block diagram

According to the sensed battery voltage on the VS pin (VS\_LOW, VS\_MID and VS\_ HIGH thresholds), the boost duty cycle is suitably adjusted (BOOST\_DC\_Max when VS voltage is between VPORVS\_F and VS\_LOW, BOOST\_DC\_High when VS is between VS\_LOW and VS\_MID, Boost\_DC\_Min when VS is between VS\_MID and VS\_HIGH and BOOST\_DC\_Low when VS is higher than VS\_HIGH) in order to keep the output voltage quite above the selected thresholds.

The system is compliant with the newly defined "Cold Cranking Pulse" required by start-stop systems. Moreover, a suitable bypass MOSFET is driven when the BOOST is not switching, in order to bypass the inductor, minimizing overall losses during normal operation.

The boost and the bypass drivers can be switched OFF permanently by setting BOOST\_DIS=1 and BYPASS\_DIS=1 respectively in the USER-NVM space.

DS14964 - Rev 1 page 15/239

If the BOOST function is used (BOOST DIS=0):

- at power-up, the bypass control is enabled when the state machine enters INIT state (after successful safety checks). If V<sub>S</sub> > V<sub>TH\_BYPASS\_R</sub>, the external bypass switch is turned on (BYPASS\_STATUS=1) while the boost PWM is stopped. When V<sub>S</sub> < V<sub>TH\_BYPASS\_F</sub>, the external switch is turned off (BYPASS\_STATUS=0) and boost switching is activated.

- in ACTIVE FULL-POWER mode and in RECOVERY-1 state, when V<sub>S</sub> > V<sub>TH\_BYPASS\_R</sub>, the external bypass switch is turned on after t<sub>F\_BYPASS\_EN</sub> timing (BYPASS\_STATUS=1) the boost PWM is stopped.

FBB > V<sub>FBB\_REGx</sub> thresholds. When V<sub>S</sub> < V<sub>TH\_BYPASS\_F</sub>, the bypass switch is turned off after t<sub>F\_BYPASS\_DIS</sub> timing (BYPASS\_STATUS=0) and the boost switching is activated if FBB < V<sub>FBB\_REGx</sub> thresholds.

- in ACTIVE LOW-POWER mode, the BYPASS controller is disabled, turning the external switch (BYPASS\_STATUS=0) off: the consumption on the battery is limited to few mA so no dissipation issue is expected on the D1\_boost diode.

- in ACTIVE–LOW-POWER mode, the BOOST IP is disabled to reduce the overall SPSB100G consumption.

It is woken up when the monitored V<sub>S</sub> goes below V<sub>TH\_BYPASS\_Fx</sub> for the remaining active BUCK with duty cycle BOOST\_DC\_LP.

- In RECOVERY-2 or DEEP-SLEEP state, the boost is always OFF and the BYPASS controller is always disabled (BYPASS STATUS=0).

If the BOOST function is not used (USER-NVM BOOST DIS=1 or SPI bit BOOST OFF=1):

- at power-up, the bypass control is enabled, turning on the external switch (BYPASS\_STATUS=1), as soon

as the state machine reaches the INIT state and following successful safety checks.

- in ACTIVE FULL-POWER mode and in RECOVERY-1 state, the BYPASS switch is turned on whatever the V<sub>S</sub> voltage (BYPASS\_STATUS=1).

- In ACTIVE LOW-POWER mode, DEEP-SLEEP or RECOVERY-2 state, the BYPASS controller is disabled, turning off the external switch (BYPASS STATUS=0).

The block diagram of the device when boost is not used is shown in the figure below. Note that the D1\_rev\_protection diode is needed only if there is no reverse battery protection solution already implemented in the application.

Figure 10. Boost controller disabled block diagram

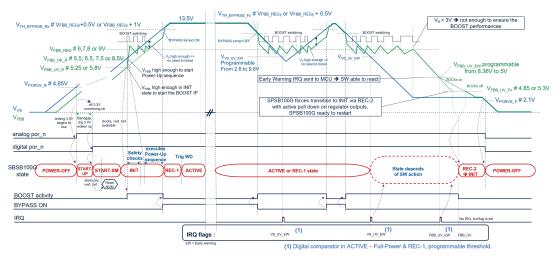

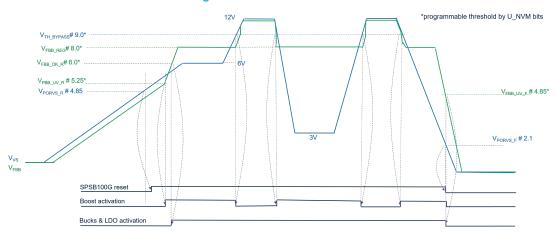

#### 3.2.1 Power-up/down and voltage drop behavior

The boost role is crucial for SPSB100G operation, so its behavior related to normal or accidental variations of the voltage supply should be clearly defined. The general behavior is described in the following figures.

DS14964 - Rev 1 page 16/239

Figure 11. Battery plug/unplug behavior

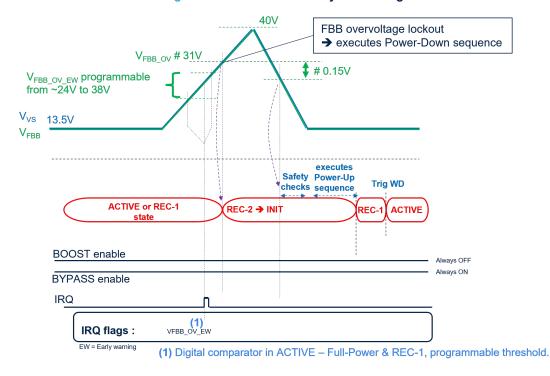

Overvoltage cases are not critical for the boost itself (bypass is ON) but for the regulators (Bucks, LDOs...) that are directly supplied. These are managed according to configured thresholds (through VFBB\_OV threshold) which trigger a power down sequence in any case. Power-up is initiated as long as the voltage decreases below the overvoltage FBB\_OV\_F.

DS14964 - Rev 1 page 17/239

Figure 13. Behavior on battery over voltage

Undervoltage cases are critical for the regulators (Bucks, LDOs...) that are directly supplied. These are managed according to configured thresholds (through  $V_{FBB\_UV\_F}$  threshold) which trigger a power-down sequence in any case. Undervoltage can be triggered based on FBB early warning thresholds. If FBB\\_UV\_EW\_PD is set high, the power-down sequence is triggered at the threshold defined by the FBB\_UV\_EW\_TH[3:0] bits.

Power-up is initiated as long as the FBB voltage increases above the threshold V<sub>FBB OK Rx</sub>.

#### 3.2.2 Boost modes

It is possible to set two different boost modes for the SPSB100G through U-NVM bits:

- Boost Cranking mode when U-NVM bit BOOST\_CRK\_ONLY = 1.

- Boost Normal mode when U-NVM bit BOOST\_CRK\_ONLY = 0.

For both modes, the following points apply:

- Flexibility on boost regulation level (V<sub>FBB\_REGx</sub>) can be set in the FBB\_REG\_LEVEL\_SEL[1:0] bit.

- Flexibility on comparator thresholds V<sub>TH\_BYPASS\_Rx</sub> to enable and V<sub>TH\_BYPASS\_Fx</sub> to disable the external bypass MOSFET can be set in the BYPASS\_OFFSET\_SEL and FBB\_REG\_LEVEL\_SEL[1:0] bits.

- Flexibility on FBB level (V<sub>FBB\_OK\_Rx</sub>) to execute the power-up sequence can be set in the FBB\_OK\_SEL[1:0] bits.

- Flexibility on FBB level (V<sub>FBB UV Rx</sub>) to start the boost can be set in the FBB\_UV\_LEVEL\_SEL bit.

- A programmable timer  $t_{boost\_crk\_tox}$  to disable the boost when  $V_S < V_{S\_SENSEx}$  can be set in the BOOST\_CRK\_TO[2:0] bits.

- The timer can be disabled if BOOST\_CRK\_TO = '000'.

- When the timer expires, the flag BOOST\_TIMER\_CNT\_END is set and generates an IRQ unless the MASK\_BOOST\_TIMER\_CNT\_END\_IRQ is set.

- The bit BOOST\_CNT\_END can be used to stop the timer when it is running by setting this bit to 1. To relaunch the timer, a transition from 1 to 0 for the bit BOOST\_CNT\_END is required.

#### 3.2.2.1 Boost Cranking mode

To activate the Boost Cranking mode, it is required to set it via the U-NVM bit BOOST CRK ONLY at "1".

DS14964 - Rev 1 page 18/239

This mode allows SPSB100G to work as follows:

- Boost active for V<sub>S</sub> < V<sub>S\_SENSEx</sub> (managing potential cranking condition)

- Boost inactive for V<sub>S</sub> ≥ V<sub>S\_SENSEx</sub>

Where  $V_{SENSE}$  is a monitoring comparator that permits enabling/disabling boost, and is programmable in the U\_NVM bit VS\_SENSE\_LEVEL\_SEL[1:0] from 5.4 V to 5.85 V, with four steps of 150 mV.

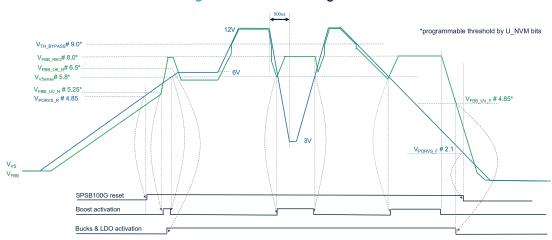

Figure 14. Boost Cranking mode

Note:

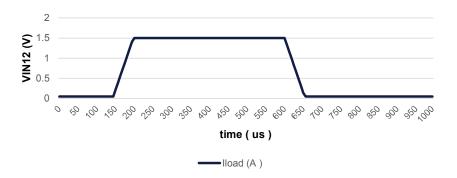

Buck1,2 output current capabilities are linked to input voltage applied. Please refer to current limitations curves reported in Section 7.9: BUCK2 converter.

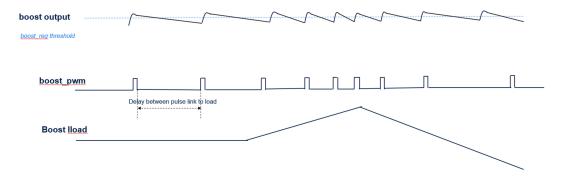

## 3.2.2.2 Boost Normal mode

To activate Boost normal mode, it is required to set it via the U-NVM bit BOOST\_CRK\_ONLY = 0.

DS14964 - Rev 1 page 19/239

Figure 15. Boost Normal mode

Figure 16. Boost Normal mode - pulses with high/medium load

# 3.3 Buck converters

### 3.3.1 Buck1 converter

The Buck1 regulator is a synchronous converter compatible with battery level, with integrated power MOS. Stability compensation network is external.

Output voltages are programmable via the USER -NVM through the bit BUCK1\_PU\_VALUE.

The switching frequency can be selected either at 400 kHz or 2.4 MHz, by USER-NVM bit BUCK1\_FREQ. To limit emission in the audio bandwidth, refresh frequency can be forced at 25 kHz by USER-NVM bit BUCK1\_REFRESH\_FREQ set low (1 kHz when high). The drawback to this will be additional consumption in low-power mode.

The spread-spectrum feature is configurable via the SPI bit BUCK1\_SPREAD\_ENA (disabled by default).

Buck1 integrates a low-power mode (automatically set by LOW\_POWER\_SET in the SPI) which optimizes its efficiency in active low-power mode (Buck1 is a mandatory regulator in active low-power mode).

Buck1 can be disabled/enabled in active full power via the SPI bit VBUCK1\_ENA (only after SPI\_PROTECT\_ACCESS has been set). In active low-power mode, enabling Buck1 is not allowed.

The live bit VBUCK1\_ENA\_STATUS reflects the state of Buck1 output.

Note that after the first power-up, the control bit VBUCK1\_ENA needs to be aligned with live bit VBUCK1\_ENA\_STATUS.

DS14964 - Rev 1 page 20/239

In active full-power, the Buck1 converter provides the following diagnostics:

- UV detection to monitor the output voltage (flag is BUCK1\_UV). Buck1 is therefore switched off after tbuck1\_UV\_TO, except if SPI bit MASK\_BUCK1\_UV\_POWER\_OFF is set

- Undervoltage detection generates an IRQ, except if MASK\_BUCK1\_IRQ is set

- OV detection to monitor the output voltage (flag is BUCK1\_OV bit). Buck1 is therefore switched off after tbuck1\_OV\_TO. The status register bit BUCK1\_OV must be read and cleared before switching ON the regulator via the SPI bit VBUCK1\_ENA to allow a proper start-up (only when Buck1 is not critical for the MCU).

- Overvoltage detection generates an IRQ, except if MASK\_BUCK1\_IRQ is set.

- Power-good detection is used to signal Buck power-on success (flag is BUCK1\_PG\_OK bit) and IRQ is generated except if MASK\_BUCK1\_PG\_IRQ is set.

- If not, after TBUCK1 PG TO timeout, Buck1 is switched off and the flag BUCK1 PG TIMEOUT is set.

- Unsuccessful power-good detection generates an IRQ except if MASK\_BUCK1\_PG\_TIMEOUT\_IRQ is set.

- Configurable overcurrent protection through U-NVM BUCK1\_IPEAK (flag is BUCK1\_OC bit). Buck1 is therefore switched off after a time of tbuck1 OC TO except if MASK BUCK1 OC POWER OFF is set.

- Overcurrent detection generates an IRQ except if MASK\_BUCK1\_OC\_IRQ is set.

- Warning temperature detection by a local thermal sensor (flag is TW CL1).

- Warning temperature detection generates an IRQ except if MASK CL1 TW IRQ is set.

- Overtemperature detection by a local thermal sensor (flag is TSD\_CL1, see also Section 4.7) and buck1 is switched off.

- Buck1 internal regulators detection (flag is BUCK1\_INT\_FAIL) and Buck1 is switched off.

- Internal fail generates an IRQ except if MASK\_BUCK1\_IRQ is set.

- After a fault detection (UV, OV, OC, FBLOSS, TSD\_CL1 or PG timeout), Buck1 can be re-enabled by setting BUCK1\_ENA = 0, followed by BUCK1\_ENA=1.

- Buck1 feedback (FB1) pin disconnection (flag is BUCK1\_FBLOSS). Buck1 is switched off.

- FB1 pin disconnection generates an IRQ except if MASK\_BUCK1\_IRQ is set.

In active low- power, the Buck1 converter provides the following diagnostics:

- UV detection to monitor the output voltage (flag is BUCK1\_UV). Buck1 is therefore switched off except if SPI bit MASK\_BUCK1\_UV\_POWER\_OFF is set.

- Undervoltage detection generates an IRQ except if MASK\_BUCK1\_IRQ is set.

- OV detection to monitor the output voltage (flag is BUCK1\_OV bit). Buck1 is therefore switched off.

- Overvoltage detection generates an IRQ except if MASK\_BUCK1\_IRQ is set.

- Overcurrent protection (flag is BUCK1\_OC bit). Buck1 is therefore switched off except if MASK\_BUCK1\_OC\_POWER\_OFF is set.

- Overcurrent detection generates an IRQ except if MASK\_BUCK1\_OC\_IRQ is set.

- Buck1 feedback (FB1) pin disconnection (flag is BUCK1 UV). Buck1 is switched off.

- FB1 pin disconnection generates an IRQ except if MASK\_BUCK1\_IRQ is set.

- Overtemperature detection by the central thermal sensor (flag is TSD\_CL0, see also Section 4.7) and device power-down sequence is executed.

In ACTIVE and REC-1 states, when BUCK1\_REGFAIL\_GO\_REC is set at 1 in the USER-NVM, in case of PG timeout, OV, UV, INT\_FAIL, OC, FBLOSS, or TSD events, the device executes a power-down sequence, enters REC-2 state and makes an automatic retry. PG\_TIMEOUT, OV, UV, OC, INT\_FAIL, FBLOSS or TSD flags are not blocking a re-enable of the BUCK1.

According to a suitably configured output voltage, it can also be used to supply another buck. It is not recommended to use MASK\_BUCK1\_OC\_POWER\_OFF and MASK\_BUCK1\_UV\_POWER\_OFF at the same time.

#### 3.3.2 Buck2 converter

The Buck2 converter is the same as the Buck1.

The Buck2 regulator is a synchronous converter compatible with battery level, with an integrated power MOS. Stability compensation network is external.

Output voltages are programmable via the USER -NVM through the bit BUCK2 PU VALUE.

DS14964 - Rev 1 page 21/239

The switching frequency can be selected either at 400 kHz or 2.4 MHz, by USER-NVM BUCK2\_FREQ. To limit emission in the audio bandwidth, refresh frequency can be forced at 25 kHz by USER-NVM bit BUCK2\_REFRESH\_FREQ set low (1 kHz when high). The drawback to this will be additional consumption in low-power mode.

The spread-spectrum feature is configurable via the SPI bit BUCK2\_SPREAD\_ENA (disabled by default).

Buck2 integrates a low-power mode (automatically set by LOW\_POWER\_SET in the SPI) which optimize its efficiency in active low-power mode. (Buck2 can be optionally enabled in active low-power mode).

Buck2 can be disabled via the SPI bit VBUCK2\_ENA. (only after SPI\_PROTECT\_ACCESS has been set). In active low-power mode, enabling Buck2 is not allowed.

The live bit VBUCK2\_ENA\_STATUS reflects the state of Buck2 output.

Note that after the first power-up, the control bit VBUCK2\_ENA needs to be aligned with live bit VBUCK2\_ENA\_STATUS.

In active full-power, the Buck2 converter provides the following diagnostics:

- UV detection to monitor the output voltage (flag is BUCK2\_UV). Buck2 is therefore switched off after tbuck2\_UV\_TO except if SPI bit MASK\_BUCK2\_UV\_POWER\_OFF is set.

- Undervoltage detection generates an IRQ except if MASK\_BUCK2\_IRQ is set.

- OV detection to monitor the output voltage (flag is BUCK2\_OV bit). Buck2 is therefore switched off after tbuck2\_OV\_TO. Status register bit BUCK2\_OV must be read and cleared before switching ON the regulator via the SPI bit VBUCK2\_ENA to allow a proper start-up (only when Buck2 is not critical for the MCU).

- Overvoltage detection generates an IRQ except if MASK\_BUCK2\_IRQ is set.

- Power-good detection is used to signal Buck power-on success (flag is BUCK2\_PG\_OK bit) and IRQ is generated except if MASK\_BUCK2\_PG\_IRQ is set.

- If not, after TBUCK2 PG TO timeout, Buck2 is switched off and the flag BUCK2 PG TIMEOUT is set.

- Unsuccessful power-good detection generates an IRQ except if MASK\_BUCK2\_PG\_TIMEOUT\_IRQ is set.

- Configurable overcurrent protection through U-NVM BUCK2\_IPEAK (flag is BUCK2\_OC bit). Buck2 is therefore switched off after tbuck2\_OC\_TO except if MASK\_BUCK2\_OC\_POWER\_OFF is set.

- Overcurrent detection generates an IRQ except if MASK\_BUCK2\_OC\_IRQ is set.

- Warning temperature detection by a local thermal sensor (flag is TW CL2).

- Warning temperature detection generates an IRQ except if MASK\_CL2\_TW\_IRQ is set.

- Overtemperature detection by local thermal sensor (flag is TSD\_CL2, see also Section 4.7) and buck2 is switched off.

- Buck2 internal regulators detection (flag is BUCK2\_INT\_FAIL). Buck2 is switched off.

- Internal fail generates an IRQ except if MASK\_BUCK2\_IRQ is set.

- Buck2 feedback (FB2) pin disconnection (flag is BUCK2 FBLOSS). Buck2 is switched off.

- FB2 pin disconnection generates an IRQ except if MASK\_BUCK2\_IRQ is set.

- After a fault detection (UV, OV, OC, FBLOSS, TSD\_CL2 or PG timeout), Buck2 can be re-enabled by setting BUCK2\_ENA = 0, followed by BUCK2\_ENA=1.

In active low-power, the Buck2 converter provides the following diagnostics:

- UV detection to monitor the output voltage (flag is BUCK2\_UV). Buck2 is therefore switched off except if SPI bit MASK\_BUCK2\_UV\_POWER\_OFF is set.

- Undervoltage detection generates an IRQ except if MASK\_BUCK2\_IRQ is set.

- OV detection to monitor the output voltage (flag is BUCK2\_OV bit) Buck2 is therefore switched off.

- Overvoltage detection generates an IRQ except if MASK\_BUCK2\_IRQ is set.

- Overcurrent protection (flag is BUCK2\_OC bit). Buck2 is therefore switched off except if MASK\_BUCK2\_OC\_POWER\_OFF is set.

- Overcurrent detection generates an IRQ except if MASK BUCK2 OC IRQ is set.

- Buck2 feedback (FB2) pin disconnection (flag is BUCK2\_UV). Buck2 is switched off.

- FB2 pin disconnection generates an IRQ except if MASK\_BUCK2\_IRQ is set.

- Overtemperature detection by the central thermal sensor (flag is TSD\_CL0, see also Section 4.7) and device power-down sequence is executed.

DS14964 - Rev 1 page 22/239

In ACTIVE and REC-1 states, when BUCK2\_REGFAIL\_GO\_REC is set at 1 in the USER-NVM, in case of PG timeout, OV, UV, INT\_FAIL, OC, FBLOSS or TSD events, the device executes a power-down sequence, enters REC-2 state and makes an automatic retry. PG\_TIMEOUT, OV, UV, OC, INT\_FAIL, FBLOSS or TSD flags are not blocking a re-enable of the BUCK2.

It is not recommended to use MASK\_BUCK2\_OC\_POWER\_OFF and MASK\_BUCK2\_UV\_POWER\_OFF at the same time.

#### 3.3.3 Buck3 converter

The Buck3 is a post-regulator and needs to be supplied by Buck1 or Buck2 through the VIN3 pin.

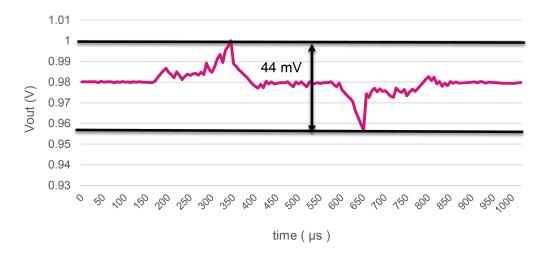

The Buck3 converter is similar to the Buck1 but with double current capability. Moreover, if the output voltage is configured at 0.98 V, a further SPI fine-tuning in steps of 10 mV is available (BUCK3\_FTUNE[2:0] control bits), covering a range from 0.95 V to 1.01 V.

Output voltages are programmable via the USER -NVM through the bit BUCK3 PU VALUE.

The spread-spectrum feature is configurable via the SPI bit BUCK3\_SPREAD\_ENA (disabled by default).

To limit emission in the audio bandwidth, refresh frequency can be forced at 25 kHz by USER-NVM bit BUCK3\_REFRESH\_FREQ set low (1 kHz when high).

Buck3 can be disabled via the SPI bit VBUCK3\_ENA (only after SPI\_PROTECT\_ACCESS has been set). Buck3 must be disabled before entering active low-power mode and must not be enabled in this mode.

The live bit VBUCK3 ENA STATUS reflects the state of BUCK3 output.

Note that after the first power-up, the control bit VBUCK3\_ENA needs to be aligned with live bit VBUCK3\_ENA\_STATUS.

The Buck3 converter provides the following diagnostics:

- UV detection to monitor the output voltage (flag is BUCK3\_UV). Buck3 is therefore switched off after tbuck3\_UV\_TO except if SPI bit MASK\_BUCK3\_UV\_POWER\_OFF is set

- Undervoltage detection generates an IRQ except if MASK\_BUCK3\_IRQ is set

- OV detection to monitor the output voltage (flag is BUCK3\_OV bit). Buck3 is therefore switched off after tbuck3\_OV\_TO. Status register bit BUCK3\_OV must be read and cleared before switching ON the regulator via the SPI bit VBUCK3\_ENA to allow a proper start-up (only when Buck3 is not critical for the MCU).

- Overvoltage detection generates an IRQ except if MASK\_BUCK3\_IRQ is set.

- Power-good detection is used to signal Buck power-on success (flag is BUCK3\_PG\_OK bit) and IRQ is generated except if MASK\_BUCK3\_PG\_IRQ is set.

- If not, after TBUCK3 PG TO timeout, Buck3 is switched off and the flag BUCK3 PG TIMEOUT is set.

- Unsuccessful power-good detection generates an IRQ except if MASK BUCK3 PG TIMEOUT IRQ is set.

- Configurable overcurrent protection through U-NVM BUCK3\_IPEAK (flag is BUCK3\_OC bit). Buck3 is therefore switched off after tbuck3\_OC\_TO except if MASK\_BUCK3\_OC\_POWER\_OFF is set.

- Overcurrent detection generates an IRQ except if MASK\_BUCK3\_OC\_IRQ.

- Warning temperature detection by a local thermal sensor(flag is TW\_CL3).

- Warning temperature detection generates an IRQ except if MASK\_CL3\_TW\_IRQ is set.

- Overtemperature detection by a local thermal sensor (flag is TSD\_CL3, see also Section 4.7) and Buck3 is switched off.

- Buck3 internal regulators detection (flag is BUCK3\_INT\_FAIL). Buck3 is switched off.

- Internal fail generates an IRQ except if MASK\_BUCK3\_IRQ is set.

- After a fault detection (UV, OV, OC, INT\_FAIL, TSD\_CL3 or PG timeout), Buck3 can be re-enabled by setting BUCK3 ENA = 0, followed by BUCK3 ENA=1.

- In ACTIVE and REC-1 states, when BUCK3\_REGFAIL\_GO\_REC is set at 1 in the USER-NVM, in case of PG timeout, OV, UV, OC, INT\_FAIL or TSD events, the device executes a power-down sequence, enters REC-2 state and makes an automatic retry. PG\_TIMEOUT, OV, UV, OC, INT\_FAIL or TSD flags are not blocking a re-enable of the BUCK3.

It is not recommended to use MASK\_BUCK3\_OC\_POWER\_OFF and MASK\_BUCK3\_UV\_POWER\_OFF at the same time.

DS14964 - Rev 1 page 23/239

# 3.4 Linear voltage regulators

#### 3.4.1 LDO1

The LDO1 is dedicated to supplying the CAN-FD in ACTIVE state or to supplying external loads (only for the SPSB100GB). It is supplied by the FBB pin. LDO1 has a 5 V output and a 120 mA current capability.

It can be enabled/disabled through the LDO1\_ENA control bit (only after SPI\_PROTECT\_ACCESS has been set).

The voltage regulator is protected against undervoltage (flag is LDO1 UV) and LDO1 is therefore switched off.

The undervoltage detection generates an IRQ except if it is masked with MASK LDO1 IRQ.

The live bit LDO1\_ENA\_STATUS reflects the state of LDO1 output.

Note:

Note that, after the first-power up, it is necessary the control bit LDO1\_ENA needs to be aligned with live bit LDO1\_ENA\_STATUS.

- Power-good is used to signal LDO1 power-on success (flag is LDO1\_PG\_OK bit).

- If not, after T<sub>LDO1 PG TO</sub> timeout, LDO1 is switched off and flag LDO1\_PG\_TIMEOUT is set.

- Power-on success generates an IRQ except if it is masked with MASK\_LDO1\_PG\_IRQ.

- Unsuccessful power-good detection generates an IRQ except if MASK\_LDO1\_PG\_TIMEOUT\_IRQ is set.

- After a fault detection (UV or PG timeout), LDO1 can be re-enabled by setting LDO1\_ENA = 0, followed by LDO1\_ENA=1, Fail flags are not blocking to re-enable the LDO1.

The output voltage is stable for ceramic load capacitors  $C_{LDO1}$  > 1  $\mu F$ .

Warning temperature detection by a local thermal sensor (flag is TW\_CL0).

Warning temperature detection generates an IRQ except if MASK\_CL0\_TW\_IRQ is set.

In case the device temperature exceeds the TSD\_CL0 threshold, the device executes a power-down sequence before entering REC-2 state.

#### 3.4.2 LDO2

The SPSB100G embeds one low-dropout tracking regulator designed to provide an output voltage that closely tracks the bucks' reference at +/-10 mV while delivering up to 10 mA on the LDO2 output pin. The LDO2 voltage tracker is supplied by the FBB pin.

The LDO2\_ENA SPI bit is used to enable/disable this LDO (only after SPI\_PROTECT\_ACCESS has been set). LDO2 must be disabled before entering ACTIVE low-power mode, and must not be enabled in this mode.

LDO2 can be configured by means of the USER-NVM LDO2\_TRK bits to track one of Buck1, Buck2 or Buck3, if related output voltages are 5 V or 3.3 V (see Table 6).

| Tracking configuration | LDO2_TRK[0,1] USER-<br>NVM configuration bits | Selected voltage source | Source output voltage | LDO2 behavior          |

|------------------------|-----------------------------------------------|-------------------------|-----------------------|------------------------|

| 4                      | 00                                            | Buck1                   | 3.3 V or 5 V          | Tracks Buck1           |

| 1                      | 00                                            | Bucki                   | 6.5 V                 | OFF what ever LDO2_ENA |

| 2                      | 01                                            | Buck2                   | 3.3 V or 5 V          | Tracks Buck2           |

| 2                      | 01                                            | Buckz                   | 6.5 V                 | OFF what ever LDO2_ENA |

| 3                      | 1x                                            | Buck3                   | 0.98 V - 1.25 V       | OFF what ever LDO2_ENA |

| 3                      | IX.                                           | Bucks                   | 3.3 V                 | Tracks Buck3           |

Table 6. Voltage regulators configuration

LDO2 is supplied by the FBB pin.

The tracking regulator provides the following diagnostics:

The live bit LDO2\_ENA\_STATUS reflects the state of LDO2 output.

Note:

Note that, after the first-power up, it is necessary the control bit LDO2\_ENA needs to be aligned with live bit LDO2\_ENA\_STATUS.

DS14964 - Rev 1 page 24/239

- Overvoltage detection to monitor the output voltage (flag is LDO2\_OV bit) and LDO2 is therefore switched

off.

- Overvoltage detection generates an IRQ except if MASK\_LDO2\_IRQ is set.

- Undervoltage detection (flag is LDO2\_UV bit) and LDO2 is therefore switched off.

- Undervoltage detection generates an IRQ except if MASK\_LDO2\_IRQ is set.

- Power-good is used to signal LDO2 power-on success (flag is LDO2 PG OK bit).

- If not, after T<sub>LDO2 PG TO</sub> timeout, LDO2 is switched off and flag LDO2\_PG\_TIMEOUT is set.

- The power-on success generates an IRQ, except if it is masked with MASK LDO2 PG IRQ.

- Unsuccessful power-good detection generates an IRQ except if MASK LDO2 PG TIMEOUT IRQ is set.

- Warning temperature detection by a local thermal sensor (flag is TW\_CL4).

- Warning temperature detection generates an IRQ except if MASK\_CL4\_TW\_IRQ is set.

- Overtemperature detection by a local thermal sensor (flag is TSD\_CL4, see also Section 4.7) and LDO2 is switched off.

- After a fault detection (UV, OV, TSD\_CL4 or PG timeout), LDO2 can be re-enabled by setting LDO2\_ENA =

0, followed by LDO2\_ENA=1, Fail flags are not blocking to re-enable the LDO2.

- LDO2 is switched off if a fault on the tracked regulator is detected.

- In active and REC-1 states, when LDO2\_REGFAIL\_GO\_REC is set at 1 in the USER-NVM, in case of PG

timeout, OV, UV, or TSD events, the device executes a power-down sequence, enters REC-2 state, and

makes an automatic retry.

# 3.5 Operating modes

The device can work in a normal operation mode (ACTIVE state - FULL-POWER mode) or in a reduced operation mode (ACTIVE state - LOW-POWER mode).

The transition between FULL-POWER and LOW-POWER mode is managed via an SPI command (LOW POWER SET control bit, only after SPI PROTECT ACCESS has been set).

In ACTIVE state, the device is fully controllable and configurable through the SPI.

Moreover, a DEEP-SLEEP state is available in order to minimize current consumption during not-operating time frames via the SPI command DO\_POWER\_DOWN (only after SPI\_PROTECT\_ACCESS has been set). Status bits DEEP-SLEEP\_FROM\_DO\_POWER\_DOWN will be set at "01" if transitioning from ACTIVE state, or "1x" if transition from REC-1 state.

DEEP-SLEEP\_FROM\_DO\_POWER\_DOWN can be cleared via the CLR\_DEEP\_SLEEP\_FROM\_DO\_POWER\_DOWN bit.

DS14964 - Rev 1 page 25/239

The table below shows the availability and operational behavior of regulators and functions across different operating modes. In some modes, a regulator can be actively turned ON or OFF, allowing dynamic control. In other modes, the regulator remains permanently OFF and cannot be enabled.

Table 7. Regulators and functions availability by operating modes

| Regulators         | FULL-POWER | LOW-POWER  | DEEP-SLEEP |

|--------------------|------------|------------|------------|

| BOOST              | ON/OFF (1) | ON/OFF (1) | OFF        |

| Buck 1             | ON/OFF (2) | ON/OFF (3) | OFF        |

| Buck 2             | ON/OFF (2) | ON/OFF (3) | OFF        |

| Buck 3             | ON/OFF (2) | OFF        | OFF        |

| LDO 1              | ON/OFF (2) | ON/OFF (3) | OFF        |

| LDO 2              | ON/OFF (2) | OFF        | OFF        |

| Wake up mechanisms | FULL-POWER | LOW-POWER  | DEEP-SLEEP |

| WU, IGN            | ON/OFF (3) | ON/OFF (3) | ON/OFF (3) |

| LDT                | ON/OFF (3) | ON/OFF (3) | ON/OFF (3) |

| CAN                | ON/OFF (3) | ON/OFF (3) | ON/OFF (3) |

| OUT_HS cyclic      | ON/OFF (3) | ON/OFF (3) | ON/OFF (3) |

| Others             | FULL-POWER | LOW-POWER  | DEEP-SLEEP |

| NFSO               | ON/OFF (3) | ON/OFF (3) | OFF (4)    |

| NRST               | ON         | ON         | OFF        |

| IRQ                | ON         | ON         | OFF        |

| FCCU               | ON/OFF (3) | OFF        | OFF        |

| CAN FD             | ON/OFF (3) | ON/OFF (3) | OFF        |

| OUT_HS             | ON/OFF (3) | ON/OFF (3) | ON/OFF (3) |

| ADC                | ON         | OFF        | OFF        |

| TSDC               | ON         | ON         | OFF        |

| TSD                | ON         | OFF        | OFF        |

| SPI                | ON         | ON         | ON/OFF     |

| Watchdog           | ON/OFF (5) | ON/OFF (3) | OFF        |

| BYPASS             | ON/OFF (1) | OFF        | OFF        |

- 1. ON/OFF depends on battery voltage level. Can be set OFF by NVM/SPI.

- 2. ON if included in the Power-ON sequence by NVM or by SPI programming.

- 3. SPI programmable.

- 4. Can be set High or low by NVM.

- 5. ON/OFF by NVM.

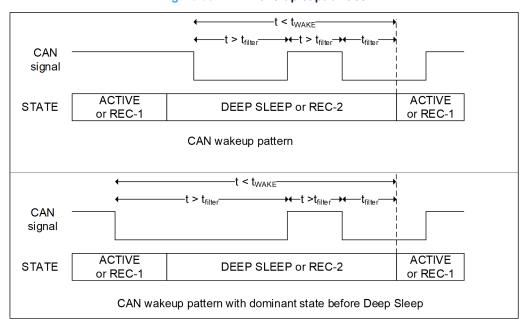

# 3.5.1 Wake-up from DEEP-SLEEP to ACTIVE state

A wake-up from DEEP-SLEEP state will transit the device to the INIT state, as described in Section 3.6.3

To avoid disabling all wake-up capability, a hard protection is implemented: the SPI writing to disable the last wake-up possibility defined in Table 8 is not taken into account and a status register bit SPI\_ALL\_WAKEUP\_DISABLE is set, and generates an IRQ except if MASK\_SPI\_ERROR\_IRQ is set.

Current consumption in DEEP-SLEEP mode is calculated as  $I_{VS\_DP}$  + wake-up current consumption contributions.

This can be initiated by one or more of the following events:

DS14964 - Rev 1 page 26/239

| Wake up source                | Description                                                    | Flag       |

|-------------------------------|----------------------------------------------------------------|------------|

| CAN bus activity              | Can be configured by SPI (CAN_WU_ENA bit)                      | CAN_WAKE   |

| Level change of wake-up (WU)  | Can be configured by SPI (WU_ENA bit)                          | WU_WAKE    |

| Level change of wake-up (IGN) | Can be configured by SPI (IGN_ENA bit)                         | IGN_WAKE   |

| Cyclic monitoring (WU)        | Can be configured by SPI (WU_FILT bit with TIMER_ENA=1)        | WU_WAKE    |

| Cyclic monitoring (IGN)       | Can be configured by SPI (IGN_FILT bit with TIMER_ENA=1)       | IGN_WAKE   |

| Timer                         | Can be configured by SPI (TIMER_WAKE_ENA bit with TIMER_ENA=1) | TIMER_WAKE |

| Long duration timer           | Can be configured by SPI (LDT_MODE bit with LDT_ENA=1)         | LDT_WAKE   |

Table 8. Wake up events description

#### 3.5.2 Wake-up events in ACTIVE mode

All enabled wake-up events described in Table 8 in ACTIVE mode are signaled to the microcontroller by an interrupt request on the IRQ pin.

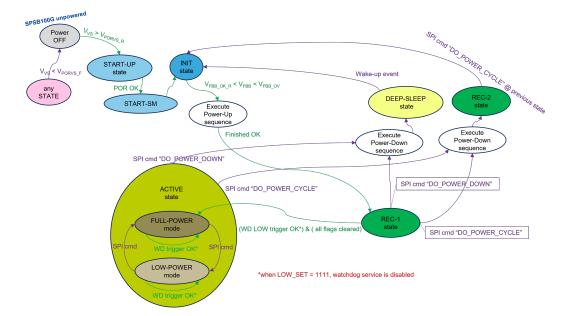

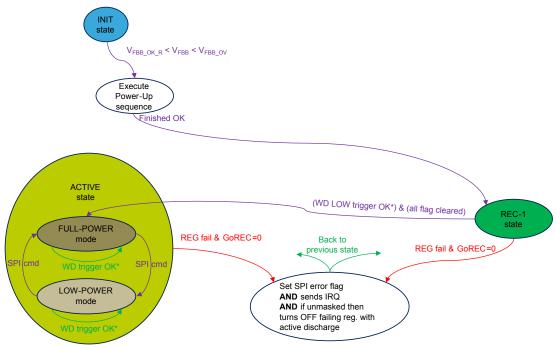

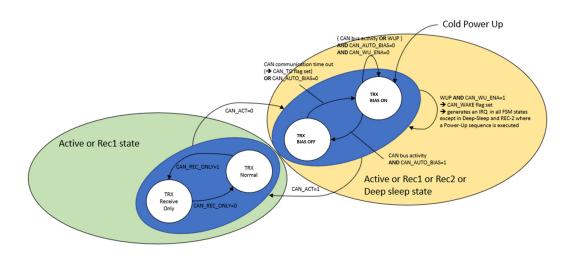

#### 3.6 Functional overview - state machine

To make the reading easier, the state machine description has been split into three parts. First, the state diagram is presented with the normal transitions (Chapter Section 3.6.1), then transitions resulting in a fault event detection are shown (Chapter Section 3.6.2), and finally the full state machine is described and states and transitions detailed (Chapter Section 3.6.3).

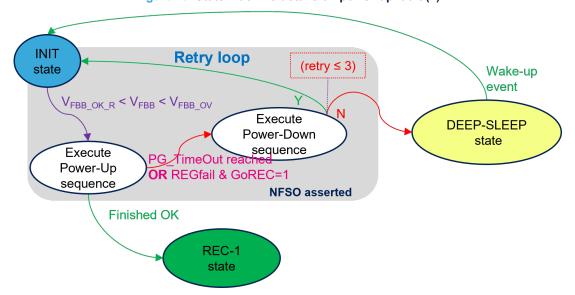

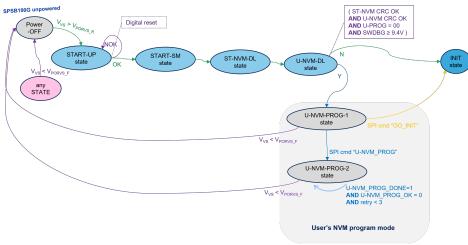

# 3.6.1 State machine without fault transitions

Figure 17. State machine without fault transitions

Until the voltage on the VS pin reaches  $V_{PORVS\_R}$  for the first time, the device is in POWER-OFF state. After that, the device transitions to the START-UP state, where internal power supplies are established. Then, a core logic reset is released and the START-SM state is reached, where oscillators start and the NVM is read and checked. Refer to Chapter Section 3.8 for details on the USER-NVM space programming.

DS14964 - Rev 1 page 27/239

After start-up completion, the device reaches the INIT state, where a digital BIST is ran, and when the FBB voltage reaches V<sub>FBB\_OK\_R</sub>, the device executes a power-up sequence, which turns ON all regulators as per application requirements stored in the USER-NVM space. The sequence includes the NRST pin deassertion to high level and, at the same time, the start of the watchdog long open window. See the power-up sequence description in Section 3.7.1 for details. After the power-up sequence, the device enters the RECOVERY-1 state: The SPSB100G is waiting for the MCU to boot up and trig the watchdog, except if LOW\_SET[3:0] = 1111, before expiration of the watchdog long open window timeout. After a valid trig of the watchdog during its long open window timeout, the device enters ACTIVE state in FULL-POWER mode. In the ACTIVE state, the device is fully controllable by SPI. The MCU can configure SPSB100G features as per application needs to optimize ECU performances and global power consumption. In particular, some regulators can be switched OFF by SPI and the SPSB100G can be set to LOW-POWER mode, to reduce ECU power consumption while delivering the strict minimum power supply and supervision to the MCU. Later, the MCU can reconfigure the SPSB100G in FULL-POWER mode by SPI.

In ACTIVE state, the MCU can also request a power cycle from the SPSB100G: a power-down sequence is then executed, followed by digital BIST in INIT state, before executing a power-up sequence. In ACTIVE state, the MCU can also request a power-down from the SPSB100G: a power-down sequence is then executed, and DEEP-SLEEP state is reached. It is left upon a wake-up event. Wake-up event sensitivity is programmable by SPI in ACTIVE state, and includes cyclic sensing of the WU pin with cyclic powering of OUT\_HS, edge and level detection on IGN, and CAN wake-up frame detection.

#### 3.6.2 State machine focusing on fault transitions

#### 3.6.2.1 NVM fault management

NVM fault management is explained in Section 3.8.1.

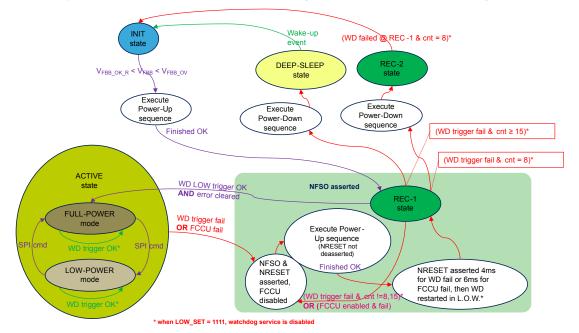

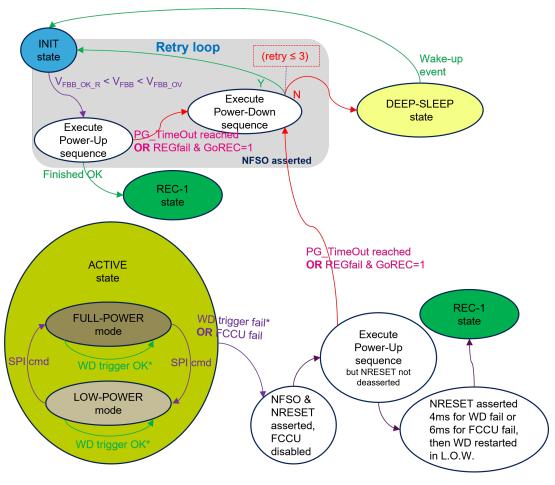

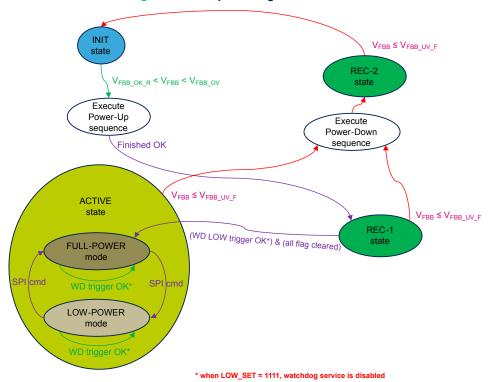

#### 3.6.2.2 Watchdog trig and FCCU monitor fault management

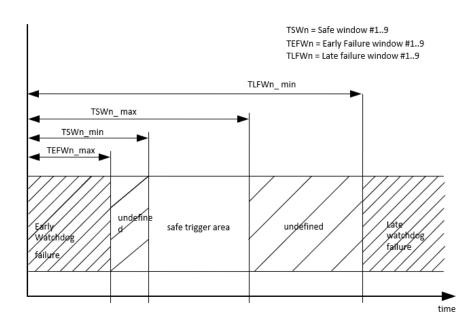

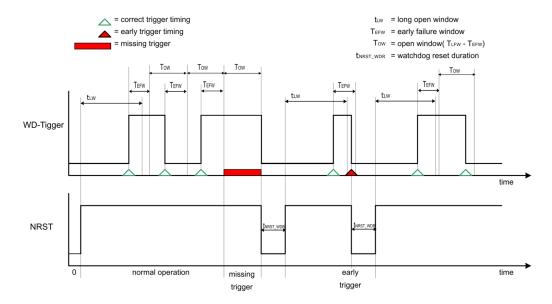

The watchdog is launched during the power-up sequence when the NRST pin is deasserted high, starting with a long open window timeout. After the power-up sequence, the SPSB100G reaches RECOVERY-1 state, which is dedicated to watchdog and FCCU monitor fault management.

Figure 18. State machine details with WD trig and FCCU monitor fault management

While in RECOVERY-1 state, a read and clear of error flags and a proper trig of the watchdog in long open window timeout initiates a transition to ACTIVE state.

If the watchdog is triggered without clearing all flags, then the device remains in RECOVERY-1 state and the watchdog runs with normal window timings.

DS14964 - Rev 1 page 28/239

In ACTIVE state, the watchdog runs with normal window timings. Proper trig of the watchdog maintains the SPSB100G in ACTIVE state, while a failure in the watchdog service or a fault detected on the FCCU monitor will:

- increment the watchdog trig fault counter (only on watchdog trig fault)

- assert NRST pin low

- disable and reset the FCCU monitor

- initiate a power-up sequence: This is mandatory to power regulators that may have been switched off by SPI back up.

- disable the BYPASS external MOSFET

Then, the NRST pin remains asserted for 4 ms at least (in case of watchdog trig fault), or 6 ms at least (in case of FCCU monitor fault). Before being released, the watchdog starts a long open window timeout and the SPSB100G reaches RECOVERY-1 state.

In case of successive faults in servicing the watchdog in long open window, the watchdog trig fault counter is incremented, a power-up sequence is run, a 4 ms NRST pulse is generated, and a long open window timeout is restarted.

If the watchdog is properly served during the long open window, then the watchdog trig fault counter is reset and the SPSB100G enters ACTIVE state.

8 successive watchdog trig faults will force the SPSB100G to initiate a power cycle through the RECOVERY-2 and INIT states. In case of 15 successive watchdog trig faults, the SPSB100G enters DEEP-SLEEP state.

The FCCU monitor is disabled and its configuration reset after the first watchdog trig fault. The FCCU monitor can be reconfigured and enabled through SPI in RECOVERY-1 or ACTIVE state.

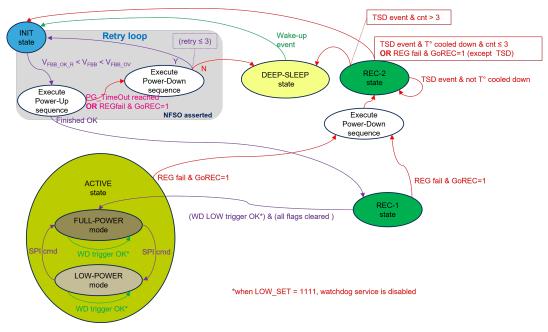

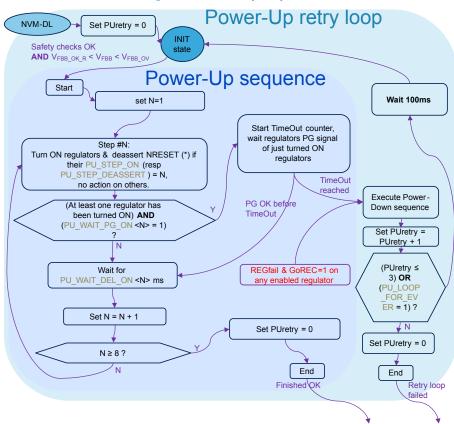

#### 3.6.2.3 Power-up fault management

The power-up sequence can be programmed to wait for the power-good signal of any of the turned-on regulators (see the power-up sequence description in Section 3.7.1 for details). In such a case, a timeout counter is run. It is longer than the maximum rising time of the SPSB100G regulators.

If the timeout elapses, the SPSB100G executes a power-down sequence, the power-up retry counter POWUP\_RETRY\_CNT is incremented, and the SPSB100G retries 4 times to power up the regulators (POWUP\_RETRY\_CNT counter can be cleared by CLR\_POWUP\_RETRY\_COUNT bit ). If 4 successive faults occur and the PU\_LOOP\_FOR\_EVER bit is not set, then the SPSB100G enters DEEP-SLEEP state, clears the POWUP\_RETRY\_CNT and generates a status register flag FORCED\_SLEEP\_POWUP. If PU\_LOOP\_FOR\_EVER bit is set, the SPSB100G will retry to power up forever.

The same retry loop applies if a fault on a regulator is detected during the power-up sequence, and the regulator has its REGFAIL GO REC configuration bit set to 1. See Section 3.6.2.5 for details.

Figure 19. State machine details on power-up fault (1)

The behavior is similar if the power-up sequence timeout is reached when the sequence is executed after a watchdog trig fault or an FCCU monitor fault detection as shown in the following figure.

DS14964 - Rev 1 page 29/239

Figure 20. State machine details on power-up fault (2)

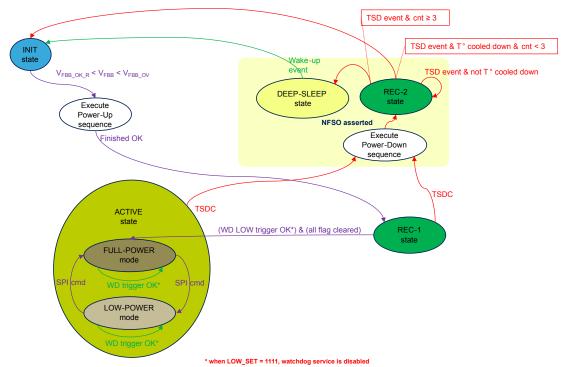

# 3.6.2.4 Central thermal sensor fault management

The central thermal sensor plays a major role in protecting the whole device. This sensor is monitoring the temperature of the SPSB100G core. If the SPSB100G core temperature exceeds the TSDC threshold, a power-down sequence is run, and the SPSB100G enters RECOVERY-2 state.

In RECOVERY-2 state, all regulators are OFF and the TSD event counter TSD\_CNT\_FAIL is incremented. After the temperature cools down, if TSD\_CNT\_FAIL is less than 3, then SPSB100G transits to INIT state and initiates a power-up sequence. If not, then the SPSB100G transitions to DEEP-SLEEP state until a wake-up event and generates a status register flag FORCED\_SLEEP\_TSD.

The TSD event counter, TSD\_CNT\_FAIL, is readable via the SPI and can be cleared by CLR\_TSD\_CNT\_FAIL bit. This counter is incremented after a TSD event on any of the clusters.

DS14964 - Rev 1 page 30/239

Figure 21. State machine details on TSDC fault

# 3.6.2.5 Regulator fault management

Each SPSB100G regulator has the following monitors:

- Temperature sensor with a warning threshold (TW) and a shut-down threshold (TSD)

- Undervoltage comparator (UV)

- Overvoltage comparator (OV) except for LDO1

- Power-good comparator (PG\_TIMEOUT)

- Overcurrent comparator (OC) on Bucks

- Internal regulator comparator (INT\_FAIL) on Bucks

- FB pin disconnection (FBLOSS for Buck1 and Buck2)

The user can decide how the SPSB100G shall react on an event of those monitors. This is done through the USER-NVM bit REGFAIL GO REC for each of them.

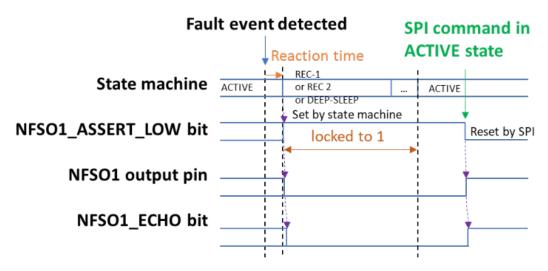

A TW event sets the associated flag and generate an interruption, while the reaction to a TSD, UV, PG\_TIMEOUT, OC, INT\_FAIL, FBLOSS and OV event depends on the regulator REGFAIL\_GO\_REC bit.