## Rad-hard plastic Dual D-type positive edge-triggered flip-flop

#### **Features**

- Dual D-type positive edge-triggered flip-flop

- 1.65 V to 6 V operating supply

- 7 V max. rating

- 8.5 ns propagation delay

- Nickel/Palladium/Gold-lead-finished (NiPdAu), whisker-free

- Gold-wires

- RML <1% and CVCM <0.1% guaranteed outgassing</li>

- 50 krad (Si) Total Ionizing Dose

- SEL-free up to 62.5 MeV.cm²/mg

- Mass: 80 mg

- Compliant with ST-LEO-specification

#### **Maturity status link**

LEOAC74

### **Applications**

· Low earth orbit (LEO) applications

### **Description**

The LEOAC74 is a CMOS Dual D-type positive edge-triggered flip-flop for use in aerospace environments. It operates from 1.65 V to 6 V power supply (7 V absolute maximum rating).

The LEOAC74 can operate over a large temperature range of -40 °C to +125 °C and it is housed in plastic TSSOP-20, Thin-Shrink Small Outline Package, 20 leads, using golden bonding and Nickel/Palladium/Golden-lead-finishing to prevent whiskers.

The LEOAC74 is compliant with ST-LEO-specification, dedicated specification for space-ready rad-hard plastic products. This AEC-Q100-based specification offers a specific trade-off between footprint size savings, cost of ownership and quality assurance together with radiation hardness and large quantity capability.

# 1 Functional description

CD1 1 2 20 VCC

D1 2 19 CD2

CP1 3 18 D2

SD1 4 17 CP2

Q1 5 16 SD2

Q1 6 15 Q2

NC 7 14 Q2

Figure 1. Pin connections (top view)

NC: not internally connected.

NC 8

NC 9

GND 10

13 NC

12 NC

11 NC

The pin can be externally connected to any potential.

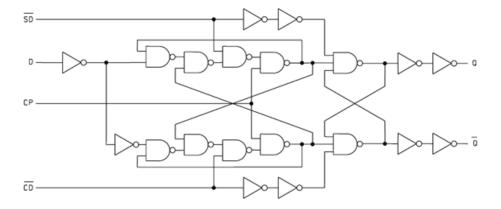

Figure 2. Equivalent schematic

DS13861 - Rev 3 page 2/19

Table 1. Truth table for each flip-flop

|     | INP | UTS             |   | OUTI             | PUTS             |

|-----|-----|-----------------|---|------------------|------------------|

| /SD | /CD | СР              | D | Q                | /Q               |

| L   | Н   | X               | X | Н                | L                |

| Н   | L   | X               | X | L                | Н                |

| L   | L   | X               | X | H <sup>(1)</sup> | H <sup>(1)</sup> |

| Н   | Н   | Rise clock edge | Н | Н                | L                |

| Н   | Н   | Rise clock edge | L | L                | Н                |

| Н   | Н   | L               | X | Q0               | /Q0              |

<sup>1.</sup> This configuration is unstable; that is, it does not persist when either SD or CD returns to its inactive (high) level.

H = High voltage level.

L = Low voltage level.

X = Don't care.

Q0 (or /Q0) = Previous Q (or /Q) before low to high transition of clock.

DS13861 - Rev 3 page 3/19

<sup>\* =</sup> This configuration is unstable; that is, it does not persist when either SD or CD returns to its inactive (high) level.

## 2 Maximum ratings and operating conditions

Table 2. Absolute maximum ratings

| Symbol                         | Parameter                                            | Value                                        | Unit |

|--------------------------------|------------------------------------------------------|----------------------------------------------|------|

| V <sub>CC</sub> (1)            | Maximum power supply between V <sub>CC</sub> and GND | -0.5 to 7                                    | V    |

| V <sub>IN</sub>                | DC input voltage range                               | -0.5 to V <sub>CC</sub> +0.5 (and 7 V max.)  | V    |

| V <sub>OUT</sub>               | DC output voltage range                              | -0.5 to V <sub>CC</sub> + 0.5 (and 7 V max.) | V    |

| I <sub>K</sub>                 | I/O clamp diode current                              | +/-20                                        | mA   |

| T <sub>stg</sub>               | Maximum temperature storage                          | -65 to +150                                  | °C   |

| T <sub>j</sub> (2)             | Maximum junction temperature                         | +150                                         | °C   |

| R <sub>th</sub> <sup>(3)</sup> | Junction to ambient thermal resistance (Θja)         | 80                                           | °C/W |

| r\th (³)                       | Junction to case thermal resistance (Ojc)            | 17                                           | °C/W |

| ESD                            | HBM (human body model)                               | 2k                                           | V    |

- 1. All voltages, except differential I/O bus voltage, are with respect to the network ground terminal.

- 2. Maximum junction temperature shall not be exceeded except for allowable short duration burn-in screening conditions as per the method 5004 of MIL-STD-883.

- 3. Short-circuits can cause excessive heating. Destructive dissipation can result from short-circuits on the amplifiers.

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All values are referred to GND.

**Table 3. Operating conditions**

| Symbol           | Parameter                 | Min. | Max.            | Unit |

|------------------|---------------------------|------|-----------------|------|

| V <sub>CC</sub>  | Analog supply voltage     | 1.65 | 6               | V    |

| V <sub>IN</sub>  | Input voltage range       | 0    | V <sub>CC</sub> | V    |

| V <sub>OUT</sub> | Output voltage range      | 0    | V <sub>CC</sub> | V    |

| Та               | Ambient temperature range | -40  | +125            | °C   |

Note: All unused inputs must be held at VCC or GND to ensure proper device operation.

DS13861 - Rev 3 page 4/19

## 3 Electrical characteristics

$V_{CC}$  = 3 V to 5.5 V, typical values are at ambient Ta = +25 °C, min. and max. values are at Ta = -40 °C and +125 °C, unless otherwise specified.

Table 4. Electrical characteristics.

| Symbol                         | Parameter                 | Test condition                                                                                                                                               | VCC<br>(V) | Min. | Тур. | Max.                                                | Unit |

|--------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|-----------------------------------------------------|------|

|                                |                           | For all inputs affecting output under test, V <sub>IN</sub> = V <sub>IH</sub>                                                                                | 3          | 2.9  |      |                                                     |      |

|                                |                           | minimum or V <sub>IL</sub> maximum. For all other inputs,                                                                                                    |            | 4.4  |      |                                                     |      |

|                                |                           | $V_{IN} = V_{CC}$ or GND, $I_{OH} = -50 \mu A$                                                                                                               | 5.5        | 5.4  |      |                                                     |      |

|                                |                           | For all inputs affecting output under test, $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum. For all other inputs,                                             | 3          | 2.4  |      |                                                     |      |

| V <sub>OH</sub> <sup>(1)</sup> | High level output voltage | $V_{IN} = V_{CC}$ or GND, $I_{OH} = -12$ mA                                                                                                                  |            |      |      |                                                     | V    |

| 1011                           | g toro: ca.pat ronago     | For all inputs affecting output under test, $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum. For all other inputs,                                             | 4.5        | 3.7  |      |                                                     |      |

|                                |                           | V <sub>IN</sub> = V <sub>CC</sub> or GND, I <sub>OH</sub> = -24 mA                                                                                           | 5.5        | 4.7  |      |                                                     |      |

|                                |                           | For all inputs affecting output under test, $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum. For all other inputs, $V_{IN} = V_{CC}$ or GND $I_{OH} = -50$ mA  | 5.5        | 3.85 |      | 0.1<br>0.1<br>0.1<br>0.1<br>0.5<br>V<br>0.5<br>1.65 |      |

|                                |                           |                                                                                                                                                              | 3          |      |      | 0.1                                                 |      |

|                                |                           | For all inputs affecting output under test, $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum. For all other inputs,                                             | 4.5        |      |      | 0.1<br>0.1<br>0.1<br>0.5<br>V<br>0.5<br>1.65        |      |

|                                |                           | $V_{IN} = V_{CC}$ or GND, $I_{OL} = +50 \mu A$                                                                                                               | 5.5        |      |      |                                                     |      |

|                                |                           | For all inputs affecting output under test, $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum. For all other inputs,                                             |            |      |      |                                                     |      |

| V <sub>OL</sub> (1)            | Low level output voltage  | V <sub>IN</sub> = V <sub>CC</sub> or GND, I <sub>OL</sub> = +12 mA                                                                                           | 3          |      |      | 0.5                                                 | V    |

| OL .                           |                           | For all inputs affecting output under test, $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum. For all other inputs,                                             | 4.5        |      |      | 0.5                                                 |      |

|                                |                           | V <sub>IN</sub> = V <sub>CC</sub> or GND, I <sub>OL</sub> = +24 mA                                                                                           | 5.5        |      |      |                                                     |      |

|                                |                           | For all inputs affecting output under test, $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum. For all other inputs, $V_{IN} = V_{CC}$ or GND, $I_{OL} = +50$ mA | 5.5        |      |      |                                                     |      |

|                                |                           |                                                                                                                                                              | 3          | -12  |      |                                                     |      |

| I <sub>OH</sub>                | High level output current |                                                                                                                                                              | 4.5        | -24  |      |                                                     |      |

|                                |                           |                                                                                                                                                              | 5.5        | -24  |      |                                                     |      |

|                                |                           |                                                                                                                                                              | 3          |      |      | 12                                                  | mA   |

| I <sub>OL</sub>                | Low level output current  |                                                                                                                                                              | 4.5        |      |      | 24                                                  |      |

|                                |                           |                                                                                                                                                              | 5.5        |      |      | 24                                                  |      |

|                                |                           |                                                                                                                                                              | 3          | 2.1  |      |                                                     |      |

| V <sub>IH</sub> (2)            | High level input voltage  |                                                                                                                                                              | 4.5        | 3.15 |      |                                                     | mA   |

|                                |                           |                                                                                                                                                              | 5.5        | 3.85 |      |                                                     |      |

|                                |                           |                                                                                                                                                              | 3          |      |      | 0.9                                                 |      |

| V <sub>IL</sub> <sup>(2)</sup> | Low level input voltage   |                                                                                                                                                              | 4.5        |      |      | 1.35                                                | V    |

|                                |                           |                                                                                                                                                              | 5.5        |      |      | 1.65                                                |      |

DS13861 - Rev 3 page 5/19

| Symbol                          | Parameter                             | Test condition                                                                           | VCC<br>(V) | Min. | Тур. | Max. | Unit |

|---------------------------------|---------------------------------------|------------------------------------------------------------------------------------------|------------|------|------|------|------|

| V <sub>IC+</sub>                | Positive input clamp voltage          | For input under test, I <sub>IN</sub> = -1.0 mA                                          | 0          | 0.4  |      | 1.5  | ٧    |

| V <sub>IC</sub> -               | Negative input clamp voltage          | For input under test, I <sub>IN</sub> = -1.0 mA                                          | Open       | 0.4  |      | -1.5 | V    |

| I <sub>IH</sub>                 | Input current high                    | For input under test, $V_{IN} = V_{CC}$ . For all other inputs, $V_{IN} = V_{CC}$ or GND | 5.5        |      |      | 1    | μA   |

| I <sub>IL</sub>                 | Input current low                     | For input under test, $V_{IN}$ = GND. For all other inputs, $V_{IN}$ = $V_{CC}$ or GND   | 5.5        |      |      | -1   | μA   |

| I <sub>CCH</sub>                | Quiescent supply current, output high | For all inputs, V <sub>IN</sub> = V <sub>CC</sub> or GND I <sub>OUT</sub> = 0 A          | 5.5        |      |      | 40   | μA   |

| I <sub>CCL</sub>                | Quiescent supply current, output low  | For all inputs, V <sub>IN</sub> = V <sub>CC</sub> or GND I <sub>OUT</sub> = 0 A          | 5.5        |      |      | 40   | μA   |

| C <sub>IN</sub> (3)             | Input capacitance                     | Ta = +25 °C                                                                              | 5          |      |      | 10   | pF   |

| C <sub>PD</sub> (3) (4)         | Power dissipation capacitance         | Ta = +25 °C, F = 1 MHz                                                                   | 5          |      |      | 88   | pF   |

|                                 |                                       | C <sub>L</sub> = 2 pF, R <sub>L</sub> = 500 ohm (see Figure 3)                           | 3          |      | 3.7  |      |      |

| $T_r$ , $T_f$                   | Output rise time and fall             | ot - 2 pr, rt - 300 onin (see righte 3)                                                  | 4.5        |      | 2.0  |      | no   |

| 'r, 'f                          | time                                  | C <sub>L</sub> = 50 pF, R <sub>L</sub> = 500 ohm (see Figure 3)                          | 3          |      | 5.2  |      | ns   |

|                                 |                                       | CL = 30 pr , RL = 300 trilli (see rigure 3)                                              | 4.5        |      | 4.5  |      |      |

| T <sub>PHL</sub> <sup>(5)</sup> | Propagation delay time An             | C <sub>L</sub> = 50 pF, R <sub>L</sub> = 500 ohm (see Figure 3)                          | 3          | 1    |      | 11.5 |      |

| PHL **                          | to Yn, high to low                    | οι – σο μι, πι – σου σπιπ (see riigure σ)                                                | 4.5        | 1    |      | 8.5  | ns   |

| T <sub>PLH</sub> <sup>(5)</sup> | Propagation delay time An             | C <sub>1</sub> = 50 pF, R <sub>1</sub> = 500 ohm (see Figure 3)                          | 3          | 1    |      | 12.5 | 115  |

| 'PLH`'                          | to Yn, low to high                    | ο <sub>L</sub> = 30 μι, τις = 300 σππ (see rigure 3)                                     | 4.5        | 1    |      | 9    |      |

- 1. The  $V_{OH}$  and  $V_{OL}$  tests shall be tested at  $V_{CC}$  = 3.0 V and 4.5 V. The  $V_{OH}$  and  $V_{OL}$  tests are guaranteed, if not tested, for other values of  $V_{CC}$ . Limits shown apply to operation at  $V_{CC}$  = 3.3 V,  $\pm$ 0.3 V and  $V_{CC}$  = 5.0 V  $\pm$ 0.5 V. Tests with input current at  $\pm$ 50 mA and  $\pm$ 50 mA are performed on only one input at a time with duration not to exceed 10 ms. Transmission driving tests may be performed using  $V_{IN}$  =  $V_{CC}$  or GND. When  $V_{IN}$  =  $V_{CC}$  or GND is used, the test is guaranteed for  $V_{IN}$  =  $V_{IH}$  minimum and  $V_{IL}$  maximum.

- 2. The V<sub>IH</sub> and V<sub>IL</sub> tests are not required if applied as forcing functions for V<sub>OH</sub> and V<sub>OL</sub> tests.

- 3. C<sub>IN</sub> and C<sub>PD</sub> shall be measured only for initial qualification and after process or design changes which may affect capacitance. C<sub>IN</sub> shall be measured between the designated terminal and GND at a frequency of 1 MHz. C<sub>PD</sub> shall be tested in accordance with the latest revision of JEDEC Standard JESD20 and table IA herein. For C<sub>IN</sub> and C<sub>PD</sub>, test all applicable pins on five devices with zero failures.

- 4. Power dissipation capacitance  $(C_{PD})$  determines both the power consumption  $(P_D)$  and dynamic current consumption (IS). Where:  $P_D = (C_{PD} + C_L) (V_{CC} \times V_{CC}) f + (I_{CC} \times V_{CC})$  and  $IS = (C_{PD} + C_L) V_{CC} \times f + I_{CC}$ , and f is the frequency of the input signal and  $C_L$  is the external output load capacitance.

- 5. For propagation delay tests, all paths are tested. The AC limits at  $V_{CC}$  = 5.5 V are equal to the limits at  $V_{CC}$  = 4.5 V and guaranteed by testing at  $V_{CC}$  = 4.5 V. The AC limits at  $V_{CC}$  = 3.6 V are equal to the limits at  $V_{CC}$  = 3.0 V and guaranteed by testing at  $V_{CC}$  = 3.0 V. Minimum AC limits for  $V_{CC}$  = 5.5 V and  $V_{CC}$  = 3.6 V are 1.0 ns and guaranteed by guard banding the  $V_{CC}$  = 4.5 V and  $V_{CC}$  = 3.0 V minimum limits, respectively, to 1.5 ns. For propagation delay tests, all paths must be tested.

DS13861 - Rev 3 page 6/19

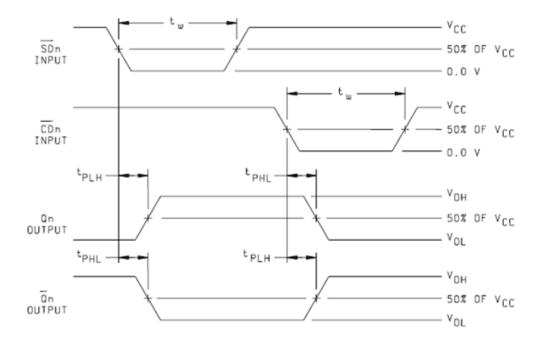

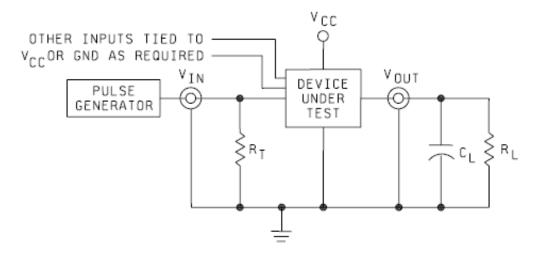

## 4 Waveform and test circuit

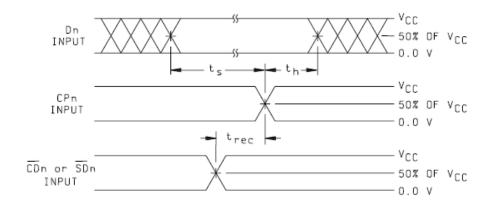

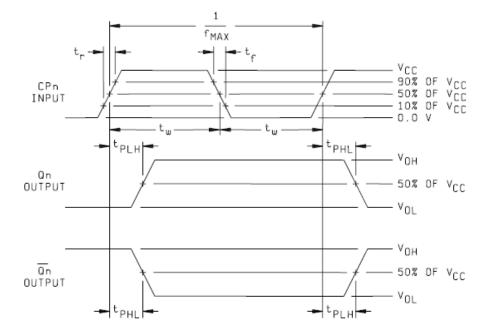

Figure 3. Switching waveforms

DS13861 - Rev 3 page 7/19

Figure 4. Switching wave forms (continued)

Figure 5. Test circuit

Note:

- $V_{TEST}$  = open for  $t_{PLH}$  and  $t_{PHL}$ .

- $C_L = 50 p_F$  or equivalent (includes probe and jig capacitance).

- $R_L = 500$ -ohm or equivalent.

- Input signal from pulse generator:  $V_{IN}$  = 0.0 V to  $V_{CC}$ ;  $P_{RR}$  < 1 MHz; ZO = 50-ohm; tr < 3.0 ns; tr and tf shall be measured from 10% of  $V_{CC}$  to 90% of  $V_{CC}$  and from 90% of  $V_{CC}$  to 10% of  $V_{CC}$ , respectively; duty cycle = 50 percent.

- Timing parameters shall be tested at a minimum input frequency of 1 MHz.

- The outputs are measured one at a time with one transition per measurement.

DS13861 - Rev 3 page 8/19

### 5 Radiations

#### Total ionizing dose (TID):

For the qualification, the product is characterized in TID as per MIL-STD-883 TM 1019 up to 50 krad(Si) on 5 biased parts at high dose rate, such a rate being the worst condition for a pure CMOS technology.

All parameters provided in Table 1 apply to both pre- and post-irradiation.

Each new production lot is tested at high dose rate as per MIL-STD-883 TM 1019 on 5 parts.

#### Heavy-ions:

Single Event Latchup (SEL) is characterized at 125 °C at a LET of 62.5 MeV.cm2/mg. The test shows the product is immune to heavy ions at this LET. Heavy-ion trials are performed on qualification lots only.

The results in radiation are summarized in table 5 as follows.

Table 5. Radiations

| Type               | Conditions                                                                                                                                                                                                         | Results                                             |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| TID <sup>(1)</sup> | <ul> <li>High-dose rate (40 krad (Si) / h)</li> <li>Temperature: 25 °C</li> <li>Performed on 5 biased parts</li> </ul>                                                                                             | Within Table 1 up to 50 krad(Si)                    |

| SEL <sup>(2)</sup> | <ul> <li>LET: 62.5 MeV.cm2/mg (Xenon ions)</li> <li>Temperature: 125 °C</li> <li>Fluence: 1 x 10<sup>7</sup> ions/cm<sup>2</sup> (10 Million of particles per cm<sup>2</sup>)</li> <li>Normal incidence</li> </ul> | Immune to SEL up to<br>62.5 MeV.cm <sup>2</sup> /mg |

<sup>1.</sup> A total ionizing dose (TID) of 50 krad(Si) is equivalent to 500 Gy(Si), (1 gray = 100 rad).

2. SEL: single event latch-up.

DS13861 - Rev 3 page 9/19

# 6 Outgassing

| Specification (tested per ASTM E 595)              | Value | Unit |

|----------------------------------------------------|-------|------|

| Recovered mass loss (RML) (1)                      | 0.06  | %    |

| Collected volatile condensable material (CVCM) (2) | 0.00  | %    |

- 1. RML < 1%

- 2. CVCM < 0.1%

DS13861 - Rev 3 page 10/19

## 7 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

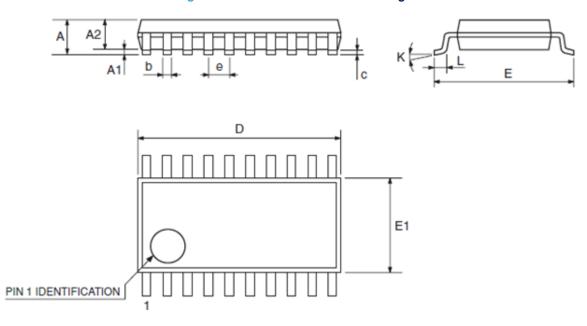

### 7.1 TSSOP-20 package information

Figure 6. TSSOP-20 Mechanical drawing

Table 6. TSSOP-20 package mechanical data

| Symbol |      | Milimeters |      |       | Inches <sup>(1)</sup> |       |  |

|--------|------|------------|------|-------|-----------------------|-------|--|

| Symbol | Min. | Тур.       | Max. | Min   | Тур                   | Max   |  |

| А      |      |            | 1.2  |       |                       | 0.047 |  |

| A1     | 0.05 |            | 0.15 | 0.002 | 0.004                 | 0.006 |  |

| A2     | 0.8  | 1          | 1.05 | 0.031 | 0.039                 | 0.041 |  |

| b      | 0.19 |            | 0.30 | 0.007 |                       |       |  |

| С      | 0.09 |            | 0.20 | 0.004 |                       |       |  |

| D      | 6.4  | 6.5        | 6.6  | 0.252 | 0.256                 | 0.260 |  |

| Е      | 6.2  | 6.4        | 6.6  | 0.244 | 0.252                 | 0.260 |  |

| E1     | 4.3  | 4.4        | 4.48 | 0.169 | 0.173                 | 0.176 |  |

| е      |      | 0.65 BSC   |      |       | 0.0256 BSC            |       |  |

| К      | 0°   |            | 8°   | 0°    |                       | 8°    |  |

| L      | 0.45 | 0.60       | 0.75 | 0.018 | 0.024                 | 0.030 |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Note: TSSOP: Thin-Shrink Small Outline Package, using golden bonding and Nickel/Palladium/Golden-lead-finishing.

DS13861 - Rev 3 page 11/19

# **5**/

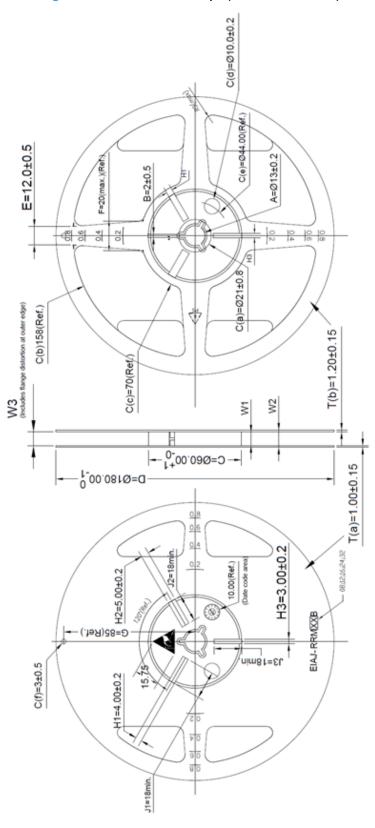

## 7.2 TSSOP-20 packing information

Figure 7. TSSOP-20 Carrier tape (dimensions in mm)

DS13861 - Rev 3 page 12/19

16.0 ±.3 1.75 ±.10 Ф Ф Φ SECTION B - B <u>ص</u>ا-Ф Ø 1.5 +0.1/-0.0 0 0 Ф 0 R 0.3 T/P. Ø 1.50 MIN Ф  $\oplus$ 0 6.95 1.80 1.80 1.20  $\oplus$ 7888 |----¥ 8.00 Ф 0 0 2.00 ±.10 SE NOTE 3 — 4.00 SE NOTE 1 —  $\oplus$ NOTES:

1. 10 SPROCKET HOLE PLTCH CUMLATIVE TOLERANCE ±0.2

2. CANGER IN COMPLIANCE WITH EIA 481

3. POCKET POSTITION RELATIVE TO SPROCKET HOLE MEASURED

AS TRUE POSTITION OF POCKET, NOT POCKET HOLE 9. 9. 8 SECTION A -T ±.05 R 0.3 MAX

Figure 8. Tape drawing for TSSOP-20 (dimensions in mm)

S13861 - Rev 3 page 13/19

# 8 Ordering information

**Table 7. Ordering information**

| Order code  | Quality level      | Package  | Lead-finish | Marking  | Packing       |

|-------------|--------------------|----------|-------------|----------|---------------|

| LEOAC74PT-D | Development sample | TSSOP-20 | NiPdAu      | DLEOAC74 | Tape and reel |

| LEOAC74PT   | Flight model       | TSSOP-20 | NiPdAu      | LEOAC74  | Tape and reel |

Table 8. Order code

| LEO               | AC74 | Р                | Т             |

|-------------------|------|------------------|---------------|

| LEO qualification | Name | TSSOP-20 package | Tape and reel |

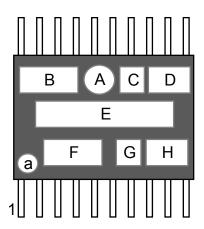

Figure 9. TSSOP20 Marking

- a: pin-1 reference

- A: Second Level of interconnexion (type of lead-finishing)

- B: ST logo

- C: Assy plant

- D: Lot code

- E: Marking area

- F: Country of origin

- G: Assy year

- H: Assy week

DS13861 - Rev 3 page 14/19

## **Revision history**

Table 9. Document revision history

| Date        | Version | Changes                                                    |

|-------------|---------|------------------------------------------------------------|

| 10-Jan-2022 | 1       | First release.                                             |

| 31-Jan-2022 | 2       | Removed footnote in Table 7. Ordering information.         |

| 27-Sep-2024 | 3       | Updated minimum operating power supply from 2 V to 1.65 V. |

DS13861 - Rev 3 page 15/19

## **Contents**

| 1  | Fun    | ctional description                    | 2  |

|----|--------|----------------------------------------|----|

| 2  | Max    | kimum ratings and operating conditions | 4  |

| 3  | Elec   | ctrical characteristics                | 5  |

| 4  | Wav    | veform and test circuit                | 7  |

| 5  | Rad    | liations                               | 9  |

| 6  | Out    | gassing                                | 10 |

| 7  | Pac    | kage information                       | 11 |

|    | 7.1    | TSSOP-20 package information           | 11 |

|    | 7.2    | TSSOP-20 packing information           | 12 |

| 8  | Ord    | ering information                      | 14 |

| Re | /ision | history                                | 15 |

## **List of tables**

| Table 1. | Truth table for each flip-flop   | 3  |

|----------|----------------------------------|----|

| Table 2. | Absolute maximum ratings         | 4  |

|          | Operating conditions             |    |

| Table 4. | Electrical characteristics       | 5  |

| Table 5. | Radiations                       | 9  |

| Table 6. | TSSOP-20 package mechanical data | 11 |

| Table 7. | Ordering information             | 14 |

| Table 8. | Order code                       | 14 |

| Table 9. | Document revision history        | 15 |

# **List of figures**

| Figure 1. | Pin connections (top view)                   | . 2 |

|-----------|----------------------------------------------|-----|

| Figure 2. | Equivalent schematic                         |     |

| Figure 3. | Switching waveforms                          | . 7 |

| Figure 4. | Switching wave forms ( continued )           | . 8 |

| Figure 5. | Test circuit                                 | . 8 |

| Figure 6. | TSSOP-20 Mechanical drawing                  | 11  |

| Figure 7. | TSSOP-20 Carrier tape (dimensions in mm)     | 12  |

| Figure 8. | Tape drawing for TSSOP-20 (dimensions in mm) | 13  |

| Figure 9. | TSSOP20 Marking                              | 14  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

DS13861 - Rev 3 page 19/19