## Rad-hard plastic 2 A positive low drop voltage regulator

Power-SO 20 slug-down

#### Product status link

LEO3910

#### **Features**

- Operating input voltage from 3 V to 12 V

- Adjustable output voltage from 1.23 V to 9 V

- Low-dropout voltage: 0.35 V @ I<sub>O</sub> = 400 mA

- Overtemperature protection

- Overcurrent protection

- · Adjustable current limitation

- Inhibit pir

- High dissipation Power-SO20 package: Rthjc < 2 °C/W</li>

- Operating temperature range: -40 to +125 °C

- Compliant with ST's LEO specification, including

- Wisker free Nickel/Palladium/Gold lead finishing

- Gold wires

- Characterized outgassing: RML < 1% CVCM < 0.1%</li>

- · Radiation performance:

- 50 krad(Si) Total Ionizing Dose

- TNID immune at 3.10<sup>11</sup> proton/cm²

- SEL free up to 62 MeV.cm²/mg

## **Application**

- LEO satellites power management

- Power supply of FPGA, MPU, ASIC, and MCU

- Power management in radiative and other harsh environments

### **Description**

The LEO3910 is a positive adjustable voltage regulator housed into a Power-SO 20 slug-down package, which is able to provide in regulation a maximum output current up to 2 A.

It can operate over a large temperature range of -40 °C to +125 °C.

The LEO3910 is compliant with the ST-LEO-specification, dedicated specifications for space-ready rad-hard plastic products. This AEC-Q100-based specidification offers radiation hardness and the capability to support large quantities, together with a trade-off optimized for LEO space crafts between quality assurance and cost of ownership (details on the ST LEO generic specification can be found in TN1432).

# 1 Block diagram

Figure 1. Block diagram Short circuit current sense On/Off Pass element • V<sub>o</sub> Error amplifier Bandgap  $V_{\mathsf{REF}}$ Driver Thermal shutdown O ADJ ISC O Current limit + monitoring осмо Antisat GND O-

DS13691 - Rev 4 page 2/23

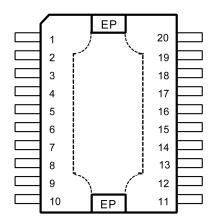

# 2 Pin configuration

Figure 2. Pin configuration

Table 1. Pinout configuration

| Pin number | Pin name | Description                                                                                                                     |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| EP         | EP       | Slug down exposed pad, internally connected to pins 1, 10, 11 and 20 The Exposed pad should be grounded to maximize dissipation |

| 1          | EP       | Internally connected to EP                                                                                                      |

| 2, 3       | NC       | Not connected                                                                                                                   |

| 4, 6       | Vo       | Output voltage                                                                                                                  |

| 5          | VI       | Input voltage                                                                                                                   |

| 6, 4       | Vo       | Output voltage                                                                                                                  |

| 7          | ISC      | Current limit setting                                                                                                           |

| 8, 9       | NC       | Not connected                                                                                                                   |

| 10, 11     | EP       | Internally connected to EP                                                                                                      |

| 12         | OCM      | Over-current monitoring                                                                                                         |

| 13, 14, 15 | NC       | Not connected                                                                                                                   |

| 16         | GND      | Ground                                                                                                                          |

| 17         | INH      | Inhibit                                                                                                                         |

| 18         | NC       | Not connected                                                                                                                   |

| 19         | ADJ      | Output voltage feedback error adjustment                                                                                        |

| 20         | EP       | Internally connected to EP                                                                                                      |

DS13691 - Rev 4 page 3/23

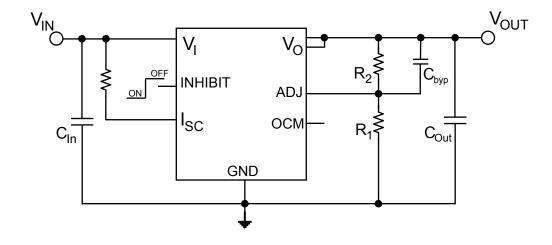

# 3 Application circuit

Figure 3. Typical application circuit

DS13691 - Rev 4 page 4/23

## 4 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol           | Parameter                                            | Value                        | Unit |

|------------------|------------------------------------------------------|------------------------------|------|

| VI               | DC input voltage                                     | -0.3 to 14                   | V    |

| Vo               | DC output voltage range -0.3 to V <sub>I</sub> + 0.3 |                              | V    |

| V <sub>ADJ</sub> | ADJ pin voltage                                      | See note 1                   | V    |

| V <sub>OCM</sub> | Over current monitor pin voltage                     | -0.3 to V <sub>I</sub> + 0.3 | V    |

| V <sub>ISC</sub> | Current limit pin voltage                            | See note 2                   | V    |

| V <sub>INH</sub> | INHIBIT input voltage -0.3 to V <sub>1</sub> +       |                              | V    |

| T <sub>stg</sub> | Storage temperature range                            | -65 to +150                  | °C   |

| ESD              | Electrostatic discharge HBM                          | 2                            | kV   |

| LOD              | Electrostatic discharge CDM                          | 750                          | V    |

- Note 1:  $V_{ADJ}$  is internally maintained at 1.23 Volt. A forced excursion below 0.3 Volt or above the smallest of  $(V_1 + 0.3)$  and 3.93 Volt may permanently damage the product.

- Note 2: V<sub>ISC</sub> may be pulled-up to V<sub>I</sub> or left floating. A forced excursion below the lowest of -0.3 Volt and (V<sub>I</sub> 2.7) or above (V<sub>I</sub> + 0.3) may permanently damage the product.

Table 3. Recommended operating conditions

| Symbol            | Parameter                                             | Value       | Unit |

|-------------------|-------------------------------------------------------|-------------|------|

| V <sub>I</sub>    | DC input voltage V <sub>I</sub> - V <sub>GROUND</sub> | 3 to 12     | V    |

| Vo                | DC output voltage range                               | 1.23 to 9   | V    |

| I <sub>OMAX</sub> | Maxium output current                                 | 2           | Α    |

| Тор               | Operating junction temperature                        | -40 to +125 | °C   |

| P <sub>D</sub>    | TC = 25 °C power dissipation                          | 15          | W    |

Table 4. Thermal data

| Symbol            | Parameter                           | Value | Unit |

|-------------------|-------------------------------------|-------|------|

| R <sub>thJC</sub> | Thermal resistance junction-case    | 2     | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction-ambient | 25    | °C/W |

DS13691 - Rev 4 page 5/23

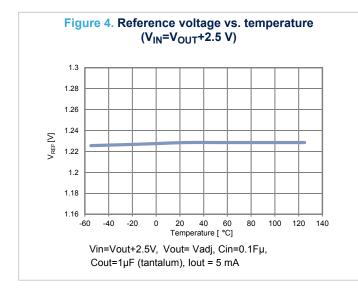

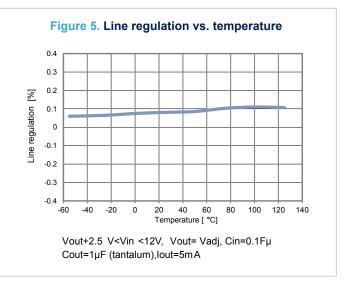

## 5 Electrical characteristics

V<sub>I</sub> = V<sub>O</sub> + 2.5 V, T<sub>j</sub> = -40 to 125 °C, C<sub>I</sub> = 10  $\mu$ F, C<sub>O</sub> = 10  $\mu$ F tantalum, unless otherwise specified.

**Table 5. Electrical characteristics**

| Symbol                      | Parameter                               | Test conditions                                                        | Min. | Тур.           | Max. | Unit    |

|-----------------------------|-----------------------------------------|------------------------------------------------------------------------|------|----------------|------|---------|

| VI                          | Input voltage                           | I <sub>O</sub> = 2 A                                                   | 3    |                | 12   | V       |

| Vo                          | Reference voltage                       | $I_O = 5 \text{ mA}, V_O = V_{ADJ}$                                    | 1.19 | 1.23           | 1.27 | V       |

| I <sub>OLIM</sub>           | Overcurrent protection lilimation (1)   | V <sub>O</sub> = 0 V                                                   | 0.8  |                | 2    | Α       |

| $\Delta V_O/\Delta V_i$     | Line regulation                         | $V_{I} = V_{O} + 2.5 \text{ V to } 12 \text{ V}, I_{O} = 5 \text{ mA}$ | -    | 0.07           | 0.35 | %       |

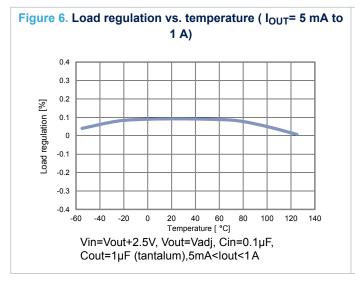

| $\Delta V_{O}/\Delta I_{O}$ | Load regulation                         | $V_{I} = V_{O} + 2.5 \text{ V}, I_{O} = 5 \text{ mA to 1 A}$           | -    | 0.4            | 0.6  | %       |

| Z <sub>OUT</sub>            | Output impedance                        | I <sub>O</sub> = 100 mA DC and 20 mA rms                               |      | 100            |      | mΩ      |

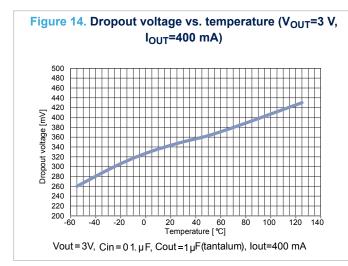

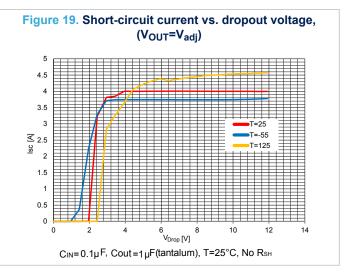

|                             |                                         | I <sub>O</sub> = 400 mA, V <sub>out</sub> = 3 V                        | -    | 0.35           | 0.7  | V       |

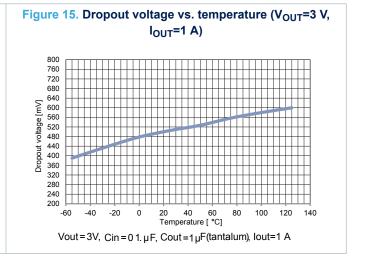

| $V_d$                       | Dropout voltage                         | I <sub>O</sub> = 1 A, V <sub>out</sub> = 3 V                           | -    | 0.5            | 1    | V       |

|                             |                                         | I <sub>O</sub> = 2 A, V <sub>out</sub> = 3 V                           | -    | 0.75           | 1.5  | V       |

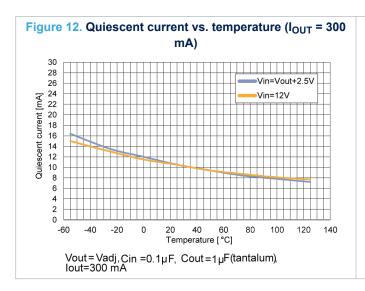

|                             |                                         | $V_I = V_O + 2.5 \text{ V to } 12 \text{ V},$                          |      | 1.6            | 6    | mA      |

| Iq                          | Quiescent current                       | I <sub>O</sub> = 5 mA                                                  | -    |                |      |         |

|                             |                                         | $V_I = V_O + 2.5 \text{ V to } 12 \text{ V},$                          |      | 2.7            |      | mΛ      |

|                             |                                         | I <sub>O</sub> = 30 mA                                                 | -    |                | 8    | mA      |

|                             |                                         | $V_I = V_O + 2.5 \text{ V to } 12 \text{ V},$                          |      | 11             | 25   |         |

|                             |                                         | I <sub>O</sub> = 300 mA                                                | -    |                |      | mA      |

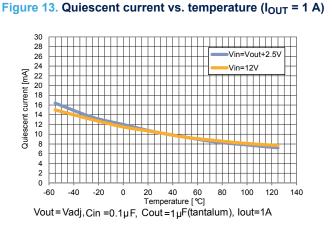

|                             |                                         | $V_I = V_O + 2.5 V \text{ to } 12 V,$                                  |      | 32             | 62   | mA      |

|                             |                                         | I <sub>O</sub> = 1 A                                                   | -    |                |      |         |

|                             |                                         | V <sub>I</sub> = 12 V V <sub>INH</sub> = 3 V, off mode                 | -    | 0.3            | -    | mA      |

|                             |                                         | $V_I = V_O + 2.5 V \pm 1 V$ ,                                          |      |                |      |         |

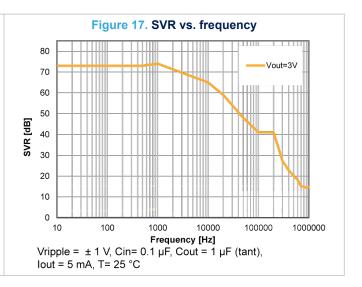

| SVR                         | Supply voltage rejection <sup>(1)</sup> | $I_O = 5 \text{ mA},$                                                  | _    | 50             | _    | dB      |

|                             |                                         | V <sub>O</sub> =3 V, f = 33 kHz<br>Tj = 25 °C                          |      |                |      |         |

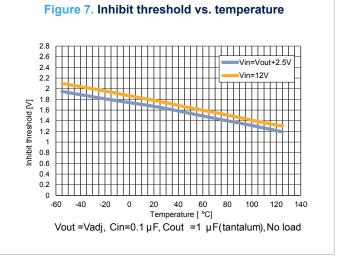

| V <sub>INH (OFF)</sub>      | Inhibit turn-off voltage                | I <sub>O</sub> = 5 mA                                                  | 2.4  | -              | -    | V       |

| V <sub>INH (ON)</sub>       | Inhibit turn-on voltage                 | I <sub>O</sub> = 5 mA                                                  | -    | -              | 8.0  | V       |

| I <sub>INH</sub>            | Shutdown input current                  | V <sub>INH</sub> = 5 V                                                 | -    | 120            | -    | μA      |

| V <sub>OCML</sub>           | Overcurrent monitor voltage low         | I <sub>OCM</sub> = 10 mA (sunk current), V <sub>I</sub> = 12 V         | -    | 0.4            | -    | V       |

| V                           | Overeument manifes welfare bi-l-        | I <sub>OCM</sub> = -10 μA (sourced current)                            |      | .,             |      |         |

| V <sub>OCMH</sub>           | Overcurrent monitor voltage high        | $V_1 = V_0 + 2.5 V \text{ to } 12 V$                                   | -    | V <sub>I</sub> | -    | V       |

|                             |                                         | B= 10 Hz to 100 kHz                                                    |      |                |      |         |

| eN                          | Output noise voltage <sup>(1)</sup>     | $I_O = 5 \text{ mA to } 2 \text{ A}$<br>$Tj = 25 ^{\circ}\text{C}$     | - 40 |                | -    | μVrms/V |

<sup>1.</sup> These values are guaranteed by design, not tested in production.

DS13691 - Rev 4 page 6/23

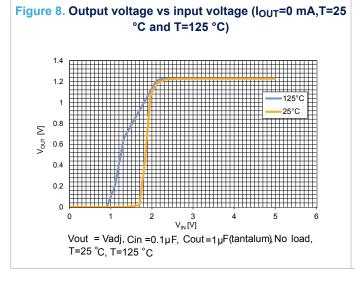

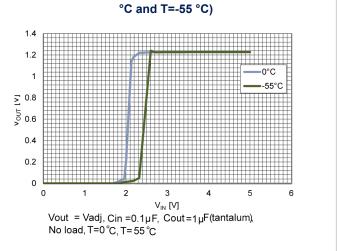

## 6 Typical characteristics

Figure 9. Output voltage vs input voltage (I<sub>OUT</sub>=0 mA,T=0

DS13691 - Rev 4 page 7/23

Figure 10. Quiescent current vs. temperature (no load)

4.5

4.5

4.5

3.5

3.5

1

0.5

0-60 -40 -20 0 20 40 60 80 100 120 140 Temperature [°C]

Vout = Vadj, Cin = 0.1 µF, Cout = 1 µF(tantalum), no load

Figure 11. Quiescent current vs. temperature (I<sub>OUT</sub> = 30 mA) 5.5 5 4.5 Quiescent current [mA] 4 3.5 3 2.5 2 1.5 0.5 20 40 60 Temperature [ °C] 120 Vout = Vadj, Cin =0.1µF, Cout =1µF(tantalum), Iout=30 mA

DS13691 - Rev 4 page 8/23

Figure 16. Dropout voltage vs. temperature (V<sub>OUT</sub>=3 V, I<sub>OUT</sub>=2 A)

Figure 18. Output noise spectrum (V<sub>OUT</sub>=V<sub>adj</sub>, C<sub>OUT</sub>=1 μF)

400.0

350.0

300.0

250.0

100.0

100.0

100.0

100.0

Frequency [Hz]

VIN = 3.5V, V<sub>out</sub>=V<sub>ADJ</sub>, Cin = 220 μF, Cout = 1 μF(tantalum)

DS13691 - Rev 4 page 9/23

DS13691 - Rev 4 page 10/23

## 7 Radiations

## 7.1 Total ionizing dose (TID)

The LEO3910 is RHA guaranteed and ELDRS immune up to 50 krad(Si) as per MIL-STD-883 TM 1019 condition A and D.

The total ionization dose has been characterized in high and low dose rate on 5 biased and 5 unbiased pieces. This test has shown that the product is immune to ELDRS and that the worst-case configuration is with biased parts.

All parameters provided in Table 5. Electrical characteristics apply to both pre- and post-irradiation.

On top of the characterization, each wafer lot is submitted to a wafer lot acceptance with a TID test at a high dose rate on 5 biased parts per wafer lot with an acceptance criterion of 0 fail.

## 7.2 Total non-ionizing dose (TNID)

The total non-ionizing dose is tested with 50 MeV protons.

The test is performed during the product characterization and as part of the wafer lot acceptance test on 5 pieces per wafer lot with an acceptance criterion of 0 fail.

## 7.3 Heavy-ions

The LEO3910 is characterized under heavy ions up to 62 MeV.cm²/mg as summarized below:

- Tests performed: SEL, SET, SEU / SEFI

- Each test is performed on 3 samples of the final silicon in the worst-case conditions.

**Table 6. Radiation summary**

| Type | Conditions                                           | Value                                            |

|------|------------------------------------------------------|--------------------------------------------------|

| TID  | Up to 50 krad(Si) at 25 °C                           | RHA guaranted and ELDRS free at 50 krad(Si)      |

| טוו  | 40 krad(Si) / hour (HDR) and 36 rad(Si) / hour (LDR) | KHA guaranted and ELDRS free at 50 klad(Si)      |

| TNID | Up to 3x10 <sup>11</sup> protons.cm² 50 MeV protons  | Post TNID characteristics compliant with Table 5 |

|      | Test up to 62.5 MeV.cm²/mg at 25 °C                  |                                                  |

| SESB | Fluence: 1.10 <sup>7</sup> ion/cm <sup>2</sup>       | Immune to SEL up to 62 MeV.cm²/mg                |

|      | Normal incidence                                     |                                                  |

| SET  | T <sub>ambient</sub> = 25 °C                         | Characterized up to 62 MeV.cm²/mg                |

DS13691 - Rev 4 page 11/23

## 8 Device description

The LEO3910 adjustable voltage regulator contains a PNP type power element controlled by a signal resulting from an amplified comparison between the internal temperature-compensated band-gap and the fraction of the desired output voltage value obtained from an external resistor divider bridge. The device is protected by several functional blocks.

#### 8.1 ADJ pin

The output voltage feedback comes through an external resistor divider (R1, R2 as in the typical application schematic), whose mid-point connected to the ADJ pin (allowing to set the output voltage at the desired level).

#### 8.2 Inhibit ON-OFF control

By setting the INHIBIT pin high, the device switches off the output current and voltage. The device is ON when the INHIBIT pin is set low. Since the INHIBIT pin is pulled down internally, it can be left floating in cases where the inhibit function is not used.

### 8.3 OCM pin

In the event of an overcurrent at the output, a voltage level of 0.4 V is present at the OCM pin. In other conditions, this voltage equals  $V_I$ . The OCM pin is internally pulled up by a 5 k $\Omega$  resistor up to  $V_I$ . It is buffered and can sink up to 10 mA.

### 8.4 Overtemperature protection

A temperature detector internally monitors the power element junction temperature. The device turns off when a temperature of approximately 175 °C is reached, returning to ON mode when back to approximately 135 °C. Combined with the other protection blocks, the device is protected from destructive junction temperature excursions in all load conditions. Prolonged operation under these conditions far exceeds the maximum operating ratings and device reliability cannot be guaranteed.

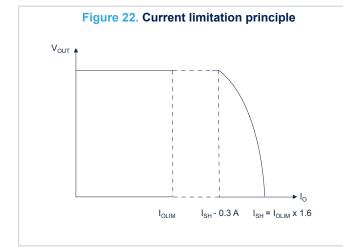

## 8.5 Overcurrent protection

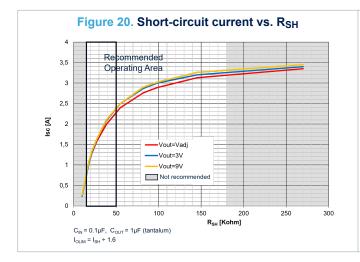

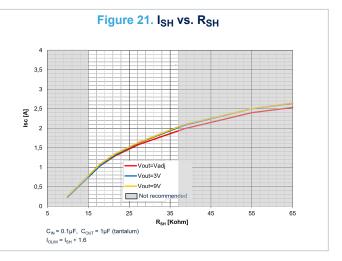

An internal non-fold-back short circuit over-current limitation limits by default the short circuit output current ISH at typically 3.6 A when pin ISC is left floating. This overcurrent limitation is primarily designed to protect the device itself

In the Power So 20 packaged version, the overcurrent limitation can be used as a basic adjustable overcurrent protection of the load. However, to secure proper startup of the regulator in all conditions, the current limit must comply with the guidelines provided below.

The overcurrent protection must be set above the maximum current required by the load in worst case conditions, including temperature and radiations, but low enough to be an effective protection. Furthermore, this I<sub>OLIM</sub> value must be within the limits specified in the electrical specification in Table 5.

Once  $I_{OLIM}$  is defined,  $I_{SHADJ}$  is calculated by applying the formula  $I_{SHADJ} = I_{OLIM} \times 1.6$  to account for the 0.3 A where the protection is active (see Section 6), for the temperature and radiation drifts as well as for the part to part variations of the default ISH and the protection circuits.

Figure 20 allow to define the typical value of the RSH resistors to be connected between pins ISC and  $V_I$  to set  $I_{SHADJ}$  at the desired value.

DS13691 - Rev 4 page 12/23

## 9 Application information

To adjust the output voltage, the  $R_2$  resistor must be connected between the  $V_0$  and ADJ pins. The  $R_1$  resistor must be connected between ADJ and ground. Resistor values can be derived from the following formula:

$$V_0 = V_{ADJ} (R_1 + R_2) / R_1$$

The V<sub>AD.I</sub> is typically 1.23 V, controlled by the internal temperature-compensated band gap block.

The minimum input voltage is 3 V. The LEO3910 is designed to operate for  $V_I - V_O >$  of the minimum specified dropout. The value of  $R_1$ , the resistance between ADJ pin and GND, must not be greater than 10 k $\Omega$ , in order to keep the output feedback error below 0.2%. A minimum of 0.5 mA  $I_O$  must be set to ensure perfect no-load regulation. It is advisable to dissipate this current into the divider bridge resistor.

The inhibit function switches off the output current very quickly. According to Lenz's law, the external circuitry reacts with Ldl/dt terms which can be of high amplitude in case somewhere a serial coil inductance exists. Large transient voltage would develop on both device terminals. It is advisable to protect the device with Schottky diodes to prevent negative voltage excursions. In the worst case, a 14 V Zener diode could protect the device input.

All available V<sub>I</sub> and V<sub>O</sub> pins must be externally interconnected, to ensure stability and reliability of the device.

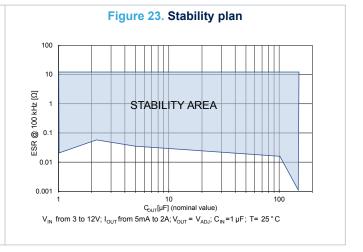

To ensure regulator stability, input and output capacitors with a minimum 10  $\mu$ F are mandatory. These capacitors must be connected as close as possible to the device terminals.

In the case of high-current operation, an important factor to look at for the reliability target of the space application is the sustainable surge current of the capacitors used. The surge current is known to be one of the major failure mechanisms for these parts, especially when the equipment is turned ON.

Derating is a means for application engineers of space systems to further reduce the probability of failures by limiting the level of stresses to capacitors during application. Typical derating requirements for solid tantalum capacitors limit the maximum applied voltage to 50% of the rated voltage (VR) and the inrush currents are bounded by additional resistors used in series with the capacitors.

In addition, a ceramic capacitor of at least 100nF in parallel to the input and output bulk capacitors must be used for decoupling purposes. A 470 nF polyester capacitors, put close to the regulator between input and ground, helps further improving the LEO3910 reliability by filtering potentially dangerous over voltages spikes coming out during particular conditions.

A separate kelvin voltage sensing line provides the ADJ pin with exact load "high potential" information (see Figure 4. Application diagram for remote sensing operation). But variable remote load current consumption induces variable Iq current (Iq is roughly the IO current divided by the hFE of the internal PNP series power element) routed through the parasitic series line resistor RW2. To compensate for this parasitic voltage, resistor RW1 can be introduced to provide the necessary compensating voltage signal to the ADJ pin. A ceramic or polyester 47nF CBYP capacitor between ADJ and  $V_{\rm O}$  pins is recommended when the remote sensing technique is implemented.

Since the LEO3910 adjustable voltage regulator is manufactured with very high speed bipolar technology (6 GHz fT transistors), the PCB layout must be designed with exceptional care, with very low inductance and low mutually coupling lines. Otherwise, high frequency parasitic signals may be picked up by the device resulting in system self-oscillation. The benefit is an SVR performance extended to far higher frequencies.

DS13691 - Rev 4 page 13/23

## 10 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

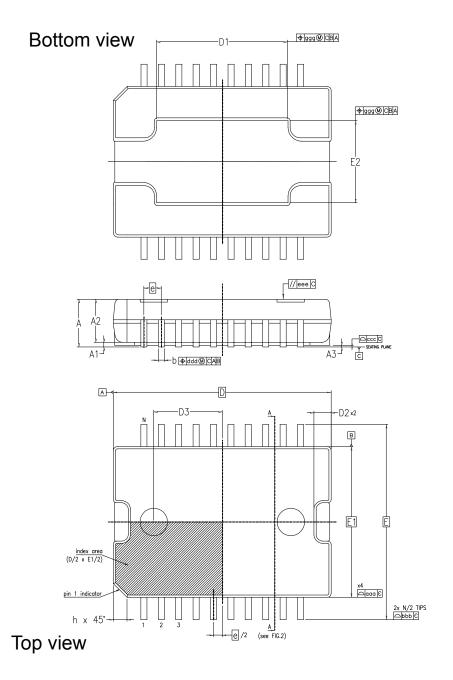

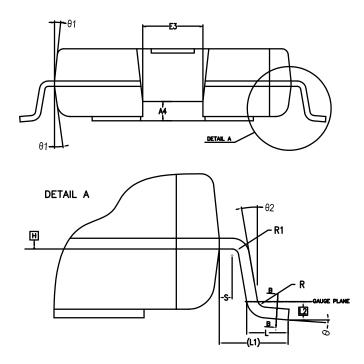

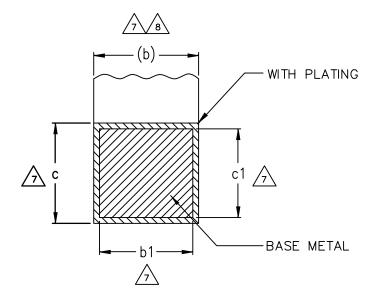

## 10.1 PowerSO-20 package information

Figure 24. PowerSO-20 package outline

DS13691 - Rev 4 page 14/23

Figure 25. PowerSO-20 detail A

Figure 26. PowerSO-20 detail B

DS13691 - Rev 4 page 15/23

Table 7. PowerSO-20 mechanical data

| O. w. b. al. | Milimeters |           |       |  |  |

|--------------|------------|-----------|-------|--|--|

| Symbol       | Min.       | Тур.      | Max.  |  |  |

| θ            | 0 °        | -         | 8°    |  |  |

| θ1           | 5°         | -         | 10°   |  |  |

| θ2           | 0°         | -         | -     |  |  |

| Α            | -          | -         | 3.50  |  |  |

| A1           | 0.20       | -         | 0.275 |  |  |

| A2           | 3.10       | -         | 3.20  |  |  |

| A3           | 0.00       | -         | 0.075 |  |  |

| A4           | 0.83       | -         | 0.95  |  |  |

| b            | 0.40       | -         | 0.53  |  |  |

| b1           | 0.40       | 0.45      | 0.50  |  |  |

| С            | 0.23       | -         | 0.32  |  |  |

| D            |            | 15.90 BSC |       |  |  |

| D1           |            | Variation |       |  |  |

| D2           | -          | -         | 1.10  |  |  |

| D3           | -          | 5.00      | -     |  |  |

| е            | 1.27 BSC   |           |       |  |  |

| E            |            | 14.20 BSC |       |  |  |

| E1           |            | 11.00 BSC |       |  |  |

| E2           |            | Variation |       |  |  |

| E3           | -          | -         | 2.85  |  |  |

| h            | -          | -         | 1.10  |  |  |

| L            | 0.85       | -         | 1.05  |  |  |

| L1           |            | 1.60 REF  |       |  |  |

| L2           |            | 0.35 BSC  |       |  |  |

| N            |            | 20        |       |  |  |

| R            | 0.20       | -         | -     |  |  |

| R1           | 0.20       | -         | -     |  |  |

| S            | 0.25       | -         | -     |  |  |

Table 8. Tolerance of form and position

| Symbol | Drawing |

|--------|---------|

| aaa    | 0.10    |

| bbb    | 0.30    |

| ccc    | 0.10    |

| ddd    | 0.25    |

| eee    | 0.10    |

| 999    | 0.25    |

| Note   | 1.2     |

DS13691 - Rev 4 page 16/23

| Table 9. Variations | Tab | le 9. | <b>Variations</b> |

|---------------------|-----|-------|-------------------|

|---------------------|-----|-------|-------------------|

| Symbol | Drawing |      |       | Opt. |

|--------|---------|------|-------|------|

| Зушьог | Min.    | Тур. | Max.  | Орг. |

| D1     | 9.00    | -    | 13.00 | ^    |

| D2     | 5.60    | -    | 6.20  | A    |

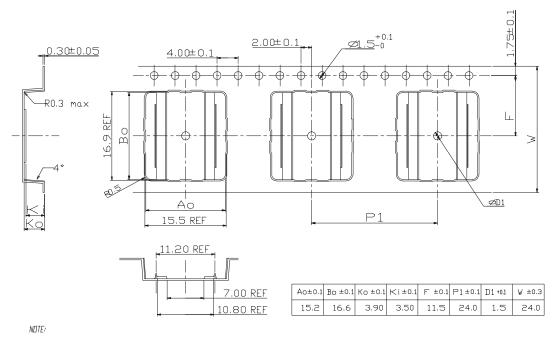

#### 10.2 PowerSO-20 packing information

The flight models are delivered in a 600 position tape, out of which 100 consecutive ones are filled with a product, the others being left empty. The carrier tape and tape are described in the figures below.

The development samples are delivered in 7-position sticks of the same tape.

W3 E=12.0±0.5 C(f)=3±0.5 C(b)158(Ref.) D=Ø180.00 0-1 F=20(max.)(Ref.) H1=4.00±0.2 H2=5.00±0.2 C(c)=70(Ref/ B=2±0.5 C=Ø60.00<sup>+1</sup>--C(d)=Ø10.0±0.2 C(a)=Ø21±0.8 W1 W2 A=Ø13±0.2 H3=3.00±0.2 T(b)=1.20±0.15 T(a)=1.00±0.15

Figure 27. PowerSO-20 carrier tape outline

Figure 28. PowerSO-20 tape outline

1) Cumulative tolerance of 10 sprocket holes: 0.2mm 2) Camber: 1mm/100mm max

DS13691 - Rev 4 page 17/23

## 10.3 Outgassing

The outgassing data of the PowerSO-20, measured as per ASTM-E-595, are provided in Table 10. They are compliant with the LEO generic specification setting the maximum limits for the recovered mass loss at 1% and for the collected volatile condensable material at 0.1%

Table 10. Outgassing

| Specification (tested per ASTM E 595)                         | Value | Unit |

|---------------------------------------------------------------|-------|------|

| Recovered mass loss (RML) <sup>(1)</sup>                      | 0.06  | %    |

| Collected volatile condensable material (CVCM) <sup>(2)</sup> | 0.00  | %    |

- 1. RML < 1%.

- 2. CVCM < 0.1%.

DS13691 - Rev 4 page 18/23

## 11 Ordering information

| Quality level | Quality level | Package       | Lead-finish | Marking | Packing | Mass   |        |        |        |        |               |        |         |         |               |

|---------------|---------------|---------------|-------------|---------|---------|--------|--------|--------|--------|--------|---------------|--------|---------|---------|---------------|

| LEO3910PDB    | Flight model  | PS0-20 NiPdAu | NiDdAu      | LEO2010 | Tube    | 1.0    |        |        |        |        |               |        |         |         |               |

| LEO3910PDT    | Flight model  |               | PS0-20      | PS0-20  | PS0-20  | PS0-20 | PS0-20 | PS0-20 | PS0-20 | PS0-20 | PS0-20 NIPdAu | NiPdAu | LEO3910 | LE03910 | Tape and reel |

<sup>1.</sup> Product specific marking. See figure Figure 29 for the descrption of the comlete marking.

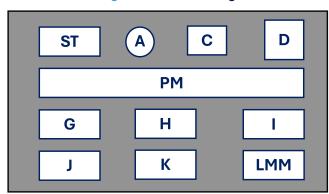

## 11.1 Marking

The marking of the parts is summarized for the LEO flight models and in Table 11 for the development samples (refer to TN1418 for the description of the development samples quality level).

Figure 29. PSO marking

Table 11. Product marking description

| Field | Description                 | LEO3910 values           |

|-------|-----------------------------|--------------------------|

| ST    | ST logo                     |                          |

| Α     | Pb free logo                | e4 <sup>(1)</sup>        |

| С     | Sublot assembly index       | Lot dependent            |

| D     | QR code                     | Lot dependent            |

| PM    | Specific product marking    | See                      |

| G     | Assembly plant              | 99 (Muar) <sup>(3)</sup> |

| Н     | Back end sequence (2)       | xxx                      |

| I     | Diffusion traceability      | VA (Agrate) (3)          |

| J     | Country of origin           | MYS (Malaysia) (3)       |

| K     | Test and finishing plant    | 99 (Muar) <sup>(3)</sup> |

| L     | Date code year (last digit) | 0 to 9                   |

| MM    | Date code week              | 01 to 52                 |

- 1. Package code as per Jedec J-STD-609. e4: precious metal, e.g. Ag, Au, NiPd, NiPdAu... excluding Sn.

- 2. Assembly flow reference.

- 3. Different value should denote that a product change notice has been issued.

DS13691 - Rev 4 page 19/23

## 11.2 Product documentation

The flight models are delivered with a certificate of conformance enclosed in the shipment box. Refer to TN1432 for the list of information it provides.

**Table 12. Documentation LEO**

| Quality level | Documentation                  |

|---------------|--------------------------------|

| Flight parts  | Certificate of conformance (1) |

1. See TN1432 for details on the information provided in the certificate of conformance.

DS13691 - Rev 4 page 20/23

## **Revision history**

Table 13. Document revision history

| Date        | Version | Changes                                                                                                                                  |

|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------|

| 17-May-2021 | 1       | Initial release.                                                                                                                         |

| 22-Feb-2022 | 2       | Updated Section 5: Electrical characteristics and Section 6: Application information.                                                    |

| 20-Jun-2024 | 3       | Minor text changes.                                                                                                                      |

| 02-Dec-2025 | 4       | Updated features and description on the cover page.  Updated Figure 1, Figure 2, Table 1,  Added Section 11.1 and Product documentation. |

DS13691 - Rev 4 page 21/23

## **Contents**

| 1   | Bloc                    | k diagram                      | 2  |  |  |  |

|-----|-------------------------|--------------------------------|----|--|--|--|

| 2   | Pin configuration       |                                |    |  |  |  |

| 3   | Application circuit     |                                |    |  |  |  |

| 4   | Maximum ratings         |                                |    |  |  |  |

| 5   |                         | trical characteristics         |    |  |  |  |

| 6   | Typical characteristics |                                |    |  |  |  |

| 7   |                         | Radiations                     |    |  |  |  |

|     | 7.1                     | Total ionizing dose (TID)      |    |  |  |  |

|     | 7.2                     | Total non-ionizing dose (TNID) |    |  |  |  |

|     | 7.3                     | Heavy-ions                     |    |  |  |  |

| 8   | Device description      |                                |    |  |  |  |

|     | 8.1                     | ADJ pin                        |    |  |  |  |

|     | 8.2                     | Inhibit ON-OFF control         | 12 |  |  |  |

|     | 8.3                     | OCM pin                        | 12 |  |  |  |

|     | 8.4                     | Overtemperature protection     | 12 |  |  |  |

|     | 8.5                     | Overcurrent protection         | 12 |  |  |  |

| 9   | Appl                    | lication information           | 13 |  |  |  |

| 10  | Pack                    | kage information               | 14 |  |  |  |

|     | 10.1                    | PowerSO-20 package information | 14 |  |  |  |

|     | 10.2                    | PowerSO-20 packing information | 17 |  |  |  |

|     | 10.3                    | Outgassing                     | 18 |  |  |  |

| 11  | Orde                    | ering information              | 19 |  |  |  |

|     | 11.1                    | Marking                        | 19 |  |  |  |

|     | 11.2                    | Product documentation          | 20 |  |  |  |

| Rev | rision                  | history                        | 21 |  |  |  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics - All rights reserved

DS13691 - Rev 4 page 23/23