# Smart octal P-channel for ultra-low current consumption automotive systems

# **Features**

| Maximum transient supply voltage | V <sub>CC</sub>    | 40 V         |

|----------------------------------|--------------------|--------------|

| Operating voltage range          | V <sub>CC</sub>    | 28 V         |

| Standby ON current (max.)        | I <sub>VCC_Q</sub> | 48 µA        |

| SPI I/O supply voltage           | V <sub>DD</sub>    | 3 V to 5.5 V |

| SPI standby ON current (max.)    | I <sub>VDD_Q</sub> | 5 μΑ         |

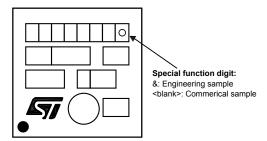

Tape and reel

**Packing**

| AEC-Q100 qualified |  |

|--------------------|--|

- 8x P-channel with R<sub>ON</sub> = 1 Ω

- Ultra low current consumption:

- 0 μA in deep standby mode

- 6 μA in standby on mode per channel

- 4x direct inputs to control channels status in limp-home mode

- 24-bit ST-SPI interface for device full configurability and standalone operation

- Limp-home mode set by dedicated pin

- Integrated ADC block to monitor:

- Outputs current in on state (both in normal and fail-safe mode)

- Battery and output voltages in both on and off state (in normal mode)

- Device junction temperature (T<sub>J</sub>) in both on and off state

- Dual range ADC for current sensing

- 500 mA minimum peak current (per channel) to avoid undesired main switch triggering due to inrush transient current (microcontroller peripherals polling, contact monitoring...)

- Built in self test (BIST), actionable on demand, to monitor correct device behavior during its working life:

- Current ADC

- Voltage ADC

- Standby on current sense chain

- P-channel stuck-on protection

- Non-volatile memory (NVM) to configure current thresholds (I<sub>THRx</sub>)

automatically to exit standby ON state two few times programmable (FTP)

bits per channel

- Capacitive charging mode (CCM) in normal operation

- Protection–whose triggering generates main switch enable:

- Overtemperature shutdown (latch-off)

- Current shutdown (based on VDS monitoring)

- Integrated ESD protection

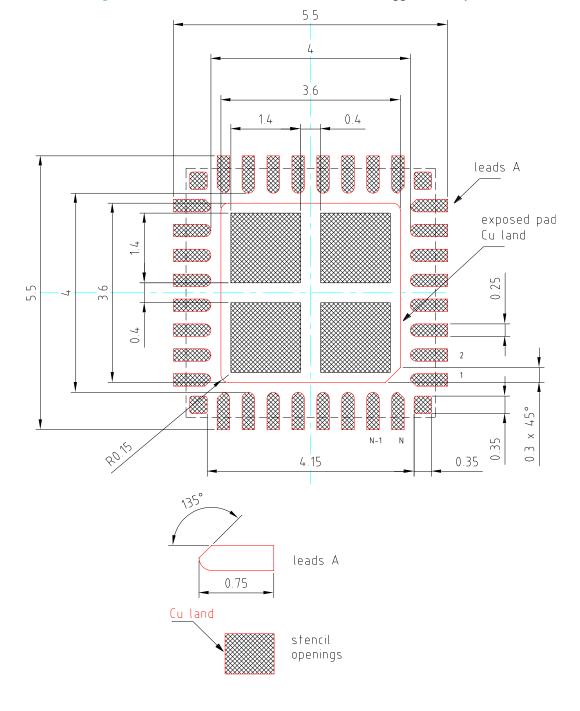

- QFN 5x5x0.9 mm 32+4L package with wettable flanks

- Compliant with European directive 2002/95/EC

# **Description**

The L99SP08 Smart P-channel is an octa channel device made using STMicroelectronics BCD9sL technology, housed in a small QFN 5x5x0.9 mm 32+4L wettable flanks package. It is designed to support standby on functionality, when interacting with hybrid and monolitich STi²Fuse product family, as well as to drive loads in standalone mode, up to I<sub>OUTX</sub> DC current per channel.

Integrating a deep standby mode, the device fulfills highly stringent requirements for all those always active battery lines, providing ultra-low current consumption with the car in parking mode.

Real time diagnostic is available through the SPI bus (communication error, oscillator stuck, overtemperature,  $V_{CC}$  and  $V_{OUT}$  monitoring). In case of overtemperature, VDS overvoltage or  $I_{PEAK}$  triggering, the device sets high EN pin, allowing the turn on of external devices, like STi²Fuse hybrid and monolithic devices (for further information on the usage of the L99SP08 in combination with the hybrid and monolithic STi²Fuse devices for parking mode functionality refer to the related application notes AN6025 and AN6371).

Built-in self-tests (BIST) are integrated to check the correct behavior of the device during its working life, allowing customer on demand activation, testing current ADC, voltage ADC, standby on current sense chain and P-channel stuck-on protection.

The device is also equipped with a nonvolatile memory (NVM) to allow the customer to set current thresholds  $(I_{THRx})$  parameters, managing the standby on exit strategy.

Limp-home mode is enabled in case of reset of watchdog monitoring time-out event or LH (limp-home) pin is set to high. In this state each output is controlled by dedicated direct inputs (DIx).

DS14248 - Rev 5 page 2/100

# 1 Block diagram and pin description

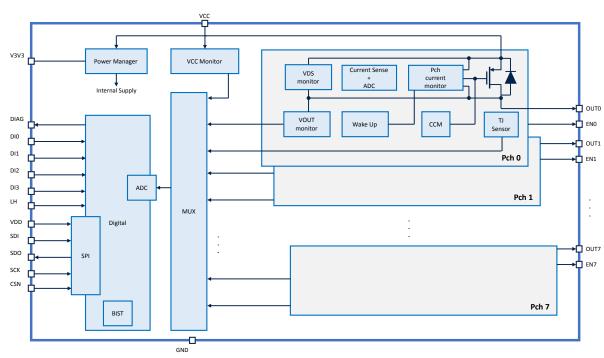

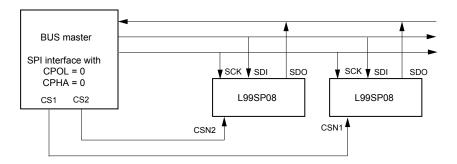

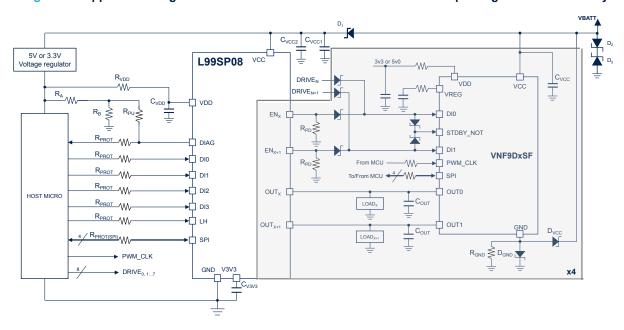

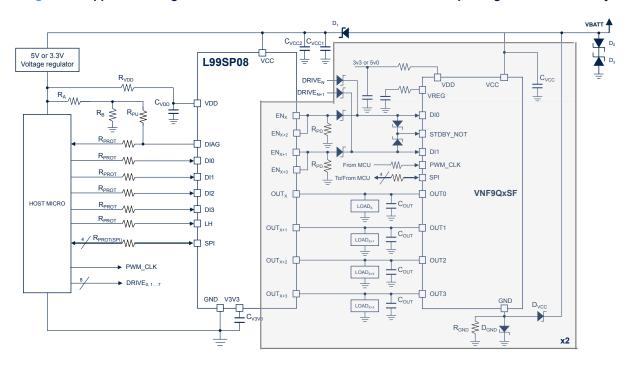

Figure 1. Block diagram

DS14248 - Rev 5 page 3/100

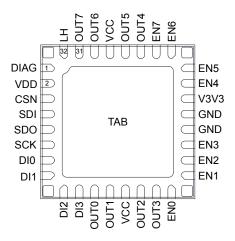

Figure 2. Device pin connection diagram (top through view - not in scale)

Note: the corner leads are electrically connected to the TAB. Those pins are intended for thermo-mechanical purpose only. They have to be soldered, but must be electrically isolated at PCB level.

**Table 1. Pin functions**

| Name | Function                                                                                                         |

|------|------------------------------------------------------------------------------------------------------------------|

| VCC  | Input supply pin. Connect to the 12 V battery voltage                                                            |

| Dlx  | 4 direct inputs for fail-safe operation                                                                          |

| ENx  | Open drain logic outputs, active high. 8 enable pins (1 per channel)                                             |

| OUTx | 8 output pins (1 per channel)                                                                                    |

| GND  | Ground connection                                                                                                |

| VDD  | DC supply input for the SPI interface. 3.3 V and 5 V compatible                                                  |

| V3V3 | Output of the 3.3 V internal LDO voltage regulator (logic and I/O supply)                                        |

| V3V3 | Connect a low ESR capacitor (1 µF) close to this pin                                                             |

| CSN  | Chip select not (active low) for SPI communication. It is the selection pin of the device. CMOS compatible input |

| SDO  | Serial data output for SPI communication. Data is transferred serially out of the device on SCK falling edge     |

| SDI  | Serial data input for SPI communication. Data is transferred serially into the device on SCK rising edge         |

| SCK  | Serial clock for SPI communication. It is a CMOS compatible input                                                |

| DIAG | Open drain logic output, active low. Diagnostic feedback                                                         |

| LH   | Active high input pin compatible with 3 V and 5 V CMOS; it activates limp-home mode                              |

| TAB  | Pin connected to internal ground through high resistive path. To be connect to GND                               |

DS14248 - Rev 5 page 4/100

# 2 Electrical specification

# 2.1 Absolute maximum ratings

Stressing the device above the rating listed in Table 2 may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to the conditions in the table below for extended periods may affect device reliability.

Table 2. Absolute maximum rating

| Symbol                                                   | Parameter                                           | Value                                     | Unit   |

|----------------------------------------------------------|-----------------------------------------------------|-------------------------------------------|--------|

| $V_{CC}$                                                 | DC supply voltage                                   | -0.3 to 40                                | V      |

| I <sub>GND</sub>                                         | DC reverse ground pin current                       | 10                                        | mA     |

| $V_{DD}$                                                 | DC input voltage                                    | -0.3 to 6.5                               | V      |

| V <sub>SDO</sub>                                         | SPI pins DC input voltage                           | -0.3 to V <sub>DD</sub>                   | V      |

| V <sub>3V3</sub>                                         | DC output voltage                                   | -0.3 to 4.6                               | V      |

| V <sub>CSN</sub> , V <sub>SDI</sub> , V <sub>SCK</sub> , | SPI pins DC input voltage                           | -0.3 to 6.5                               | V      |

| $V_{LH}$                                                 | DC input voltage                                    | -0.3 to 40                                | V      |

| $V_{DIAG}$                                               | DC output voltage                                   | -0.3 to V <sub>3v3</sub>                  | V      |

| I <sub>DIAG</sub>                                        | DC input current                                    | 10                                        | mA     |

| V <sub>OUTx</sub>                                        | DC output voltage                                   | (V <sub>CC</sub> - 45) to V <sub>CC</sub> | V      |

| $V_{DIx}$                                                | DC input voltage                                    | -0.3 to 40                                | V      |

| V <sub>ENx</sub>                                         | DC input voltage                                    | -0.3 to V <sub>3V3</sub>                  | V      |

| I <sub>ENx</sub>                                         | DC input current                                    | -10                                       | mA     |

|                                                          | Electrostatic discharge (JEDEC 22A-114F) local pin  | ±2000                                     | V      |

| VESD                                                     | Electrostatic discharge (JEDEC 22A-114F) global pin | ±4000                                     | V      |

| VESD                                                     | Charge device model (CDM-AEC-Q100-011) corner pin   | ±750                                      | V      |

|                                                          | Charge device model (CDM-AEC-Q100-011) all pin      | ±500                                      | V      |

| TJ                                                       | Junction operating temperature                      | -40 to 150                                | °C     |

| T <sub>stg</sub>                                         | Storage temperature                                 | -55 to 150                                |        |

| N <sub>FTP</sub>                                         | Number of FTP writing cycles                        | 1000                                      | Cycles |

## 2.2 Thermal data

Table 3. Thermal data

| Symbol            | Parameter                                                     | Typ. value | Unit |

|-------------------|---------------------------------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance, junction-to-ambient (JEDEC JESD 51-2) (1) | 25.5       | °C/W |

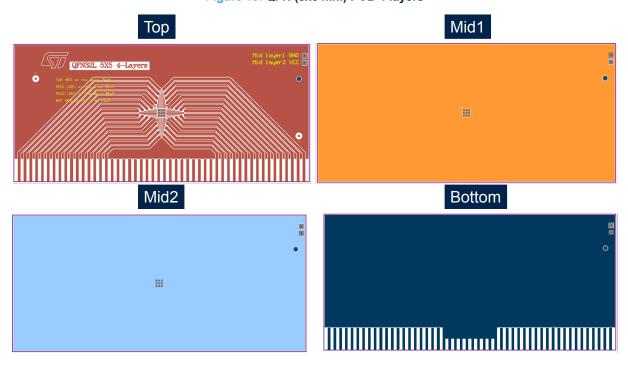

1. Device mounted on four-layer 2s2p PCB.

DS14248 - Rev 5 page 5/100

# 2.3 Main electrical characteristics

5 V <  $V_{CC}$  < 40 V; -40 °C <  $T_J$  < 150 °C, unless otherwise specified. All typical values refer to  $V_{CC}$  = 12 V;  $T_J$  = 25 °C, unless otherwise specified.

Table 4. Supply specification

| ID   | Symbol                   | Parameter                                                                               | Test conditions                                                                                                                | Min. | Тур. | Max. | Unit |

|------|--------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| 1.1  | V <sub>CC</sub>          | Operating supply voltage                                                                |                                                                                                                                | 5    | 12   | 28   | V    |

| 1.2  | V <sub>CC_EXT</sub>      | Extended operating supply voltage                                                       |                                                                                                                                | 3    |      | 40   | V    |

| 1.3  | V <sub>CC_USD</sub>      | Undervoltage shutdown                                                                   |                                                                                                                                | 3.9  |      |      | V    |

| 1.4  | V <sub>CC_USD_RES</sub>  | Undervoltage shutdown reset                                                             |                                                                                                                                |      |      | 4.5  | V    |

| 1.5  | V <sub>CC_USD_HYST</sub> | Undervoltage shutdown hysteresis                                                        |                                                                                                                                |      | 0.3  |      | V    |

| 1.6  | V <sub>CC_OV</sub>       | V <sub>CC</sub> overvoltage                                                             | Normal or fail-safe mode                                                                                                       | 15.6 | 16   | 16.4 | V    |

| 1.7  | V <sub>CC_OV_RES</sub>   | V <sub>CC</sub> overvoltage reset                                                       | Normal or fail-safe mode                                                                                                       | 14.7 | 15.4 | 16.1 | V    |

| 1.8  | V <sub>CC_OV_HYST</sub>  | V <sub>CC</sub> overvoltage hysteresis                                                  | Normal or fail-safe mode                                                                                                       |      | 0.5  |      | V    |

| 1.9  | $V_{DD}$                 | SPI I/Os supply voltage                                                                 |                                                                                                                                | 3    |      | 5.5  | V    |

| 1.10 | V <sub>DD_UV</sub>       | SPI I/Os undervoltage                                                                   |                                                                                                                                | 1.5  | 1.7  | 1.9  | V    |

| 1.11 | V <sub>DD_UV_RES</sub>   | SPI I/Os undervoltage reset                                                             |                                                                                                                                | 1.7  | 2.1  | 2.3  | V    |

| 1.12 | V <sub>DD_UV_HYST</sub>  | SPI I/Os undervoltage hysteresis                                                        |                                                                                                                                |      | 0.4  |      | V    |

| 1.13 | V <sub>V3V3</sub>        | 3.3 V output regulator                                                                  | Normal or fail-safe mode                                                                                                       | 3.1  | 3.25 | 3.4  | V    |

| 1.14 | I <sub>VDD</sub>         | SPI supply current in normal mode                                                       | 1 SPI frame (24-bit)<br>at 1 MHz                                                                                               |      | 1.5  | 3    | mA   |

| 1.15 | I <sub>VDD_Q</sub>       | SPI supply current in standby ON state                                                  |                                                                                                                                | 0.2  | 1    | 3    | μA   |

| 1.16 | I <sub>VCC</sub> ON      | Supply current (includes logic)                                                         | $V_{CC}$ = 12 V, $I_{OUT}$ = 0A<br>$T_{J}$ = 130°C,<br>Normal mode                                                             | 11   | 12   | 13   | mA   |

| 1.17 | I <sub>VCC_Q</sub>       | V <sub>CC</sub> quiescent current (not including I <sub>OUT</sub>                       | $V_{CC}$ = 12 V,<br>all $I_{OUT} \le 30$ mA,<br>$V_{OUT} = V_{Batt}, T_J = 25^{\circ}C$<br>Standby ON mode<br>$V_{CC}$ = 12 V, |      | 35   | 48   | μА   |

|      | _                        | current)                                                                                | all $I_{OUT}$ = 100 mA,<br>$T_J$ = 130°C,<br>Standby on mode                                                                   |      | 1.25 | 1.8  | mA   |

|      |                          |                                                                                         | V <sub>CC</sub> = 12 V,<br>Deep standby mode                                                                                   |      |      | 1    | μA   |

| 1.18 | Іоитх                    | DC output current per channel                                                           | $V_{CC}$ = 12 V, $T_A$ = 85 °C,<br>All channel ON                                                                              |      |      | 300  | mA   |

|      |                          |                                                                                         | $V_{CC}$ = 12 V, $T_A$ = 85 °C,<br>One channel ON                                                                              |      |      | 500  | mA   |

| 1.19 | V <sub>CC_POR_H</sub>    | Power ON reset threshold. Device leaves the Reset mode. Supply of digital part is reset |                                                                                                                                | 2.4  | 2.5  | 2.7  | V    |

DS14248 - Rev 5 page 6/100

| ID   | Symbol                     | Parameter                                                                                 | Test conditions | Min. | Тур. | Max. | Unit |

|------|----------------------------|-------------------------------------------------------------------------------------------|-----------------|------|------|------|------|

| 1.20 | V <sub>CC_POR_L</sub>      | Power ON shutdown threshold. Device enters Reset mode. Supply of digital part in shutdown |                 | 2.2  | 2.3  | 2.5  | V    |

| 1.21 | V <sub>CC_POR_HYST</sub>   | Power ON reset hysteresis                                                                 |                 |      | 0.2  |      | V    |

| 1.22 | V <sub>V3V3_POR_</sub> H   | Power ON digital threshold. Device leaves the Standby ON mode. Digital part is waking up  |                 | 2.7  | 2.85 | 3.0  | V    |

| 1.23 | V <sub>V3V3_POR_L</sub>    | Shutdown digital threshold. Device enters in Standby ON mode. Digital part is frozen      |                 | 2.4  | 2.5  | 2.65 | V    |

| 1.24 | V <sub>V3V3</sub> POR_HYST | Digital part wake up hysteresis                                                           |                 |      | 0.3  |      | V    |

| 1.25 | V <sub>POR_LH_H</sub>      | Power-on wake-up threshold. Device leaves the deep standby state                          |                 | 2.2  | 2.5  | 2.8  | V    |

| 1.26 | V <sub>POR_LH_L</sub>      | Shutdown threshold. Device enters in deep standby state                                   |                 | 2.0  | 2.3  | 2.6  | V    |

| 1.27 | V <sub>POR_LH_HYST</sub>   | Device wake-up hysteresis                                                                 |                 |      | 0.2  |      | V    |

Table 5. SPI logic inputs (CSN, SCK and SDI) specification

| ID  | Symbol                                                                             | Parameter                             | Test conditions   | Min. | Тур. | Max. | Unit |  |  |  |  |  |

|-----|------------------------------------------------------------------------------------|---------------------------------------|-------------------|------|------|------|------|--|--|--|--|--|

|     | V <sub>CC</sub> = 12 V; -40°C < T <sub>J</sub> < 150°C, unless otherwise specified |                                       |                   |      |      |      |      |  |  |  |  |  |

| 2.1 | I <sub>IL_CSN</sub>                                                                | Low level Input current CSN PAD       | CSN = 1.5 V       | -5   | -2.5 | -1   | μA   |  |  |  |  |  |

| 2.2 | I <sub>IH_CSN</sub>                                                                | High level Input current in CSN PAD   | CSN = 2.31 V      | -15  | -10  | -5   | μA   |  |  |  |  |  |

| 2.3 | I <sub>IH_SCK</sub> , SDI                                                          | High level input current SCK, SDI PAD | SCK, SDI = 2.31 V | -15  | -5   | -1   | μA   |  |  |  |  |  |

| 2.4 | I <sub>IL_SCK, SDI</sub>                                                           | Low level input current SCK, SDI PAD  | SCK, SDI = 1.5 V  | 1    | 2.5  | 5    | μA   |  |  |  |  |  |

| 2.5 | V <sub>IL</sub>                                                                    | Low level Input voltage               |                   |      |      | 1.35 | V    |  |  |  |  |  |

| 2.6 | V <sub>IH</sub>                                                                    | High level input voltage              |                   | 2.3  |      |      | V    |  |  |  |  |  |

| 2.7 | V <sub>I_HYST</sub>                                                                | Input hysteresis voltage              |                   |      | 0.4  |      | V    |  |  |  |  |  |

Table 6. SPI logic outputs (SDO) specification

| ID                                                                                 | Symbol          | Parameter                 | Test conditions | Min.                | Тур. | Max.                | Unit |  |  |  |  |

|------------------------------------------------------------------------------------|-----------------|---------------------------|-----------------|---------------------|------|---------------------|------|--|--|--|--|

| V <sub>CC</sub> = 12 V; -40°C < T <sub>J</sub> < 150°C, unless otherwise specified |                 |                           |                 |                     |      |                     |      |  |  |  |  |

| 3.1                                                                                | V <sub>OL</sub> | Low level output voltage  |                 |                     |      | 0.2*V <sub>DD</sub> | V    |  |  |  |  |

| 3.2                                                                                | V <sub>OH</sub> | High level output voltage |                 | 0.8*V <sub>DD</sub> |      |                     | V    |  |  |  |  |

| 3.3                                                                                | I <sub>LO</sub> | Output leakage current    |                 |                     |      | 1                   | μA   |  |  |  |  |

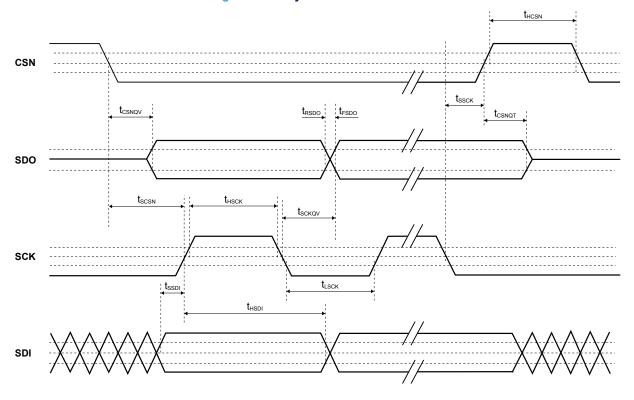

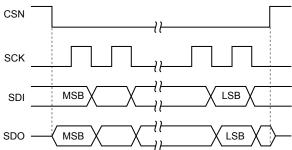

Table 7. SPI timing specification

| ID  | Symbol            | Parameter                                     | Test conditions | Min. | Тур. | Max. | Unit |

|-----|-------------------|-----------------------------------------------|-----------------|------|------|------|------|

| 4.1 | f <sub>SCK</sub>  | SPI clock frequency                           |                 | -    | -    | 8    | MHz  |

| 4.2 | t <sub>HSCK</sub> | SCK high time                                 |                 | 55   | -    | -    | ns   |

| 4.3 | t <sub>LSCK</sub> | SCK low time                                  |                 | 55   | -    | -    | ns   |

| 4.4 | t <sub>HCSN</sub> | CSN high time                                 |                 | 1    | -    | -    | μs   |

| 4.5 | t <sub>SCSN</sub> | CSN setup time-CSN low before SCK rising edge |                 | 100  | -    | -    | ns   |

| 4.6 | t <sub>SSCK</sub> | SCK setup time–SCK low before CSN rising edge |                 | 100  | -    | -    | ns   |

DS14248 - Rev 5 page 7/100

| ID   | Symbol             | Parameter                                     | Test conditions        |    | Min. | Тур.    | Max. | Unit |

|------|--------------------|-----------------------------------------------|------------------------|----|------|---------|------|------|

| 4.7  | t <sub>SSDI</sub>  | SDI setup time before SCK rising edge         |                        |    | 25   | -       | -    | ns   |

| 4.8  | t <sub>HSDI</sub>  | SDI hold time                                 |                        |    | 20   | -       | -    | ns   |

| 4.9  | t <sub>CSNQV</sub> | CSN falling edge until SDO valid              |                        |    | -    | -       | 70   | ns   |

| 4.10 | t <sub>CSNQT</sub> | CSN rising edge until SDO tristate            |                        |    | -    | 220     | -    | ns   |

| 4.11 | t <sub>SCKQV</sub> | SCK falling edge until SDO valid              |                        |    | -    | -       | 50   | ns   |

| 4.12 | t <sub>RSDO</sub>  | SDO rise time                                 |                        |    | -    | -       | 25   | ns   |

| 4.13 | t <sub>FSDO</sub>  | SDO fall time                                 |                        |    | -    | -       | 25   | ns   |

| 4.14 | twhch              | CSN low timeout                               |                        |    | -10% | 50      | +10% | ms   |

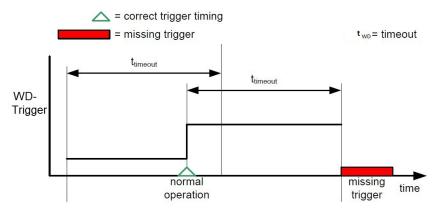

|      |                    |                                               | WD_TIME configuration: | 00 |      | 50      |      |      |

| 4.15 | t                  | Watchdog toggle hit timeout                   |                        | 01 | -10% | 100     | +10% | ms   |

| 4.13 | WDTB               | t <sub>WDTB</sub> Watchdog toggle bit timeout |                        | 10 |      | 150     |      |      |

|      |                    |                                               |                        |    | Г    | Disable | ed   | -    |

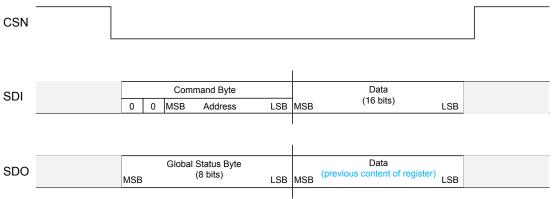

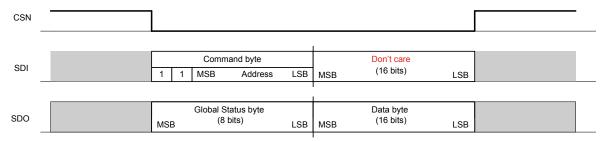

Figure 3. SPI dynamic characteristics

$t_{\text{HCSN}}$

: CSN high time : CSN falling until SDO valid : SDO fall time  $t_{\text{CSNQV}}$

$t_{\text{RSDO}}$  $t_{\text{FSDO}}$

: SDO fall time

: SDO rise time

: SCK setup time before CSN rising

: CSN rising until SDO tristate

: CSN setup time before SCK rising

: SCK high time

: SCK falling until SDO valid

: SDI setup time before SCK rising

: SDI hold time

: SCK low time  $t_{\text{SSCK}}$  $t_{CSNQT}$  $t_{\text{\tiny SCSN}}$

$t_{\mathsf{HSCK}}$

$t_{\text{SCKQV}}$ t<sub>SSDI</sub>

$t_{\mathsf{HSDI}}$  $t_{\mathsf{LSCK}}$

DS14248 - Rev 5 page 8/100

# Table 8. ENx pin specification

| ID                                                                                 | Symbol                | Parameter                                 | Test conditions                        | Min. | Тур. | Max. | Unit |  |  |  |

|------------------------------------------------------------------------------------|-----------------------|-------------------------------------------|----------------------------------------|------|------|------|------|--|--|--|

| V <sub>CC</sub> = 12 V; -40°C < T <sub>J</sub> < 150°C, unless otherwise specified |                       |                                           |                                        |      |      |      |      |  |  |  |

| 5.1                                                                                | $V_{ENx\_PU}$         | Channel x enable pin - pull up voltage    |                                        | 3    |      |      | V    |  |  |  |

| 5.2                                                                                | I <sub>ENx_CC</sub>   | Channel x enable pin – current capability | V <sub>ENX</sub> = V <sub>ENX_PU</sub> |      |      | 300  | μA   |  |  |  |

| 5.3                                                                                | I <sub>ENx_LEAK</sub> | Channel x enable pin - leakage current    |                                        |      |      | 1    | μA   |  |  |  |

## Table 9. Dlx pin specification

| ID  | Symbol              | Parameter                                               | Test conditions            | Min. | Тур. | Max. | Unit |

|-----|---------------------|---------------------------------------------------------|----------------------------|------|------|------|------|

|     |                     | V <sub>CC</sub> = 12 V; -40°C < T <sub>J</sub> < 150°C, | unless otherwise specified |      |      |      |      |

| 6.1 | I <sub>IL</sub>     | Low level Input current                                 | DIx = 1.5 V                | 1    | 2.5  | 5    | μA   |

| 6.2 | I <sub>IH</sub>     | High level Input current                                | DIx = 2.31 V               | -10  | -5   | -1   | μA   |

| 6.3 | V <sub>IL</sub>     | Low level input voltage                                 |                            |      |      | 1.35 | V    |

| 6.4 | V <sub>IH</sub>     | High level input voltage                                |                            | 2.3  |      |      | V    |

| 6.5 | V <sub>I_HYST</sub> | Input hysteresis voltage                                |                            |      | 0.4  |      | V    |

# Table 10. Digital timings specification

| ID  | Symbol                       | Parameter                                                                                       | Test conditions                                                                                                                                                     | Min. | Тур. | Max. | Unit |

|-----|------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|     |                              | V <sub>CC</sub> = 12 V; -40°C < T <sub>C</sub>                                                  | < 150°C, unless otherwise specified                                                                                                                                 |      |      |      |      |

| 7.1 | f <sub>C</sub>               | Clock frequency                                                                                 | Dithering configuration = 000 (see Table 20)                                                                                                                        | 19   | 20   | 21   | MHz  |

| 7.2 | t <sub>WHCH</sub>            | CSN low timeout                                                                                 | Covered by SCAN                                                                                                                                                     |      | 50   |      | ms   |

| 7.3 | tsтву_оит                    | Minimum time during which<br>CSN must be low or LH<br>must be high to exit<br>Standby ON mode   |                                                                                                                                                                     | 1    | 5    | 10   | μs   |

| 7.4 | tstby_in                     | Minimum time during which<br>CSN must be high and LH<br>must be low to go to<br>Standby ON mode | Covered by SCAN                                                                                                                                                     |      | 14   |      | ms   |

| 7.5 | tstartup                     | Startup time from initialization to Standby ON                                                  | $V_{CC} > V_{CC\_POR\_H}$ ,<br>V3V3 external cap. = 1 $\mu$ F,<br>LH > $V_{POR\_LH\_H}$                                                                             |      |      | 1.2  | ms   |

| 7.6 | t <sub>STBY_LOW_to_MID</sub> | Transition time from<br>Standby ON low to high<br>consumption                                   | I <sub>OUT</sub> > I <sub>STBYON_TH_H</sub>                                                                                                                         | 150  | 300  | 550  | μs   |

| 7.7 | tstby_low_to_fs              | Transition time from<br>Standby ON low<br>consumption to fail-safe                              | V3V3 external cap. = 1 µF,  (I <sub>OUT</sub> > I <sub>Peak</sub> OR I <sub>OUT</sub> < I <sub>STDBY_ON_TH_H</sub> )  OR  (LH "high" OR CSN "low" OR VDS_OV "high") | 150  | 350  | 550  | μs   |

| 7.8 | tstby_mid_to_fs              | Transition time from<br>Standby ON high<br>consumption to fail-safe                             | V3V3 external cap. = 1 µF, (I <sub>OUT</sub> > I <sub>Peak</sub> OR I <sub>OUT</sub> > I <sub>STDBY_ON_TH_H</sub> ) OR                                              | 10   | 25   | 40   | μs   |

DS14248 - Rev 5 page 9/100

| ID   | Symbol                 | Parameter                                                    | Test conditions                                                                          | Min. | Тур. | Max. | Unit |

|------|------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

|      |                        |                                                              | (LH "high" OR CSN "low" OR TSD "high")                                                   |      |      |      |      |

|      |                        |                                                              | V3V3 external cap. = 1 μF,                                                               |      |      |      |      |

| 7.0  |                        | Transition time from                                         | (I <sub>OUT</sub> > I <sub>Peak</sub> OR I <sub>OUT</sub> > I <sub>STDBY_ON_TH_H</sub> ) |      |      |      |      |

| 7.8  | tSTBY_MID_to_FS        | Standby ON high consumption to fail-safe                     | OR                                                                                       | 0.1  | 0.5  | 1    | μs   |

|      |                        | ·                                                            | (LH "high" OR CSN "low" OR TSD "high")                                                   | 0.1  | 0.5  | '    |      |

|      |                        |                                                              | AND                                                                                      |      |      |      |      |

|      |                        |                                                              | V3V3 > V3V3_POR_H                                                                        |      |      |      |      |

| 7.9  | t <sub>MAX</sub>       | Digital counter to manage<br>the standby ON exit<br>strategy |                                                                                          | 0    |      | 255  | ms   |

| 7.10 | t <sub>NVM_READ</sub>  |                                                              | Covered by SCAN                                                                          | 30   |      |      | μs   |

| 7.11 | t <sub>NVM_WRITE</sub> |                                                              | Covered by SCAN                                                                          | 10   |      |      | ms   |

|      |                        |                                                              | Standby ON - low consumption mode,                                                       | 3    |      | 5    |      |

| 7.12 | t <sub>ENhigh</sub>    | ENx delay from fault rise                                    | no exsternal resistive load on ENx pin                                                   |      |      | 1    | μs   |

| 1.12 | *EINHIGH               | time                                                         | All states except standby ON - low consumption mode,                                     | 0.05 |      |      | μο   |

|      |                        |                                                              | no exsternal resistive load on ENx pin                                                   |      |      |      |      |

Table 11. LH logic input pin specification

| ID  | Symbol                                                                             | Parameter                | Test conditions          | Min. | Тур. | Max. | Unit |  |  |

|-----|------------------------------------------------------------------------------------|--------------------------|--------------------------|------|------|------|------|--|--|

|     | V <sub>CC</sub> = 12 V; -40°C < T <sub>J</sub> < 150°C, unless otherwise specified |                          |                          |      |      |      |      |  |  |

| 8.1 | I <sub>IL</sub>                                                                    | Low level Input current  | V <sub>IL</sub> = 1.5 V  | 1    |      |      | μA   |  |  |

| 8.2 | I <sub>IH</sub>                                                                    | High level Input current | V <sub>IH</sub> = 2.31 V |      |      | 15   | μA   |  |  |

| 8.3 | V <sub>IL</sub>                                                                    | Low level Input voltage  |                          |      |      | 1.5  | V    |  |  |

| 8.4 | V <sub>IH</sub>                                                                    | High level input voltage |                          | 2.31 |      |      | V    |  |  |

| 8.5 | V <sub>I_HYST</sub>                                                                | Input hysteresis voltage |                          |      | 0.4  |      | V    |  |  |

| 8.6 | t <sub>LH</sub>                                                                    | LH filtering time        |                          |      | 32   |      | μs   |  |  |

Table 12. DIAG logic output pin specification

| ID  | Symbol                 | Parameter                                        | Test conditions            | Min. | Тур. | Max. | Unit |

|-----|------------------------|--------------------------------------------------|----------------------------|------|------|------|------|

|     |                        | $V_{CC}$ = 12 V; -40°C < T <sub>J</sub> < 150°C, | unless otherwise specified |      |      |      |      |

| 9.1 | $V_{DIAG\_PD}$         | DIAG pin pull down voltage                       | I <sub>DIAG_PD</sub> = 1mA |      | -    | 0.25 | V    |

| 9.2 | I <sub>DIAG_PD</sub>   | DIAG pin input current                           | $V_{DIAG} = V_{DIAG\_PD}$  |      | -    | 1    | mA   |

| 9.3 | I <sub>DIAG_LEAK</sub> | DIAG pin leakage current                         | V <sub>DIAG</sub> = V3V3   | 0    | -    | 1    | μA   |

Table 13. Thermal specification

| ID   | Symbol                                                                             | Parameter                                       | Test conditions | Min. | Тур. | Max. | Unit |

|------|------------------------------------------------------------------------------------|-------------------------------------------------|-----------------|------|------|------|------|

|      | V <sub>CC</sub> = 12 V; -40°C < T <sub>J</sub> < 150°C, unless otherwise specified |                                                 |                 |      |      |      |      |

| 10.1 | T <sub>TSD</sub>                                                                   | Junction temperature thermal shutdown threshold |                 | 160  | 175  | 190  | °C   |

DS14248 - Rev 5 page 10/100

| ID   | Symbol               | Parameter                                        | Test conditions | Min. | Тур. | Max. | Unit |

|------|----------------------|--------------------------------------------------|-----------------|------|------|------|------|

| 10.2 | T <sub>TSD_HYS</sub> | Junction temperature thermal shutdown hysteresis |                 |      | 15   |      | °C   |

| 10.3 | T <sub>W</sub>       | Junction temperature thermal warning threshold   |                 |      | 140  |      |      |

Table 14. Current sense amplifier with integrated ADC

| ID   | Symbol                            | Parameter                                                   | Test conditions                   | Min. | Тур.          | Max. | Unit |

|------|-----------------------------------|-------------------------------------------------------------|-----------------------------------|------|---------------|------|------|

|      | ,                                 | / <sub>CC</sub> = 12 V; -40°C < T <sub>J</sub> < 150°C, unl | ess otherwise specified           |      |               |      |      |

| 11.1 | ADC <sub>RES_IOUTx</sub>          | ADC resolution                                              |                                   |      | 10            |      | bit  |

| 11.2 | ADC <sub>REFRESH_RATE_IOUTx</sub> | ADC refresh rate                                            |                                   |      | 3.3           |      | μs   |

| 11.3 | ADC <sub>FS</sub>                 | ADC full scale for I <sub>OUTx</sub>                        |                                   |      | 0.55          |      | Α    |

| 11.4 | ADC <sub>STEP_IOUTx</sub>         | ADC step for I <sub>OUTx</sub>                              |                                   |      | 0.55/<br>1023 |      | Α    |

| 11.5 | ADC_FS_DIAG                       | ADC full scale for I <sub>OUTx</sub> in leak mode           |                                   |      | 37            |      | mA   |

| 11.6 | ADC_STEP_DIAG                     | ADC step for I <sub>OUTx</sub> in leak mode                 |                                   |      | 37/<br>1023   |      | mA   |

|      |                                   |                                                             | 0.04 A ≤ I <sub>OUT</sub> < 0.1 A | -20  |               | 20   | %    |

| 11.7 | C <sub>S_PRECISION</sub>          | Digital current sense accuracy                              | 0.1 A ≤ I <sub>OUT</sub> < 0.2 A  | -10  |               | 10   | %    |

|      |                                   |                                                             | 0.2 A ≤ I <sub>OUT</sub> < 0.5 A  | -5   |               | +5   | %    |

|      |                                   |                                                             | 1 mA < I <sub>OUT</sub> < 5 mA    | -35  |               | 35   | %    |

| 11.8 | C <sub>S_PRECISION_DIAG</sub>     |                                                             | 5 mA ≤ I <sub>OUT</sub> < 10 mA   | -10  |               | 10   | %    |

|      |                                   |                                                             | 10 mA ≤ I <sub>OUT</sub> < 37 mA  | -8   |               | 8    | %    |

Table 15. P-channel bypass switch specification

| ID   | Symbol                     | Parameter                                                                | Test conditions                                                                             | Min. | Тур. | Max. | Unit |

|------|----------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|------|------|------|

|      |                            | V <sub>CC</sub> = 12 V; -40°C < T <sub>J</sub> < 150°C                   | C, unless otherwise specified                                                               |      |      |      |      |

| 12.1 | V <sub>DS_BYPASS_SAT</sub> | Bypass switch V <sub>DS</sub> saturation protection threshold            |                                                                                             | 0.4  |      | 1.2  | V    |

| 12.2 | R <sub>ON</sub>            | Internal bypass resistance                                               | T <sub>J</sub> = 25°C                                                                       | 0.7  | 1    | 1.3  | Ω    |

| 12.3 | R <sub>ON_STBY_LC</sub>    | Internal bypass resistance in Standby ON low consumption                 | T <sub>J</sub> = 25°C                                                                       | 7    | 14   | 16   | Ω    |

| 12.4 | I <sub>STBYON_TH_</sub> H  | Current threshold for transition from Standby ON low to high consumption | V <sub>S</sub> - V <sub>OUT</sub> = V <sub>DS_BYPASS_SAT</sub> , Standby ON low consumption | 30   |      | 85   | mA   |

|      |                            |                                                                          | Standby on state,<br>T <sub>J</sub> = -40 °C                                                | 0.8  |      | 1.2  |      |

| 12.5 | I <sub>PEAK_STBY</sub>     | Peak current                                                             | Standby on state,<br>T <sub>J</sub> = 25 °C                                                 | 0.6  |      | 0.9  | Α    |

|      |                            |                                                                          | Standby on state,<br>T <sub>J</sub> = 130 °C                                                | 0.5  |      | 0.7  |      |

| 12.6 | I <sub>STBYON_TH_L</sub>   | Output current to go in Standby ON low consumption state                 |                                                                                             | 8    | 15   | 25   | mA   |

| 12.7 | I <sub>THRx</sub>          | Output current threshold                                                 |                                                                                             | -10% | 100  | 10%  | mA   |

DS14248 - Rev 5 page 11/100

| ID   | Symbol            | Parameter                                | Test conditions          | Min. | Тур. | Max. | Unit |

|------|-------------------|------------------------------------------|--------------------------|------|------|------|------|

|      |                   |                                          |                          | -10% | 200  | 10%  |      |

| 12.7 | I <sub>THRx</sub> | Output current threshold                 |                          | -10% | 300  | 10%  | mA   |

|      |                   |                                          |                          | -10% | 400  | 10%  |      |

| 12.8 | I <sub>PEAK</sub> | Peak current in normal or fail-safe mode | Normal or fail-safe mode | -5%  | 500  | 5%   | mA   |

## Table 16. Overvoltage specification

| ID   | Symbol                 | Parameter                                                           | Test conditions   | Min. | Тур. | Max. | Unit |

|------|------------------------|---------------------------------------------------------------------|-------------------|------|------|------|------|

|      |                        | $V_S$ = 12 V; -40°C < $T_J$ < 150°C, unless other                   | nerwise specified |      |      |      |      |

| 13.1 | V <sub>DS_OV_L</sub>   | Drain-source overvoltage threshold-rising edge of V <sub>OUT</sub>  |                   | 1.3  | 1.4  | 1.5  | V    |

| 13.2 | V <sub>DS_OV_H</sub>   | Drain-source overvoltage threshold-falling edge of V <sub>OUT</sub> |                   | 1.9  | 2.1  | 2.3  | V    |

| 13.3 | V <sub>DSOV_HYST</sub> |                                                                     |                   |      | 700  |      | mV   |

# Table 17. Capacitive Charging Mode (CCM) Specification

| ID   | Symbol                | Parameter                                                     | Test conditions            | Min. | Тур. | Max. | Unit |

|------|-----------------------|---------------------------------------------------------------|----------------------------|------|------|------|------|

|      |                       | V <sub>S</sub> = 12 V; -40°C < T <sub>J</sub> < 150°C, unless | otherwise specified        |      |      |      |      |

| 14.1 | I <sub>OUT_CCM</sub>  | Output current in CCM                                         | V <sub>OUT</sub> = 0 V     | 12   | 20   | 25   | mA   |

| 14.2 | toou                  | Time to charge OUT voltage to V <sub>CC</sub>                 | C <sub>OUT</sub> = 180 μF, |      |      | 200  | ms   |

| 14.2 | 14.2 t <sub>CCM</sub> |                                                               | V <sub>CC</sub> = 16V      |      |      | 200  | 1115 |

# Table 18. Voltage and temperature monitoring with integrated ADC

| ID   | Symbol                      | Parameter                                                  | Test conditions                                 | Min. | Тур. | Max. | Unit |

|------|-----------------------------|------------------------------------------------------------|-------------------------------------------------|------|------|------|------|

|      |                             | V <sub>CC</sub> = 13 V; -40°C < T <sub>J</sub> < 150°C, ur | nless otherwise specified                       |      |      |      |      |

| 15.1 | ADC <sub>RES</sub>          | ADC resolution                                             |                                                 |      | 10   |      | bit  |

| 15.2 | ADC <sub>REFRESH_RATE</sub> | ADC refresh rate                                           |                                                 |      | 47.6 |      | μs   |

| 15.3 | ADC <sub>FS_VOUTx</sub>     | ADC full scale for V <sub>OUTx</sub>                       |                                                 |      | 25   |      | V    |

| 15.4 | ADC <sub>STEP_VOUTx</sub>   | ADC step for V <sub>OUTx</sub>                             |                                                 |      | 24.5 |      | mV   |

| 15.5 | ADC <sub>FS_Vcc</sub>       | ADC full scale for V <sub>CC</sub>                         |                                                 |      | 25   |      | V    |

| 15.6 | ADC <sub>STEP_Vcc</sub>     | ADC step for V <sub>CC</sub>                               |                                                 |      | 24.5 |      | mV   |

| 15.7 | ADC <sub>FS_Tjx</sub>       | ADC full scale for T <sub>JX</sub>                         |                                                 |      | 2.5  |      | V    |

| 15.8 | ADC <sub>STEP_Tjx</sub>     | ADC step for T <sub>JX</sub>                               |                                                 |      | 2.45 |      | mV   |

| 15.9 | ADC <sub>ACCURACY</sub>     | ADC reading accuracy                                       | $V_{OUTx} \ge 1.5V$ $V_{CC} \ge V_{CC\_POR\_L}$ | -5   |      | 5    | %    |

DS14248 - Rev 5 page 12/100

# 3 Functional description

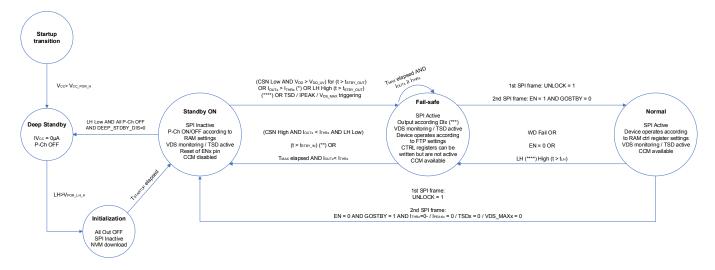

Figure 4. Device state diagram

#### NOTES:

- (\*) Only if transition from standby on to fail-safe is triggered by the following condition:  $I_{THRx} < I_{OUTx} < I_{PEAK}$ , then  $T_{MAX}$  timer is enabled.

- (\*\*)  $t_{\text{STBY\_IN}}$  timer is reset if  $T_{\text{MAX}}$  timer is enabled.

- (\*\*\*) Output according to OUT\_CTRL if T<sub>MAX</sub> time is enabled.

- (\*\*\*\*) If NVM bit DEEP\_STDBY\_DIS = 1, the contribution of LH signal to this transition of the device FSM is disabled.

# 3.1 Operating modes

The L99SP08 features different operating modes:

- Deep standby on mode

- Standby on mode

- Normal mode

- Fail-safe mode

Nevertheless, there is a transition startup phase which is not an operation mode for the device.

When the voltage on VCC pin exceeds the power on or reset threshold ( $V_{CC\_POR\_H}$ ) and LH >  $V_{POR\_LH\_H}$ , the device enters in the initialization phase, during which:

- the FTP registers values are downloaded into corresponding RAM registers

- · the internal bypass switches are OFF

The transition to standby ON state is triggered after the end of FTP download (t<sub>STARTUP</sub>).

DS14248 - Rev 5 page 13/100

Table 19. Operating modes

| Operating<br>mode                                                    | Entering conditions                                                                                                                                                                                                               | Leaving conditions                                                                                                                                                                                                | Characteristics                                                                                                                                                                  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Startup<br>transition<br>(Not considered<br>as an operating<br>mode) |                                                                                                                                                                                                                                   | Deep Standby:<br>V <sub>CC</sub> > 0                                                                                                                                                                              |                                                                                                                                                                                  |

| Deep standby mode  Initialization (Not considered                    | Startup transition:  V <sub>CC</sub> > 0  Standby on:  LH low AND all P-channel off AND  DEEP_STDBY_DIS = 0  Deep Standby:                                                                                                        | Initialization:  LH > V <sub>POR_LH_H</sub> Standby on:                                                                                                                                                           | <ul> <li>Outputs: off</li> <li>SPI: inactive</li> <li>Diagnostics: not available</li> <li>IV<sub>CC</sub> = 0 μA</li> <li>Outputs: off</li> <li>SPI: inactive</li> </ul>         |

| as an operating mode)                                                | LH > V <sub>POR_LH_H</sub>                                                                                                                                                                                                        | T <sub>STARUP</sub> elapsed                                                                                                                                                                                       | SPI: inactive     NVM download                                                                                                                                                   |

| Standby ON                                                           | Initialization:  T <sub>STARTUP</sub> elapsed  Fail-safe:  (CSN high AND I <sub>OUTx</sub> < I <sub>THRx</sub> and LH low) (t > t <sub>STBY_IN</sub> ) (**) OR T <sub>MAX</sub> elapsed AND I <sub>OUTx</sub> < I <sub>THRx</sub> | Deep standby:  LH low AND all P-channel off AND  DEEP_STDBY_DIS = 0                                                                                                                                               | SPI: inactive     P-channel on/off according to RAM settings                                                                                                                     |

| Standby ON<br>mode                                                   | Normal:<br>1stSPI frame:<br>UNLOCK = 1<br>2nd SPI frame:<br>EN = 0 AND GOSTBY = 1 AND I <sub>THRX</sub> =<br>0- / IPEAKx = 0 / TSDx = 0 /<br>VDS_MAXx = 0                                                                         | Fail-safe:  CSN low (t > t <sub>STBY_OUT</sub> ) OR  I <sub>OUTx</sub> > I <sub>THRx</sub> (*) OR  LH high (t > t <sub>STBY_OUT</sub> ) (****) OR  TSD / IPEAK / VDS_MAX triggering                               | VDS monitoring/TSD active     Reset of ENx pin     CCM disabled                                                                                                                  |

| Fail-safe                                                            | Standby on:  CSN Low (t > t <sub>STBY_OUT</sub> ) OR  I <sub>OUTx</sub> > I <sub>THRx</sub> (*) OR  LH High (t > t <sub>STBY_OUT</sub> ) (****) OR  TSD/IPEAK/VDS_MAX triggering  Normal:                                         | Standby on:  (CSN High AND I <sub>OUTx</sub> < I <sub>THRx</sub> and LH Low) (t > t <sub>STBY_IN</sub> ) (**) OR  T <sub>MAX</sub> elapsed AND I <sub>OUTx</sub> <i<sub>THRx  Normal:</i<sub>                     | SPI: inactive     Output according to DIx (***)     VDS monitoring/TSD active     Device operates according to FTP settings     CTRL registers can be written but are not active |

|                                                                      | WD fail OR $EN = 0 \text{ OR}$ $LH(****) \text{ high } (t > t_{LH})$                                                                                                                                                              | 1st SPI frame:<br>UNLOCK = 1<br>2nd SPI frame:<br>EN = 1 AND GOSTBY = 0                                                                                                                                           | • CCM available • Reset =1 after SW reset                                                                                                                                        |

| Normal                                                               | Fail-safe:  1st SPI frame: UNLOCK = 1  2nd SPI frame: EN = 1 AND GOSTBY = 0                                                                                                                                                       | Standby on:  1st SPI frame: UNLOCK=1  2nd SPI frame: EN = 0 AND GOSTBY = 1 AND I <sub>THRX</sub> =0- / IPEAKx = 0 / TSDx = 0 / VDS_MAXx = 0  Fail-safe: WD fail OR EN = 0 OR LH(****) high (t > t <sub>LH</sub> ) | SPI Active     Device operates according to RAM CTRL register settings     VDS monitoring/TSD active     CCM available                                                           |

DS14248 - Rev 5 page 14/100

#### 3.1.1 Deep standby mode

The deep standby mode is a state with the following characteristics:

- The device consumption is below 1 μA;

- NO SPI response;

- NO device features are available;

The device enters this state:

From startup:

V<sub>CC</sub> > V<sub>CCPOR H</sub>

From standby ON:

LH < V<sub>POR LH L</sub> AND (ALL P-Channel OFF) AND (DEEP\_STDBY\_DIS = 0)

The device leaves this state:

• LH >  $V_{POR\ LH\ H}$  for t > 600  $\mu s$

If LH is maintained  $> V_{POR\ LH\ H}$  for t  $> T_{startup}$  the device enters automatically in fail-safe.

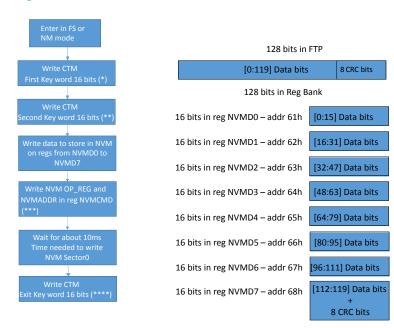

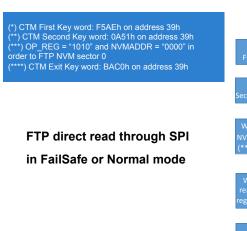

#### 3.1.2 Standby on mode

The L99SP08 device features a standby on operation mode, with the following characteristics:

- The SPI interface is inactive—the digital part is supplied (but the clock is off) and the registers are frozen to the latest state:

- the bypass switches can be on or off depending on dedicated BIT on control register CR3 "Output control Register";

- The capacitive charging mode is disabled;

- The bypass drain-source voltage and the junction temperature are monitored to ensure the device protected while keeping the lowest current consumption from the supply voltage.

The device enters this state:

- From initialization phase, after the FTP download (and within t<sub>STARTUP</sub> timing);

- From normal mode by sending two dedicated SPI frames (see Figure 4):

- First SPI frame: 02x0009

- Second SPI frame: 01x8001

- · From fail-safe when:

- CSN goes high for t> t<sub>STBY IN</sub> AND

- I<sub>OUTX</sub> < I<sub>THRX</sub> (for all the output currents) AND

- LH goes low for t> t<sub>STBY IN</sub>

The standby ON exit strategy is deeply described in the Section 3.2: Standby on state exit strategy.

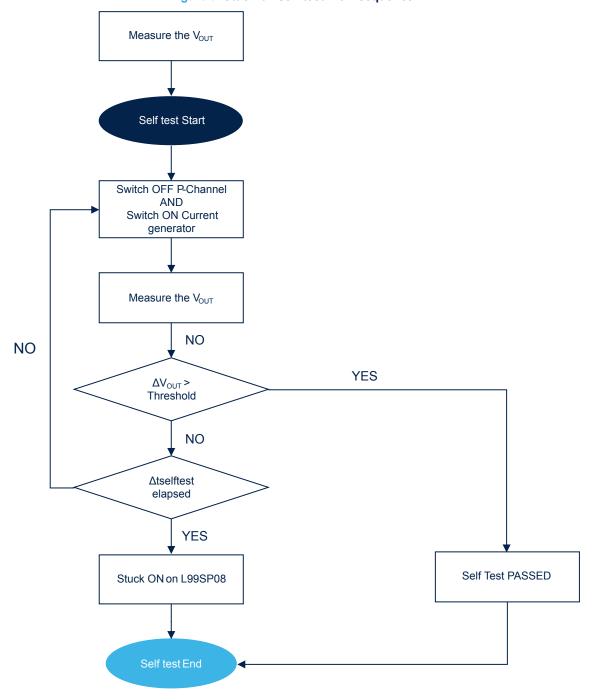

#### 3.1.3 Fail-safe mode

The device enters the fail-safe operation from standby ON if:

- If CSN goes low for a time t> t<sub>STBY OUT</sub> OR

- If I<sub>OUTX</sub>>I<sub>THRX</sub> (it is enough the current of one channel only is higher than its configured threshold) OR

- If LH goes high a time t> t<sub>STBY OUT</sub> AND DEEP\_STDBY\_DIS = 1 OR

- If a fault occurs in at least one channel:

- Goes in thermal shutdown (TSDx is triggered)

- The drain-source voltage of the P-channel bypass is exceeding a fixed threshold (V<sub>DSMAXx</sub> is triggered)

- The output current overcome the Ipeak fixed threshold (I<sub>PEAKX</sub> is triggered)

When the device enters from standby ON to fail-safe mode, the DIAG goes down for 1 ms. In case of transition triggered from a fault the DIAG is latched down.

The device enters the fail-safe operation from normal mode when:

- WD\_FAIL bit set (the microcontroller connection is lost, and the watchdog is not anymore served) OR

- EN bit is set to 0, OR

DS14248 - Rev 5 page 15/100

LH pin is set in high state.

The fail-safe state characteristics are:

- SPI active with control registers locked and values corresponding to the latest ones;

- · Capacitive charging mode enabled;

- Bypass switches handled according to the direct inputs (4x Dlx);

- Diagnostic active.

#### 3.1.4 Normal mode

The device enters the normal operation, only from fail-safe, through two dedicated SPI frames (see Figure 4):

- First SPI frame: 02x0009

- Second SPI frame: 01x4001

The characteristics of the normal mode are:

- SPI active (until the watchdog, regularly toggled, is served);

- Capacitive charging mode is enabled;

- Bypass switches handled according to the values stored in the dedicated registers or to the direct inputs (4x DI<sub>x</sub> in total);

- · Diagnostic active.

If NVM bit DEEP\_STDBY\_DIS = 0, the L99SP08 leaves the normal mode to enter the fail-safe under the following conditions:

- · WD FAIL bit set (the microcontroller connection is lost, and the watchdog is not anymore served) OR

- EN bit is set to 0, OR

- LH pin is set in high state.

The normal mode leaving conditions to enter the standby ON state are managed by sending two dedicated SPI frames (see Figure 4).

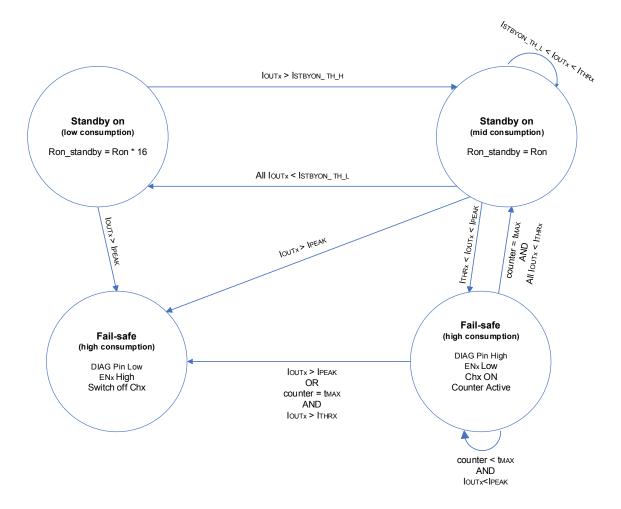

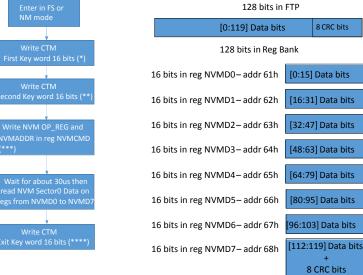

#### 3.2 Standby on state exit strategy

The standby on is a key state for the L99SP08. This section is dedicated to the strategy implemented to leave this device operation.

The standby on is the state during which the L99SP08 delivers the required current to the outputs.

The key requirement in this phase is to minimize the current consumption from the supply voltage. Then, this state can be split in two sub states, depending on the IOUTx values (see Figure 5): the first one with a very low consumption (see  $I_{VCC\ Q}$ ); the second one, with medium consumption (see  $I_{VCC\ Q}$ ).

The transition between these two phases, is handled according to the current required by the output: if below than  $I_{STBYON\_TH\_L}$ , the device is in low consumption sub state, then if the current is above than  $I_{STBYON\_TH\_H}$ , the device moves to standby on high consumption sub state.

The L99SP08 leaves the standby on state when the channel output current is exceeding the configurable threshold (per channel) I<sub>THRx</sub>.

In that case, the device goes in fail-safe and a digital counter starts counting until a configurable  $t_{MAX}$  timing. When the programmed  $t_{MAX}$  is reached, the L99SP08 compares the output current  $l_{OUTx}$  against the  $l_{THRx}$  threshold:

- If the output current I<sub>OUTx</sub> is higher than the threshold I<sub>THRx</sub>, the enable pin (ENx) of the channel x is raised, and the relative P-channel is switched OFF. Meanwhile, the DIAG pin is pulled down;

- If the output current I<sub>OUTx</sub> is lower than the threshold I<sub>THRx</sub>: the channel x come back to standby on state (see Figure 5).

DS14248 - Rev 5 page 16/100

Figure 5. Standby on exit strategy

## 3.3 Channel enable (ENx) pin behavior

The L99SP08 features one EN pin per channel. These are open drain outputs active high.

They are used to wake up or enable external devices, like the STi<sup>2</sup>Fuse hybrid and monolithic devices.

The ENx pin is raised in case of at least one of the following trigger condition is verified:

- I<sub>OUTx</sub> > I<sub>PEAK</sub>

- TSD<sub>x</sub> is triggered

- $V_{DSx} > V_{DS_OV}$

- I<sub>OUTx</sub> > I<sub>THRx</sub> AND t<sub>MAX</sub> expired

The L99SP08 implements the possibility to drive, during normal mode operation, the ENx through control register (CR8 "Direct External EN Control Register") even if the cases mentioned above are not triggered.

On top of this, the device allows to configure the ENx pin through the NVM bits.

In standby mode:

- EN CONF STDBY

- [1]: ENx pin internally set to ENCTRL\_STDBYx NVM bits (8 bits, one per channel), even if the trigger condition is not present.

- [0]: ENx pin depends on the trigger conditions previously listed.

#### In fail-safe mode:

- DIS\_CONF\_FS

- [0]: ENx pin internally set to the ENCTRL\_FSx bits (8 bits, one per channel) in logical OR combination with the faults occurring on the channels.

- [1]: the ENCTRL\_FSx bits are not acting

DS14248 - Rev 5 page 17/100

#### 3.4 DIAG pin behavior

The L99SP08 has one diagnostic pin called DIAG. This is an open drain output active low, used to provide an information hard wire to the microcontroller. The DIAG pin is pulled down when the device goes from standby ON to fail-safe; the pin is pulled down for 1ms, then it is released in case anyone of the below listed fault is triggered:

- I<sub>OUTx</sub> > I<sub>PEAK</sub>

- TSD<sub>X</sub> triggering

- $V_{DSx} > V_{DSOV}$

- I<sub>OUTx</sub> > I<sub>THRx</sub> AND t<sub>MAX</sub> expired

In normal mode, the fault is cleared through the SPI frame; while in fail-safe, the DIAG pin is released upon a falling edge on DIN (after a filtering time of 20  $\mu$ s).

#### 3.5 OUTPUT control in fail-safe mode

In fail-safe mode the OUTPUT channel driving depends on the DIx mapping (refer to the Section 5: DIx input management) and the two dedicated NVM registers (OUTCTRL and OUTCTRL\_FS).

DIS CONF OUT FS

[1]: OUTPUT pins depend on the OUTCTRL register content, while the content of OUTCTRL\_FS and the DIx pin levels are ignored.

[0]: OUTPUT pins internally set to the logical OR combination of DIx pins and OUTCTRL FS NVM bits.

#### 3.6 Oscillator 20 MHz

The L99SP08 embeds a 20 MHz oscillator and a dithering block, for the relevant parameter of modulation, aimed to improve the EMC performances of the device.

There are three dedicated bits to program the desired frequency modulation and deviation to be applied (see Table 20).

| DITH_STEP [2:0] | N_STEP | Fosc_Mod [kHz] | Fosc_Dev [%] | Rejection [dB] |

|-----------------|--------|----------------|--------------|----------------|

| 000 disable     | 0      | 0              | 0            | 0              |

| 001             | 8      | 156            | 1.6          | -7.38          |

| 010             | 16     | 78             | 3.2          | -11.68         |

| 011             | 24     | 52             | 4.8          | -13.28         |

| 100             | 32     | 39             | 6.4          | -14.58         |

| 101             | 40     | 32             | 8            | -15.48         |

| 110             | 48     | 25             | 9.6          | -16.28         |

| 111             | 56     | 22             | 11.2         | -16.78         |

Table 20. 20 MHz oscillator, dithering-modulation parameters

## 3.7 P-channel bypass

The L99SP08 embeds eight bypass switches, aimed to feed the load during standby ON state.

The switches are P-channel Power MOSFET, with an I<sub>PFAK</sub> maximum current capability.

A dedicated driver controls each bypass switch, with zero current consumption in DC mode. The P-channel driver is put in high-Z when capacitive charging mode is enabled: in this latter case, a dedicated circuitry overtakes the gate control.

The device features the P-channel current monitoring in both standby ON state low and mid consumption.

#### 3.7.1 Output current monitoring in standby ON low consumption mode

To keep the lowest current consumption from the battery, the current monitoring is performed through an analog current sense: this is used to manage the transition from standby ON low to mid consumption, occurring as soon as the output current exceeds the  $I_{STBY}$  ON  $I_{H}$  threshold (see Figure 5).

When the device is in standby ON low consumption, the P-channel Ron is augmented at Ron STBY LC.

DS14248 - Rev 5 page 18/100

When the output current I<sub>OUTx</sub> overcomes the threshold I<sub>STDBY\_ON\_TH\_H</sub> (configurable via SPI), the bypass switch Ron is reduced to its typical value.

Finally, if the output current increases, exceeding the I<sub>PEAK</sub>, the enable pin (ENx) is raising and the bypass switch is turned off.

## 3.7.2 Output current monitoring in standby ON mid consumption mode

In this case, the current monitoring is still performed through analog current sense but with higher accuracy. It is used to manage:

- The transition from standby ON mid consumption to fail-safe, occurring as soon as the output current of one channel (at least) exceeds the configured I<sub>THRx</sub> threshold;

- The transition from standby ON mid to low consumption in the case of all the output current I<sub>OUTx</sub> is lower than I<sub>STBYON\_TH\_L</sub>.

A built-in self-test is implemented to check the whole P-channel monitoring circuitry. A dedicated bit per channel in the status register is set if the self-test is passed.

#### 3.8 Bypass drain-source overvoltage

The L99SP08 features a regular monitoring of the drain-source voltage ( $V_{DS}$ ) to avoid P-channel switches overheating. As soon as the  $V_{DS_X}$  voltage overcomes the  $V_{DS\_OV\_H}$  threshold, the enable pin (ENx) is forced high, and the relative channel x is switched off.

The  $V_{DS\_OV\_H}$  threshold is a fixed value, far enough from the worst case conditions of the maximum current on the P-channel multiplied by its  $R_{on}$ .

#### 3.9 ADC current sense

The device integrates eight 10-bit successive approximation register (SAR) analog-to-digital converters (ADCs) dedicated to current measurement. These ADCs provide digital information of the output current, which are stored in dedicated registers, 0x20 for Channel 0 to 0x27 for Channel 7, specifically in bits 13 to 4.

The update of the current sense registers is disabled when the corresponding channel is in the off state. Nevertheless, the device is capable of detecting potential malfunctions in the channels even when they are off, by employing alternative mechanisms based on the voltage measurement across the P-channels, as detailed in Section 3.11: Voltage ADC.

The ADC operates under both fail-safe and normal conditions. After each conversion, an update flag bit, UPDTIxSR, is set to indicate the availability of new conversion data. This bit is cleared following the reading of the corresponding RAM register.

$$I_{OUTx} = ADC_{Xconv} * 550 / 1024$$

In normal state, the ADC can be configured into a diagnostic mode by setting the bit CS\_DIAGx in the control register of each channel. In this diagnostic mode, the ADC's full-scale range is scaled to ADC\_FS\_DIAG, enabling the measurement of output currents up to 1 mA.

$I_{OUTx} = ADC_{Xconv} * 37 / 1024$

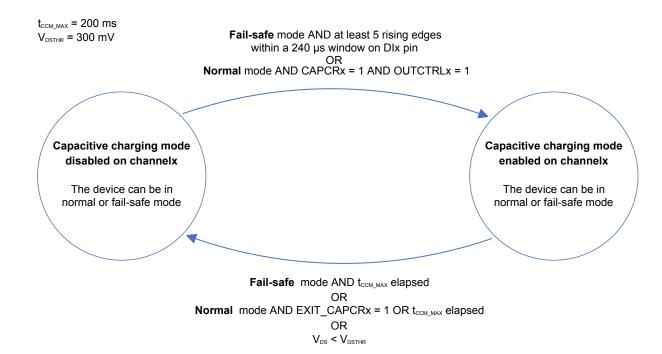

#### 3.10 Capacitive charging mode (CCM)

The capacitive charging mode (CCM) feature is used to precharge the output voltage to  $V_{CC}$  in case of a capacitive load is present. Thanks to this functionality, the turn on of the bypass switch with a capacitive load not leads to an inrush current through the P-channel, avoiding device potential switching off due to high dissipation and overheating, the CCM feature is disabled in case of  $V_{CCOV}$ .

The CCM is configured by means bit "CAPCRx" in the channels control register, moreover when the CCM is ended the P-channel driver could be left in generator current mode (CCM setting) or in ON/OFF mode depending on bit OUTCTRL.

Once CCM is configured the capacitive load is sustained by an I<sub>OUT CCM</sub> as per Table 17.

Hereafter the state diagram of CCM mode.

DS14248 - Rev 5 page 19/100

Figure 6. CCM mode state diagram

# 3.11 Voltage ADC

The device embeds one multiplexed voltage 10-bit successive approximation register (SAR) analog-to-digital converter. The parameters converted by the voltage ADC through MUX are:  $8 \text{ V}_{OUT}$  -  $8 \text{ T}_{J}$  -  $1 \text{ V}_{CC}$ . The conversion are stored in the dedicated registers (from 0x28 to 0x2F for VOUTxSR; from 0x30 to 0x37 for TJxSR and 0x38 for VCCSR).

The ADC works both in fail-safe and normal conditions, moreover both in channels ON or OFF, after each conversion, an updated bit "UPDTIxSR" is set to advise about the new conversion data. This bit is reset after the read process of the dedicated RAM register.

DS14248 - Rev 5 page 20/100

# 4 Protections and diagnostics

#### 4.1 Oscillator stuck

The 20 MHz oscillator integrated in the L99SP08 implements a safety redundancy, consisting in a second oscillator activated by a dedicated IP that monitors any potential stuck of the main oscillator.

Then, the main oscillator stuck fault is used for functional safety: until the fault is not reached, the secondary oscillator is switched off; as soon as the main oscillator is in stuck, the second one is woken up (and the fault signal is sent to the digital part, in a dedicated status register SR1 bit[12]).

#### 4.2 Bandgap stuck

The bandgap integrated in the L99SP08 implements a safety redundancy, consisting in a second bandgap activated by a dedicated IP that monitors any potential stuck low of the main bandgap.

Then, the main bandgap stuck fault is used for functional safety: until the fault is not reached, the secondary bandgap is switched off; as soon as the main bandgap is in stuck, the second one is woken up (and the fault signal is sent to the digital part, in a dedicated status register SR1 bit[13]).

#### 4.3 Overtemperature

The device integrates eight thermal sensors, one per channel: each sensor is used to monitor the die junction temperature  $(T_J)$ . The thermal sensors are positioned close to the P-channel (thermal sources).

Two thermal thresholds are implemented on the device:

- T<sub>Wx</sub>, one per channel, it is a flag highlighted in the GSB just as warning for a temperature increasing. No

action from the device in case of this threshold exceeding;

- T<sub>SDx</sub>, one per channel, this is a thermal shutdown, the device will switch off the channel x related to the thermal sensor detecting the T<sub>SDx</sub> event for safety reasons.

The  $T_J$  is converted through an ADC in Failsafe and Normal state, instead in standby ON condition, the output of the thermal sensor is compared with a fixed threshold ( $T_{SDx}$ , one per channel) for thermal shutdown.

In fail-safe or normal operations, the thermal sensor output is sent to the voltage ADC.

A dedicated bit in the channels status register from SR2 to SR5 bit[15:14] is set in case of fault.

The  $T_J$  ADC conversion is stored from SR30h to SR37h. The conversion formula is the following one:

$$TJ[^{\circ}C] = -\frac{\frac{TJxSR}{1023}*2.5 - 2.136}{0.006}$$

(1)

#### 4.4 Output and battery voltages monitoring

The L99SP08 embeds a voltage ADC used to monitor both the output voltage for each channel (V<sub>OUTx</sub>) and the battery voltage at the VCC pin.

This monitoring is active only in fail-safe and normal mode operation, both channel on or off. It is disable in standby on to keep the lowest current consumption from the battery that is the key requirement in this standby on operation.