# Automotive quad and dual half-bridge pre-driver

VFQFN32+4L WF

VFQFN48L WF exposed pad down

# Product status link L99MH94 L99MH92

| Product summary                      |                                |               |  |  |  |  |

|--------------------------------------|--------------------------------|---------------|--|--|--|--|

| Order code                           | Package                        | Packing       |  |  |  |  |

| L99MH92Q5-<br>TR<br>L99MH94Q5-<br>TR | VFQFN32+4L<br>WF<br>5x5x0.9 mm | Tape and reel |  |  |  |  |

| L99MH94Q7-<br>TR                     | VFQFN48L WF<br>7x7x0.9 mm      | Tape and reel |  |  |  |  |

#### **Features**

- ISO26262 compliant, covering ASIL-B safety integrity level

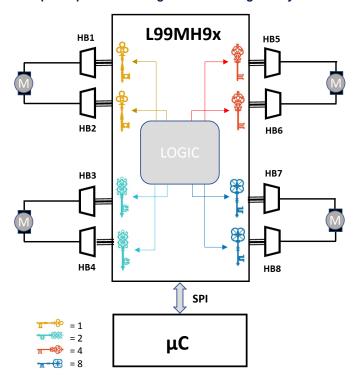

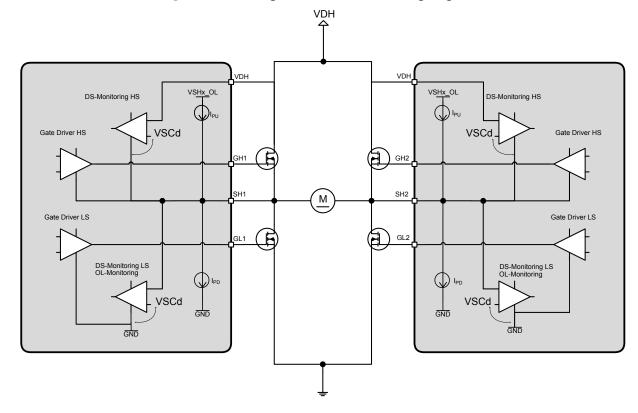

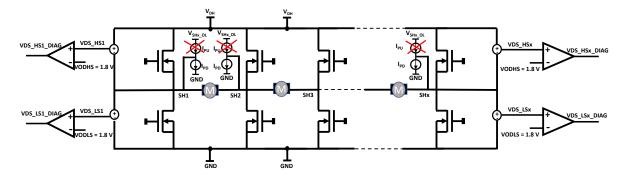

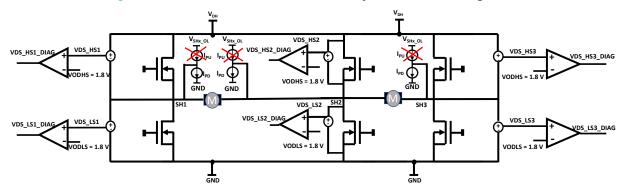

- Quad (L99MH94) and dual (L99MH92) half-bridge, or dual (L99MH94) and single (L99MH92) H-Bridge, pre-driver

- Independent channel driver up to 4 (L99MH94) and 2 (L99MH92) high-side or 4 (L99MH94) and 2 (L99MH92) low-side

- Driving logic permits any H-bridge configuration, pairing different half-bridges, using the internal gate drivers (GHx/SHx/GLx can be associated to any GHy/SHy/GLy)

- Support logic level and standard level MOSFETs

- Control of reverse battery protection MOSFET

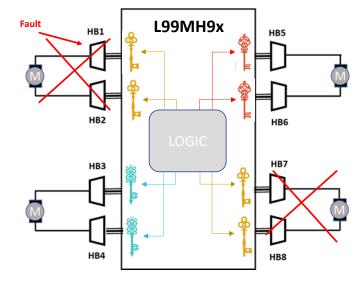

- Fully configurable half-bridge driver in case of fault occurrence

- · Generator mode for power trunk/tailgate applications

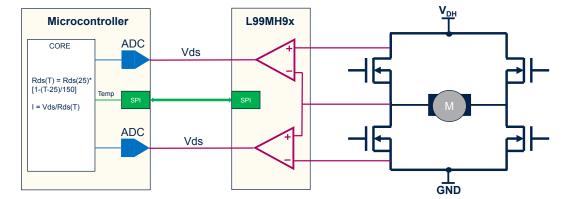

- Supporting indirect current measurement of external MOSFETs

- SPI configurable overvoltage threshold

- Adaptive MOSFET gate control

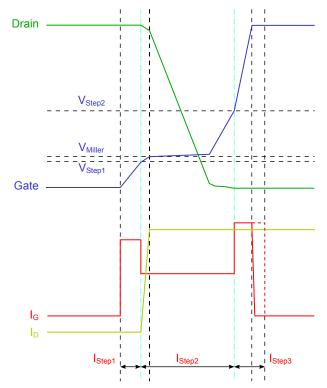

- Three steps gate control of external HS/LS

- Improved electromagnetic emission

- Programmable gate current up to 120 mA

- Reduced switching losses in PWM mode

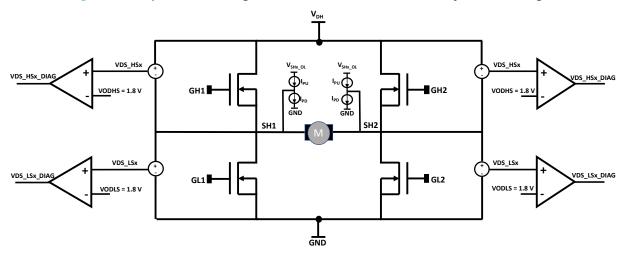

- V<sub>ds</sub> monitoring

- Low IQ (1.05 μA) in reset mode

- · High-side and low-side capable of protection and diagnosis

- Two external diodes control, needed for assisting calibration of indirect current measurement, can be used for steady - temperature monitoring

- Drain-source monitoring for short circuit detection

- · Overtemperature warning and shutdown

- Timeout watchdog for MCU control

- Detailed off-state diagnostic (open load, short circuit to battery or short circuit to GND) via SPI

- Three PWM inputs

- High-side and low-side PWM capable

- Active freewheeling

- Up to 50 kHz PWM frequency

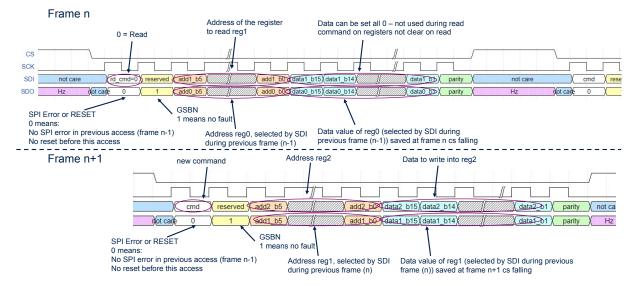

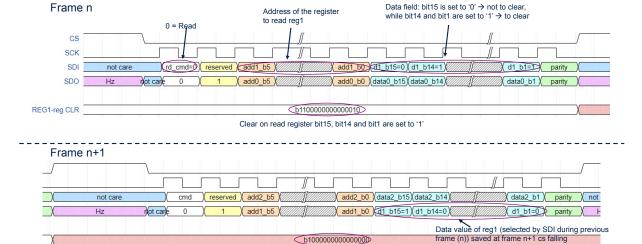

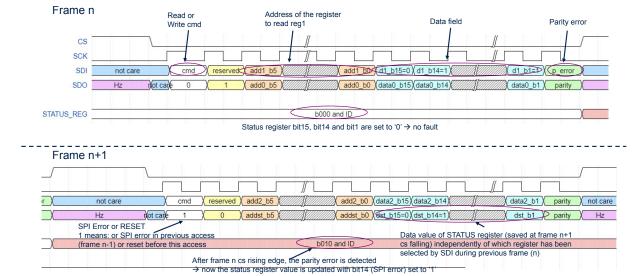

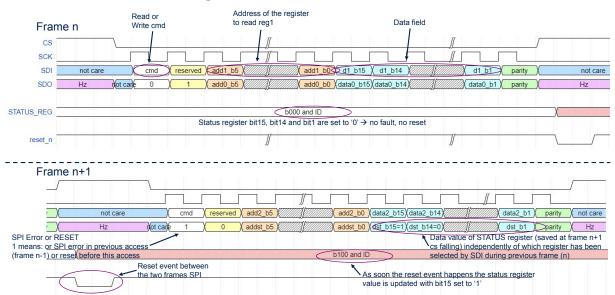

- Out-of-frame serial peripheral interface (SPI), 24 bits

- QFN package with wettable flanks

- Green product (RoHS compliant)

# **Applications**

- Seat control

- Steering column adjustment, gas pedal adjustment

- · Sunroof, sliding doors, window lift, seat-belt pre-tensioners, cargo cover, washer pump

- Engine vibrations compensation system

- Power lift gate

- Central door lock

## **Description**

The L99MH94 and L99MH92 integrate respectively a quad and a dual half-bridge pre-driver dedicated to control up to eight and four N-channel MOSFETs.

It is intended for DC motor control applications such as automotive power seat control or other applications.

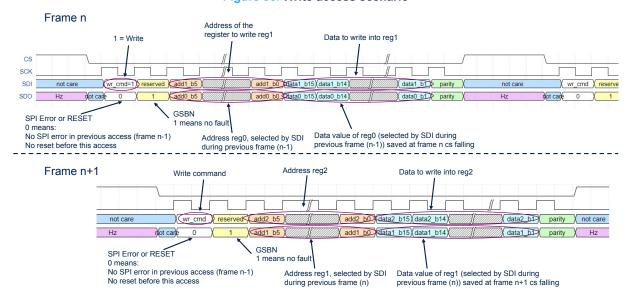

A 24-bit serial peripheral interface (SPI) is used for configuring and controlling the eight half-bridges or four H-bridge. SPI status registers provide high-level diagnostic information such as supply voltage monitoring, the charge pump voltage monitoring, temperature warning and overtemperature shutdown.

Each gate driver monitors independently its external MOSFET drain-source voltage for fault conditions.

The L99MH94 / L99MH92 support indirect current measurement on external MOSFETs, allowing cost saving and lower system complexity, avoiding the usage of shunt resistors.

A more efficient gate current control of the external MOSFETs, called "three stages gate current", decreases and optimizes electromagnetic interference (EMI).

Protection features (drain-source monitoring for short circuit detection, overtemperature warning and shutdown, timeout watchdog for MCU control, detailed off-state diagnostic via SPI) ensure the ASIL-B achievement according to ISO 26262 standard.

The L99MH94 is housed in VFQFN48L and VFQFN32L packages with an exposed pad, the L99MH92 is housed in a VFQFN32L package with exposed pad. These packages have wettable flanks for easy visual inspection of the solder joint.

DS15025 - Rev 1 page 2/130

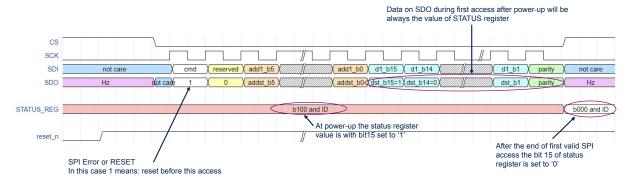

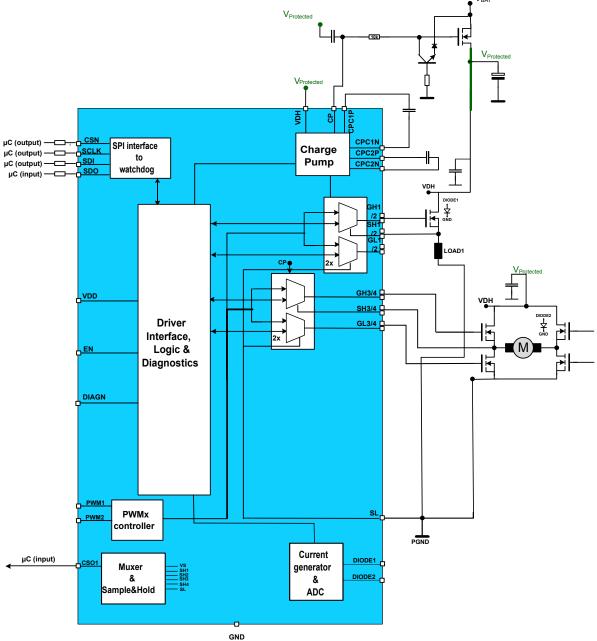

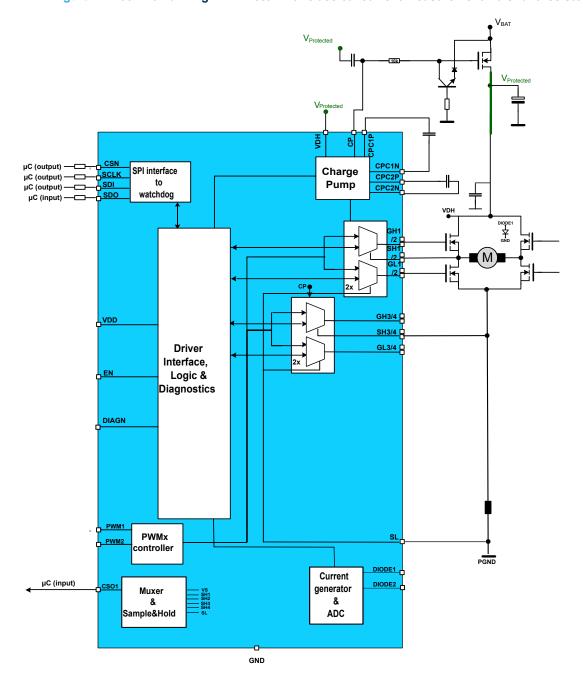

# Block diagram and pin description

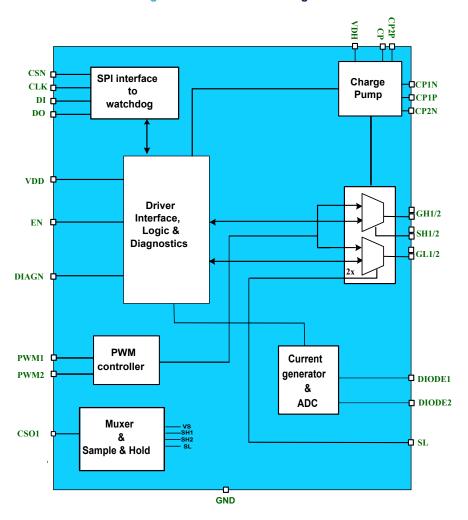

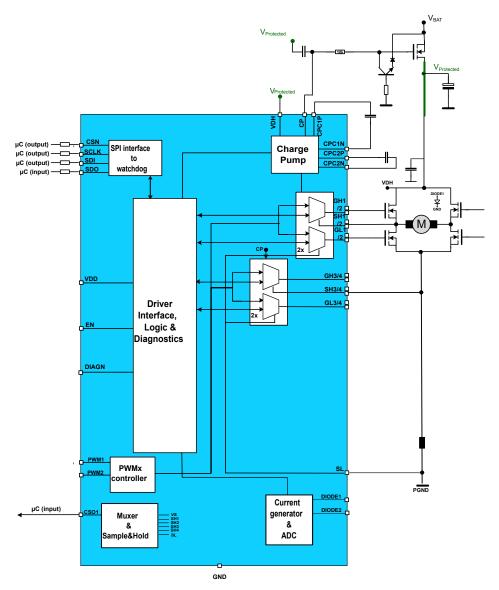

# 1.1 Block diagram

CP2P CP CSN, SPI interface Charge CP1N CLK Pump CP1P DI 🖥 watchdog CP2N DO GH1/2 SH1/2 GL1/2 VDD СРФ Driver Interface, **GH3/4** Logic & **Diagnostics** SH3/4 GL3/4 DIAGN | PWM1 **PWMx** controller PWM2 Current DIODE1

generator

ADC

DIODE2

SL

Figure 1. L99MH94 block diagram

DS15025 - Rev 1 page 3/130

Muxer

Sample & Hold

CSO1

Figure 2. L99MH92 block diagram

DS15025 - Rev 1 page 4/130

# 1.2 Pin description

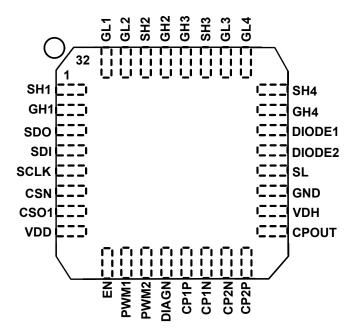

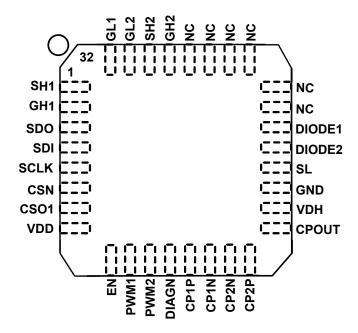

Figure 3. L99MH94 pin connection - VFQFN32 (top view)

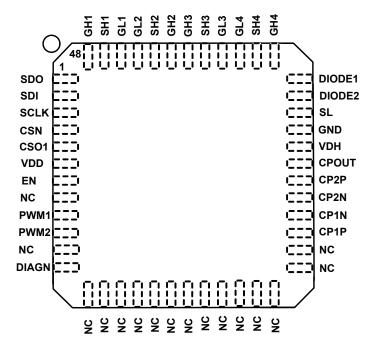

Figure 4. L99MH94 pin connection - VFQFN48 (top view)

DS15025 - Rev 1 page 5/130

Figure 5. L99MH92 pin connection (top view)

Table 1. Pin function - VFQFN32

| Pin | L99MH94 | L99MH92         | Function                                                                                                    |

|-----|---------|-----------------|-------------------------------------------------------------------------------------------------------------|

| 1   | SH      | H1              | SH1 Source high-side 1: Connection to source of high-side MOSFET 1                                          |

| 2   | GH1     |                 | GH1 Gate high-side 1: Analog output pin to turn on/off high-side MOSFET 1. Connect to the gate of high side |

| 3   | SE      | 00              | SDO Serial Data Output                                                                                      |

| 4   | SI      | DI              | SDI Serial Data Input with internal pull-down                                                               |

| 5   | SC      | CLK             | SCLK Serial Clock Input with internal pull-down                                                             |

| 6   | CS      | SN              | CSN Chip Select Not with internal pull-up                                                                   |

| 7   | CS      | O1              | CSO1 Current Sense Amplifier Output1                                                                        |

| 8   | VE      | DD              | VDD Logic supply                                                                                            |

| 9   | Е       | N               | EN Enable input with internal pull-down                                                                     |

| 10  | PW      | /M1             | PWM1: PWM input 1                                                                                           |

| 11  | PW      | /M2             | PWM2: PWM input 2                                                                                           |

| 12  | DIA     | \GN             | Diagnostic output NOT (Active Low)                                                                          |

| 13  | CP1P    |                 | NC: Not Connected                                                                                           |

|     | OI .    |                 | CP1P: Positive connection to Charge Pump Capacitor 1                                                        |

| 14  | CP      | 21N             | NC: Not Connected                                                                                           |

|     | 0.      |                 | CP1N: Negative connection to Charge Pump Capacitor 1                                                        |

| 15  | CP      | <sup>2</sup> 2N | NC: Not Connected                                                                                           |

|     | OI ZIN  |                 | CP2N: Negative connection to Charge Pump Capacitor 2                                                        |

| 16  | 6 CP2P  |                 | NC: Not Connected                                                                                           |

|     |         |                 | CP2P: Positive connection to Charge Pump Capacitor 2                                                        |

| 17  | CPC     | DUT             | CP: Charge Pump Output                                                                                      |

DS15025 - Rev 1 page 6/130

| Pin | L99MH94                                                       | L99MH92 | Function                                                                                                    |  |  |  |  |

|-----|---------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 18  | VDH                                                           |         | VDH input pin                                                                                               |  |  |  |  |

| 19  | GND                                                           |         | GND Ground connection                                                                                       |  |  |  |  |

| 20  | S                                                             | L       | SL Source low-side: Common connection to the source of the low-side MOSFETs.                                |  |  |  |  |

| 21  | DIO                                                           | DE2     | External diode control 2                                                                                    |  |  |  |  |

| 22  | DIO                                                           | DE1     | External diode control 1                                                                                    |  |  |  |  |

| 23  | GH4                                                           | NC      | GH4 Gate high-side 4: Analog output pin to turn on/off high-side MOSFET 4. Connect to the gate of high side |  |  |  |  |

|     |                                                               |         | NC: Not Connected                                                                                           |  |  |  |  |

| 24  | SH4                                                           | NC      | SH4 Source high-side 4: Connection to source of high-side MOSFET 4                                          |  |  |  |  |

|     | 0114                                                          | 140     | NC: Not Connected                                                                                           |  |  |  |  |

| 25  | GL4                                                           | NC      | GL4 Gate low-side 4: Analog output pin to turn on/off low-side MOSFET 4. Connect to the gate of low side    |  |  |  |  |

|     |                                                               |         | NC: Not Connected                                                                                           |  |  |  |  |

| 26  | GL3                                                           | NC      | GL3 Gate low-side 3: Analog output pin to turn on/off low-side MOSFET 3. Connect to the gate of low side    |  |  |  |  |

|     |                                                               |         | NC: Not Connected                                                                                           |  |  |  |  |

| 27  | SH3                                                           | NC      | SH3 Source high-side 3: Connection to source of high-side MOSFET 3                                          |  |  |  |  |

| 21  | 3113                                                          | NO      | NC: Not Connected                                                                                           |  |  |  |  |

| 28  | GH3                                                           | NC      | GH3 Gate high-side 3: Analog output pin to turn on/off high-side MOSFET 3. Connect to the gate of high side |  |  |  |  |

|     |                                                               |         | NC: Not Connected                                                                                           |  |  |  |  |

| 29  | GH2                                                           |         | GH2 Gate high-side 2: Analog output pin to turn on/off high-side MOSFET 2. Connect to the gate of high side |  |  |  |  |

| 30  | SH2                                                           |         | SH2 Source high-side 2: Connection to source of high-side MOSFET 2                                          |  |  |  |  |

| 31  | I GL2                                                         |         | GL2 Gate low-side 2: Analog output pin to turn on/off low-side MOSFET 2. Connect to the gate of low side    |  |  |  |  |

| 32  | 2 GL1                                                         |         | GL1 Gate low-side 1: Analog output pin to turn on/off low-side MOSFET 1. Connect to the gate of low side    |  |  |  |  |

|     | E.P. Exposed pad connected to ground on the application board |         |                                                                                                             |  |  |  |  |

Table 2. Pin function - VFQFN48

| #                                                                      | Name | Function                                        |

|------------------------------------------------------------------------|------|-------------------------------------------------|

| 1                                                                      | SDO  | SDO serial data output                          |

| 2                                                                      | SDI  | SDI serial data input with internal pull-down   |

| 3                                                                      | SCLK | SCLK serial clock input with internal pull-down |

| 4                                                                      | CSN  | CSN chip select not with internal pull-up       |

| 5                                                                      | CSO1 | CSO1 current sense amplifier output1            |

| 6                                                                      | VDD  | VDD logic supply                                |

| 7                                                                      | EN   | EN enable input with internal pull-down         |

| 8, 11, 13, 14,<br>15, 16, 17, 18,<br>19, 20, 21, 22,<br>23, 24, 25, 26 | NC   | Not Connected                                   |

| 9                                                                      | PWM1 | PWM1: PWM input 1                               |

| 10                                                                     | PWM2 | PWM2: PWM input 2                               |

DS15025 - Rev 1 page 7/130

| #  | Name   | Function                                                                                                        |

|----|--------|-----------------------------------------------------------------------------------------------------------------|

| 12 | DIAGN  | DIAGN: Diagnostic output NOT (active low)                                                                       |

| 27 | CP1P   | CP1P:positive connection to charge pump capacitor 1                                                             |

| 28 | CP1N   | CP1N: negative connection to charge pump capacitor 1                                                            |

| 29 | CP2N   | CP2N: negative connection to charge pump capacitor 2                                                            |

| 30 | CP2P   | CP2P: Positive connection to charge pump capacitor 2                                                            |

| 31 | CPOUT  | CPOUT: Charge pump output                                                                                       |

| 32 | VDH    | VDH input pin                                                                                                   |

| 33 | GND    | GND Ground connection                                                                                           |

| 34 | SL     | SL source low-side: common connection to the source of the low-side MOSFETs                                     |

| 35 | DIODE2 | External diode control 2                                                                                        |

| 36 | DIODE1 | External diode control 1                                                                                        |

| 37 | GH4    | GH4 gate high-side 4: analog output pin to turn on/off high-side MOSFET 4. Connect to the gate of the high side |

| 38 | SH4    | SH4 source high-side 4: connection to source of high-side MOSFET 4                                              |

| 39 | GL4    | GL4 gate low-side 4: analog output pin to turn on/off low-side MOSFET 4. Connect to the gate of the low side    |

| 40 | GL3    | GL3 gate low-side 3: analog output pin to turn on/off low-side MOSFET 3. Connect to the gate of the low side    |

| 41 | SH3    | SH3 source high-side 3: connection to source of high-side MOSFET 3                                              |

| 42 | GH3    | GH3 gate high-side 3: analog output pin to turn on/off high-side MOSFET 3. Connect to the gate of the high side |

| 43 | GH2    | GH2 gate high-side 2: analog output pin to turn on/off high-side MOSFET 2. Connect to the gate of the high side |

| 44 | SH2    | SH2 source high-side 2: connection to source of high-side MOSFET 2                                              |

| 45 | GL2    | GL2 gate low-side 2:analog output pin to turn on/off low-side MOSFET 2. Connect to the gate of the low side     |

| 46 | GL1    | GL1 gate low-side 1: analog output pin to turn on/off low-side MOSFET 1. Connect to the gate of the low side    |

| 47 | SH1    | SH1 source high-side 1: connection to source of high-side MOSFET 1                                              |

| 48 | GH1    | GH1 gate high-side 1: analog output pin to turn on/off high-side MOSFET 1. Connect to the gate of the high side |

| -  | E.P.   | Exposed pad connected to ground on the application board                                                        |

DS15025 - Rev 1 page 8/130

# 2 Electrical specifications

Stressing the device above the rating listed in the Table 3 may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 2.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol                 | Parameter                                         | Min       | Тур | Max       | Unit |

|------------------------|---------------------------------------------------|-----------|-----|-----------|------|

| $V_{DH}$               | Power supply voltage                              | -0.3      | -   | 28        | V    |

| $V_{DH}$               | Single pulse tmax < 400 ms                        | -         | -   | 40        | V    |

| V <sub>PWM1</sub>      | PWM input voltages (PWMx)                         | -0.3      | -   | VDD + 0.3 | V    |

| V <sub>PWM2</sub>      | PWM input voltages (PWMx)                         | -0.3      | -   | VDD + 0.3 | V    |

| V <sub>SDI</sub>       | SDI logic input voltages                          | -0.3      | -   | VDD + 0.3 | V    |

| V <sub>SCLK</sub>      | SCLK logic input voltages                         | -0.3      | -   | VDD + 0.3 | V    |

| V <sub>CSN</sub>       | CSN logic input voltages                          | -0.3      | -   | VDD + 0.3 | V    |

| V <sub>EN</sub>        | EN logic input voltages                           | -0.3      | -   | 20        | V    |

| V <sub>SDO/DIAGN</sub> | Voltage range at SDO/DIAGN                        | -0.3      | -   | VDD + 0.3 | V    |

| V <sub>SL</sub>        | Voltage range at SL                               | -6.0      | -   | 6         | V    |

| V <sub>SH</sub>        | Voltage range at SHx                              | -6.0      | -   | VDH       | V    |

| $V_{GH}$               | Voltage range at GHx, V <sub>CPOUT</sub> = +0.3 V | Sxy - 0.3 | -   | Sxy + 13  | V    |

| $V_{GL}$               | Voltage range at GLx, V <sub>CPOUT</sub> = +0.3 V | Sxy - 0.3 | -   | Sxy + 13  | V    |

| V <sub>GS_LS</sub>     | Voltage difference between GLx and SL             | -0.3      | -   | 13        | V    |

| V <sub>GS_HS</sub>     | Voltage difference between GHx and SHx            | -0.3      | -   | 13        | V    |

| V <sub>CP1</sub> -     | CP1 minus                                         | -0.3      | -   | VDH       | V    |

| V <sub>CP2</sub> -     | CP2 minus                                         | -0.3      | -   | VDH       | V    |

| V <sub>CP1+</sub>      | CP1 plus                                          | VDH - 0.3 | -   | VDH + 13  | V    |

| V <sub>CP2+</sub>      | CP2 plus                                          | VDH - 0.6 | -   | VDH + 13  | V    |

| V <sub>CPOUT</sub>     | CP out                                            | VDH - 0.6 | -   | VDH + 13  | V    |

| V <sub>DIODE</sub>     | Voltage at Vdiode pins                            | -0.3      | -   | 40        | V    |

| $V_{DD}$               | Logic supply voltage                              | -0.3      | -   | 18        | V    |

| V <sub>CSO1</sub>      | Voltage at CSO1                                   | -0.3      | -   | VDD + 0.3 | V    |

Note:

- All maximum ratings are absolute ratings. Leaving the limitation of any of these values may cause an irreversible damage of the integrated circuit.

- Loss of ground or ground shift with externally grounded loads: ESD structures are configured for nominal currents only. If external loads are connected to different grounds, the current load must be limited to this nominal current.

DS15025 - Rev 1 page 9/130

# 2.2 ESD protection

Table 4. ESD protection

| Symbol                                                                                                 | Parameter | Min  | Тур | Max  | Unit |

|--------------------------------------------------------------------------------------------------------|-----------|------|-----|------|------|

| Electrostatic discharge test (AEC-Q100-002-E) all pins (HBM)                                           | -         | -2   | -   | +2   | kV   |

| Electrostatic discharge test (AEC-Q100-002-E) output pins SHx $(X = 18)$ and $V_{DH}$ versus GND (HBM) | -         | -4   | -   | +4   | kV   |

| Charge device model (CDM-AEC-Q100-011) all pins                                                        | -         | -500 | -   | +500 | V    |

| Charged device model (CDM-AEC-Q100-011) corner pins                                                    | -         | -750 | -   | +750 | V    |

#### 2.3 Thermal data

Table 5. Operation junction temperature

| Symbol           | Parameter                      | Min | Тур | Max | Unit |

|------------------|--------------------------------|-----|-----|-----|------|

| T <sub>j</sub>   | Operating junction temperature | -40 | -   | 150 | °C   |

| T <sub>stg</sub> | Storage temperature            | -55 | -   | 150 | °C   |

All parameters are guaranteed in the temperature range -40 to 150 °C (unless otherwise specified); the device is still operative and functional at higher temperatures (up to 165 °C).

Note:

- Parameters limits at higher temperatures than 150 °C may change with respect to what is specified as per the standard temperature range.

- Device functionality at high temperature is guaranteed by characterization.

Table 6. Temperature warning and thermal shutdown

| Symbol                 | Parameter                                       | Test condition            | Min | Тур | Max | Unit |

|------------------------|-------------------------------------------------|---------------------------|-----|-----|-----|------|

| T <sub>jTW_ON</sub>    | Junction temperature thermal warning threshold  | T <sub>j</sub> increasing | 140 | 150 | 160 | °C   |

| T <sub>jSD_ON</sub>    | Junction temperature thermal shutdown threshold | T <sub>j</sub> increasing | 170 | 180 | 190 | °C   |

| T <sub>jSD_OFF</sub>   | Junction temperature thermal shutdown threshold | T <sub>j</sub> decreasing | 160 | 170 | 180 | °C   |

| t <sub>fTjTW/TSD</sub> | Temperature warning/shutdown filtering time     | Tested by scan            | 24  | -   | 43  | μs   |

Note: Those parameters are guaranteed at hot only.

#### 2.3.1 Packages thermal data

Table 7. Packages thermal resistance

| Symbol                               | Parameter                                             | Test condition | Value | Unit |

|--------------------------------------|-------------------------------------------------------|----------------|-------|------|

| R <sub>thj-amb</sub> <sup>(1)</sup>  | VFQFN32 thermal resistance junction to ambient (max.) |                | 28.6  | °C/W |

| R <sub>thj-amb</sub> <sup>(1)</sup>  | VFQFN48 thermal resistance junction to ambient (max.) |                | 26    | °C/W |

| R <sub>thj-case</sub> <sup>(2)</sup> | VFQFN32 thermal resistance junction to case (max.)    |                | 7.6   | °C/W |

| R <sub>thj-case</sub> <sup>(2)</sup> | VFQFN48 thermal resistance junction to case (max.)    |                | 4.5   | °C/W |

- 1. The parameter is retrieved according to JEDEC 51.2. Device mounted on a four-layer 2s2p PCB.

- 2. The  $R_{thi-case}$  is retrieved according to MIL-STD-883E referring to thermal testing method.

DS15025 - Rev 1 page 10/130

# 2.4 Electrical characteristics

# 2.4.1 Supply, supply monitoring and current consumption

$V_{DH}$  = 6 V to 28 V;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40 °C to 150 °C, all voltages are referred to ground and currents are assumed positive when flow into the pin (unless otherwise specified).

Table 8. Supply, supply monitoring and current consumption

| Symbol                  | Parameter                                                | Test condition                                                                | Min  | Тур  | Max  | Unit |

|-------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| $V_{DH}$                | High-side drain voltage                                  |                                                                               | 6    | -    | 28   | V    |

| V <sub>SL</sub>         | SL operative voltage range                               |                                                                               | -0.3 | -    | 0.5  | V    |

| V <sub>SH</sub>         | SH operative voltage range                               |                                                                               | -0.3 | -    | VDH  | V    |

| V <sub>DH_ext</sub>     | High-side drain voltage extended range <sup>(1)</sup>    |                                                                               | 5    | -    | 6    | V    |

| $V_{DD}$                | I/O supply voltage                                       |                                                                               | 3    | -    | 5.5  | V    |

| I <sub>DD</sub>         | V <sub>DD</sub> DC supply current                        | $V_{DH} = 13.5 V$ $V_{DD} = 5 V$ Active mode                                  | 3.5  | -    | 7.5  | mA   |

| I <sub>DD_SDN</sub>     | V <sub>DD</sub> quiescent supply current                 | V <sub>DD</sub> = 5 V<br>Reset mode                                           | -    | -    | 0.5  | μA   |

| I <sub>DH</sub>         | V <sub>DH</sub> current consumption in active mode       | $V_{DH} = 13 \text{ V}$ $V_{DD} = 5 \text{ V}$ Active mode Outputs floating   | -    | 40   | 50   | mA   |

| I <sub>DH</sub>         | V <sub>DH</sub> current consumption in active mode       | $V_{DH}$ = 6 V to 28 V<br>$V_{DD}$ = 5.0 V<br>Active mode<br>Outputs floating | -    | 48   | 60   | mA   |

| I <sub>DH_SDN</sub>     | V <sub>DH</sub> quiescent supply current                 | $V_{DH} = 13 \text{ V}$ $V_{DD} = 0 \text{ V}$ Reset mode Outputs floating    | -    | -    | 0.55 | μА   |

| V <sub>DHUV</sub>       | V <sub>DH</sub> undervoltage threshold                   | V <sub>DH</sub> increasing/decreasing                                         | 4    | -    | 4.5  | V    |

| V <sub>DHUV_hyst</sub>  | V <sub>DH</sub> undervoltage hysteresis                  |                                                                               | 0.04 | -    | 0.2  | V    |

| V <sub>DHOVT1_LH</sub>  | V <sub>DH</sub> overvoltage threshold 1 LH               | V <sub>DH</sub> increasing                                                    | 19   | -    | 21   | V    |

| V <sub>DHOVT1_HL</sub>  | V <sub>DH</sub> overvoltage threshold 1 HL               | V <sub>DH</sub> decreasing                                                    | 18.4 | -    | 20.4 | V    |

| V <sub>DHOVT2_LH</sub>  | V <sub>DH</sub> overvoltage threshold 2 LH               | V <sub>DH</sub> increasing                                                    | 29   | -    | 33   | V    |

| V <sub>DHOVT2_HL</sub>  | V <sub>DH</sub> overvoltage threshold 2 HL               | V <sub>DH</sub> decreasing                                                    | 28.5 | -    | 32.5 | V    |

| V <sub>DHOV2_hyst</sub> | V <sub>DH</sub> overvoltage threshold 2 hysteresis       | Guaranteed by design                                                          | -    | 0.8  | -    | V    |

| V <sub>DHOV1_hyst</sub> | V <sub>DH</sub> overvoltage threshold 1 hysteresis       | Guaranteed by design                                                          | -    | 0.65 | -    | V    |

| t <sub>UV_FILT</sub>    | V <sub>DH</sub> undervoltage filter time                 |                                                                               | 7    | 10   | 13   | μs   |

| t <sub>OV_FILT</sub>    | V <sub>DH</sub> /V <sub>DD</sub> overvoltage filter time |                                                                               | 7    | 10   | 13   | μs   |

| V <sub>DDOVT_LH</sub>   | V <sub>DD</sub> overvoltage threshold LH                 |                                                                               | 5.4  | -    | 5.9  | V    |

| V <sub>DDOVT_HL</sub>   | V <sub>DD</sub> overvoltage threshold HL                 |                                                                               | 5.3  | -    | 5.8  | V    |

| V <sub>DDhyst_OV</sub>  | V <sub>DD</sub> overvoltage hysteresis                   |                                                                               | 0.07 | -    | 0.2  | V    |

| V <sub>DDPOR_OFF</sub>  | V <sub>DD</sub> power-on-reset                           | V <sub>DD</sub> increasing                                                    | 2.40 | 2.60 | 2.80 | V    |

DS15025 - Rev 1 page 11/130

| Symbol                | Parameter                       | Test condition             | Min  | Тур  | Max  | Unit |

|-----------------------|---------------------------------|----------------------------|------|------|------|------|

| V <sub>DDPOR_ON</sub> | V <sub>DD</sub> power-off-reset | V <sub>DD</sub> decreasing | 2.30 | 2.50 | 2.70 | V    |

<sup>1.</sup> Only functionality guaranteed.

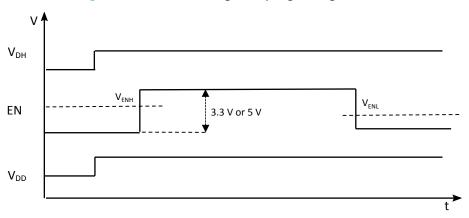

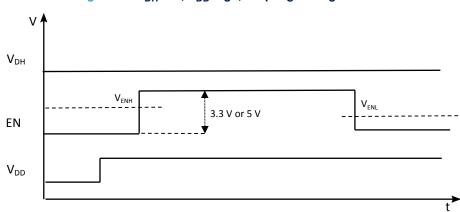

# 2.4.2 Logic inputs PWMx, EN

$V_{DH}$  = 6 V to 28 V;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40 °C to 150 °C, all voltages are referred to ground and currents are assumed positive when flow into the pin (unless otherwise specified).

Table 9. PWMx, EN

| Symbol                 | Parameter                | Test condition                                                                                                              | Min  | Тур | Max   | Unit |

|------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|-----|-------|------|

| V <sub>ENH</sub>       | EN high voltage          |                                                                                                                             | 0.9  | -   | 2     | V    |

| V <sub>ENL</sub>       | EN low voltage           |                                                                                                                             | 0.4  | -   | 0.95  | V    |

| V <sub>ENHY</sub>      | EN hysteresis            | (1)                                                                                                                         | 0.45 | -   | 0.95  | V    |

| R <sub>PD_OFF_EN</sub> | EN pull-down resistor    | EN pin below EN threshold                                                                                                   | 150  | 200 | 250.5 | kΩ   |

| I <sub>PD_ON_EN</sub>  | EN pull-down current     | EN pin above EN threshold, additional current, pull down resistor still present.  Expected 80 µA + 25 µA with 5 V at EN pin | 8.5  | 15  | 25    | μA   |

| V <sub>PWMH</sub>      | PWMx high voltage        | (2)                                                                                                                         | 1    | -   | 2     | V    |

| V <sub>PWML</sub>      | PWMx low voltage         | (3)                                                                                                                         | 0.75 | -   | 1.65  | V    |

| V <sub>PWMHY</sub>     | PWMx hysteresis          | (1)                                                                                                                         | 0.1  | -   | 0.5   | V    |

| R <sub>PD_PWMx</sub>   | PWMx pull-down resistor  |                                                                                                                             | 20   | 30  | 40    | kΩ   |

| fрwмн                  | PWMH switching frequency | VDH = 13.5 V, VSLx = 0 V<br>RG = 0 Ω, CG = 2.7 nF<br>PWMH-duty-cycle = 50%                                                  | -    | -   | 50    | kHz  |

- 1. Not subject to production test, specified by design.

- 2. High level guaranteed above max voltage.

- 3. Low level guaranteed below min voltage.

#### 2.4.3 Diagnostic not output (DIAGN)

The voltages are referred to ground and currents are assumed positive when the current flows into the pin. 6 V  $\leq$  V<sub>DH</sub>  $\leq$  18 V; T<sub>i</sub> = -40 °C to 150 °C, unless otherwise specified.

Table 10. DIAGN outputs

| Symbol          | Parameter                 | Test condition          | Min       | Тур | Max | Unit |

|-----------------|---------------------------|-------------------------|-----------|-----|-----|------|

| V <sub>OL</sub> | Low-level output voltage  | I <sub>out</sub> = 1 mA | -         | -   | 0.4 | V    |

| V <sub>OH</sub> | High-level output voltage | I <sub>out</sub> = 1 mA | VDD - 0.4 | -   | -   | V    |

DS15025 - Rev 1 page 12/130

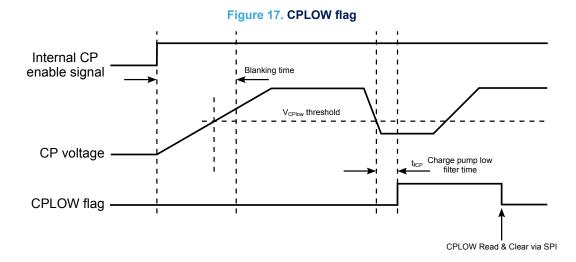

#### 2.4.4 Charge pump

$V_{DH}$  = 6 V to 28 V;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40 °C to 150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified).

Symbol **Test condition Parameter** Min Тур Max Unit (1)  $f_{CP}$ Charge Pump frequency 325 400 475 kHz V<sub>DH</sub> ≥ 8 V  $V_{DH} + 8.2$ V<sub>DH</sub> + 11.2 V<sub>DH</sub> + 13  $V_{\mathsf{CP}}$ Charge pump output voltage ٧  $I_{CP} \ge -10 \text{ mA}^{(2)}$  $V_{DH} = 6 V$ Charge pump output voltage  $V_{DH} + 6.2$  $V_{DH} + 7$  $V_{CP\_vbmin}$  $I_{CP} = -5 \text{ mA}^{(2)}$  $V_{CP\_low}$ Charge pump low threshold voltage  $V_{DH} + 4.5$  $V_{DH} + 5$  $V_{DH} + 5.5$ V V<sub>CP</sub>= V<sub>DH</sub> = 13.5 V -36 I<sub>CP lim</sub> Charge pump output current limitation(3) mA  $t_{CP}$ Charge pump low filter time Tested by scan 8 10 12 μs Charge pump startup blanking time Tested by scan 500 800 t<sub>CP blank</sub> μs

Table 11. Charge pump

#### 2.4.5 Gate driver

The electrical characteristics related to the gate driver are valid for  $V_{CP} > V_{DH} + 8.5 \text{ V}$ .

$V_{DH}$  = 6 V to 28 V;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40 °C to 150 °C,  $V_{CP}$  >  $V_{DH}$  + 8.5 V, all voltages with respect to ground, positive current flowing into pin except for  $I_{GLx}$  and  $I_{GHx}$  (unless otherwise specified).

The gate source and sink current level can be affected in case of high SHx/GHx slew rate due to capacitive current injected into the GATE pin from an external MOS miller capacitor. This behavior is described in a dedicated application note.

Table 12. Gate driver

| Symbol            | Parameter                                                             | Test condition                                             | Min  | Тур   | Max  | Unit |

|-------------------|-----------------------------------------------------------------------|------------------------------------------------------------|------|-------|------|------|

| I <sub>onx</sub>  | Gate source current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub> | ISTEP1_CONFx = ISTEP2_CONFx = 0000                         | -50% | -0.72 | +50% | mA   |

| I <sub>offx</sub> | Gate sink current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub>   | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 0000                     | -50% | 0.88  | +50% | mA   |

| I <sub>onx</sub>  | Gate source current                                                   | ISTEP1_CONFx = ISTEP2_CONFx = 0001<br>ISTEP3_CONFx = 0000  | -50% | -1.58 | +50% | mA   |

| I <sub>offx</sub> | Gate sink current                                                     | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 0001 ISTEP3_CONFx = 0000 | -50% | 1.77  | +50% | mA   |

| I <sub>onx</sub>  | Gate source current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub> | ISTEP1_CONFx = ISTEP2_CONFx = 0010                         | -50% | -2.6  | +50% | mA   |

| I <sub>offx</sub> | Gate Sink Current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub>   | ISTEP1_CONFX = ISTEP2_OFF_CONFx = 0010                     | -50% | 2.6   | +50% | mA   |

| I <sub>onx</sub>  | Gate source current                                                   | ISTEP1_CONFx = ISTEP2_CONFx = 0011<br>ISTEP3_CONFx = 0001  | -45% | -3.3  | +45% | mA   |

| I <sub>offx</sub> | Gate sink current                                                     | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 0011 ISTEP3_CONFx = 0001 | -45% | 3.5   | +45% | mA   |

DS15025 - Rev 1 page 13/130

<sup>1.</sup> Not subject to production test, specified by design.

<sup>2.</sup>  $C_{CPC1} = C_{CPC2} = 100 \text{ nF}, C_{CP} = 220 \text{ nF}.$

<sup>3.</sup> In case of short to battery. This pin is not protected from short to ground.

| Symbol             | Parameter                                                             | Test condition                                             | Min  | Тур | Max  | Unit |

|--------------------|-----------------------------------------------------------------------|------------------------------------------------------------|------|-----|------|------|

| I <sub>onx</sub>   | Gate source current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub> | ISTEP1_CONFx = ISTEP2_CONFx = 0100                         | -45% | -6  | +45% | mA   |

| I <sub>offx</sub>  | Gate sink current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub>   | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 0100                     | -45% | 6   | +45% | mA   |

| I <sub>onx</sub>   | Gate source current                                                   | ISTEP1_CONFx = ISTEP2_CONFx = 0101<br>ISTEP3_CONFx = 0010  | -35% | -8  | 35%  | mA   |

| I <sub>offx</sub>  | Gate sink current                                                     | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 0101 ISTEP3_CONFx = 0010 | -35% | 8   | 35%  | mA   |

| I <sub>onx</sub>   | Gate source current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub> | ISTEP1_CONFx = ISTEP2_CONFx = 0110                         | -35% | -10 | 35%  | mA   |

| I <sub>offx</sub>  | Gate Sink Current, only ISTEP1x and ISTEP2x                           | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 0110                     | -35% | 10  | 35%  | mA   |

| I <sub>onx</sub>   | Gate source current                                                   | ISTEP1_CONFx = ISTEP2_CONFx = 0111<br>ISTEP3_CONFx = 0011  | -35% | -12 | 35%  | mA   |

| I <sub>offx</sub>  | Gate sink current                                                     | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 0111 ISTEP3_CONFx = 0011 | -35% | 12  | 35%  | mA   |

| I <sub>onx</sub>   | Gate source current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub> | ISTEP1_CONFx = ISTEP2_CONFx = 1000                         | -35% | -16 | 35%  | mA   |

| I <sub>offx</sub>  | Gate sink current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub>   | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 1000                     | -35% | 16  | 35%  | mA   |

| I <sub>onx</sub>   | Gate source current                                                   | ISTEP1_CONFx = ISTEP2_CONFx = 1001<br>ISTEP3_CONFx = 0100  | -35% | -20 | 35%  | mA   |

| I <sub>offx</sub>  | Gate sink current                                                     | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 1001 ISTEP3_CONFx = 0100 | -35% | 20  | 35%  | mA   |

| I <sub>onx</sub>   | Gate source current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub> | ISTEP1_CONFx = ISTEP2_CONFx = 1010                         | -35% | -24 | 35%  | mA   |

| I <sub>offx</sub>  | Gate sink current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub>   | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 1010                     | -35% | 24  | 35%  | mA   |

| I <sub>onx</sub>   | Gate source current                                                   | ISTEP1_CONFx = ISTEP2_CONFx = 1011<br>ISTEP3_CONFx = 0101  | -35% | -28 | 35%  | mA   |

| I <sub>offx</sub>  | Gate sink current                                                     | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 1011 ISTEP3_CONFx = 0101 | -35% | 28  | 35%  | mA   |

| I <sub>onx</sub>   | Gate source current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub> | ISTEP1_CONFx = ISTEP2_CONFx = 1100                         | -35% | -32 | 35%  | mA   |

| I <sub>offx</sub>  | Gate sink current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub>   | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 1100                     | -35% | 32  | 35%  | mA   |

| I <sub>onx</sub>   | Gate source current                                                   | ISTEP1_CONFx = ISTEP2_CONFx = 1101<br>ISTEP3_CONFx = 0110  | -35% | -36 | 35%  | mA   |

| I <sub>Toffx</sub> | Gate sink current                                                     | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 1101 ISTEP3_CONFx = 0110 | -35% | 36  | 35%  | mA   |

| I <sub>onx</sub>   | Gate source current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub> | ISTEP1_CONFx = ISTEP2_CONFx = 1110                         | -35% | -40 | 35%  | mA   |

DS15025 - Rev 1 page 14/130

| Symbol            | Parameter                                                           | Test condition                                                                          | Min      | Тур    | Max    | Unit |

|-------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------|--------|--------|------|

| I <sub>offx</sub> | Gate sink current, only I <sub>STEP1x</sub> and I <sub>STEP2x</sub> | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 1110                                                  | -35%     | 40     | 35%    | mA   |

| I <sub>onx</sub>  | Gate source current                                                 | ISTEP1_CONFx = ISTEP2_CONFx = 1111<br>ISTEP3_CONFx = 0111                               | -25%     | -42    | +25%   | mA   |

| I <sub>offx</sub> | Gate sink current                                                   | ISTEP1_CONFx = ISTEP2_OFF_CONFx = 1111 ISTEP3_CONFx = 0111                              | -25%     | 37     | +25%   | mA   |

| I <sub>onx</sub>  | Gate source current only ISTEP3x                                    | ISTEP3_CONFx = 1000                                                                     | -25%     | -52    | +25%   | mA   |

| I <sub>offx</sub> | Gate sink current only I <sub>STEP3x</sub>                          | ISTEP3_CONFx = 1000                                                                     | -25%     | 52     | +25%   | mA   |

| I <sub>onx</sub>  | Gate source current only ISTEP3x                                    | ISTEP3_CONFx = 1001                                                                     | -25%     | -60    | +25%   | mA   |

| I <sub>offx</sub> | Gate sink current only ISTEP3x                                      | ISTEP3_CONFx = 1001                                                                     | -25%     | 60     | +25%   | mA   |

| I <sub>onx</sub>  | Gate source current only I <sub>STEP3x</sub>                        | ISTEP3_CONFx = 1010                                                                     | -25%     | -68    | +25%   | mA   |

| I <sub>offx</sub> | Gate sink current only ISTEP3x                                      | ISTEP3_CONFx = 1010                                                                     | -25%     | 68     | +25%   | mA   |

| I <sub>onx</sub>  | Gate source current only ISTEP3x                                    | ISTEP3_CONFx = 1011                                                                     | -25%     | -76    | +25%   | mA   |

| I <sub>offx</sub> | Gate sink current only I <sub>STEP3x</sub>                          | ISTEP3_CONFx = 1011                                                                     | -25%     | 76     | +25%   | mA   |

| I <sub>onx</sub>  | Gate source current only I <sub>STEP3x</sub>                        | ISTEP3_CONFx = 1100                                                                     | -25%     | -84    | +25%   | mA   |

| I <sub>offx</sub> | Gate sink current only ISTEP3x                                      | ISTEP3_CONFx = 1100                                                                     | -25%     | 84     | +25%   | mA   |

| I <sub>onx</sub>  | Gate source current only ISTEP3x                                    | ISTEP3_CONFx = 1101                                                                     | -25%     | -92    | +25%   | mA   |

| I <sub>offx</sub> | Gate sink current only I <sub>STEP3x</sub>                          | ISTEP3_CONFx = 1101                                                                     | -25%     | 92     | +25%   | mA   |

| I <sub>onx</sub>  | Gate source current only ISTEP3x                                    | ISTEP3_CONFx = 1110                                                                     | -25%     | -104   | +25%   | mA   |

| I <sub>offx</sub> | Gate sink current only ISTEP3x                                      | ISTEP3_CONFx = 1110                                                                     | -25%     | 104    | +25%   | mA   |

| I <sub>onx</sub>  | Gate source current only I <sub>STEP3x</sub>                        | ISTEP3_CONFx = 1111                                                                     | -25%     | -120   | +25%   | mA   |

| I <sub>offx</sub> | Gate sink current only ISTEP3x                                      | ISTEP3_CONFx = 1111                                                                     | -25%     | 120    | +25%   | mA   |

| V <sub>GSHx</sub> | Gate-on voltage                                                     | VDH = VSH = 6 V<br>ICP = -5 mA, DC measure GH-SH                                        | VSHx +   | -      | -      | V    |

| V <sub>GSHx</sub> | Gate-on voltage                                                     | VDH = VSH >= 8 V                                                                        | VSHx +-  | VSHx + | VSHx + | V    |

| R <sub>GHx</sub>  | Passive gate-pull-down resistance                                   | ICP = -10 mA, DC measure GH-SH  Resistance between gate HS and ground when device is ON | -        | 1      | -      | ΜΩ   |

| R <sub>SHx</sub>  | Passive source-pull-down resistance                                 | Resistance between source HS and ground when device is ON                               | -        | 1      | -      | ΜΩ   |

| V <sub>GLx</sub>  | Gate-on voltage                                                     | VSL = 0 V, VDH = 6 V                                                                    | VSLx + 6 | _      | _      | V    |

DS15025 - Rev 1 page 15/130

| Symbol               | Parameter                            | Test condition                                            | Min      | Тур    | Max          | Unit     |  |

|----------------------|--------------------------------------|-----------------------------------------------------------|----------|--------|--------------|----------|--|

|                      |                                      | ICP = -5 mA, DC measure GL-SL                             |          |        |              |          |  |

|                      |                                      | VSL = 0 V, VDH ≥ 8 V                                      |          | VSLx + | VSLx +       |          |  |

| $V_{GLx}$            | Gate-on voltage                      | ICP = -10 mA, DC measure GL-SL                            | VSLx + 8 | 10     | 12           | V        |  |

| R <sub>GLx</sub>     | Passive gate-pull-down resistance    | Resistance between gate LS and ground when device is ON   | -        | 1      | -            | ΜΩ       |  |

| R <sub>SL</sub>      | Passive source-pull-down resistance  | Resistance between source LS and ground when device is ON | -        | 125    | -            | ΚΩ       |  |

| .,                   | Step voltage1 for x channel          | VSTEP1_CONFx = 00/01                                      |          |        | ,            | ļ        |  |

| V <sub>step1xl</sub> | x = 18                               | Switch ON, command = 1                                    | -55%     | 1.1    | +55%         | V        |  |

| \ /                  | Step voltage1 for x channel          | VSTEP1_CONFx = 00/01                                      | 4-04     |        | 4-0/         | .,       |  |

| V <sub>step1xh</sub> | x = 18                               | Switch OFF command = 0                                    | -47%     | 1.3    | +47%         | V        |  |

| .,                   | Step voltage1 for x channel          | VSTEP1_CONFx = 10/11                                      |          |        |              |          |  |

| V <sub>step1xl</sub> | x = 18                               | Switch ON, command = 1                                    | -35%     | 2.2    | +35%         | V        |  |

|                      | Step voltage1 for x channel          | VSTEP1_CONFx = 10/11                                      |          |        |              |          |  |

| V <sub>step1xh</sub> | x = 18                               | Switch OFF command = 0                                    | -35%     | 2.6    | +35%         | V        |  |

|                      | Step voltage2 for x channel          | VSTEP2_CONFx = 00                                         |          |        |              |          |  |

| V <sub>step2xl</sub> | x = 18                               | Switch ON, command = 1                                    | -31%     | 2.67   | +31%         | V        |  |

|                      | Step voltage2 for x channel          | VSTEP2_CONFx = 00                                         |          |        |              |          |  |

| V <sub>step2xh</sub> | x = 18                               | Switch OFF command = 0                                    | -28%     | 3.33   | +28%         | V        |  |

|                      | Stan voltage? for v channel          | VSTEP2_CONFx = 01                                         |          |        |              |          |  |

| V <sub>step2x</sub>  | Step voltage2 for x channel $x = 18$ | Switch ON, command = 1                                    | -27%     | 3.56   | +27%         | V        |  |

|                      | Otan walta as 2 fan walta anal       | VSTEP2_CONFx = 01                                         |          |        |              |          |  |

| V <sub>step2xh</sub> | Step voltage2 for x channel $x = 18$ | Switch OFF command = 0                                    | -25%     | 4.44   | +25%         | V        |  |

|                      | Otan walta as 2 fan walta anal       | VSTEP2_CONFx = 10                                         |          |        | +24%         |          |  |

| V <sub>step2xl</sub> | Step voltage2 for x channel $x = 18$ | Switch ON, command = 1                                    | -24%     | 4.45   |              | V        |  |

|                      | Otan calle as O face of the same     | VSTEP2_CONFx = 10                                         |          |        |              |          |  |

| V <sub>step2xh</sub> | Step voltage2 for x channel $x = 18$ | Switch OFF command = 0                                    | -24%     | 5.55   | +24%         | V        |  |

|                      | 0, 1, 0, 1, 1                        | VSTEP2_CONFx = 11                                         |          |        |              |          |  |

| V <sub>step2xl</sub> | Step voltage2 for x channel $x = 18$ | Switch ON, command = 1                                    | -24%     | 5.34   | +24%         | V        |  |

|                      |                                      |                                                           |          |        |              |          |  |

| V <sub>step2xh</sub> | Step voltage2 for x channel $x = 18$ | VSTEP2_CONFx = 11 Switch OFF command = 0                  | -24%     | 6.66   | +24%         | V        |  |

|                      |                                      |                                                           |          |        |              |          |  |

|                      |                                      | Gate drivers dynamic parameters                           |          |        |              |          |  |

| $t_{GLxr}$           | Rise time LS                         | VDH = 13.5 V; VSLx = 0 V                                  | -        | -      | 2.1          | μs       |  |

|                      |                                      | RG = 0 Ω; CG = 10 nF                                      |          |        |              |          |  |

| t <sub>GHxr</sub>    | Rise time HS                         | VDH = 13.5 V; VSLx = 0 V                                  | _        | -      | 2.1          | μs       |  |

|                      |                                      | RG = 0 Ω; CG = 10 nF                                      |          |        |              |          |  |

| $t_{GLxf}$           | Fall time LS                         | VDH = 13.5 V; VSLx = 0 V                                  | _        | _      | 2.1          | μs       |  |

|                      |                                      | RG = 0 Ω; CG = 10 nF                                      |          |        |              |          |  |

| t <sub>GHxf</sub>    | Fall time HS                         | VDH = 13.5 V; VSLx = 0 V                                  | _        | _      | 2.1          | μs       |  |

| //                   |                                      | RG = 0 Ω; CG = 10 nF                                      |          |        |              | <u>'</u> |  |

| $V_{GSHx}$           | Gate-on voltage HS                   | Maximum VGH-VSH in turn-on condition                      | -        | -      | VSHx +<br>13 | V        |  |

| V <sub>GSLx</sub>    | Gate-on voltage LS                   | Maximum VGL-VSL in turn-on condition                      | _        | _      | VSLx +       | V        |  |

DS15025 - Rev 1 page 16/130

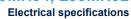

Figure 6. H-driver delay times

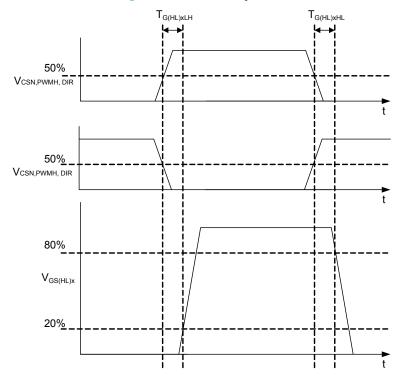

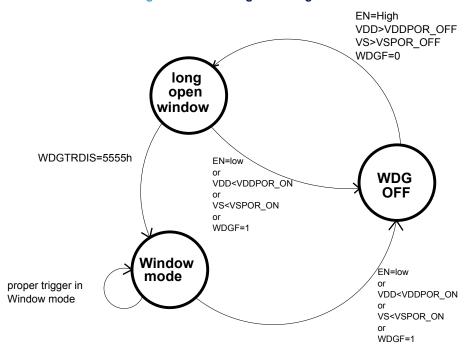

# 2.4.6 Watchdog

Table 13. Watchdog

| Symbol               | Parameter        | Test condition     | Min | Тур | Max | Unit |

|----------------------|------------------|--------------------|-----|-----|-----|------|

| t <sub>LOW</sub>     | Long open window | Guaranteed by scan | 52  | -   | 87  | ms   |

| t <sub>CW</sub>      | Closed window    | Guaranteed by scan | 11  | -   | 20  | ms   |

| t <sub>WDP</sub>     | Watchdog period  | Guaranteed by scan | 32  | -   | 54  | ms   |

| t <sub>timeout</sub> | Timeout period   | Guaranteed by scan | 90  | -   | 110 | ms   |

Figure 7. Watchdog early, late and safe window

DS15025 - Rev 1 page 17/130

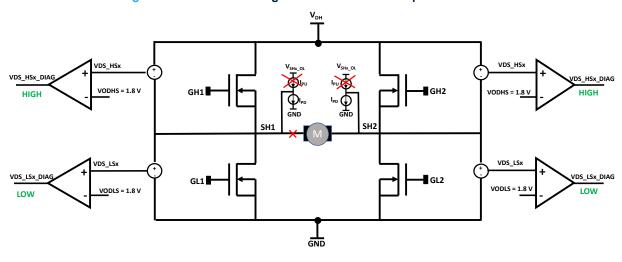

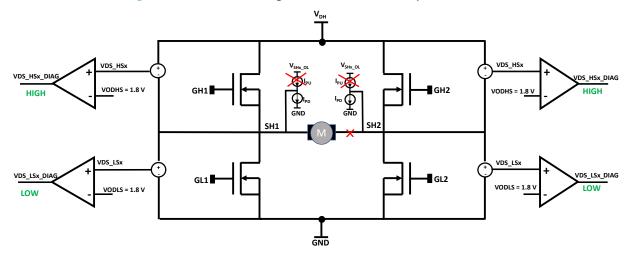

## 2.4.7 Open-load monitoring external

The voltages are referred to power ground and currents are assumed positive when the current flows into the pin.  $6 \text{ V} \le \text{V}_{DH} \le 28 \text{ V}$ ;  $\text{T}_{j} = -40 \,^{\circ}\text{C}$  to 150  $^{\circ}\text{C}$ , unless otherwise specified.

Table 14. Open-load monitoring threshold

| Symbol              | Parameter                                                    | Test condition             | Min     | Тур | Max  | Unit |

|---------------------|--------------------------------------------------------------|----------------------------|---------|-----|------|------|

|                     |                                                              | VDH = 13.5 V               |         |     |      |      |

| V <sub>ODLS</sub>   | Low-side drain-source monitor off state-threshold voltage    | VDS_CONFx = 1xxx           | 1.5     | 1.8 | 2.1  | V    |

| VODES               | Low-side drain-source monitor on state-timeshold voltage     | or                         | 1.0     | 1.0 | 2.1  |      |

|                     |                                                              | (HB_MODEx = 00, OUTEx = 1) |         |     |      |      |

|                     |                                                              | VDH = 13.5 V               |         |     |      |      |

| V <sub>ODHS</sub>   | High-side drain-source monitor off state-threshold voltage   | VDS_CONFx = 1xxx           | 1.5     | 1.8 | 2.1  | V    |

| ODHS                | riigii side didiii sedice monitoi on state tiresnota voitage | or                         | 1.0     | 1.0 | 2.1  |      |

|                     |                                                              | (HB_MODEx = 00, OUTEx = 1) |         |     |      |      |

| V <sub>SHx_OL</sub> | Output voltage of selected SHx in open-load test mode        | VSLx = 0 V; VDH = 13.5 V   | 2.1     | 3   | 3.9  | V    |

| I <sub>shx PU</sub> | Pull-up current in DIAG OFF                                  | VSHx = 0 V; VDH = 13.5 V   | 0.5     | 0.9 | 1.25 | mA   |

| 'snx_PU             | Full-up current in DIAG OFF                                  | DIAGOFF_CURR_SEL = 0       | 0.5     | 0.9 | 1.23 | IIIA |

| I <sub>shx PU</sub> | Pull-up current in DIAG OFF                                  | VSHx = 0 V; VDH = 13.5 V   | 1.2     | 1.6 | 2.4  | mA   |

| 'SNX_PU             | Tull-up current in DIAC Of T                                 | DIAGOFF_CURR_SEL = 1       | 1.2     | 1.0 | 2.4  | ША   |

| Lu. pp              | Pull-down current in DIAG OFF                                | VSHx = 3 V; VDH = 13.5 V   | 200     | 300 | 400  | μA   |

| I <sub>shx_PD</sub> | Tull-down current in DIAC OTT                                | DIAGOFF_CURR_SEL = 0       | 200     | 300 | 400  | μΛ   |

| later DD            | Pull-down current in DIAG OFF                                | VSHx = 3 V; VDH = 13.5 V   | 400     | 600 | 800  | μA   |

| I <sub>shx_PD</sub> | T diredown current in DIAC Of I                              | DIAGOFF_CURR_SEL = 1       | 400 600 | 000 | 000  | μΛ   |

| t <sub>diag</sub>   | DIAG OFF time                                                |                            | 130     | 200 | 270  | μs   |

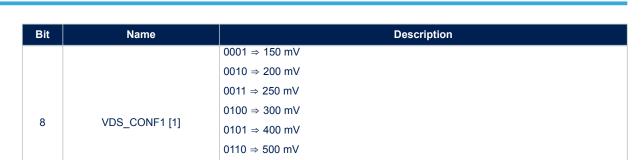

# 2.4.8 Drain-source monitoring threshold

$V_{DH}$  = 6 V to 28 V;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40 °C to 150 °C,  $V_{CP}$  >  $V_{DH}$  + 8.5 V, all voltages are referred to ground and currents are assumed positive when flow into the pin (unless otherwise specified).

Table 15. Drain-Source monitoring threshold

| Symbol            | Parameter                         | Test condition   | Min   | Тур  | Max   | Unit |

|-------------------|-----------------------------------|------------------|-------|------|-------|------|

| V <sub>SCd0</sub> | Drain-source monitoring threshold | VDS_CONFx = 0000 | 0.045 | 0.08 | 0.095 | V    |

| V <sub>SCd1</sub> | Drain-source monitoring threshold | VDS_CONFx = 0001 | 0.12  | 0.16 | 0.18  | V    |

| V <sub>SCd2</sub> | Drain-source monitoring threshold | VDS_CONFx = 0010 | 0.16  | 0.20 | 0.24  | V    |

| V <sub>SCd3</sub> | Drain-source monitoring threshold | VDS_CONFx = 0011 | 0.20  | 0.25 | 0.30  | V    |

| V <sub>SCd4</sub> | Drain-source monitoring threshold | VDS_CONFx = 0100 | 0.24  | 0.30 | 0.36  | V    |

| V <sub>SCd5</sub> | Drain-source monitoring threshold | VDS_CONFx = 0101 | 0.32  | 0.40 | 0.48  | V    |

| V <sub>SCd6</sub> | Drain-source monitoring threshold | VDS_CONFx = 0110 | 0.40  | 0.50 | 0.62  | V    |

| V <sub>SCd7</sub> | Drain-source monitoring threshold | VDS_CONFx = 0111 | 0.48  | 0.60 | 0.72  | V    |

DS15025 - Rev 1 page 18/130

#### 2.4.9 Drain source monitoring blanking time

$V_{DH}$  = 6 V to 28 V;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40 °C to 150 °C,  $V_{CP}$  >  $V_{DH}$  + 8.5 V, all voltages are referred to ground and currents are assumed positive when flow into the pin (unless otherwise specified).

Table 16. Drain source monitoring external H-bridge

| Symbol             | Parameter                                 | Test condition                                                                                                                               | Min | Тур   | Max  | Unit |

|--------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|------|

| t <sub>B0000</sub> | DS monitoring blank time                  | VDS_BLANKx = 0000                                                                                                                            | 0.5 | 0.625 | 0.85 | μs   |

| t <sub>B0001</sub> | DS monitoring blank time                  | VDS_BLANKx = 0001                                                                                                                            | 0.8 | 1     | 1.2  | μs   |

| t <sub>B0010</sub> | DS monitoring blank time                  | VDS_BLANKx = 0010                                                                                                                            | 1   | 1.25  | 1.5  | μs   |

| t <sub>B0011</sub> | DS monitoring blank time                  | VDS_BLANKx = 0011                                                                                                                            | 1.2 | 1.5   | 1.8  | μs   |

| t <sub>B0100</sub> | DS monitoring blank time                  | VDS_BLANKx = 0100                                                                                                                            | 1.6 | 2     | 2.4  | μs   |

| t <sub>B0101</sub> | DS monitoring blank time                  | VDS_BLANKx = 0101                                                                                                                            | 2.4 | 3     | 3.6  | μs   |

| t <sub>B0110</sub> | DS monitoring blank time                  | VDS_BLANKx = 0110                                                                                                                            | 3.2 | 4     | 4.8  | μs   |

| t <sub>B0111</sub> | DS monitoring blank time                  | VDS_BLANKx = 0111                                                                                                                            | 4   | 5     | 6    | μs   |

| t <sub>B1000</sub> | DS monitoring blank time                  | VDS_BLANKx = 1000                                                                                                                            | 4.8 | 6     | 7.2  | μs   |

| t <sub>B1001</sub> | DS monitoring blank time                  | VDS_BLANKx = 1001                                                                                                                            | 5.6 | 7     | 8.4  | μs   |

| t <sub>B1010</sub> | DS monitoring blank time                  | VDS_BLANKx = 1010                                                                                                                            | 6.4 | 8     | 9.6  | μs   |

| tscs               | Drain-source comparator propagation delay | VDH = 14 V VDS jump from 10 mV to 1 V, time from filter time end to VGS external FET under threshold without external MOSFETs <sup>(1)</sup> |     | -     | 1    | μs   |

<sup>1.</sup> Not subject to production test, specified by design.

Note: For the VDS\_BLANKx = 1x11 the default value (VDS\_BLANKx = 0000) will be set.

## 2.4.10 Drain source monitoring filter time

$V_{DH}$  = 6 V to 28 V;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40 °C to 150 °C,  $V_{CP}$  >  $V_{DH}$  + 8.5 V, all voltages are referred to ground and currents are assumed positive when flow into the pin (unless otherwise specified).

Table 17. Drain source monitoring filter time

| Symbol             | Parameter                                | Test condition  | Min | Тур | Max  | Unit |

|--------------------|------------------------------------------|-----------------|-----|-----|------|------|

| t <sub>FT000</sub> | DS monitoring filter time <sup>(1)</sup> | VDS_FILTx = 000 | 0.4 | 0.5 | 0.85 | μs   |

| t <sub>FT001</sub> | DS monitoring filter time <sup>(1)</sup> | VDS_FILTx = 001 | 0.8 | 1   | 1.4  | μs   |

| t <sub>FT010</sub> | DS monitoring filter time <sup>(1)</sup> | VDS_FILTx = 010 | 1.6 | 2   | 2.4  | μs   |

| t <sub>FT011</sub> | DS monitoring filter time <sup>(1)</sup> | VDS_FILTx = 011 | 2.4 | 3   | 3.6  | μs   |

| t <sub>FT100</sub> | DS monitoring filter time <sup>(1)</sup> | VDS_FILTx = 100 | 3.2 | 4   | 4.8  | μs   |

| t <sub>FT101</sub> | DS monitoring filter time <sup>(1)</sup> | VDS_FILTx = 101 | 4   | 5   | 6    | μs   |

| t <sub>FT110</sub> | DS monitoring filter time <sup>(1)</sup> | VDS_FILTx = 110 | 4.8 | 6   | 7.2  | μs   |

<sup>1.</sup> Not subject to production test, specified by design.

Note: If the VDS\_FILTx = 111 the default value (VDS\_FILTx = 000) will be set.

DS15025 - Rev 1 page 19/130

#### 2.4.11 Cross current protection time

$V_{DH}$  = 6 V to 28 V;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40 °C to 150 °C,  $V_{CP}$  >  $V_{DH}$  + 8.5 V, all voltages are referred to ground and currents are assumed positive when flow into the pin (unless otherwise specified).

Table 18. Cross current protection time

| Symbol | Parameter                     | Test condition                             | Min  | Тур | Max  | Unit |

|--------|-------------------------------|--------------------------------------------|------|-----|------|------|

| tDT000 | Cross-current protection time | Tested by scan, DTP_REF = 0 <sup>(1)</sup> | 350  | 500 | 650  | ns   |

| tDT001 | Cross-current protection time | Tested by scan, DTP_REF = 0 <sup>(1)</sup> | 0.8  | 1   | 1.2  | μs   |

| tDT010 | Cross-current protection time | Tested by scan, DTP_REF = 0 <sup>(1)</sup> | 1.6  | 2   | 2.4  | μs   |

| tDT011 | Cross-current protection time | Tested by scan, DTP_REF = 0 <sup>(1)</sup> | 2.4  | 3   | 3.6  | μs   |

| tDT100 | Cross-current protection time | Tested by scan, DTP_REF = 0 <sup>(1)</sup> | 3.2  | 4   | 4.8  | μs   |

| tDT101 | Cross-current protection time | Tested by scan, DTP_REF = 0 <sup>(1)</sup> | 4    | 5   | 6    | μs   |

| tDT110 | Cross-current protection time | Tested by scan, DTP_REF = 0 <sup>(1)</sup> | 4.8  | 6   | 7.2  | μs   |

| tDT111 | Cross-current protection time | Tested by scan, DTP_REF = 0 <sup>(1)</sup> | 12.8 | 16  | 19.2 | μs   |

<sup>1.</sup> When DTP\_REF = 1 it is necessary to add 850 ns to the maximum value.

Note: Not subject to production test, specified by design.

#### 2.4.12 External temperature diode

$V_{DH}$  = 6 V to 28 V;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40 °C to 150 °C,  $V_{CP}$  >  $V_{DH}$  + 8.5 V, all voltages are referred to ground and currents are assumed positive when flow out from the pin (unless otherwise specified).

Table 19. External temperature diode

| Symbol              | Parameter              | Test condition    | Min  | Тур  | Max  | Unit |

|---------------------|------------------------|-------------------|------|------|------|------|

| I <sub>DIODE</sub>  | Diode current          | IDIODE_CONFx = 00 | 200  | 250  | 300  | μΑ   |

| I <sub>DIODE</sub>  | Diode current          | IDIODE_CONFx = 01 | 400  | 500  | 600  | μΑ   |

| I <sub>DIODE</sub>  | Diode current          | IDIODE_CONFx = 10 | 600  | 750  | 900  | μA   |

| I <sub>DIODE</sub>  | Diode current          | IDIODE_CONFx = 11 | 800  | 1000 | 1200 | μΑ   |

| V <sub>dioinc</sub> | Diode voltage range    |                   | 0.3  | -    | 2    | V    |

| -                   | ADC nbit               |                   | -    | 11   | -    | bit  |

| -                   | ADC offset error       |                   | -2   | -    | +2   | mV   |

| -                   | ADC gain error vs temp |                   | -    | -    | +1.5 | %    |

| -                   | ADC total gain error   |                   | -2.5 | -    | +2.5 | %    |

DS15025 - Rev 1 page 20/130

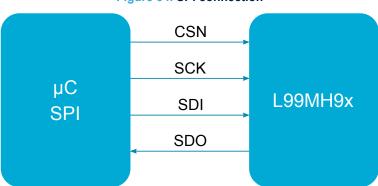

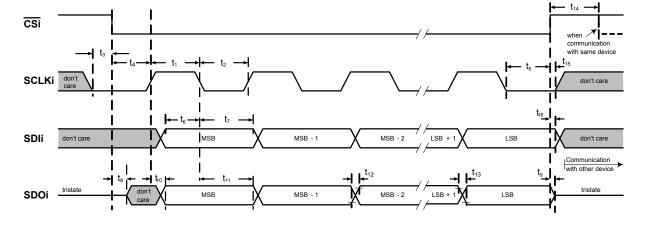

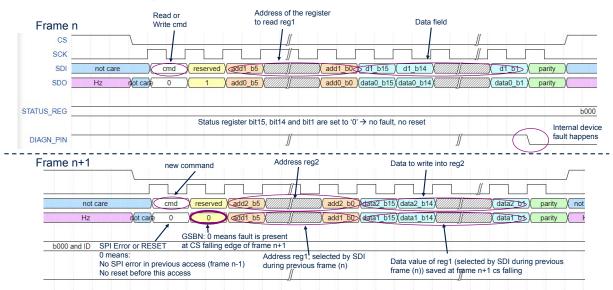

#### 2.4.13 SPI

$V_{DH}$  = 6 V to 28 V;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40 °C to 150 °C,  $V_{CP}$  >  $V_{DH}$  + 8.5 V, all voltages are referred to ground and currents are assumed positive when flow into the pin (unless otherwise specified).

Table 20. SPI parameters

| Symbol                         | Parameter                                                       | Test condition                                                   | Min       | Тур | Max  | Unit |

|--------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|-----------|-----|------|------|

| DC param                       | eters                                                           |                                                                  |           |     |      |      |

| $V_{IL}$                       | Low-level input voltage                                         |                                                                  | 0.75      | -   | 1.65 | V    |

| V <sub>IH</sub>                | High-level input voltage                                        |                                                                  | 0.85      | -   | 1.75 | V    |

| $V_{\text{ihyst}}$             | Input voltage hysteresis                                        |                                                                  | 0.1       | -   | 0.5  | V    |

| I <sub>CSN in</sub>            | CSN pull-up current input                                       | Probe current on force input pin at VHL voltage in DC conditions | 20        | 40  | 60   | uA   |

| I <sub>SDI in</sub>            | SCLK, SDI pull down current input                               | Probe current on force input pin at VIL voltage in DC conditions | 20        | 40  | 60   | μA   |

| V <sub>SDO low</sub>           | SDO output low voltage                                          | ISDO out = 1 mA                                                  | -         | -   | 0.4  | V    |

| V <sub>SDO high</sub>          | SDO output high voltage                                         | ISDO out = 1 mA<br>3.0 V ≤ VDD ≤ 5.5 V                           | VDD - 0.4 | -   | -    | V    |

| I <sub>SDO leak</sub>          | SDO tristate leakage current                                    | VCSN ≥ 2 V<br>0 V ≤ VSDO IN ≤ VDD                                | -10       | -   | 10   | μA   |

| AC param                       | neters                                                          |                                                                  |           |     |      |      |

| f <sub>CLK</sub>               | Clock frequency                                                 | CSDO = 50 pF                                                     | -         | -   | 6    | MHz  |

| t <sub>CLK</sub>               | Clock period                                                    | CSDO = 50 pF                                                     | 166       | -   | -    | ns   |

| t <sub>1</sub> <sup>(1)</sup>  | Clock high time                                                 |                                                                  | 75        | -   | -    | ns   |

| t <sub>2</sub> <sup>(1)</sup>  | Clock low time                                                  |                                                                  | 75        | -   | -    | ns   |

| t <sub>3</sub> <sup>(1)</sup>  | CLK low before CSN active                                       |                                                                  | 20        | -   | -    | ns   |

| t <sub>4</sub> <sup>(1)</sup>  | CLK active after CSN active                                     |                                                                  | 100       | -   | -    | ns   |

| t <sub>5</sub> <sup>(1)</sup>  | CLK passive before CSN passive                                  |                                                                  | 100       | -   | -    | ns   |

| t <sub>6</sub> <sup>(1)</sup>  | SDI setup time                                                  |                                                                  | 30        | -   | -    | ns   |

| t <sub>7</sub> <sup>(1)</sup>  | SDI hold time                                                   |                                                                  | 30        | -   | -    | ns   |

| t <sub>8</sub> <sup>(1)</sup>  | SDO active after CSN active                                     | CSDO = 50 pF                                                     | -         | -   | 100  | ns   |

| t <sub>9</sub> <sup>(1)</sup>  | SDO tristate after CSN passive                                  | CSDO = 50 pF                                                     | -         | -   | 100  | ns   |

| t <sub>10</sub> <sup>(1)</sup> | SDO valid time                                                  | CSDO = 50 pF                                                     | -         | -   | 70   | ns   |

| t <sub>11</sub> <sup>(1)</sup> | SDO hold time                                                   | CSDO = 50 pF                                                     | 10        | -   | -    | ns   |

| t <sub>12</sub> <sup>(1)</sup> | SDO rise time                                                   | CSDO = 50 pF                                                     | -         | -   | 50   | ns   |

| t <sub>13</sub> <sup>(1)</sup> | SDO fall time                                                   | CSDO = 50 pF                                                     | -         | -   | 50   | ns   |

| t <sub>14</sub> <sup>(1)</sup> | CSN passive time to next frame                                  |                                                                  | 600       | -   | -    | ns   |

| t <sub>15</sub> <sup>(1)</sup> | CLK passive time to next                                        |                                                                  | 100       | -   | -    | ns   |

| t <sub>16</sub> <sup>(1)</sup> | SDI data of next frame                                          |                                                                  | 20        | -   | -    | ns   |

| t <sub>CSN_fail</sub>          | CSN low timeout                                                 | Tested by scan                                                   | 20        | 35  | 50   | ms   |

| t <sub>START</sub>             | Time at the start up before a correct SPI frame can be received | Tested by scan                                                   | -         | -   | 300  | μs   |

<sup>1.</sup> See the Figure 1.

DS15025 - Rev 1 page 21/130

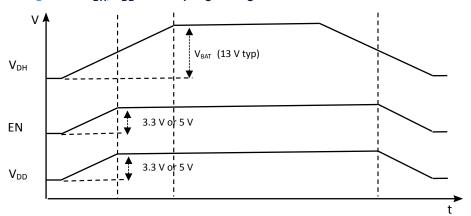

# 2.4.14 Indirect current sense output