# Automotive flexible U-chip for braking and transmission

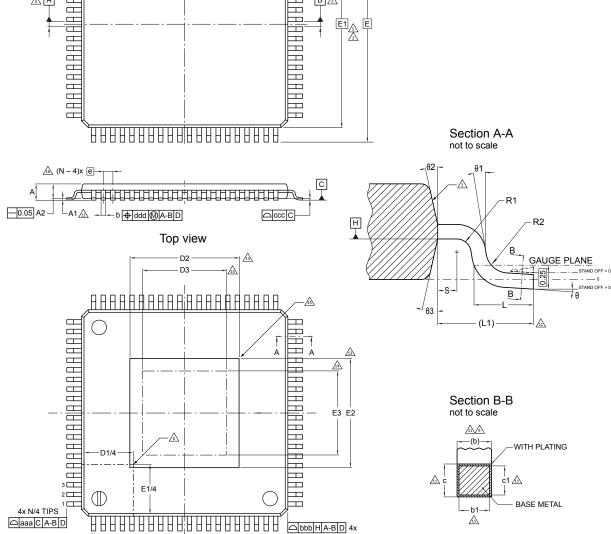

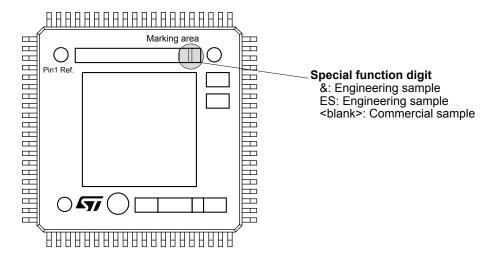

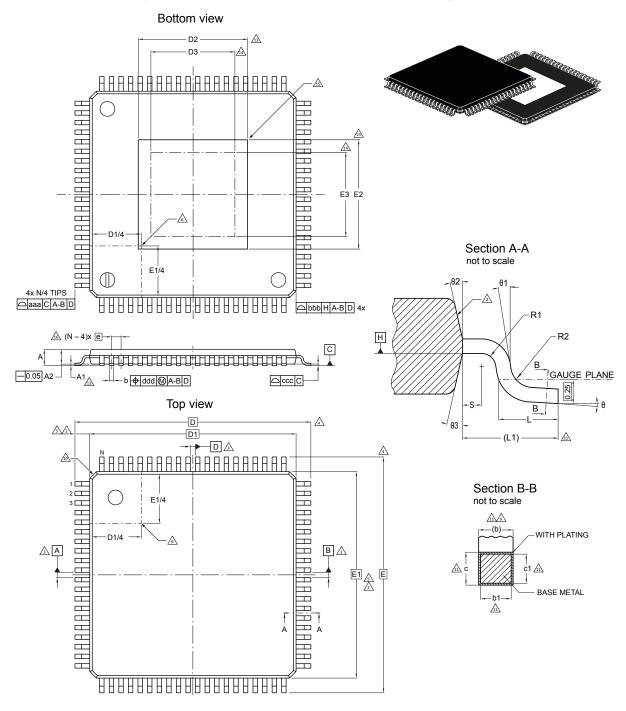

TQFP80 (Exp. pad down)

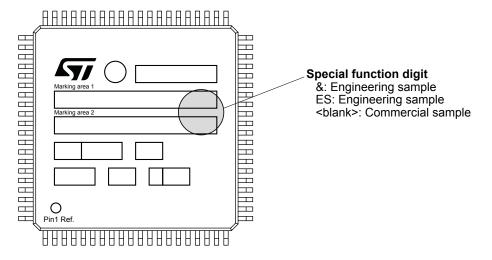

TQFP80 (Exp. pad up)

# Product status link

| Product summary |                          |               |  |  |  |  |  |  |  |

|-----------------|--------------------------|---------------|--|--|--|--|--|--|--|

| Order code      | Order code Package       |               |  |  |  |  |  |  |  |

| L9300TU80T      | TQFP80<br>exp. pad<br>up | Tray          |  |  |  |  |  |  |  |

| L9300TD80T      | TQFP80                   | Tray          |  |  |  |  |  |  |  |

| L9300TD80T-TR   | exp. pad<br>down         | Tape and reel |  |  |  |  |  |  |  |

# **Features**

- Four voltage regulators

- One configurable 5 V or 6.5 V buck regulator

- One configurable 5 V linear/tracking regulator

- Two linear regulators with selectable output voltage

- Four tracking regulators/wheel speed sensor interfaces

- Six low-side/high-side current control drivers

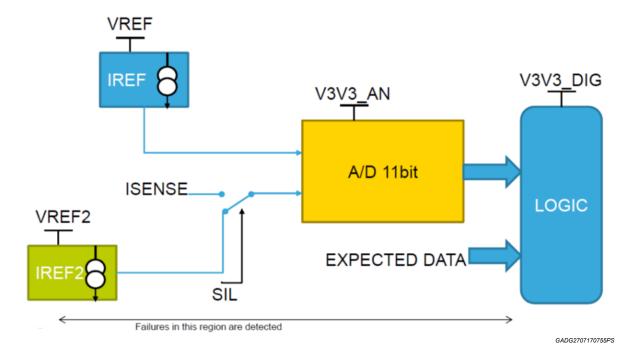

- Integrated current sense path

- Current accuracy (in normal range)

- ± 8 mA in 0 to 0.5 A range

- ± 1% in 0.5 A to 1.5 A range

- Current accuracy (in extended range)

- ± 20 mA in 0 to 0.075 A range

- -15 / +12 mA 0.075 A to 0.3 A

- 5 / +4% in 0.3 A to 0.5 A range

- ± 4% in 0.5 A to 2 A range

- Max driver RDS<sub>ON</sub> 500 m $\Omega$  @ 175 °C

- 11-bit current set-point resolution

- Variable and fixed frequency current control algorithm

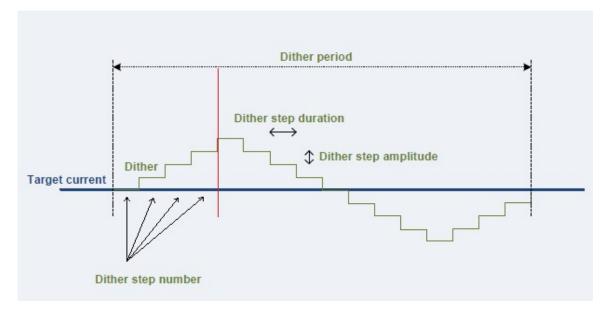

- Programmable dither function

- Selectable driver slew-rate control

- Two high-side NFET pre-drivers

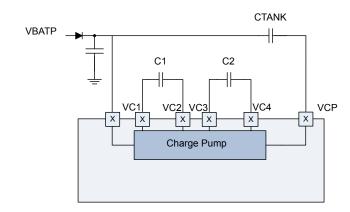

- Integrated charge-pump

- CAN transceiver

- Two watchdogs types:

- Hardware watchdog

- Software Query and Answer based watchdog

- Wake-up control

- Temperature sensor and monitoring

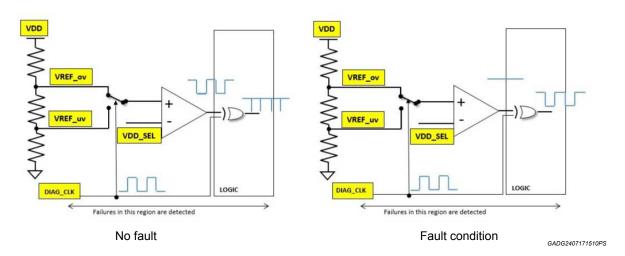

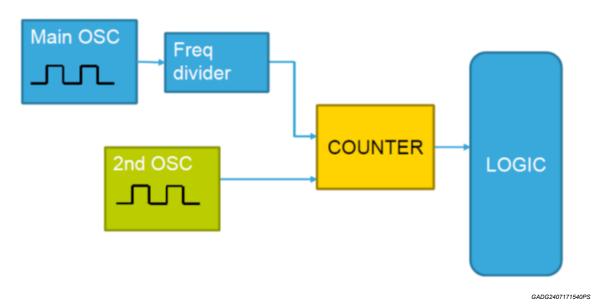

- Dual band gap reference and oscillator

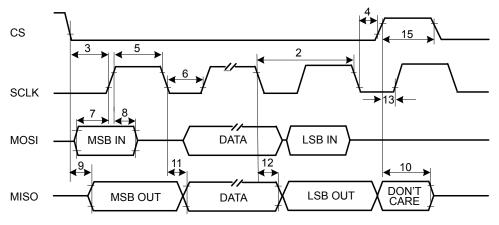

- 32-bit SPI interface

- TQFP 80 EP (14x14)

# **Description**

The device is an integrated circuit designed for automotive environment and implemented in BCD8s\_auto technology.

The device configurability involves both the supplies block and the valve drivers stage and particularly addresses to transmission applications.

# 1 Main features details

# 1.1 Supplies

# 1.1.1 VDD1 regulator

VDD1 is a buck regulator with internal N-ch FET that can provide 6.5 V or 5 V with 3% accuracy.

# 1.1.2 VDD2 regulator

VDD2 is a configurable internal regulator. It can work as tracking regulator (± 20 mV) or linear 5 V regulator (2% accuracy) and can provide up to 200 mA. VDD2 regulator is short to battery protected

# 1.1.3 VDD3 regulator

VDD3 is a linear regulator based on an external pass transistor. The output voltage selection is obtained through an external voltage divider. The accuracy of VDD3 is ± 2%.

# 1.1.4 VDD4 regulator

VDD4 is a linear regulator based on an external pass transistor. The output voltage selection is obtained through an external voltage divider. The accuracy of VDD4 is  $\pm$  2%.

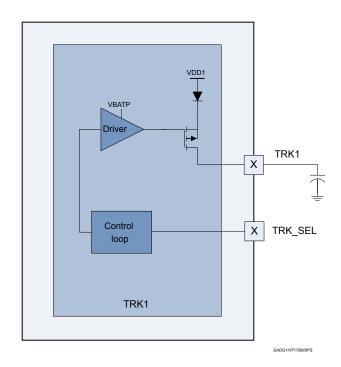

# 1.1.5 TRK 1, 2, 3, 4

TRK1, TRK2, TRK3, TRK4 are 4 additional configurable tracking regulators. The regulators track the TRK\_SEL pin voltage with an error of  $\pm$  20 mV. The tracking regulator outputs can be configured to be used alternatively as wheel speed interfaces.

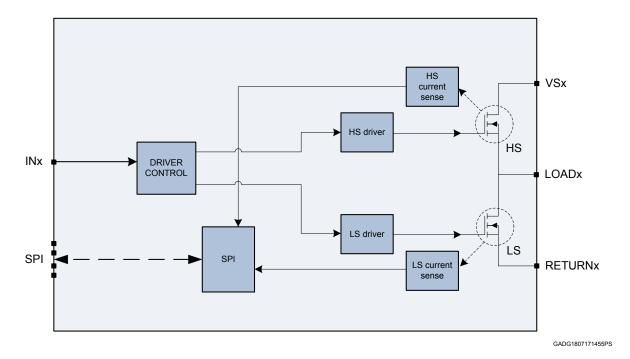

# 1.2 Valve drivers

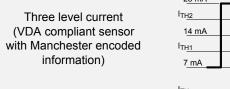

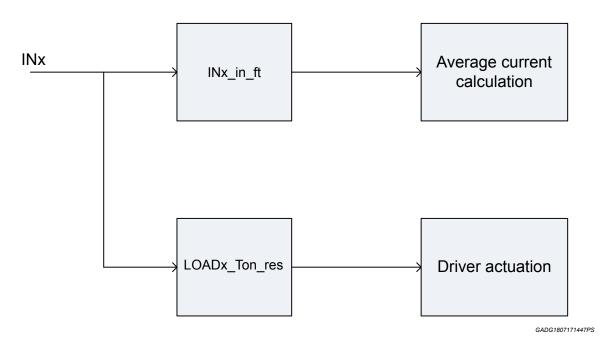

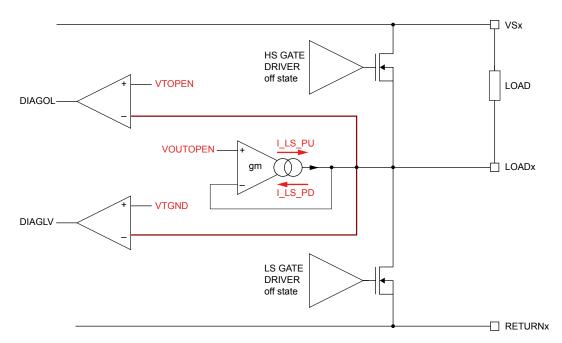

#### 1.2.1 Current controlled channels

The device provides 6 current controlled channels. Each channel is based on a LS/HS driver structure. The device is able to work as low–side driver (with high–side active freewheeling) or as high–side driver (with low–side active freewheeling).

# 1.3 Others

# 1.3.1 High-side pre-driver

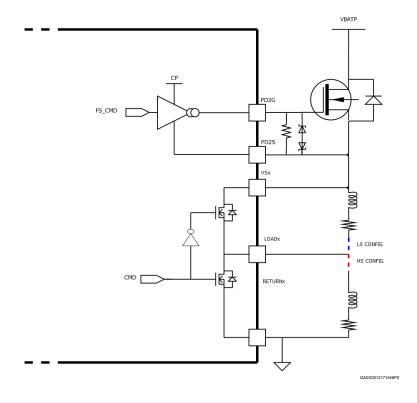

The device provides 2 High-side pre-drivers, and one of them is able to work in PWM mode up to roughly 18 kHz.

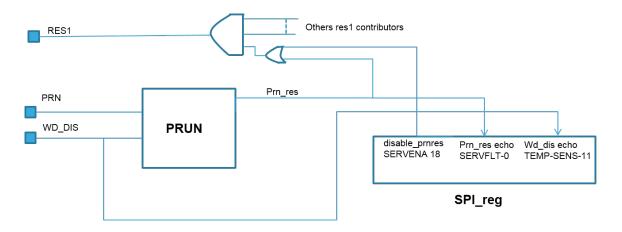

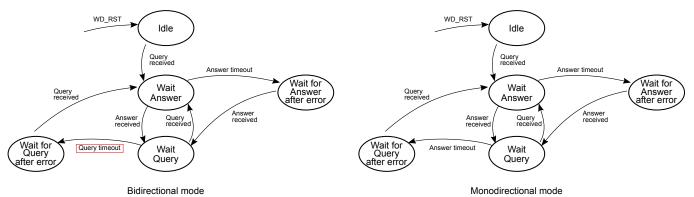

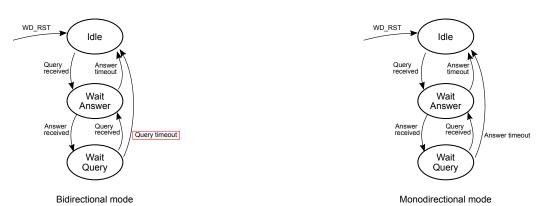

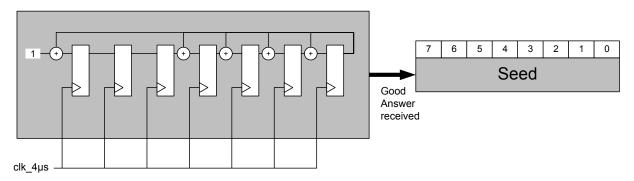

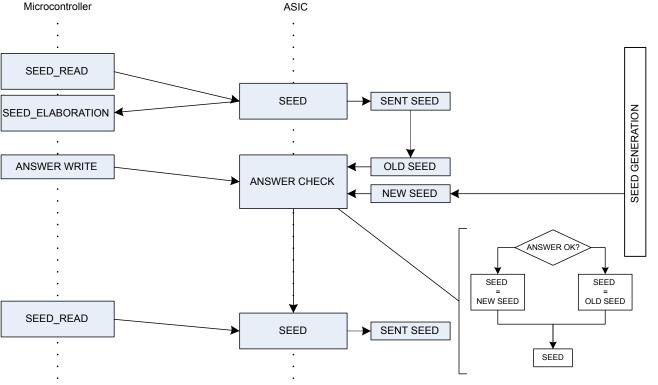

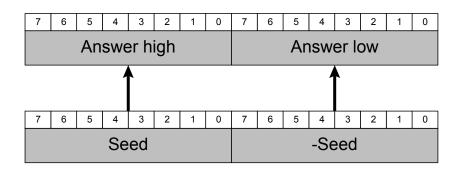

# 1.3.2 Watchdog

Watchdog functionality to monitor CPU activity.

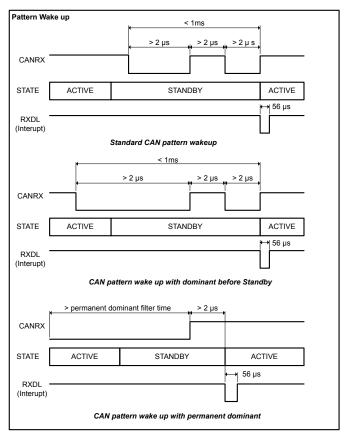

#### 1.3.3 CAN

The device includes a CAN interface.

# 1.3.4 **RESET**

The device includes two Reset pins. Both of them can be used as output while one of them can be used also as input.

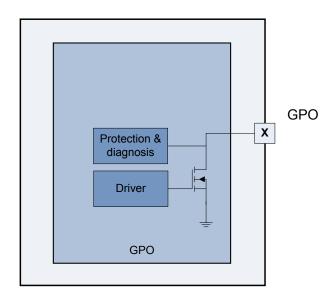

# 1.3.5 GPO

The device provides a low–side open drain general purpose output. This output can be used as a standard low–side output or as a configurable interrupt generator through a dedicated SPI bit in the Service Enable register.

DS12258 - Rev 5 page 2/178

GADG0607171209PS

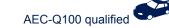

# 2 Block diagrams

VBATT VBATP Transient Protection VCP VBATP. VBATP PD1D Vds cor Charge Pump PD1G GND PD1S GNDA **VBATP** Bandgap1 PD2G NFET Pre-Driver On/Off X PD2S VSOL System Status Bandgap2 WAKE X Temperature Sensor VDD1\_SEL CAN\_VDD VDD1 CANHI CANLO X VROUT CANTXD CANRXDX VDD2\_SUP CAN\_DIS VBATP Configuration & Control EN\_DR VDD 2 VDD2 RES1 RESET RES2 X VDD2\_SEL VDDIO VDD3\_G CS VDD 3 Linear VDD3\_SEL SCLK SPI Oscillator 1 SDI VDD4\_SH Х Oscillator2 SDO VDD4\_SL Х GPO GPO X VDD4\_BTS Watch dog VDD4 G VDD 4 Linear VDD4\_S WSI\_CONF/ TRK\_SEL VDD4\_SEL X IN1 VSOL WSI1/ TRK1 WSII X VS1 DOUT1 LOAD1 WSI2/ TRK2 WS12 X RETURN-1 DOUT2 WSI3/ VSOL TRK3 พรต DOUT3 X LOAD2 WSI4/ TRK4 WS4 X RETURN-2 DOUT4 X IN3 VSOL IN5 X X VS3 VS2 VSOL VS5 LOAD5 X LOAD3 RETURN-5 X RETURN-3 X IN4 VSOL IN6 X VSOL VS6 X x VS4 X LOAD4 LOAD6 X RETURN-6 X RETURN-4

Figure 1. Internal block diagram

DS12258 - Rev 5 page 3/178

Figure 2. Internal block diagram with internal supply domain partitioning

GADG0607171507PS

DS12258 - Rev 5 page 4/178

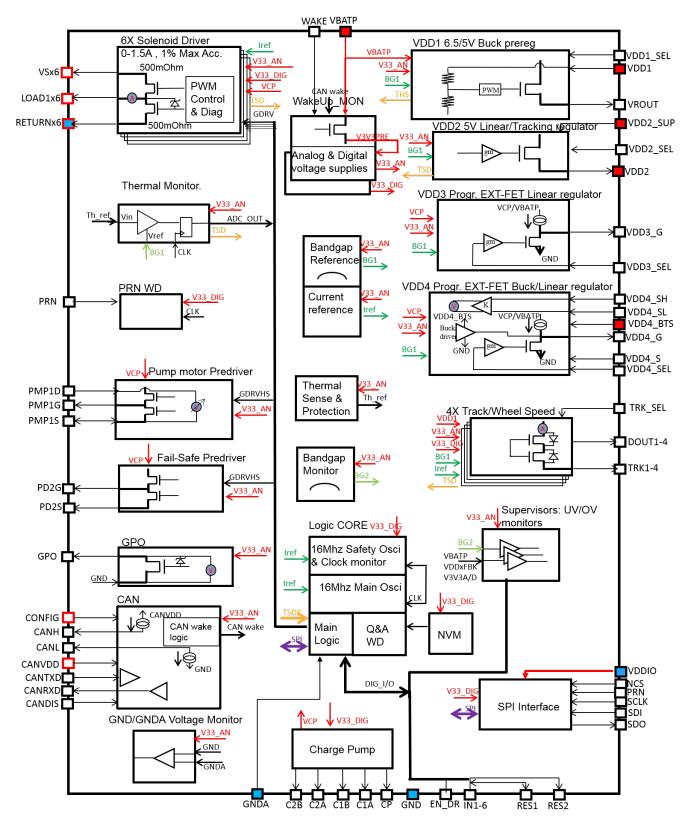

# 3 Pin out

Figure 3. Pin out (exposed pad down top view, exposed pad up bottom view)

GADG0607171524PS

DS12258 - Rev 5 page 5/178

# 4 Absolute maximum ratings

The component must withstand all the following stimuli without any damage or latch-up. Exceeding any of these values or sustaining it for an extended period (defined in the battery voltage range table) may lead to characteristics degradation or component damage. All voltages are related to analog ground pin GND.

Table 1. Absolute maximum ratings (-40 °C  $\leq$  T<sub>j</sub>  $\leq$  175 °C)

| Symbol   | Parameter | Test conditions                                                                                                                             | Min. | Тур. | Max. | Unit | Pin Direction |

|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|---------------|

| VBATP    | Global    |                                                                                                                                             | -0.3 |      | 40   | V    | S             |

| VCP      | Local     | VCP-VBATP < 13 V, VBATP-VCP < 0.3 V                                                                                                         | -0.3 |      | 50   | V    | S             |

| VC1, VC3 | Local     | VCx-VBATP < 0.3 V                                                                                                                           | -0.3 |      | 40   | V    | 0             |

| VC2, VC4 | Local     | VCx-VBATP < 13 V VBATP-VCx < 0.3 V                                                                                                          | -0.3 |      | 50   | V    | 0             |

| VSx      | Global    | In the application condition -1/+40 V; no impact on other functions <sup>(1)</sup>                                                          | -0.3 |      | 40   | V    | S             |

| PD1D     | Global    |                                                                                                                                             | -0.3 |      | 40   | V    | I             |

| PD1G     | Local     | Internally shorted to PD1S (off phase). PD1G-PD1S < 13 V                                                                                    | -2   |      | 50   | ٧    | 0             |

| PD1S     | Global    | PD1S-PD1G < 0.3 V                                                                                                                           | -2   |      | 40   | V    | 0             |

| PD2G     | Local     | Internally shorted to PD2S (off phase). PD2G-PD2S < 13 V                                                                                    | -0.3 |      | 50   | ٧    | 0             |

| PD2S     | Global    | In the application condition: VSx in short condition supplied by PD2S -1/+40 V, no impact on other functions.  (1) PD2S-PD2G < 0.3 V        | -0.3 |      | 40   | V    | 0             |

| GPO      | Global    | In the application condition -1/+40 V; no impact on other functions <sup>(1)</sup>                                                          | -0.3 |      | 40   | V    | 0             |

| LOADx    | Global    | In the application condition -1/+40 V; no impact on other functions <sup>(1)</sup>                                                          | -0.3 |      | 40   | V    | 0             |

| RETURNX  | Local     |                                                                                                                                             | -0.3 |      | 0.3  | V    | I             |

| VDD1     | Local     |                                                                                                                                             | -0.3 |      | 19   | V    | 0             |

| VDD1_SEL | Local     |                                                                                                                                             | -0.3 |      | 40   | V    | I             |

| VROUT    | Local     |                                                                                                                                             | -2   |      | 40   | V    | 0             |

| VDD2_SUP | Global    |                                                                                                                                             | -0.3 |      | 40   | V    | S             |

| VDD2     | Global    |                                                                                                                                             | -2   |      | 40   | V    | 0             |

| VDD2_SEL | Local     |                                                                                                                                             | -0.3 |      | 19   | V    | I             |

| VDD3_G   | Local     |                                                                                                                                             | -0.3 |      | 19   | V    | 0             |

| VDD3_SEL | Local     |                                                                                                                                             | -0.3 |      | 19   | V    | I             |

| VDD4_SH  | Global    |                                                                                                                                             | -0.3 |      | 40   | V    | I             |

| VDD4_SL  | Global    |                                                                                                                                             | -0.3 |      | 40   | V    | I             |

| VDD4_G   | Local     | VDD4G-VDD4S < 13 V, VDD4G-VDD4BTS < 0.3 V                                                                                                   | -0.3 |      | 50   | V    | 0             |

| VDD4_S   | Local     | In the application condition -2/+40 V (Schottky diode activation time < 0.2 $\mu$ s), no impact on other functions. (2) VDD4S-VDD4G < 0.3 V | -0.3 |      | 40   | V    | 0             |

| VDD4_SEL | Local     |                                                                                                                                             | -0.3 |      | 19   | V    | I             |

| VDD4_BTS | Local     | VDD4BTS-VDD4G < 13 V                                                                                                                        | -0.3 |      | 50   | V    | S             |

| TRKn     | Global    |                                                                                                                                             | -2   |      | 40   | V    | 0             |

| TRL_SEL  | Local     |                                                                                                                                             | -0.3 |      | 19   | V    | I             |

DS12258 - Rev 5 page 6/178

| Symbol                                                     | Parameter | Test conditions          | Min. | Тур. | Max. | Unit | Pin Direction |

|------------------------------------------------------------|-----------|--------------------------|------|------|------|------|---------------|

| VDDIO                                                      | Local     |                          | -0.3 |      | 19   | V    | S             |

| WAKE                                                       | Global    | (3)                      | -0.3 |      | 40   | V    | I             |

| CONFIG                                                     | Local     | (3)                      | -0.3 |      | 40   | V    | I             |

| CS, SCLK, SDI, EN_DR,<br>VDD1_SEL, CAN_DIS,<br>PRN, WD_DIS | Local     |                          | -0.3 |      | 19   | V    | I             |

| SDO, DOUTx                                                 | Local     |                          | -0.3 |      | 19   | V    | 0             |

| RES1, RES2                                                 | Local     |                          | -0.3 |      | 5.5  | V    | 0             |

| INx                                                        | Local     |                          | -0.3 |      | 19   | V    | I             |

| CAN_VDD                                                    | Local     |                          | -0.3 |      | 19   | V    | S             |

| CANTXD                                                     | Local     |                          | -0.3 |      | 19   | V    | I             |

| CANRXD                                                     | Local     |                          | -0.3 |      | 19   | V    | 0             |

| CANH, CANL                                                 | Global    | CANH-CANL≤40 V           | -18  |      | 40   | V    | I/O           |

| GND_A                                                      | Local     | Digital ground reference | -0.3 |      | 0.3  | V    | S             |

| GND                                                        | Local     | Ground reference         |      | 0    |      | V    | S             |

<sup>1.</sup> In case ECU pin is shorted to GND and gnd shift is present, the absolute values can be exceeded without damage and without impact on other functions provided that the max reverse current on the involved pin is within the max value specified in the electrical characteristic sections:

- 2. During Schottky diode activation time the absolute value can be exceeded without impact on buck functionality.

- 3. Protected with external 1  $k\Omega$  series resistor during battery transients

# 4.1 Latch-up trials

Latch-up tests performed according to JEDEC 78 class 2 Level A

# 4.2 ESD

**Table 2. ESD requirements**

| Symbol                        | Parameter       | Test condition                                                                                  | Min  | Тур | Max | Unit | Pin    |

|-------------------------------|-----------------|-------------------------------------------------------------------------------------------------|------|-----|-----|------|--------|

| ESD HBM Global                | HBM global pins | ESD according to the Human Body Model (HBM), Q100-002 for global pins; (100 pF/1.5 k $\Omega$ ) | -4   |     | 4   | kV   | Global |

| ESD HBM                       | HBM local pins  | SD according to the Human Body Model (HBM), Q100-002 for all ns; (100 pF/1.5 kΩ)                |      |     | 2   | kV   | ALL    |

| ESD CDM Corner <sup>(1)</sup> | CDM corner pins | ESD according to the Charged Device Model (CDM), Q100-011 Corner pins                           | -750 |     | 750 | V    | Corner |

| ESD CDM                       | CDM all pins    | ESD according to the Charged Device Model (CDM), Q100-011 All pins                              | -500 |     | 500 | ٧    | ALL    |

1. VDD4\_SH, WAKE: -650V, slug-up version only.

DS12258 - Rev 5 page 7/178

# 5 Temperature ranges and thermal data

All parameters are guaranteed, and tested, in the temperature range  $T_j$ -40÷150 °C (unless otherwise specified); the device is still operative and functional at higher temperatures (up to  $T_i$  175 °C).

Device functionality at high temperature is guaranteed by bench validation, electrical parameters are guaranteed by correlation with ATE tests at reduced temperature and adjusted limits (if needed).

Table 3. Temperature ranges and thermal data

| Symbol                            | Parameter                              | Test condition | Min | Тур  | Max | Unit | Pin |

|-----------------------------------|----------------------------------------|----------------|-----|------|-----|------|-----|

| T <sub>a</sub>                    | Operating Temperature                  |                | -40 |      | 135 | °C   | ALL |

| Tj                                | Junction Temperature                   |                | -40 |      | 175 | °C   | ALL |

| T <sub>str</sub>                  | Storage Temperature                    |                | -50 |      | 175 | °C   | ALL |

| R <sub>THj-c</sub> <sup>(1)</sup> | Thermal Resistance junction to case    |                |     | 0.66 | 0.9 | °C/W | ALL |

| R <sub>THj-a</sub> <sup>(1)</sup> | Thermal Resistance junction to ambient |                | 8.5 |      |     | °C/W | ALL |

<sup>1.</sup> With 2s2p PCB thermally enhanced, cold plate as per std Jedec best practice guidelines (JESD51), assuming  $P_{diss} = 5$  W dissipated statically and homogeneously.

DS12258 - Rev 5 page 8/178

# 6 Battery voltage range

Table 4. Battery voltage range

| Symbol          | Parameter                                     | Test condition          | Min  | Тур | Max  | Unit | Pin   |

|-----------------|-----------------------------------------------|-------------------------|------|-----|------|------|-------|

|                 |                                               | T <sub>a</sub> = -40 °C | 5.5  |     | 19   | V    |       |

| VBATP operative | Normal Operative Voltage Range <sup>(1)</sup> | T <sub>a</sub> = 27 °C  | 5.55 |     | 19   | V    | VBATP |

|                 |                                               | T <sub>a</sub> = 135 °C | 5.6  |     | 19   | V    |       |

| VBATP double    | Full Operating Voltage Range <sup>(2)</sup>   | T <sub>a</sub> ≤ 50 °C  | 19   |     | 27   | V    | VBATP |

| VBATP high      | High Voltage Range <sup>(3)</sup>             | T <sub>a</sub> ≤ 50 °C  | 27   |     | 40   | V    | VBATP |

|                 |                                               | T <sub>a</sub> = -40 °C | -0.3 |     | 5.5  | V    |       |

| VBATP low       | Low Voltage Range <sup>(4)</sup>              | T <sub>a</sub> = 27 °C  | -0.3 |     | 5.55 | V    | VBATP |

|                 |                                               | T <sub>a</sub> = 135 °C | -0,3 |     | 5.6  | V    |       |

- The device shall be capable of full functional operation; min value of VBATP pin is considering the drop voltage of its reverse protection diode.

- 2. The device shall be capable of full functional operation at T<sub>a</sub> ≤ 50 °C There shall be no damage to flexible, no false operation and input pins shall withstand voltage and current defined in Absolute ratings regardless of battery voltage range. Also, linear regulators output shall not exceed the Transient Load Response defined in the related section and output voltage of other output signals (i.e., CPU control signal, CAN-RXD, etc) shall not exceed the voltage at normal operation. Full functional operation shall resume without any operator intervention when battery voltage returns to Normal Operating Voltage Range at T<sub>a</sub> ≤ 50 °C

- 3. There shall be no damage to the device, Solenoid channels will be disabled, together with Fail Safe and Pump pre-drivers, to limit power dissipation; input pins shall withstand voltage and current defined in Absolute ratings regardless of battery voltage range. Regulator outputs shall not exceed the Transient Load Response defined in related section and output voltage of other output signals (i.e., CPU control signal, CAN-RXD, etc.) shall not exceed the voltage at normal operation. Switching regulators may violate Transient Load Response accuracy depending on target regulated voltage, however no reset should be triggered. Full functional operation shall resume without any operator intervention when battery voltage returns to Normal Operating Voltage Range.

- Depending on VBATP input level the device may be in reset condition or operating mode with degraded parameters. Details

of VBATP voltage range are described in Functional table, degraded parameters are specified in Electrical Characteristic

tables.

DS12258 - Rev 5 page 9/178

# 7 Power up and power down

# 7.1 Device configuration

The device can be configured to work in two different modes through a dedicated pin CONFIG.

As the protected battery is available and internal logic is out of reset (POR released), the device senses the connection on the CONFIG pin: in case the pin is grounded the device is configured to work with reduced stby current consumption (no CAN activity during stby) and with a subset of functions disabled in ON state. An external 1 k $\Omega$  resistor is highly recommended to implement the connection to limit the risk of parasitic effects in case of ground shifts in the board. Once configured in reduced current consumption mode, the following features are kept disabled:

- CAN WAKE-UP

- Q&A WATCHDOG

The status of CONFIG pin is latched at power-up and available as echo on bit15 (Asic Configuration) of TRKFAULT SPI register; the latched configuration can be reset only by a switch-off of the device: in case CONFIG pin connection is lost during the device activity the status of the device will not change until a new power-up sequence. To avoid additional current consumption from protected battery line when the device is configured in fully functional mode no internal pull-up/down structure is implemented on the pin itself; to latch properly the high configuration on CONFIG pin, CONFIG has to be connected to a power supply available before the ASIC POR release (example: battery line).

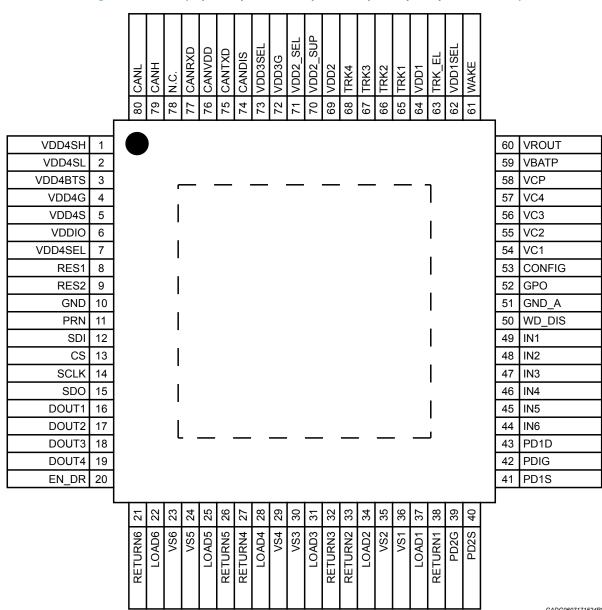

# 7.2 Power up

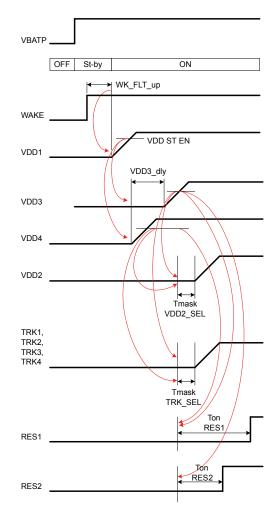

As the protected battery is available the device moves to a stand-by state (STBY): at that point a wake up signal on the WAKE pin is required to turn on the device and to start the regulators power up sequence as in the figure below.

The device first enables internal charge pump and VDD1 pre-regulator, the following regulator's enable signals are delayed until VDD1 reaches the VDD1\_ST\_en threshold to guarantee they have enough supply voltage to perform slope control and minimize overshoot; this delay is applied independently of the chosen supply for configurable regulators. Regulators enabling are delayed to distribute total in-rush current from supply lines: first regulator enabled after VDD1 is VDD4, followed by VDD3 and finally from VDD2 and TRKn outputs. The latest regulators wait for VDD3 and VDD4 to be out from under voltage conditions to ensure proper configuration latch in case either VDD3 or VDD4 is used as tracking reference.

DS12258 - Rev 5 page 10/178

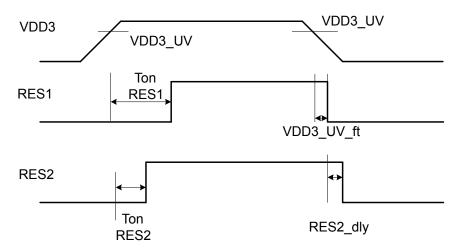

Figure 4. Internal supply power-up timings

GADG0707170939PS

DS12258 - Rev 5 page 11/178

Figure 5. Wake up through WAKE pin

GADG0707170959PS

# 7.3 Keep on

The device provides three different possibilities to stay ON.

- 1. A persistent high signal on WAKE pin

- 2. The setting of the power hold bit through SPI

- 3. The refreshing of the keep alive SPI bit within a certain time frame.

At each high to low transition on the WAKE pin the device enters the keep-alive mode for one keep-alive period (KA\_period).

If the device receives an SPI command to set the power hold bit within the first keep-alive period, the device remains awake.

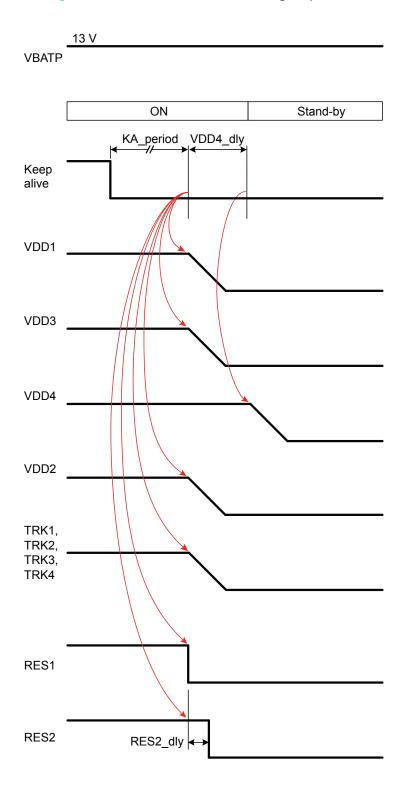

If the device receives an SPI command to refresh the keep-alive bit within the first keep-alive period the device remains awake. Once the keep-alive bit is refreshed a new KA\_period starts and so forth. To stay on the keep-alive bit should be refreshed at each KA\_period; after each refresh of the keep alive counter, the keep alive bit is automatically reset.

Otherwise after the KA\_period the device exits the keep-alive mode and enters in power down, unless the WAKE pin remains high.

At each power up by CAN the device enters the keep-alive mode for one keep-alive period (KA\_period).

If the device receives an SPI command to set the power hold bit within the first keep-alive period the device remains awake.

DS12258 - Rev 5 page 12/178

If the device receives an SPI command to refresh the keep-alive bit within the first keep-alive period the device remains awake. Once the keep-alive bit is refreshed a new KA\_period starts and so forth. To stay on the keep-alive bit should be refreshed at each KA\_period.

# 7.4 Power down

The power down, depending on the keep on condition that is maintaining on the device, can happen in three different ways.

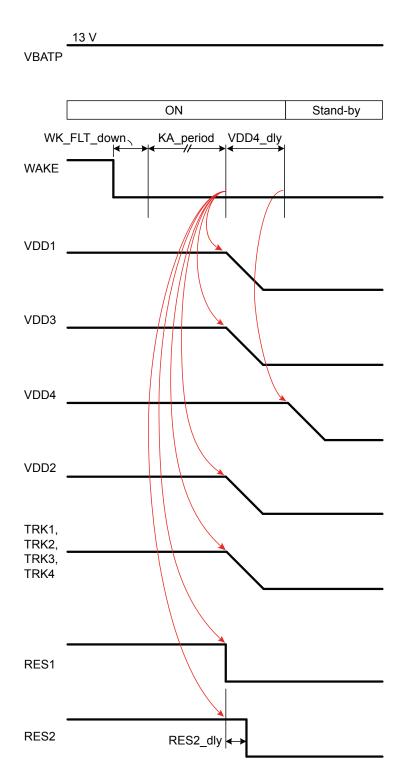

In Figure 6 the power down related to a high low transition on the WAKE pin.

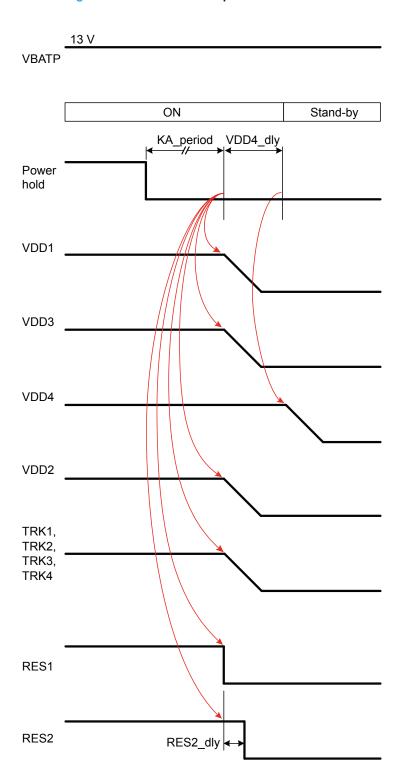

In Figure 7 the power down related to the removal of power hold bit.

In Figure 8 the power down related to the not refreshing keep-alive bit from the microcontroller.

During power down all the regulators are switched off at the same time except VDD4 that is delayed by a fixed timing, provided that ASIC battery is kept supplied. No voltage control is performed during power down; in case the relative voltage between regulators is needed it has to be guaranteed through external components.

DS12258 - Rev 5 page 13/178

Figure 6. Power down from WAKE pin

GADG0707171050PS

DS12258 - Rev 5 page 14/178

Figure 7. Power down from power hold condition

GADG0707171105PS

DS12258 - Rev 5 page 15/178

Figure 8. Power down from not refreshing keep-alive bit

GADG0707171110PS

DS12258 - Rev 5 page 16/178

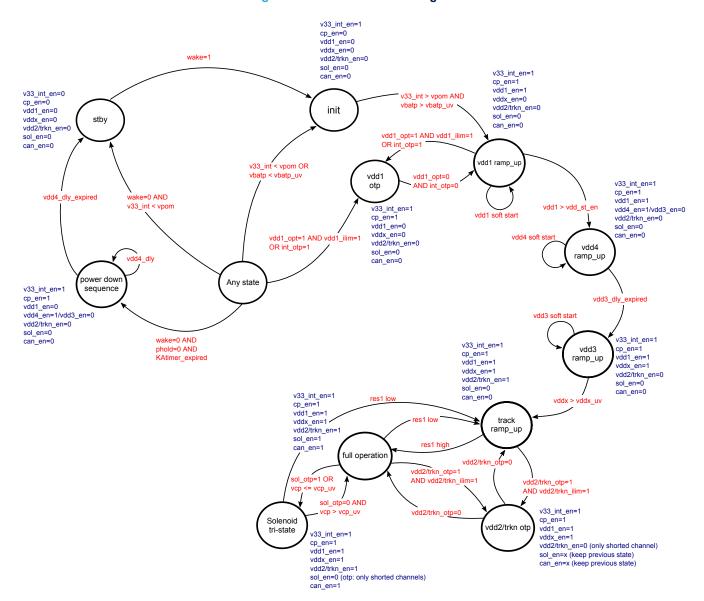

# 7.5 Functional state block diagram

Figure 9. Device state block diagram

DS12258 - Rev 5 page 17/178

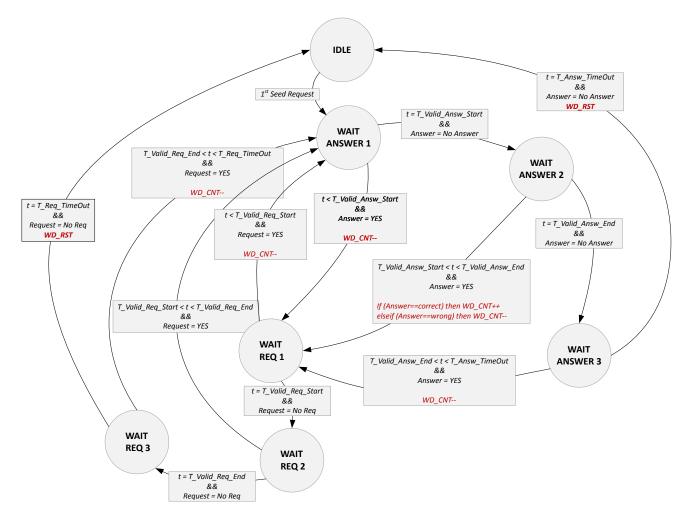

# 7.6 Power up/down electrical characteristics

$5.5V \le VBATP \le 19V$ ;  $-40^{\circ}C \le Tj \le 175^{\circ}C$  unless otherwise noticed. All voltages referred to GND pin.

Table 5. Power up/down electrical characteristics

| Symbol              | Parameter                                               | Test condition                                                                                | Min  | Тур | Max  | Unit | Pin      |

|---------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|-----|------|------|----------|

| Current Consumption | on                                                      |                                                                                               |      |     |      |      |          |

| VBATP_stby_cur      | VBATP stby current consumption                          | WAKE=0V, VBATP, PD1D,<br>VDD4_SH, VDD4_SL, VDD2_SUP,<br>VSx=13V CONFIG=0V Tambient<br><= 70°C | 5    |     | 45   | μА   | VBATP    |

| VBATP_stby_cur      | VBATP stby current consumption                          | WAKE=0V, VBATP, PD1D,<br>VDD4_SH, VDD4_SL, VDD2_SUP,<br>VSx=13V, CONFIG=13V                   | 20   |     | 90   | μΑ   | VBATP    |

| VBATP_cur           | VBATP ON current cunsumption                            | VBATP = 13V, WAKE=HIGH                                                                        | 20   | 30  | 75   | mA   | VBATP    |

| Wake Up             |                                                         |                                                                                               |      |     |      |      |          |

| WAKE_high_th        | WAKE high threshold                                     |                                                                                               | 2.7  |     | 3.5  | V    | WAKE     |

| WAKE_low_th         | WAKE low threshold                                      |                                                                                               | 2    |     | 2.7  | V    | WAKE     |

| WAKE_hys            | WAKE hysteresis                                         |                                                                                               | 0.5  |     |      | ٧    | WAKE     |

| WAKE_pd             | WAKE pull down                                          | WAKE < WAKE_high_th                                                                           | 0.4  |     | 2    | ΜΩ   | WAKE     |

| CONFIG_low          | Low current mode                                        |                                                                                               |      |     | 0.75 | V    | CONFIG   |

| CONFIG_high         | Full functionality mode                                 |                                                                                               | 1.75 |     |      | V    | CONFIG   |

| VDD_st_en           | Supply start enable                                     |                                                                                               | 4.3  | 4.5 | 4.7  | V    | VDD1     |

| VDD_st_en_deglitch  | Digital filter time                                     | Guaranteed by scan                                                                            | 7.5  | 10  | 12.5 | μs   | VDD1     |

| Tmask_VDD2_SEL      | Masking of VDD2 enable signal (after VDD3/4_uv release) | Guaranteed by scan                                                                            | 150  | 200 | 250  | μs   | VDD2_SEL |

| Tdelay_VDD2         | Analog delay on soft start ramp                         |                                                                                               | 100  |     | 700  | μs   | VDD2     |

| Tmask_TRK_SEL       | Masking of TRKn enable signal (after VDD3/4_uv release) | Guaranteed by scan                                                                            | 150  | 200 | 250  | μs   | TRK_SEL  |

| Tdelay_TRKn         | Analog delay on soft start ramp                         |                                                                                               | 100  |     | 700  | μs   | TRKn     |

| WK_FLT_up           | Wake up deglitch                                        | Guaranteed by scan                                                                            | 7.5  | 10  | 12.5 | μs   | WAKE     |

| WK_FLT_down         | Wake up deglitch                                        | Guaranteed by scan                                                                            | 7.5  | 10  | 12.5 | μs   | WAKE     |

| WAKE_tmin           | Wake high minimum time to power-on internal logic       | Design info, guaranteed by design                                                             | 150  |     |      | μs   | WAKE     |

| Keep On             |                                                         |                                                                                               |      |     |      |      |          |

| KA_period           | Keep-alive period                                       | Guaranteed by scan                                                                            | 180  | 200 | 220  | ms   | WAKE     |

| VDD3_dly            | Delay VDD3 from VDD4 at power up                        | Guaranteed by scan                                                                            | 8.0  | 1   | 1.2  | ms   | VDD3/4   |

| Power Down          |                                                         |                                                                                               |      |     |      |      |          |

| VDD4_dly            | Delay VDD4 from VDD3 at power down                      | Guaranteed by scan                                                                            | 23   |     | 35   | μs   | VDD3/4   |

DS12258 - Rev 5 page 18/178

# 8 Power supply

#### 8.1 VDD1

# 8.1.1 VDD1 functional description

VDD1 is a configurable buck regulator with internal high–side MOS and external recirculation diode. The regulator, depending on the status of the VDD1\_SEL pin, can provide two different output voltages: if the pin is floating, VDD1 selected output voltage is 6.5 V, while if it is connected to GND, the output selected voltage is 5 V.

On VDD1\_SEL an internal 500  $k\Omega$  pull up resistor is present and the pin is latched at power-up, after internal POR release, to avoid unwanted changes in VDD1 output voltage during operation. The echo of latched value is available in the SPI registers.

The switching frequency of the buck PWM is around 470 kHz.

The VDD1 regulator has an inductor's peak current limitation circuitry, as a protection in case of output short to GND. When the output stage sensed current is higher than current limitation value, the output, after min duty cycle has expired, is switched off until next PWM rising edge; should the overcurrent condition still be present, the regulator is forced to work at minimum duty cycle causing a drop in the output voltage.

The status of the current limitation circuit is internally monitored to detect when the regulator is not able to provide the target output voltage: in case the circuit is triggered, VDD1 OVER CURRENT flag is set in the SPI registers.

The fault condition may be triggered at low battery as well, even if load current is within the specified range (in this case, the VDD1 OVER CURRENT bit shall be intended as a generic Out of Regulation diagnostic). Under this condition, the regulator shall operate at 100% duty cycle to minimize dropout.

The diagnostic is not masked during power-up phase.

VDD1 has an internal thermal protection with a dedicated thermal sensor: in case temperature shutdown threshold is reached and OVER CURRENT flag is set, all the regulators are turned off and a dedicated diagnostic bit is set (T\_SD\_VDD1). Once the sensed temperature decreases below the shutdown threshold (plus a thermal hysteresis), the powerup sequence is restarted and fault bit can be cleared by SPI reading.

VBATP

VCP

Driver

X

VROUT

X

VDD 1

SEL

VDD1

Buck

Figure 10. VDD1 regulator circuit

DS12258 - Rev 5 page 19/178

# 8.1.2 VDD1 electrical characteristics

5.5 V  $\leq$  VBATP  $\leq$  19 V; -40 °C  $\leq$  T $_{j}$   $\leq$  175 °C, unless otherwise noticed. All voltages refer to GND pin.

Table 6. VDD1 electrical characteristics

| Symbol                  | Parameter                                 | Test condition                                                                                                                                                                              | Min   | Тур | Max   | Unit | Pin      |

|-------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|----------|

| I <sub>VDD1</sub>       | Output load current                       | Application note                                                                                                                                                                            | 0.01  |     | 1.3   | Α    | VDD1     |

| C <sub>VDD1</sub>       | Output capacitor                          | Application note Temperature and component drift included                                                                                                                                   | -35%  | 22  | +35%  | μF   | VDD1     |

| C <sub>VDD1</sub> ESR   | Output capacitor ESR                      | Application note f ≤ 150 kHz                                                                                                                                                                |       |     | 150   | mΩ   | VDD1     |

| L <sub>VROUT</sub>      | Buck inductor                             | Application note Component & temperature drift included                                                                                                                                     | -20%  | 22  | +20%  | μН   | VROUT    |

| L <sub>VROUT</sub>      | Inductor res                              | Application note                                                                                                                                                                            |       |     | 105   | mΩ   | VROUT    |

| Configuration Inpu      | ut                                        |                                                                                                                                                                                             |       |     |       |      |          |

| V <sub>IL</sub>         | Logic Input Low Voltage                   |                                                                                                                                                                                             | -     |     | 0.75  | V    | VDD1_SEL |

| V <sub>IH</sub>         | Logic Input High Voltage                  |                                                                                                                                                                                             | 1.75  |     |       | V    | VDD1_SEL |

| V <sub>hysteresis</sub> | Input hysteresis Voltage                  |                                                                                                                                                                                             | 0.1   |     | 1     | V    | VDD1_SEL |

| VDD1_SELPU              | VDD1_SEL pull-up to internal logic supply | VDD1_SEL = 0 V                                                                                                                                                                              | 10    | 30  | 60    | μА   | VDD1_SEL |

| VDD1                    |                                           |                                                                                                                                                                                             |       |     |       |      |          |

| VDD1_Vout1              | Regulated output voltage                  | VDD1_SEL = low VBATP $\geq$ 6 V, 10 mA $\leq$ $I_{VDD1} \leq$ 1.3 A                                                                                                                         | 4.85  | 5   | 5.15  | V    | VDD1     |

| VDD1_Vout2              | Regulated output voltage                  | VDD1_SEL = high VBATP ≥ 7.5 V, 10 mA $\leq$ I <sub>VDD1</sub> $\leq$ 1.3 A                                                                                                                  | 6.305 | 6.5 | 6.695 | V    | VDD1     |

| VDD1_line               | Line regulation                           | VBATP 7.5 V to 19 V, I <sub>VDD1</sub> = 10 mA,<br>1.3 A                                                                                                                                    | -10   |     | +10   | mV   | VDD1     |

| VDD1_load               | Load regulation                           | $I_{VDD1}$ = 10 mA to 1.3 A, VBATP 7.5 V to 19 V                                                                                                                                            | -10   |     | +10   | mV   | VDD1     |

| VDD1_Vout1_tr 1         | Transient output voltage 1                | VDD1_SEL = low, VBATP = 13 V, $I_{VDD1}$ = 10 mA to 1.3 A dI/dt = 500 mA/µs, $C_{VDD1}$ = 22 µF, LVROUT = 22 µH, Guaranteed by design                                                       | -8    |     | +8    | %    | VDD1     |

| VDD1_Vout2_tr 1         | Transient output voltage 1                | VDD1_SEL = high, VBATP = 13 V, $I_{VDD1}$ = 10 mA to 1.3 A dI/dt = 500 mA/ $\mu$ s, $C_{VDD1}$ = 22 $\mu$ F, LVROUT = 22 $\mu$ H, Guaranteed by design                                      | -8    |     | +8    | %    | VDD1     |

| VDD1_Vout1_tr 2         | Transient output voltage 2                | VDD1_SEL = low, VBATP step 12 V to 18 V; 18 V to 12 V, dVBATP/dt = 3 V/ $\mu$ s, I <sub>VDD1</sub> = 10 mA,1.3 A, C <sub>VDD1</sub> = 22 $\mu$ F, LVROUT = 22 $\mu$ H, Guaranteed by design | -8    |     | +8    | %    | VDD1     |

| VDD1_Vout2_tr 2         | Transient output voltage 2                | VDD1_SEL = high, VBATP step 12 V to 18 V; 18 V to 12 V, dVBATP/dt = 3 V/us, $I_{VDD1}$ = 10 mA, 1.3 A, $C_{VDD1}$ = 22 $\mu$ F, LVROUT = 22 $\mu$ H, Guaranteed by design                   | -8    |     | +8    | %    | VDD1     |

| VDD1_ripple             | Ripple voltage                            | VBATP = 13 V, I <sub>VDD1</sub> = 1.3 A Guaranteed by design                                                                                                                                | -20   |     | +20   | mV   | VDD1     |

| VDD1_slope              | Slope control                             | VBATP = 13 V                                                                                                                                                                                | 5     |     | 25    | V/ms | VDD1     |

| VDD1_ovs_1              | Overshoot at power on Vout1               |                                                                                                                                                                                             |       |     | 5.2   | V    | VDD1     |

| VDD1_ovs_2              | Overshoot at power on Vout2               |                                                                                                                                                                                             |       |     | 6.7   | V    | VDD1     |

DS12258 - Rev 5 page 20/178

| Symbol          | Parameter                                  | Test condition                                                                                                                           | Min | Тур                     | Max  | Unit | Pin   |

|-----------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------|------|------|-------|

| VDD1_ovs_1 a    | Overshoot VBATP step on Vout1              | VBATP step from 5.5 V to 13 V during 10 μS, considering 1 μH wiring harness, Guaranteed by design                                        |     |                         | 5.5  | V    | VDD1  |

| VDD1_ovs_2 a    | Overshoot VBATP step on Vout2              | VBATP step from 5.5 V to 13 V during 10 μS, considering 1 μH wiring harness, Guaranteed by design                                        |     |                         | 7.5  | V    | VDD1  |

| PSRR            | PSRR                                       | VBATP = 13 V, $I_{VDD1}$ = 1.3 A, Vnoise = 1 Vpp, fnoise = 100-200 Hz, $C_{VDD1}$ = 22 $\mu$ F, LVROUT = 22 $\mu$ H Guaranteed by design | 50  |                         |      | dB   | VDD1  |

| VROUT_ovc       | Ipeak limitation                           | Open loop, current ramp on VROUT                                                                                                         | 2.5 |                         | 3.5  | Α    | VROUT |

| VROUT_min_duty  | VDD1 output stage minimum on time duration | Design info, Guaranteed by design                                                                                                        | 100 |                         | 300  | ns   | VROUT |

| Sw_fr           | Switching frequency                        |                                                                                                                                          |     | f <sub>OSCINT</sub> /34 |      | kHz  | VROUT |

| Buck_Rds_ON     | High-side Rds_ON                           | Tj=150 °C                                                                                                                                |     |                         | 0.35 | Ω    | VROUT |

| Buck_Rds_ON     | High-side Rds_ON                           | Tj=175 °C, Guaranteed by design                                                                                                          |     |                         | 0.4  | Ω    | VROUT |

| Buck_ton        | High-side ton                              | Guaranteed by design                                                                                                                     | 5   |                         | 40   | ns   | VROUT |

| Buck_toff       | High-side toff                             | Guaranteed by design                                                                                                                     | 5   |                         | 40   | ns   | VROUT |

| VDD1 Diagnostic |                                            |                                                                                                                                          |     |                         |      |      |       |

| T_SD_VDD1       | Temperature shut down                      |                                                                                                                                          | 175 |                         | 185  | °C   | VROUT |

| T_SD_hy         | Temperature shut down hysteresis           |                                                                                                                                          | 5   |                         | 10   | °C   | VROUT |

| T_SD_deglitch   | Digital deglitch filter time               | Guaranteed by scan                                                                                                                       | 7.5 | 10                      | 12.5 | μs   | VROUT |

#### 8.1.3 **VDD1 error handling**

Table 7. VDD1 type of errors

| Type of error           | Detection condition | Action                                                                                                                                                                                                                                                          | Clear<br>SPI flag | Restart condition                                                                 |

|-------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------|

| VDD1 overcurrent        | ON state            | VDD1 OVER CURRENT SPI fault bit (4) latched in SERVFLT register                                                                                                                                                                                                 | On read           | N.A.                                                                              |

| VDD1<br>overtemperature | ON state            | If current limitation is not triggered: no action  If current limitation is triggered: all outputs except Charge Pump, CAN and GPO disabled, all regulators disabled, power up sequence interrupted and T_SD_VDD1 SPI fault bit (5) latched in SERVFLT register | On read           | Automatic restart with re-trigger of power-up sequence after OT fault disappears. |

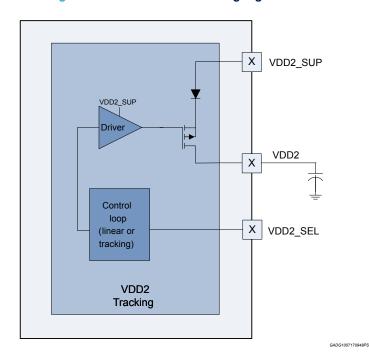

#### 8.2 VDD2

#### 8.2.1 VDD2 functional description

VDD2 is an internal regulator that is configurable through VDD2\_SEL pin. If 3.3 V ≤ VDD2\_SEL ≤ 5 V, the regulator tracks VDD2 SEL while if VDD2 SEL = 0 V VDD2 works as linear 5 V regulator. VDD SUP is the supply voltage of VDD2 regulator that can be connected externally to VBATP or, to limit the power dissipation, to VDD1.

Since VDD2 could be used to track either VDD3 or VDD4 voltages, VDD2 enable and configuration pin is sensed and latched at power up only after VDD3 and VDD4 voltages are above their own undervoltage thresholds: this is intended to avoid wrong configuration latch during the VDD3 and VDD4 rising phase. Echo of the latched VDD2 configuration is available in the SPI registers.

DS12258 - Rev 5 page 21/178

VDD2 output is short to battery protected to avoid reverse current into VDD2\_SUP pin: in case the protection is triggered a diagnostic bit is set in the dedicated SPI register.

An out of regulation comparator is implemented: this comparator senses when the internal current limitation circuitry is activated to regulate properly the output voltage due to either a low drop condition or an overcurrent condition. Once out of regulation condition is detected a flag is set in SPI registers and latched until read. The diagnostic is not masked during power-up phase.

VDD2 has a thermal protection with thermal sensors shared with TRKn regulators. In case the temperature shutdown threshold is reached, and the regulator detects an out of regulation fault, it will be turned off and its dedicated diagnostic bit will be set. Once the sensed temperature is decreased below the shutdown threshold plus a thermal hysteresis, the regulator is automatically turned on with soft start function. T\_SD\_TRK is the bit that latches the thermal shutdown and it is cleared on SPI read.

A dedicated disable SPI bit VDD2\_DIS (default condition = 0) is present and it can be used to switch off the VDD2 regulator and avoid thermal on/off oscillations in case the short on output pin cannot be removed.

Figure 11. VDD2 linear or tracking regulator

# 8.2.2 VDD2 electrical characteristics

$5.5~V \le VBATP \le 19~V$ ;  $5.5~V \le VDD2\_SUP \le 19~V$ ;  $-40~^{\circ}C \le T_{j} \le 175~^{\circ}C$  unless otherwise noticed. All voltages refer to GND pin. If VDD2\_SUP < 6 V the regulator may enter in Rds ON mode where tracking error and line/load regulation accuracy depend on regulator dropout.

| Symbol                 | Parameter                    | Test condition                                          | Min  | Тур | Max  | Unit | Pin      |

|------------------------|------------------------------|---------------------------------------------------------|------|-----|------|------|----------|

| I <sub>VDD2</sub>      | Output load current          | Application note                                        | 10   |     | 200  | mA   | VDD2     |

| C <sub>VDD2</sub>      | Output capacitor             | Application note Component & temperature drift included | -25% | 2.2 | +25% | μF   | VDD2     |

| C <sub>VDD2</sub> ESR  | Output capacitor maximum ESR | Application note f ≤ 150 kHz                            | 0.01 |     | 1    | Ω    | VDD2     |

| C <sub>VDD2</sub> EXT  | External sensor capacitor    | Application note                                        |      |     | 150  | μF   | VDD2     |

| VDD2_SUP_<br>Ileak_dis | VDD2_SUP<br>leakage current  | VDD2_SUP = 13 V, WAKE = 0 V                             | -1   |     | 1    | μA   | VDD2_SUP |

Table 8. VDD2 electrical characteristics

DS12258 - Rev 5 page 22/178

| Symbol          | Parameter                        | Test condition                                                                                                                                           | Min                | Тур      | Max                | Unit | Pin      |

|-----------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|--------------------|------|----------|

| Configuration I | nput                             |                                                                                                                                                          |                    |          |                    |      |          |

| VIL             | Logic Input Low<br>Voltage       |                                                                                                                                                          | -                  |          | 0.75               | ٧    | VDD2_SEL |

| VIH             | Logic Input High<br>Voltage      |                                                                                                                                                          | 1.75               |          | -                  | V    | VDD2_SEL |

| Vhysteresis     | Input hysteresis<br>Voltage      |                                                                                                                                                          | 0.1                |          | 1                  | V    | VDD2_SEL |

| VDD2_SELPD      | VDD2_SEL pull down               | VDD2_SEL = 5 V                                                                                                                                           | 10                 | 50       | 130                | μA   | VDD2_SEL |

| Tracking config | juration 3.3 V ≤ VDD2            | 2_SEL ≤ 5 V                                                                                                                                              |                    |          |                    |      |          |

| VDD2_Vout       | Regulated output voltage         | VDD2_SUP ≥ 6 V, 10 mA ≤ I <sub>VDD2</sub> ≤ 200 mA                                                                                                       | VDD2_SEL<br>-20 mV | VDD2_SEL | VDD2_SEL<br>+20 mV | V    | VDD2     |

| VDD2_error      | Matching error                   | VDD2_SEL - VDD2, VDD2_SUP $\geq$ 6 V,<br>10 mA $\leq$ I <sub>VDD2</sub> $\leq$ 200 mA                                                                    | -20 m              |          | +20 m              | V    | VDD2     |

| VDD2_line       | Line regulation                  | VDD2_SUP 6 V to 19 V, I <sub>VDD2</sub> = 10 mA, 200 mA                                                                                                  | -10                |          | +10                | mV   | VDD2     |

| VDD2_load       | Load regulation                  | I <sub>VDD2</sub> = 10 mA to 200 mA, VDD2_SUP<br>6 V to 19 V                                                                                             | -10                |          | +10                | mV   | VDD2     |

| VDD2_Vout_tr1   | Transient output voltage 1       | VBATP = 13 V, $I_{VDD2}$ = 10 mA to 200 mA dl/dt = 200 mA/ $\mu$ s, $C_{VDD2}$ = 2.2 $\mu$ F, Guaranteed by design                                       | -5                 |          | +5                 | %    | VDD2     |

| VDD2_Vout_tr2   | Transient output voltage 2       | VDD2_SUP step 12 V to 18 V; 18 V to 12 V dVDD2_SUP/dt = 3 V/ $\mu$ s, $I_{VDD2}$ = 10 mA, 200 mA, $C_{VDD2}$ = 2.2 $\mu$ F, Guaranteed by design         | -5                 |          | +5                 | %    | VDD2     |

| VDD2_RdsON      | RdsON                            | Tj =150 °C, VDD2_SUP = VDD2_SEL, $I_{VDD2}$ = 200 mA                                                                                                     |                    |          | 3.6                | Ω    | VDD2     |

| VDD2_RdsON      | RdsON                            | Tj = 175 °C, VDD2_SUP = VDD2_SEL, $I_{VDD2}$ = 200 mA, Guaranteed by design                                                                              |                    |          | 4                  | Ω    | VDD2     |

| VDD2_PSSR       | PSSR                             | VDD2_SUP = 6.5 V, $I_{VDD2}$ = 200 mA,<br>Vnoise = 1 Vpp, fnoise = 465 kHz, $C_{VDD2}$ = 2.2 $\mu$ F Guaranteed by design                                | 20                 |          |                    | dB   | VDD2     |

| VDD2_cur lim    | Current limitation               | VDD2 = -2 V                                                                                                                                              | 250                |          | 390                | mA   | VDD2     |

| VDD2_rev cur    | Reverse current in off condition | VDD2 = VDD2_SUP + 2 V, VDD2 disabled                                                                                                                     | 0.2                |          | 2                  | mA   | VDD2     |

| VDD2_rev cur    | Reverse current in on condition  | VDD2 = VDD2_SUP + 2 V, VDD2<br>enabled                                                                                                                   | 0.2                |          | 2                  | mA   | VDD2     |

| VDD2_ovs_a      | Overshoot at power on            | $I_{VDD2}$ = 10 mA, $C_{VDD2}$ = 2.2 $\mu$ F                                                                                                             |                    |          | 5.5                | V    | VDD2     |

| VDD2_ovs_b      | Overshoot at<br>VBATP step       | VBATP step from 5.5 to 13 V during 10 $\mu$ S, considering 1 $\mu$ H wiring harness, $I_{VDD2}$ = 200 mA, $C_{VDD2}$ = 2.2 $\mu$ F, Guaranteed by design |                    |          | 5.7                | V    | VDD2     |

| VDD2_off        | Off state voltage                |                                                                                                                                                          |                    |          | 1                  | V    | VDD2     |

| VDD2_soft       | Slope control                    | VDD2_SUP=VBATP = 13 V $I_{VDD2}$ = 10 mA, $C_{VDD2}$ = 2.2 $\mu$ F                                                                                       | 5                  |          | 30                 | V/ms | VDD2     |

| Linear configur | ation VDD2_SEL=0 \               | 1                                                                                                                                                        |                    |          |                    |      |          |

| VDD2_Vout       | Regulated output voltage         | VDD2_SUP ≥ 6 V, 10 mA ≤ I <sub>VDD2</sub> ≤ 200 mA                                                                                                       | 4.9                | 5        | 5.1                | V    | VDD2     |

DS12258 - Rev 5 page 23/178

| Symbol               | Parameter                         | Test condition                                                                                                                                      | Min      | Тур | Max              | Unit | Pin  |

|----------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|------------------|------|------|

| VDD2_line            | Line regulation                   | VDD2_SUP 6 V to 19 V, I <sub>VDD2</sub> = 10 mA, 200 mA                                                                                             | -10      |     | +10              | mV   | VDD2 |

| VDD2_load            | Load regulation                   | $I_{VDD2}$ = 10 mA to 200 mA, VBATP 6 V to 19 V                                                                                                     | -10      |     | +10              | mV   | VDD2 |

| VDD2_Vout_tr1        | Transient output voltage 1        | VDD2_SUP = 13 V, $I_{VDD2}$ = 10 mA to 200 mA dI/dt = 200 mA/µs, $C_{VDD2}$ = 2.2 µF, Guaranteed by design                                          | -5       |     | +5               | %    | VDD2 |

| VDD2_Vout_tr2        | Transient output voltage 2        | VDD2_SUP step 12 V to 18 V; 18 V to 12 V, dVDD2_SUP/dt = 3 V/ $\mu$ s, l $_{VDD2}$ = 10 mA, 200 mA, C $_{VDD2}$ = 2.2 $\mu$ F, Guaranteed by design | -5       |     | +5               | %    | VDD2 |

| VDD2_RdsON           | RdsON                             | $Tj$ = 150 °C, VDD2_SUP = VDD2_SEL, $I_{VDD2}$ = 200 mA                                                                                             |          |     | 3.6              | Ω    | VDD2 |

| VDD2_RdsON           | RdsON                             | Tj = 175 °C, VDD2_SUP = VDD2_SEL,<br>I <sub>VDD2</sub> = 200 mA, Guaranteed by design                                                               |          |     | 4                | Ω    | VDD2 |

| VDD2_PSSR            | PSSR                              | VDD2_SUP = 6.5 V, $I_{VDD2}$ = 200 mA,<br>Vnoise = 1 Vpp, fnoise = 465 kHz, $C_{VDD2}$ = 2.2 $\mu$ F Guaranteed by design                           | 20       |     |                  | dB   | VDD2 |

| VDD2_cur lim         | Current limitation                | VDD2 = -2 V                                                                                                                                         | 250      |     | 375              | mA   | VDD2 |

| VDD2_rev cur         | Reverse current in off condition  | VDD2 = 20 V VDD2_SUP from 0 V to 19 V, VDD2 disabled                                                                                                | 0.2      |     | 2                | mA   | VDD2 |

| VDD2_rev cur         | Reverse current in on condition   | VDD2 = 20 V VDD2_SUP from 0 V to 19 V VDD2 enabled                                                                                                  | 0.2      |     | 2                | mA   | VDD2 |

| VDD2_ovs_a           | Overshoot at power on             | $I_{VDD2}$ = 10 mA, $C_{VDD2}$ = 2.2 $\mu$ F                                                                                                        |          |     | 5.5              | V    | VDD2 |

| VDD2_ovs_b           | Overshoot at VBATP step           | VBATP step from 5.5 V to 13 V during 10 $\mu$ s, considering 1 $\mu$ H wiring harness, $I_{VDD2}$ = 200 mA, $C_{VDD2}$ = 2.2 $\mu$ F                |          |     | 5.7              | V    | VDD2 |

| VDD2_off             | Off state voltage                 |                                                                                                                                                     |          |     | 1                | V    | VDD2 |

| VDD2_soft            | Soft start                        | $I_{VDD2}$ = 10 mA, $C_{VDD2}$ = 2.2 $\mu$ F                                                                                                        | 5        |     | 25               | V/ms | VDD2 |

| Diagnostic           |                                   |                                                                                                                                                     |          |     |                  |      |      |

| VDD2_rev_<br>cur_det | Reverse current detection voltage |                                                                                                                                                     | VDD2_SUP |     | VDD2_SUP<br>+0.2 | V    | VDD2 |

| T_SD_TRK             | Temperature shut down             |                                                                                                                                                     | 175      |     | 185              | °C   | VDD2 |

| T_SD_hy              | Temperature shut down hysteresis  |                                                                                                                                                     | 5        |     | 10               | °C   | VDD2 |

| T_SD_deglitch        | Digital deglitch filter time      | Guaranteed by scan                                                                                                                                  | 7.5      | 10  | 12.5             | μs   | VDD2 |

# 8.2.3 VDD2 error handling

Table 9. VDD2 type of errors

| Type of error          | Detection condition | Action                                                                                                  | Clear SPI<br>flag | Restart condition                        |

|------------------------|---------------------|---------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------|

| VDD2 out of regulation | ON state            | Set VDD2_OUT_OF_REGULATION SPI flag (4) in TRK-CAN FAULT register                                       | On read           | N.A                                      |

| VDD2 reverse current   | ON state            | VDD2 internal path to VDD2_SUP open, VDD2_REVERSE_CURRENT SPI flag (6) latched in TRK-CANFAULT register | On read           | Automatic restart when fault disappears. |

DS12258 - Rev 5 page 24/178

| Type of error        | Detection condition | Action                                                                                                                                      | Clear SPI<br>flag | Restart condition                                                        |

|----------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------|

| VDD2 overtemperature | ON state            | No action if out of regulation is not triggered; output disabled, and T_SD_TRK (5)SPI fault bit latched otherwise in TRK-CAN FAULT register | On read           | Automatic restart<br>with slope control<br>after OT fault<br>disappears. |

# 8.3 VDD3

# 8.3.1 VDD3 functional description

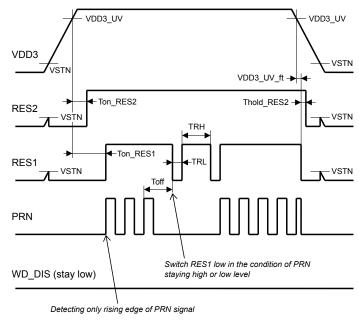

VDD3 is a linear regulator using external N-channel transistor as output stage to deliver current to the load and reduce ASIC power dissipation. The regulated voltage is configurable through the external feedback resistors. Dedicated monitors are present on the VDD3\_SEL pin to detect VDD3 undervoltage and overvoltage conditions; voltage monitors are not masked during power-up phase.

VDD3\_C VDD3\_SEL R3dw

VDD3\_Linear

Figure 12. VDD3 linear regulator with external N-ch FET

VDRAIN can be connected to either VBATP or, in order to limit power consumption, to a pre-regulated voltage.

#### 8.3.2 VDD3 electrical characteristics

$5.5 \text{ V} \le \text{VBATP} \le 19 \text{ V}$ ;  $5.5 \text{ V} \le \text{VDRAIN} \le 19 \text{ V}$ ;  $-40 \text{ °C} \le T_j \le 175 \text{ °C}$  unless otherwise noticed. All voltages refer to GND pin. STD20NF06L used as test reference for external MOS.

| Symbol            | Parameter                     | Test condition                                                               | Min  | Тур | Max | Unit | Pin  |

|-------------------|-------------------------------|------------------------------------------------------------------------------|------|-----|-----|------|------|

| Ciss              | External FET input capacitor  | Application note: FET selection max input capacitance to guarantee stability |      |     | 900 | pF   |      |

| Gm                | External FET transconductance | Application note: FET selection                                              |      | 20  |     | mho  |      |

| Vth               | External FET threshold        | Application note: FET selection threshold voltage                            |      |     | 3   | V    |      |

| VDD3_Vout         | Output voltage                | Application note                                                             | 0.8  |     | 5   | V    | VDD3 |

| I <sub>VDD3</sub> | Output load current           | Application note                                                             | 0.01 |     | 1   | Α    | VDD3 |

| C <sub>VDD3</sub> | Output capacitor              | Application note                                                             | 5    | 22  | 40  | μF   | VDD3 |

Table 10. VDD3 electrical characteristics

DS12258 - Rev 5 page 25/178

| Symbol                  | Parameter                                         | Test condition                                                                                                                                                       | Min                        | Тур | Max                         | Unit | Pin      |

|-------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|-----------------------------|------|----------|

| C <sub>VDD3_OPT</sub>   | Optional output capacitor <sup>(1)</sup>          | Application note max drivable cap in parallel with C <sub>VDD3</sub>                                                                                                 |                            |     | 220                         | μF   | VDD3     |

| C <sub>VDD3</sub> ESR   | Output capacitor ESR                              | Application note f ≤ 150 kHz                                                                                                                                         | 0.01                       |     | 0,1                         | Ω    | VDD3     |

| C <sub>DRAIN3</sub> EMI | Drain Output capacitor                            | Application note, VDRAIN=VBATP<br>Capacitor required on the drain of<br>external N-channel FET to prevent<br>self-mode oscillations and to improve<br>EMI robustness | 1                          |     |                             | μF   |          |

| C <sub>DRAIN3</sub> EMI | Drain Output capacitor                            | Application note, VDRAIN=VDD1<br>Capacitor required on the drain of<br>external N-channel FET to prevent<br>self-mode oscillations and to improve<br>EMI robustness  | 0.1                        |     |                             | μF   |          |

| R3up                    | Feedback resistor range                           |                                                                                                                                                                      | 5                          |     | 15                          | kΩ   | VDD3_SEL |

| VDD3 Regulator          |                                                   |                                                                                                                                                                      |                            |     |                             |      |          |

| VDD3_SEL                | Regulated feedback voltage                        | 0.01 A ≤ I <sub>VDD3</sub> ≤ 1 A                                                                                                                                     | 0.8–2%                     | 0.8 | 0.8+2%                      | V    | VDD3_SEL |

| VDD3_SEL line           | Line regulation                                   | VDRAIN 6 V to 19 V, I <sub>VDD3</sub> = 0.01 A, 1 A                                                                                                                  | -5                         |     | +5                          | mV   | VDD3_SEL |

| VDD3_SEL load           | Load regulation                                   | I <sub>VDD3</sub> = 0.01 A to 1 A, VDRAIN 6 V to 19 V                                                                                                                | -5                         |     | +5                          | mV   | VDD3_SEL |

| VDD3_SEL _tr1           | Transient output voltage                          | VDRAIN = 13 V, VDD3 $\geq$ 3.3 V,<br>$\Delta I_{VDD3}$ =300 mA; dI/dt = 0.5 A/ $\mu$ s,<br>$C_{VDD3}$ = 5 $\mu$ F, Guaranteed by design                              | -5                         |     | +5                          | %    | VDD3_SEL |

| VDD3_SEL _tr1           | Transient output voltage<br>1 (No Reset Asserted) | VDRAIN = 13 V, VDD3 < 3.3 V, $\Delta I_{VDD3}$ =300 mA; dI/dt = 0.5 A/ $\mu$ s, $C_{VDD3}$ = 5 $\mu$ F, Guaranteed by design                                         | -8                         |     | +8                          | %    | VDD3_SEL |

| VDD3_SEL _tr2           | Transient output voltage 2 (No Reset Asserted)    | VDRAIN step 12 V to 18 V; 18 V to 12 V, dVDRAIN/dt = 3 V/ $\mu$ s, I <sub>VDD3</sub> = 0.01 A, 1 A, C <sub>VDD3</sub> = 5 $\mu$ F, Guaranteed by design              | -7                         |     | +7                          | %    | VDD3_SEL |

| VDD3_G out              | Gate output voltage                               | VBATP = 5.5 V, Open loop condition,<br>VDD3_SEL = 0.7 V                                                                                                              | 12                         |     | 16                          | V    | VDD3_G   |

| VDD3_G pd               | Gate internal pull down                           |                                                                                                                                                                      | 100                        |     | 1000                        | kΩ   | VDD3_G   |

| VDD3_PSSR               | PSSR                                              | VDRAIN = 6.5 V, $I_{VDD3}$ = 500 mA,<br>Vnoise = 1 Vpp, fnoise = 465 kHz,<br>$C_{VDD3}$ = 5 $\mu$ F Guaranteed by design                                             | 20                         |     |                             | dB   | VDD3     |

| VDD3_SEL<br>ovs_a       | Overshoot at power on                             | $I_{VDD3}$ = 10 mA, $C_{VDD3}$ = 5 $\mu$ F                                                                                                                           |                            |     | 4%                          | V    | VDD3_SEL |

| VDD3_SEL<br>ovs_b       | Overshoot at VBATP step                           | VBATP step from 5.5 V to 13 V during 10 $\mu$ s, I <sub>VDD3</sub> = 500 mA, C <sub>VDD3</sub> = 5 $\mu$ F, Guaranteed by design                                     |                            |     | 10%                         | V    | VDD3_SEL |

| VDD3_SEL soft           | Slope control                                     | VDRAIN=VBATP = 13 V $I_{VDD3}$ = 10 mA, $C_{VDD3}$ = 4.7 $\mu$ F                                                                                                     | 1                          |     | 5                           | V/ms | VDD3_SEL |

| Diagnostic              |                                                   |                                                                                                                                                                      |                            |     |                             |      |          |

| VDD3_UV                 | VDD3_SEL undervoltage                             |                                                                                                                                                                      | VDD3_SEL<br>typ * (9.1/10) |     | VDD3_SEL<br>typ * (9.6/10)  | ٧    | VDD3_SEL |

| VDD3_UV_ft              | VDD3_SEL undervoltage filter time                 | Guaranteed by scan                                                                                                                                                   | 8                          |     | 16                          | μs   | VDD3_SEL |

| VDD3_OV                 | VDD3_SEL overvoltage                              |                                                                                                                                                                      | VDD3_SEL<br>typ * (11/10)  |     | VDD3_SEL<br>typ * (11.8/10) | V    | VDD3_SEL |

DS12258 - Rev 5 page 26/178

| Symbol     | Parameter                        | Test condition     | Min | Тур | Max | Unit | Pin      |

|------------|----------------------------------|--------------------|-----|-----|-----|------|----------|

| VDD3_OV_ft | VDD3_SEL overvoltage filter time | Guaranteed by scan | 16  |     | 32  | μs   | VDD3_SEL |

<sup>1.</sup> If VDRAIN is supplied by VDD1, the value of the optional filtering capacitor must be chosen taking into account VDD1 current limitation value vs in-rush current during regulator power-up and supply transients.

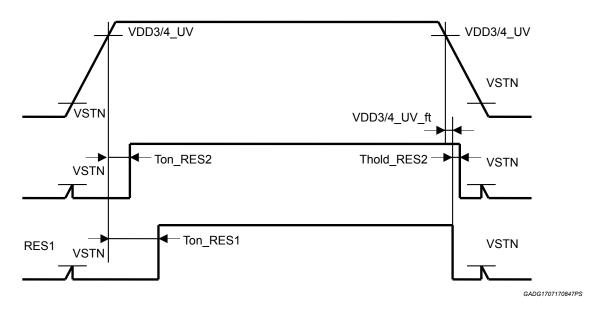

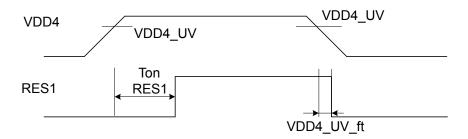

# 8.3.3 VDD3 error handling