Datasheet

#### Quad high-side smart power solid-state relay in QFN48L 8x6 mm package

**Features**

- Operating output current: 0.6 A (IPS4140HQ) or 1.0 A (IPS4140HQ-1) per channel

- Per channel short-circuit protection

- Per channel overtemperature protection

- Thermal case protection

- Not simultaneous channel reactivation at thermal case reset

- All type of loads (resistive, capacitive, inductive load) are driven

- Loss of GND protection

- · Undervoltage shutdown with hysteresis

- Overvoltage protection (V<sub>CC</sub> clamping)

- Very low supply current

- Per channel open drain thermal fault pins

- 5 V and 3.3 V compatible I/Os

- Fast demagnetization of inductive loads

- Designed to drive DC-13 loads according to EN 60947-5-1

- Designed to meet IEC61131-2, IEC61000-4-4, and IEC61000-4-5

- ESD according to IEC 61000-4-2 up to ±25 kV

#### Product status link

IPS4140HQ

IPS4140HQ-1

#### **Applications**

Industrial PC peripheral input/output

Numerical control machines

#### **Description**

The IPS4140HQ (for loads up to 0.6 A) and IPS4140HQ-1 (for loads up to 1.0 A) are monolithic 4-channel drivers featuring very low  $R_{DS(on)}$  and per-channel diagnostic. The ICs, realized in STMicroelectronics  $^{\text{TM}}$  VIPower  $^{\text{TM}}$  technology, are intended to drive any kind of load with one side connected to ground.

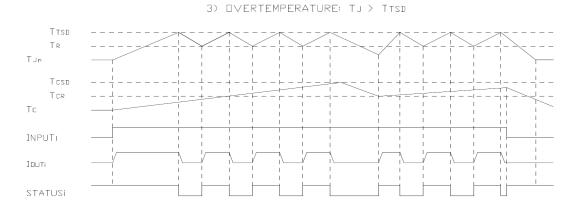

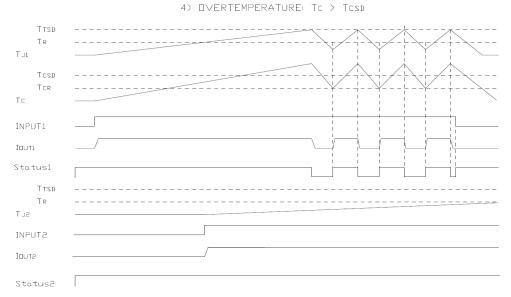

Active channel current limitation combined with thermal shutdown, independent for each channel, and automatic restart, protect the device against overload.

A channel in an overload condition overheats and turns OFF and back ON automatically in order to maintain its junction temperature between  $T_{TSD}$  and  $T_{R}$ . If this condition makes case temperature reach  $T_{CSD}$ , the overloaded channel is turned OFF and restarts only when case temperature has decreased down to  $T_{CR}$ .

In case of more than one channel in overload, restart of the overloaded channels is not simultaneous, in order to avoid high peak current from the supply. Non-overloaded (non-overheated) channels continue operating normally.

The four open drain  $STATUS_X$  output pins indicate per-channel overtemperature conditions.

# 1 Block diagram

Undervoltage Detection Vcc Clamp Input 1 GND Output 1 Input 2 Clamp Power Input 3 Output 2 Input 4Output 3 Current Limiter LOGIC Output 4 Junction Temp. Detection Status 1 Same structure for all channels Status 2 Status 3 Case Temp. Detection Status 4

Figure 1. Block diagram

DS14694 - Rev 3 page 2/29

### 2 Pin connection

NC VCC (TAB) NC NCNC NC NC NC NC NC NC NC NC NC STAT1 STAT3 STAT4

Figure 2. Pin connection (top through view)

Table 1. Pin description

| Pin                   | Name     | Туре              | Description                                                                                              |

|-----------------------|----------|-------------------|----------------------------------------------------------------------------------------------------------|

| TAB                   | $V_{CC}$ | Supply            | IC supply voltage.                                                                                       |

| 1 to 12, 22 to 35, 48 | NC       | -                 | Internally not connected (these pins can be routed at pcb level).                                        |

| 13                    | IN1      | Logic input       | Channel 1 input, 3.3 V CMOS/TTL compatible.                                                              |

| 14                    | STAT1    | Output/Open drain | Channel 1 overtemperature status (active low).                                                           |

| 15                    | IN2      | Logic input       | Channel 2 input, 3.3 V CMOS/TTL compatible.                                                              |

| 16                    | STAT2    | Output/Open drain | Channel 2 overtemperature status (active low).                                                           |

| 17                    | GND      | Ground            | Device ground connection.                                                                                |

| 18                    | STAT3    | Output/Open drain | Channel 3 overtemperature status (active low).                                                           |

| 19                    | IN3      | Logic input       | Channel 3 input, 3.3 V CMOS/TTL compatible.                                                              |

| 20                    | STAT4    | Output/Open drain | Channel 4 overtemperature status (active low).                                                           |

| 21                    | IN4      | Logic input       | Channel 4 input, 3.3 V CMOS/TTL compatible.                                                              |

| 36,37,38              | OUT4     | Output            | Channel 4 power stage output, internally protected. These three pins must be shorted on the application. |

| 39,40,41              | OUT3     | Output            | Channel 3 power stage output, internally protected. These three pins must be shorted on the application. |

| 42,43,44              | OUT2     | Output            | Channel 2 power stage output, internally protected. These three pins must be shorted on the application. |

| 45,46,47              | OUT1     | Output            | Channel 1 power stage output, internally protected. These three pins must be shorted on the application. |

DS14694 - Rev 3 page 3/29

## Maximum ratings

Table 2. Absolute maximum ratings

| Symbol              | Parameter                                                                                     | Value                  | Unit |

|---------------------|-----------------------------------------------------------------------------------------------|------------------------|------|

| V <sub>CC</sub>     | Power supply voltage                                                                          | -0.3 to 41             | V    |

| I <sub>GND</sub>    | DC ground reverse current                                                                     | -250                   | mA   |

| Гоит                | DC output current                                                                             | Internally limited (1) | Α    |

| I <sub>R</sub>      | DC reverse output current (per channel)                                                       | -15 <sup>(2)</sup>     | Α    |

| I <sub>IN</sub>     | Input pin current (per channel)                                                               | +/-10                  | mA   |

| V <sub>IN</sub>     | Input pin voltage                                                                             | +V <sub>CC</sub>       | V    |

| V <sub>STAT</sub>   | Status pin voltage                                                                            | +V <sub>CC</sub>       | V    |

| I <sub>STAT</sub>   | Status pin current (per pin)                                                                  | +/-10                  | mA   |

| V <sub>ESD</sub>    | Electrostatic discharge (R = 1.5 kΩ; C = 100 pF)                                              | 2000                   | V    |

| E <sub>AS</sub> (3) | Single channel/single pulse avalanche energy $@T_{amb} = 125  ^{\circ}C$ , $I_{OUT} = 0.5  A$ | 2.5                    | J    |

| P <sub>TOT</sub>    | Power dissipation at T <sub>C</sub> = 25 °C                                                   | Internally limited (1) | W    |

| T <sub>J</sub>      | Junction operating temperature                                                                | Internally limited (1) | °C   |

| T <sub>STG</sub>    | Storage temperature                                                                           | -55 to 150             | °C   |

Protection functions are intended to avoid IC damage in fault conditions and are not intended for continuous operation. Continuous and repetitive operation of protection functions may reduce the IC lifetime.

Table 3. Thermal data

| Symbol              | Parameter                               | Value | Unit |

|---------------------|-----------------------------------------|-------|------|

| R <sub>th(JC)</sub> | Thermal resistance junction-case (1)    | 1.5   | °C/W |

| R <sub>th(JA)</sub> | Thermal resistance junction-ambient (2) | 27    | °C/W |

<sup>1.</sup> Rth between the die and the bottom case surface measured by cold plate as per JESD51-12

2. JESD51-7

DS14694 - Rev 3 page 4/29

<sup>2.</sup> Intended with the 3 pins of each OUTX connected together in the application board.

<sup>3.</sup> Single pulse, not repetitive

## 4 Recommended operating conditions

Table 4. Input switching limits

| Symbol                | Parameter                                | Value | Unit |

|-----------------------|------------------------------------------|-------|------|

| f <sub>VIN(MAX)</sub> | N(MAX) Maximum input switching frequency |       | kHz  |

DS14694 - Rev 3 page 5/29

## 5 Electrical characteristics

10.5 V <  $V_{CC}$  < 36 V; -40 °C <  $T_{J}$  < 125 °C; unless otherwise specified

#### 5.1 Power section

Table 5. Power section

| Symbol                                  | Parameter                                                        | Test conditions                                                                  | Min. | Тур. | Max. | Unit |

|-----------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|------|

| V <sub>CC</sub>                         | Supply voltage                                                   |                                                                                  | 10.5 |      | 36   | V    |

|                                         |                                                                  | IPS4140HQ,<br>I <sub>OUT</sub> = 0.5 A @T <sub>J</sub> = 25 °C                   |      |      | 0.08 |      |

| В                                       | ON state assistence                                              | IPS4140HQ, I <sub>OUT</sub> = 0.5 A                                              |      |      | 0.14 |      |

| R <sub>DS(on)</sub> ON-state resistance | IPS4140HQ-1,<br>I <sub>OUT</sub> = 0.7 A @T <sub>J</sub> = 25 °C |                                                                                  |      | 0.08 | Ω    |      |

|                                         |                                                                  | IPS4140HQ-1, I <sub>OUT</sub> = 0.7 A                                            |      |      | 0.14 |      |

|                                         |                                                                  | All channels in OFF-state                                                        |      | 0.25 |      | mA   |

| I <sub>S</sub>                          | V <sub>CC</sub> supply current                                   | All channels in ON-state,<br>V <sub>IN14</sub> = 5 V                             |      | 2.4  | 4    | mA   |

| V <sub>CC</sub> clamp                   | Clamp on V <sub>CC</sub>                                         | I <sub>S</sub> = 20 mA                                                           | 41   | 45   | 52   | V    |

| V <sub>OUT(OFF)</sub>                   | OFF-state output voltage                                         | V <sub>IN</sub> = 0 V, I <sub>OUT</sub> = 0 A, V <sub>CC</sub> = 24V             |      |      | 1    | V    |

| I <sub>OUT(OFF)</sub>                   | OFF-state output current                                         | V <sub>IN</sub> = V <sub>OUT</sub> = 0 V, V <sub>CC</sub> = 24V                  | 0    |      | 5    | μΑ   |

|                                         | IPS4140HQ output current at GND disconnection                    | V <sub>CC</sub> = V <sub>IN</sub> = V <sub>STAT</sub> = V <sub>GND</sub> = 24 V; |      |      | 1.0  | mA   |

| curre                                   | IPS4140HQ-1 output<br>current at GND<br>disconnection            | $V_{OUT} = 0 V$                                                                  |      |      | 0.5  | mA   |

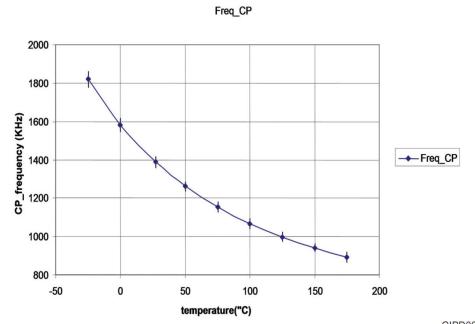

| f <sub>CP</sub>                         | Charge pump frequency                                            | Channel in ON-state (1)                                                          |      | 1.45 |      | MHz  |

<sup>1.</sup> To cover EN55022 class A and class B normative.

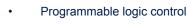

#### 5.2 Switching

Table 6. Switching

| Symbol                               | Parameter              | Test conditions                                                                | Min. | Тур. | Max. | Unit |

|--------------------------------------|------------------------|--------------------------------------------------------------------------------|------|------|------|------|

| t <sub>PD(L-H)</sub>                 | Turn-on delay time     |                                                                                |      | 16   | 35   | μs   |

| t <sub>r</sub>                       | Rise time              |                                                                                |      | 8    | 25   | μs   |

| t <sub>PD(H-L)</sub>                 | Turn-off delay time    | $V_{CC}$ = 24 V, R <sub>L</sub> = 48 Ω, input rise time < 0.1 μs, see Figure 3 |      | 21   | 36   | μs   |

| t <sub>f</sub>                       | Fall time              |                                                                                |      | 4    | 12   | μs   |

| dV <sub>(ON)</sub> /dt <sub>r</sub>  | Turn-on voltage slope  |                                                                                |      | 2    |      | V/µs |

| dV <sub>(OFF)</sub> /dt <sub>f</sub> | Turn-off voltage slope |                                                                                |      | 4    |      | V/µs |

DS14694 - Rev 3 page 6/29

Figure 3. Timing in normal operation

## 5.3 Logic inputs

Table 7. Logic inputs

| Symbol               | Parameter                | Test conditions        | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------|------------------------|------|------|------|------|

| V <sub>IL</sub>      | Input low level voltage  |                        |      |      | 0.8  | V    |

| V <sub>IH</sub>      | Input high level voltage |                        | 2.20 |      |      | V    |

| V <sub>I(HYST)</sub> | Input hysteresis voltage |                        |      | 0.15 |      | V    |

| 1                    | Innut ourrant            | V <sub>IN</sub> = 15 V |      |      | 10   |      |

| IIN                  | Input current            | V <sub>IN</sub> = 36 V |      |      | 210  | μA   |

DS14694 - Rev 3 page 7/29

### 5.4 Protection and diagnostic

Table 8. Protection and diagnostic

| Symbol              | Parameter                                 | Test conditions                                          | Min.                 | Тур.                 | Max.                 | Unit |

|---------------------|-------------------------------------------|----------------------------------------------------------|----------------------|----------------------|----------------------|------|

| V <sub>STAT</sub>   | Status voltage output low                 | I <sub>STAT</sub> = 1.6 mA                               |                      |                      | 0.6                  | V    |

| V <sub>USD</sub>    | Undervoltage protection                   |                                                          | 7                    |                      | 10.5                 | V    |

| V <sub>USDHYS</sub> | Undervoltage hysteresis                   |                                                          | 0.4                  | 0.5                  |                      | V    |

| I                   | IPS4140HQ maximum DC output current       | Dunamia land                                             |                      | 1.3                  |                      |      |

| I <sub>PEAK</sub>   | IPS4140HQ-1 maximum DC output current     | Dynamic load                                             |                      | 1.6                  |                      | Α    |

| Luci                | IPS4140HQ, DC short-circuit current       | $V_{CC} = 24 \text{ V}, R_{LOAD} \le 10 \text{ m}\Omega$ | 0.7                  | 1.0                  | 1.7                  |      |

| I <sub>LIM</sub>    | IPS4140HQ-1, DC short-<br>circuit current | VCC - 24 V, KLOAD = 10 11112                             | 1.1                  | 1.5                  | 2.6                  | Α    |

| I <sub>LSTAT</sub>  | Status leakage current                    | V <sub>CC</sub> = V <sub>STAT</sub> = 36 V               |                      | 30                   |                      | μΑ   |

| T <sub>TSD</sub>    | Junction shutdown temperature             |                                                          | 150                  | 170                  | 190                  | °C   |

| T <sub>R</sub>      | Junction reset temperature                |                                                          | 135                  |                      |                      | °C   |

| T <sub>HYST</sub>   | Junction thermal hysteresis               |                                                          | 7                    | 15                   |                      | °C   |

| T <sub>CSD</sub>    | Case shutdown temperature                 |                                                          | 125                  | 130                  | 135                  | °C   |

| T <sub>CR</sub>     | Case reset temperature                    |                                                          | 110                  |                      |                      | °C   |

| T <sub>CHYST</sub>  | Case thermal hysteresis                   |                                                          | 7                    | 15                   |                      | °C   |

| $V_{DEMAG}$         | Output voltage at turn-OFF                | I <sub>OUT</sub> = 0.5 A; L <sub>LOAD</sub> ≥ 1 mH       | V <sub>CC</sub> - 41 | V <sub>CC</sub> - 45 | V <sub>CC</sub> - 52 | V    |

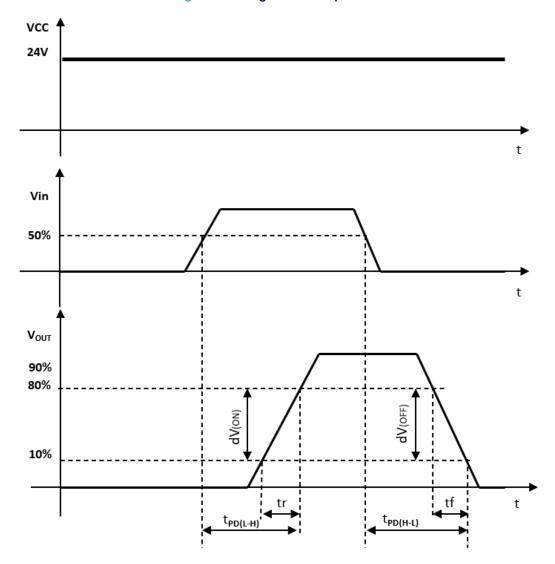

#### 5.5 Current and voltage conventions

Figure 4. Current and voltage conventions

DS14694 - Rev 3 page 8/29

## 6 Truth table

Table 9. Truth table

| Condition                                   | Input <sub>n</sub> | Output <sub>n</sub> | Status <sub>n</sub> |

|---------------------------------------------|--------------------|---------------------|---------------------|

| Normal eneration                            | L                  | L                   | Н                   |

| Normal operation                            | Н                  | Н                   | Н                   |

| Overtemperature                             | L                  | L                   | Н                   |

| Overtemperature                             | Н                  | L                   | L                   |

| Lindonyoltogo                               | L                  | L                   | X                   |

| Undervoltage                                | Н                  | L                   | X                   |

| Output overload                             | L                  | L                   | Н                   |

| (current limitation before overtemperature) | Н                  | X                   | Н                   |

Note: X = don't care

DS14694 - Rev 3 page 9/29

## Typical application circuit

Vcc 100 n OUT Vcc IN 1 IN 2 IN 3 IN 4 LOAD1 OUT1 LOAD2 OUT2 ۲ Vdd IC  $\mu \mathrm{C}$ LOAD3 OUT3 STAT 1 STAT 2 STAT 3 STAT 4 10k LOAD4 OUT4 10 n GND

Figure 5. Typical application circuit

DS14694 - Rev 3 page 10/29

### 8 Thermal management

The power dissipation in the IC is the main factor that sets the safe operating condition of the device in the application. Therefore, it must be considered very carefully. Furthermore, the available space on the PCB should be chosen considering the power dissipation. Heat sinking can be achieved using copper on the PCB with proper area and thickness. Two different protections have been implemented to guarantee safety of the device if it overheats due to an overloaded condition or high environment temperature. The following flowchart explains in detail this protection functionality.

OUT(i) On STAT(i) Off (H) 1 NO YES Tj(i) > Ttsd OUT(i) Off STAT(i) On (L) YES NO 2 Tc > Tcsd 4 YES NO Tc >Tar YES NO  $T_{j}(i) > T_{j}r$ 3 GIPG030420151405LM

Figure 6. Thermal behavior

Note: 1 Thermal shutdown

2 Junction hysteresis

3 Restore to idle condition

4 Case hysteresis

DS14694 - Rev 3 page 11/29

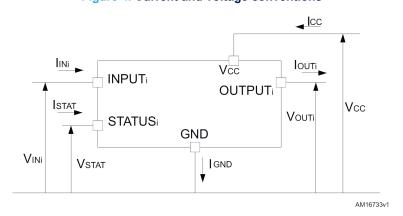

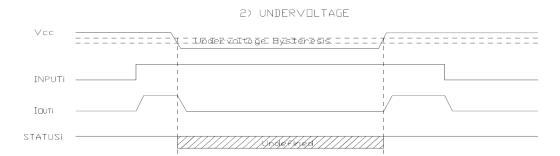

## 9 Switching waveforms

Figure 7. Switching waveforms

1) NORMAL OPERATION

GIPD0611131025LM

DS14694 - Rev 3 page 12/29

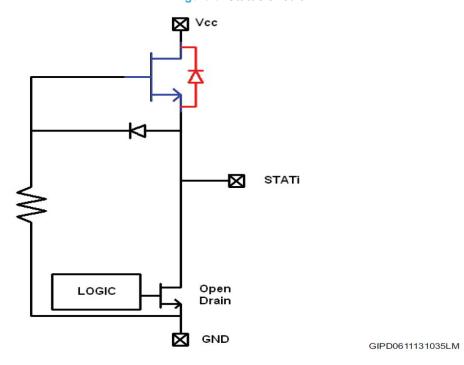

## 10 Pin function description

Figure 8. Input circuit

Figure 9. Status circuit

DS14694 - Rev 3 page 13/29

Figure 10. Charge pump switching frequency (typical) vs. temperature

GIPD0611131040LM

DS14694 - Rev 3 page 14/29

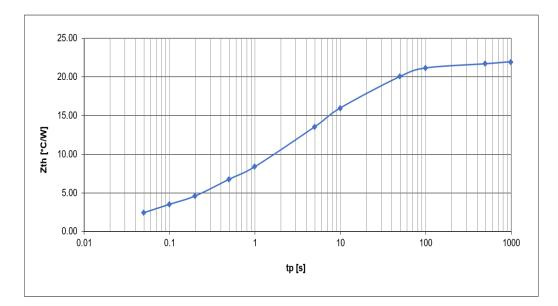

#### 11 Thermal data

The power dissipation in the IC is the main factor that sets the safe operating condition of the device in the application. Therefore, it must be taken into account very carefully.

Heatsinking can be achieved using copper on the PCB with proper area and thickness.

The following image shows the junction-to-ambient thermal impedance values for the QFN48L 8x6 mm package referred to JEDEC conditions with 2s2p layers and thermal vias below the exposed pad.

Figure 11. QFN48L 8x6 mm, thermal impedance

DS14694 - Rev 3 page 15/29

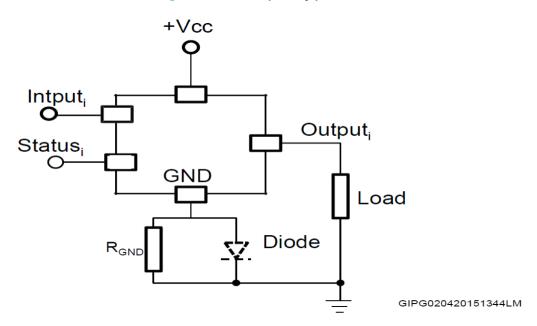

#### 12 Reverse polarity protection

Reverse polarity protection can be implemented on-board using two different solutions:

- 1. Placing a resistor (R<sub>GND</sub>) between IC GND pin and load GND

- 2. Placing a diode between IC GND pin and load GND

If option 1 is selected, the minimum resistance value has to be selected according to the following equation:

where I<sub>GND</sub> is the DC reverse ground pin current and can be found in Section 3 of this datasheet.

Power dissipated by  $R_{GND}$  (when  $V_{CC} < 0$ : during reverse polarity situations) is:

$$P_D = (V_{CC})^2 / R_{GND}$$

If option 2 is selected, the diode has to be chosen by taking into account VRRM  $>|V_{CC}|$  and its power dissipation capability:

$$P_D \ge I_S^*V_F$$

Note:

In normal conditions (no reverse polarity), due to the diode, there is a voltage drop between GND of the device and GND of the system.

Figure 12. Reverse polarity protection

This schematic can be used with any type of load.

DS14694 - Rev 3 page 16/29

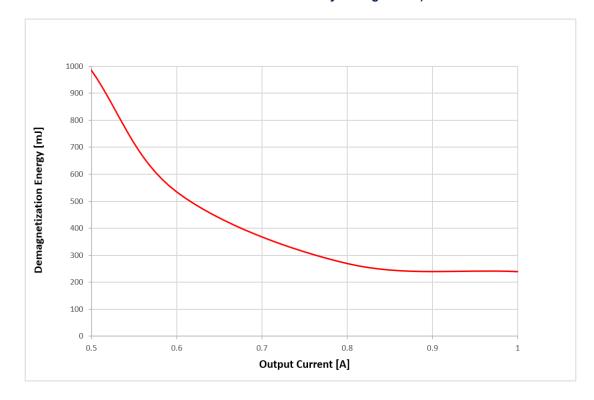

## 13 Demagnetization energy

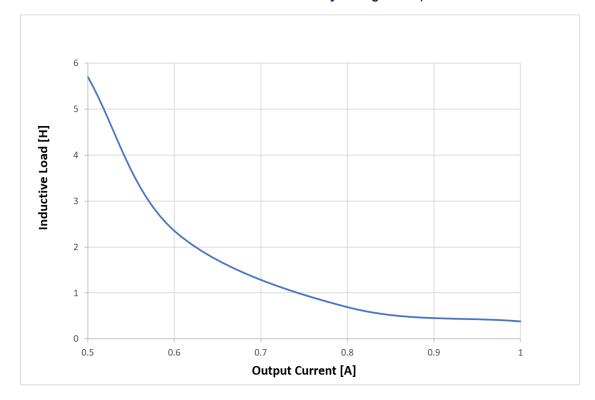

Figure 13. Typical single pulse (not repetitive) demagnetization:  $E_{OFF}$  vs  $I_{OUT}$  ( $V_{CC}$  = 24 V,  $T_{AMB}$  = 125 °C, all channels simultaneously demagnetized)

DS14694 - Rev 3 page 17/29

Figure 14. Typical single pulse (not repetitive) demagnetization:  $L_{LOAD}$  vs  $I_{OUT}$  ( $V_{CC}$  = 24 V,  $T_{AMB}$  = 125 °C, all channels simultaneously demagnetized)

DS14694 - Rev 3 page 18/29

## 14 Maximum capacitive load

Following table shows the value of maximum capacitive load.

The value is calculated using a dedicated evaluation board (X-Nucleo-OUT20A1 or X-Nucleo-OUT21A1) with an RC load on one channel and leaving the other three channels in open load state.

Table 10. Maximum capacitive load

| Symbol                 | Parameter                                       | Value | Unit |

|------------------------|-------------------------------------------------|-------|------|

| C <sub>LOAD(MAX)</sub> | Maximum capacitive load @ VCC=24 V, Tamb=125 °C | 300   | μF   |

DS14694 - Rev 3 page 19/29

## 15 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

#### 15.1 Package mechanical data

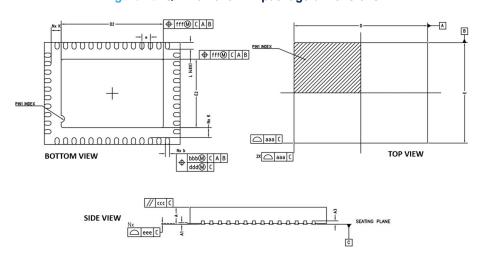

Figure 15. QFN48L 8x6 mm package dimensions

Table 11. QFN48L, mechanical data

| Dim.   | (mm)  |                                  |       |  |  |

|--------|-------|----------------------------------|-------|--|--|

| Dilli. | Min.  | Тур.                             | Max.  |  |  |

| Α      | 0.80  | 0.85                             | 0.90  |  |  |

| A1     | 0.00  | -                                | 0.05  |  |  |

| A3     |       | 0.20 REF.                        |       |  |  |

| b      | 0.20  | 0.25                             | 0.30  |  |  |

| D      |       | 8.00 BSC                         |       |  |  |

| е      |       | 0.50 BSD                         |       |  |  |

| E      |       | 6.00 BSC                         |       |  |  |

| D2     | 5.97  | 6.02                             | 4.07  |  |  |

| E2     | 3.97  | 4.02                             | 4.07  |  |  |

| L      | 0.365 | 0.40                             | 0.435 |  |  |

| k      | 0.53  | -                                | -     |  |  |

| N      |       | Tolerance of forms and positions | ;     |  |  |

| aaa    |       | 0.10                             |       |  |  |

| bbb    | 0.10  |                                  |       |  |  |

| ccc    | 0.10  |                                  |       |  |  |

| ddd    | 0.05  |                                  |       |  |  |

| eee    | 0.05  |                                  |       |  |  |

| fff    |       | 0.10                             |       |  |  |

DS14694 - Rev 3 page 20/29

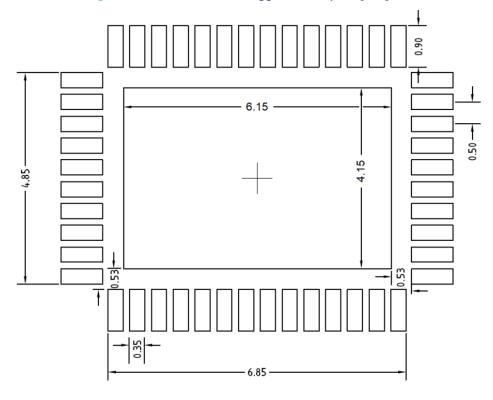

Figure 16. QFN48L 8x6 mm suggested footprint [mm]

Note:

STMicroelectronics is not responsible for any PCB related issues. The footprint shown in the above figure is a suggestion which might not be in line with the customer PCB supplier design rules.

DS14694 - Rev 3 page 21/29

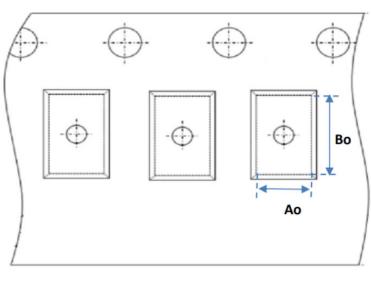

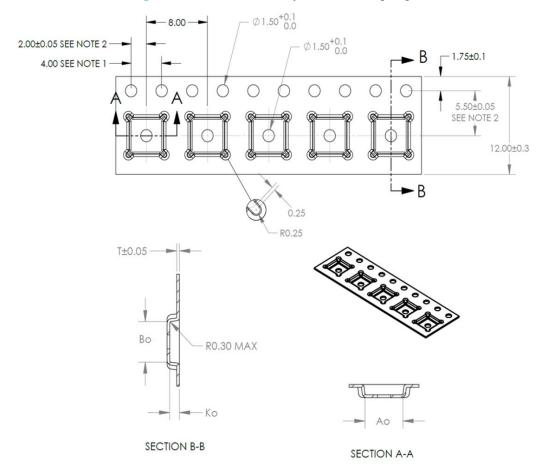

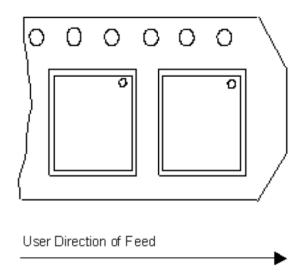

## 16 QFN48L, packing information

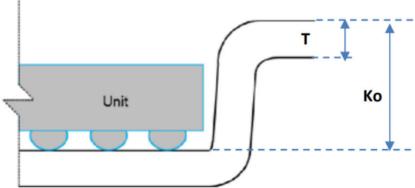

Figure 17. QFN48L reel shipment reference

Table 12. Standard SPC parameters

| Description | Value          |

|-------------|----------------|

| Ao          | Pocket Length  |

| Во          | Pocket Width   |

| Ко          | Pocket Depth   |

| Т           | Tape Thickness |

DS14694 - Rev 3 page 22/29

Figure 18. QFN48L carrier tape dimensions [mm]

Figure 19. QFN48L carrier tape, Pin 1 indication

DS14694 - Rev 3 page 23/29

## 17 Ordering information

Table 13. Order codes

| Order code  | Package       | Package marking | Packaging     |

|-------------|---------------|-----------------|---------------|

| IPS4140HQ   | QFN48L 8x6 mm | IPS4140HQ       | Tape and reel |

| IPS4140HQ-1 |               | IPS4140HQ-1     | Tape and Teer |

DS14694 - Rev 3 page 24/29

## **Revision history**

**Table 14. Document revision history**

| Date        | Version | Changes                                                                                                |

|-------------|---------|--------------------------------------------------------------------------------------------------------|

| 06-Dec-2024 | 1       | Initial release.                                                                                       |

| 10-Jul-2025 | 2       | Corrected typo in Table 13; some minor changes.                                                        |

| 13-Oct-2025 | 3       | Added "Designed to drive DC-13 loads according to EN 60947-5-1" in Section Features; added Section 14. |

DS14694 - Rev 3 page 25/29

## **Contents**

| 1     | Blo    | ck diagram                      | 2    |

|-------|--------|---------------------------------|------|

| 2     | Pin    | connection                      | 3    |

| 3     | Max    | imum ratings                    | 4    |

| 4     | Rec    | ommended operating conditions   | 5    |

| 5     | Elec   | ctrical characteristics         | 6    |

|       | 5.1    | Power section                   | 6    |

|       | 5.2    | Switching                       | 6    |

|       | 5.3    | Logic inputs                    | 7    |

|       | 5.4    | Protection and diagnostic       | 8    |

|       | 5.5    | Current and voltage conventions | 8    |

| 6     | Trut   | h table                         | 9    |

| 7     | Тур    | ical application circuit        | .10  |

| 8     | The    | rmal management                 | .11  |

| 9     | Swi    | tching waveforms                | .12  |

| 10    | Pin    | function description            | .13  |

| 11    | The    | rmal data                       | .15  |

| 12    | Rev    | erse polarity protection        | .16  |

| 13    | Den    | nagnetization energy            | .17  |

| 14    | Max    | imum capacitive load            | .19  |

| 15    | Pac    | kage information                | .20  |

|       | 15.1   | Package mechanical data         | . 20 |

| 16    | QFN    | N48L, packing information       | .22  |

| 17    | Ord    | ering information               | .24  |

| Rev   | ision  | history                         | .25  |

|       |        | bles                            |      |

| l iet | of fic | THE                             | 28   |

## **List of tables**

| Table 1.  | Pin description           | 3  |

|-----------|---------------------------|----|

| Table 2.  | Absolute maximum ratings  | 4  |

| Table 3.  | Thermal data              |    |

| Table 4.  | Input switching limits    | 5  |

| Table 5.  | Power section             | 6  |

| Table 6.  | Switching                 | 6  |

| Table 7.  | Logic inputs              | 7  |

| Table 8.  | Protection and diagnostic | 8  |

| Table 9.  | Truth table               |    |

| Table 10. |                           |    |

| Table 11. | QFN48L, mechanical data   | 0  |

| Table 12. |                           | 2  |

| Table 13. | Order codes               | 4  |

| Table 14. | Document revision history | :5 |

DS14694 - Rev 3 page 27/29

# **List of figures**

| Figure 1.  | Block diagram                                                                                                                                                  | . 2 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Pin connection (top through view)                                                                                                                              | . 3 |

| Figure 3.  | Timing in normal operation                                                                                                                                     | . 7 |

| Figure 4.  | Current and voltage conventions                                                                                                                                | . 8 |

| Figure 5.  | Typical application circuit                                                                                                                                    | 10  |

| Figure 6.  | Thermal behavior                                                                                                                                               | 11  |

| Figure 7.  | Switching waveforms                                                                                                                                            | 12  |

| Figure 8.  | Input circuit                                                                                                                                                  | 13  |

| Figure 9.  | Status circuit                                                                                                                                                 | 13  |

| Figure 10. | Charge pump switching frequency (typical) vs. temperature                                                                                                      | 14  |

| Figure 11. | QFN48L 8x6 mm, thermal impedance                                                                                                                               | 15  |

| Figure 12. | Reverse polarity protection                                                                                                                                    | 16  |

| Figure 13. | Typical single pulse (not repetitive) demagnetization: $E_{OFF}$ vs $I_{OUT}$ ( $V_{CC}$ = 24 V, $T_{AMB}$ = 125 °C, all channels simultaneously demagnetized) | 17  |

| Figure 14. | Typical single pulse (not repetitive) demagnetization: L <sub>LOAD</sub> vs I <sub>OUT</sub> (V <sub>CC</sub> = 24 V, T <sub>AMB</sub> = 125 °C, all channels  |     |

|            | simultaneously demagnetized)                                                                                                                                   | 18  |

| Figure 15. | QFN48L 8x6 mm package dimensions                                                                                                                               | 20  |

| Figure 16. | QFN48L 8x6 mm suggested footprint [mm]                                                                                                                         | 21  |

| Figure 17. | QFN48L reel shipment reference                                                                                                                                 | 22  |

| Figure 18. | QFN48L carrier tape dimensions [mm]                                                                                                                            | 23  |

| Figure 19. | QFN48L carrier tape, Pin 1 indication                                                                                                                          | 23  |

|            |                                                                                                                                                                |     |

DS14694 - Rev 3 page 28/29

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics - All rights reserved

DS14694 - Rev 3 page 29/29