## Single channel low side switch with configurable smart overload protection

#### **Features**

- Smart overload protection with configurable inrush and limitation levels

- Fast demagnetization of inductive loads

- Junction over-temperature protections

- Over-temperature diagnostic pin

- Designed to drive DC-13 loads according to EN 60947-5-1

- Designed to meet IEC 61000-4-2, IEC 61000-4-4, IEC 61000-4-5

- Package QFN32L 6x6 mm

#### **Typical Applications**

- Programmable logic control

- Industrial PC peripheral input/output

- · Numerical control machines

- General Low-Side Switch Applications

# Product status link

IPS1050LQ

# SUSTAINABLE TECHNOLOGY

#### **Description**

The IPS1050LQ is a single low side switch IC, with 65 V absolute maximum rating on the output stage, able to drive capacitive, resistive, or inductive loads with one side connect to supply rail.

The very low  $R_{DS-ON}$  ( $\leq$  50 m $\Omega$ ) and the smart overload protection based on the configuration of the pins  $I_{PDX}$ , make the IC suitable for the for applications requiring high inrush current (up to 25 A) and with different configurable steady state operating current

The level of inrush current can be modified setting high/low the  $I_{PDX}$  pins or automatically reduced by the IC itself when the internal timer (regulated by capacitors on  $I_{PDX}$  pins) elapses.

After the inrush current phase, the embedded overload protection can limit the steady state output current to  $I_{LIM}$  level featuring both the IC and load protections.

The output channel is protected against junction over-temperature by dedicated temperature sensor.

The diagnostic pin OVT is activated while the over-temperature event persist.

PGND

# **Block diagram**

VCC UVLO I<sub>PD1</sub> CONTROL OUT LOGIC  $I_{PD2}$ I<sub>PD3</sub> **OUTPUT CLAMP** IN CURRENT OVT LIMITATION **FAULT OVER-TEMPERATURE** MANAGER **PROTECTION**

SGND

Figure 1. Block diagram

page 2/29

## 2 Pin connection

SGND PGND PGND PGND PGND PGND VCC  $\mathbb{R}$ 32 25 31 24 NC IN 23 NC NC 3 22 NC OVT 4 21 NC TEST ΕP (Exposed Pad = OUT) 5 20 NC NC 6 19 NC IPD1 18 NC IPD2 17 8 IPD3 NC 16 2  $\mathbb{R}$ 2 PGND PGND PGND PGND PGND

Figure 2. Pin connections (top through view)

DS14912 - Rev 2 page 3/29

**Table 1. Pin descriptions**

| N.                          | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Туре                   |

|-----------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1                           | IN   | Input signal driving internal power switch and power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Input                  |

| 2                           | NC   | This lead is not internally connected: it can be used for routing at pcb level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                      |

| 3                           | OVT  | Overtemperature diagnostic pin. This pin is activated when the IC triggers the over-temperature condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Output<br>(Open Drain) |

| 4                           | TEST | Reserved for internal use: leave it floating or connected to SGND by 1 $\mbox{k}\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Open Drain             |

| 5                           | NC   | This lead is not internally connected: it can be used for routing at pcb level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                      |

| 6                           | IPD1 | Current limitation level and timer selectors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |

| 7                           | IPD2 | These I <sub>PDX</sub> pins can be set High or Low by connecting to IN or SGND pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |

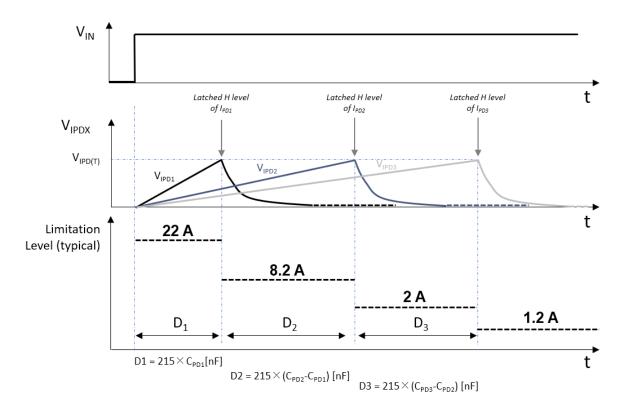

| 8                           | IPD3 | through a 10 k $\Omega$ resistor to select the steady state current limitation level, Table 11 <sup>(1)</sup> . Smart/dynamic output current limitation can be activated by connecting the pin I <sub>PDX</sub> pin to SGND by a capacitor (C <sub>PDX</sub> ) defining how long the initial level is active (I <sub>LIM(I)</sub> ) before the steady state limitation level (I <sub>LIM(S)</sub> ) is activated. The I <sub>LIM(S)</sub> remains active until next Low-to-High transition of the IN pin, Table 12 <sup>(1)</sup> . It is also possible to connect a capacitor between each I <sub>PDX</sub> pin and SGND. The output current limitation level automatically reduces from highest current limitation level to lowest level across intermediate levels; the values of the C <sub>PDX</sub> capacitors define how long each level remains active and the sequence of the intermediate levels, Figure 4. Leaving I <sub>PDX</sub> floating is equivalent to a 1 $\mu$ s duration for D <sub>PKX</sub> .  (1): the maximum operating current in steady state condition is anyway limited by the thermal capability of the package and by the ambient temperature. For example, assumed the R <sub>TH(JA)</sub> reported in Table 3 and load current of 6.0 A with I <sub>PD1, 2, 3</sub> = L-H-H, the maximum ambient temperature is 92 °C. | Logic / Analog Input   |

| 9,10,11                     | NC   | These leads are not internally connected: they can be used for routing at pcb level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                      |

| 12,13,14,15,16              | DCND | Internal power switch ground. These leads are connected to the source of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cround                 |

| 25,26,27,28,29              | PGND | the embedded N-channel power switch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ground                 |

| 17,18,19,20,21,<br>22,23,24 | NC   | These leads are not internally connected: they can be used for routing at pcb level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                      |

| 30                          | SGND | Internal Logic ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Ground                 |

| 31                          | NC   | This lead is not internally connected: it can be used for routing at pcb level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                      |

| 32                          | VCC  | Logic supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Supply                 |

| EP                          | OUT  | Power stage output / load connection point. The exposed pad is connected to the drain of the embedded N-channel power mosfet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Analog Output          |

DS14912 - Rev 2 page 4/29

# 3 Absolute maximum ratings

Absolute maximum ratings are the values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All voltages are referenced to GND.

Table 2. Absolute maximum ratings

| Symbol            | Parameter                                                                                                   | Value              | Unit |

|-------------------|-------------------------------------------------------------------------------------------------------------|--------------------|------|

| V <sub>OUT</sub>  | Voltage at output switch drain                                                                              | Internally clamped | V    |

| I <sub>OUT</sub>  | Output switch current                                                                                       | Internally limited | Α    |

| -I <sub>OUT</sub> | Reverse output current (from PGND to OUT)                                                                   | 30 (1)             | Α    |

| V <sub>CC</sub>   | Voltage at supply pin                                                                                       | -0.3 to 12         | V    |

| V <sub>IN</sub>   | Input pin voltage                                                                                           | -0.3 to 5.5        | V    |

| I <sub>IN</sub>   | Input pin current                                                                                           | -1/+10             | mA   |

| V <sub>PDX</sub>  | I <sub>PD1</sub> , I <sub>PD2</sub> , I <sub>PD3</sub> pins voltage                                         | -0.3 to 5.5        | V    |

| I <sub>PDX</sub>  | I <sub>PD1</sub> , I <sub>PD2</sub> , I <sub>PD3</sub> pins current                                         | -1/+10             | mA   |

| $V_{DIAG}$        | OVT pin voltage                                                                                             | -0.3 to 5.5        | V    |

| I <sub>DIAG</sub> | OVT pin current                                                                                             | -1/+10             | mA   |

| E <sub>AS</sub>   | Single pulse avalanche energy (T <sub>AMB</sub> = 125 °C, V <sub>LOAD</sub> = 24 V, I <sub>OUT</sub> = 2 A) | 1                  | J    |

| P <sub>TOT</sub>  | Power Dissipation at T <sub>C</sub> = 25 °C                                                                 | Internally limited | W    |

| T <sub>STG</sub>  | Storage Temperature Range                                                                                   | -55 to 150         | °C   |

| TJ                | Junction Temperature                                                                                        | -40 to 150         | °C   |

<sup>1.</sup> The limit is intended with all PGND leads connected to the ground layer of the application board. Also, note that in reverse polarity conditions the internal protections (such as overload and over-temperature) are not active.

DS14912 - Rev 2 page 5/29

# 4 Thermal data

Table 3. Thermal data

| Symbol                  | Parameter                           | Value  | Unit |

|-------------------------|-------------------------------------|--------|------|

| R <sub>th(JC)</sub> (1) | Thermal resistance junction-case    | 2      | °C/W |

| R <sub>th(JA)</sub> (2) | Thermal resistance junction-ambient | 32 (3) | °C/W |

- 1. Rth between the die and the bottom case surface measured by cold plate as per JESD51-12

- 2. JESD51-7.

- 3. Maximum output power =2 W (at  $T_J$  < 150 °C and  $T_{AMB}$  = 85 °C).

DS14912 - Rev 2 page 6/29

# 5 Electrical characteristics

(V<sub>CC</sub> = 9 V; -40 °C < T<sub>J</sub> < 125 °C, unless otherwise specified)

Table 4. Output stage

| Symbol                          | Parameter                         | Test Conditions                                                                           | Min. | Тур. | Max. | Unit |

|---------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>CC</sub>                 | Operating range                   | -                                                                                         | 5.8  |      | 10   | V    |

| V <sub>CC(ON)</sub>             | VCC activation threshold          | VCC rising                                                                                |      | 5.3  | 5.8  | V    |

| V <sub>CC(OFF)</sub>            | VCC deactivation threshold        | VCC falling                                                                               | 4.5  | 5.2  |      | V    |

| V <sub>CC(HYST)</sub>           | VCC deactivation hysteresis       | -                                                                                         |      | 0.2  |      | V    |

| I <sub>CC(ON)</sub>             | Supply current in ON state        | V <sub>IN</sub> = 3.3 V                                                                   |      | 1    | 1.4  | mA   |

| I <sub>CC(OFF)</sub>            | Supply current in inactive status | V <sub>IN</sub> = SGND                                                                    |      | 1    | 1.5  | mA   |

| R <sub>DSON</sub> (             | On-state resistance               | $V_{CC}$ = 6 V, $V_{IN}$ = 3.3 V, $I_{LOAD}$ = 2 A,<br>@ $T_J$ = 25 °C                    |      | 25   |      | mΩ   |

|                                 |                                   | $V_{CC}$ = 6 V, $V_{IN}$ = 3.3 V, $I_{LOAD}$ = 2 A,<br>@ $T_J$ = 125 °C                   |      |      | 50   | mΩ   |

| $V_{DEMAG}$                     | Output Clamp Voltage              | IOUT ≥ 50 mA                                                                              | 65   | 70   | 75   | V    |

|                                 |                                   | V <sub>IN</sub> = 0 V, V <sub>OUT</sub> = 7 V                                             |      |      | 3    |      |

|                                 | OFF state output current          | V <sub>IN</sub> = 0 V, V <sub>OUT</sub> = 24 V                                            |      |      | 4    |      |

| I <sub>OUT(OFF)</sub>           |                                   | V <sub>IN</sub> = 0 V, V <sub>OUT</sub> = 36 V                                            |      |      | 6    | μA   |

|                                 |                                   | V <sub>IN</sub> = 0 V, V <sub>OUT</sub> = 60 V                                            |      |      | 25   |      |

| Body diod                       | e of output switch                | '                                                                                         |      |      |      |      |

| V <sub>OUT(REV)</sub>           | Forward voltage of output switch  | V <sub>IN</sub> = 0V, I <sub>OUT</sub> = -5 A                                             |      |      | 1.5  | V    |

| t <sub>rr</sub> (1)             | Reverse recovery time             |                                                                                           |      | 250  |      | ns   |

| Q <sub>rr</sub> <sup>(1)</sup>  | Reverse recovery charge           | I <sub>OUT</sub> = -5 A, di/dt = 25 A/μs, V <sub>OUT</sub> = 24 V, T <sub>J</sub> = 25 °C |      | 1    |      | μC   |

| I <sub>RRM</sub> <sup>(1)</sup> | Reverse recovery current          |                                                                                           |      | 8    |      | Α    |

#### 1. Not tested at final test

Table 5. Input and I<sub>PDx</sub> pins

| Symbol               | Parameter                                              | Test Conditions                                     | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------------------------|-----------------------------------------------------|------|------|------|------|

| V <sub>IH</sub>      | Input pin high level voltage                           | IN pin voltage rising                               | 2.2  |      |      | V    |

| V <sub>IL</sub>      | Input pin low level voltage                            | IN pin voltage falling                              |      |      | 0.75 | V    |

| V <sub>I(HYST)</sub> | Input pin hysteresis voltage                           |                                                     |      | 0.3  |      | V    |

| I <sub>IN</sub>      | Input pin current                                      | VCC = 6 V, V <sub>IN</sub> = 3.3 V, OUT = open load |      | 45   | 110  | μA   |

| V <sub>IPD(T)</sub>  | V <sub>IPDX</sub> pins transition voltage (L-H or H-L) | I <sub>PDX</sub> voltage rising or falling          |      | 2.4  |      | V    |

DS14912 - Rev 2 page 7/29

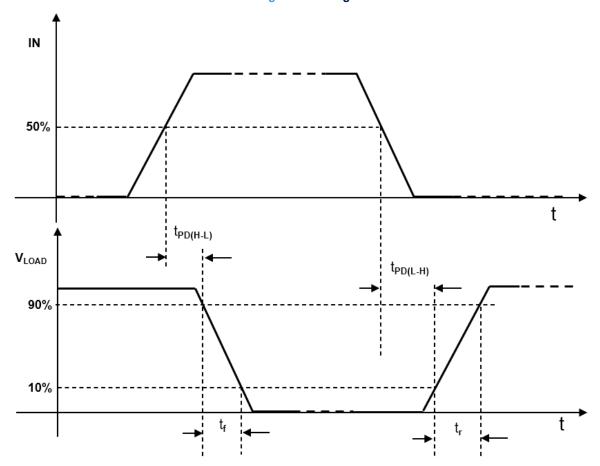

Table 6. Switching

(VCC = 6 V,  $V_{\text{IN}}$  = 3.3 V,  $V_{\text{LOAD}}$  = 24 V,  $R_{\text{LOAD}}$  = 12  $\Omega$ )

| Symbol               | Parameter                                                             | Test Conditions                         | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------------------------------------|-----------------------------------------|------|------|------|------|

| t <sub>f</sub>       | Output voltage fall time                                              | Power switch activation, see Figure 3   |      | 20   | 40   | μs   |

| t <sub>PD(H-L)</sub> | Propagation delay time IN to OUT (V <sub>OUT</sub> level high to low) |                                         |      | 10   | 20   | μs   |

| t <sub>r</sub>       | Output voltage rise time                                              | Power switch deactivation, see Figure 3 |      | 15   | 25   | μs   |

| t <sub>PD(L-H)</sub> | Propagation delay time IN to OUT (V <sub>OUT</sub> level low to high) |                                         |      | 25   | 50   | μs   |

Figure 3. Timing

Table 7. Diagnostic pin (OVT)

| Symbol            | Parameter                  | Test Condition                                          | Min. | Тур. | Max. | Unit |

|-------------------|----------------------------|---------------------------------------------------------|------|------|------|------|

| V <sub>DIAG</sub> | Voltage drop on OVT pin    | I <sub>DIAG</sub> = 4 mA<br>Fault condition active      |      | 0.85 | 1    | V    |

| I <sub>DIAG</sub> | Leakage current on OVT pin | V <sub>DIAG</sub> = 3.3 V<br>Fault condition not active |      |      | 5    | μA   |

DS14912 - Rev 2 page 8/29

**Table 8. Protections and Diagnostic**

| Symbol              | Parameter                        | Test Condition                                                   | Min.                     | Тур.                      | Max.       | Unit |

|---------------------|----------------------------------|------------------------------------------------------------------|--------------------------|---------------------------|------------|------|

| Sta                 | tic Overload detection           | and output current limitation: IP                                | <sub>DX</sub> pins set l | ligh (= 3.3 V) or L       | ow (= SGNI | )    |

| I <sub>PK(S)</sub>  | Overcurrent activation threshold |                                                                  |                          | I <sub>LIM(S)</sub> + 20% |            | А    |

|                     |                                  | I <sub>PD1</sub> = L, I <sub>PD2</sub> = L, I <sub>PD3</sub> = L | 21                       | 25                        | 39         | А    |

|                     |                                  | I <sub>PD1</sub> = L, I <sub>PD2</sub> = L, I <sub>PD3</sub> = H | 15.8                     | 22                        | 27.5       | Α    |

|                     |                                  | I <sub>PD1</sub> = L, I <sub>PD2</sub> = H, I <sub>PD3</sub> = L | 11                       | 16.5                      | 22         | Α    |

| L                   | Overcurrent                      | I <sub>PD1</sub> = L, I <sub>PD2</sub> = H, I <sub>PD3</sub> = H | 7.9                      | 12                        | 16         | Α    |

| I <sub>LIM(S)</sub> | limitation level                 | I <sub>PD1</sub> = H, I <sub>PD2</sub> = L, I <sub>PD3</sub> = L | 4.5                      | 8.2                       | 12         | Α    |

|                     |                                  | I <sub>PD1</sub> = H, I <sub>PD2</sub> = L, I <sub>PD3</sub> = H | 2.4                      | 4                         | 5.6        | Α    |

|                     |                                  | I <sub>PD1</sub> = H, I <sub>PD2</sub> = H, I <sub>PD3</sub> = L | 1                        | 2                         | 3          | А    |

|                     |                                  | I <sub>PD1</sub> = H, I <sub>PD2</sub> = H, I <sub>PD3</sub> = H | 0.7                      | 1.2                       | 1.8        | Α    |

allowed: see Figure 4

| I <sub>PK(I)</sub>  | Initial overcurrent activation threshold  |                                                                                              |      | I <sub>LIM(S)</sub> + 20%   |      | Α  |

|---------------------|-------------------------------------------|----------------------------------------------------------------------------------------------|------|-----------------------------|------|----|

| I <sub>LIM(I)</sub> | Initial overcurrent limitation level      |                                                                                              | 21   | 25                          | 39   | Α  |

| D <sub>PK(I)</sub>  | Initial overcurrent time                  | $I_{PD1}$ = to SGND by $C_{PD1}$ $I_{PD2}$ = L, $I_{PD3}$ = L                                |      | 215 × C <sub>PD1</sub> [nF] |      | μs |

| I <sub>LIM(S)</sub> | Steady state overcurrent limitation level |                                                                                              | 4.5  | 8.2                         | 12   | Α  |

| I <sub>LIM(I)</sub> | Initial overcurrent limitation level      |                                                                                              | 15.8 | 22                          | 27.5 | Α  |

| D <sub>PK(I)</sub>  | Initial overcurrent time                  | $I_{PD1}$ = to SGND by $C_{PD1}$ $I_{PD2}$ = L, $I_{PD3}$ = H                                |      | 215 × C <sub>PD1</sub> [nF] |      | μs |

| I <sub>LIM(S)</sub> | Steady state overcurrent limitation level |                                                                                              | 2.4  | 4                           | 5.6  | Α  |

| I <sub>LIM(I)</sub> | Initial overcurrent limitation level      |                                                                                              | 11   | 16.5                        | 22   | Α  |

| D <sub>PK(I)</sub>  | Initial overcurrent time                  | I <sub>PD1</sub> = to SGND by C <sub>PD1</sub> I <sub>PD2</sub> =<br>H, I <sub>PD3</sub> = L |      | 215 × C <sub>PD1</sub> [nF] |      | μs |

| I <sub>LIM(S)</sub> | Steady state overcurrent limitation level | , 153 =                                                                                      | 1    | 2                           | 3    | Α  |

| I <sub>LIM(I)</sub> | Initial overcurrent limitation level      |                                                                                              | 7.9  | 12                          | 16   | Α  |

| D <sub>PK(I)</sub>  | Initial overcurrent time                  | I <sub>PD1</sub> = to SGND by C <sub>PD1</sub> I <sub>PD2</sub> =<br>H, I <sub>PD3</sub> = H |      | 215 × C <sub>PD1</sub> [nF] |      | μs |

| I <sub>LIM(S)</sub> | Steady state overcurrent limitation level | , , , , , , , , , , , , , , , , , , , ,                                                      | 0.7  | 1.2                         | 1.8  | А  |

DS14912 - Rev 2 page 9/29

Figure 4. Dynamic current limitation ( $C_{PD1} < C_{PD2} < C_{PD3}$ )

DS14912 - Rev 2 page 10/29

# 6 Output Logic

Table 9. Output stage truth table

(L = pin voltage Low, H = pin voltage High, X = not determined)

| Condition                                | V <sub>IN(MCU)</sub> | IN | OUT              | OVT |

|------------------------------------------|----------------------|----|------------------|-----|

| Normal Operation                         | L                    | L  | H                | H   |

|                                          | H                    | H  | L                | H   |

| Overload                                 | L                    | L  | L                | H   |

|                                          | H                    | H  | X <sup>(1)</sup> | H   |

| Junction over-temperature protection (2) | L                    | L  | H                | L   |

|                                          | H                    | H  | H                | L   |

- 1.  $Pin \ voltage = V_{SUPPLY} (I_{OUT} * R_{LOAD})$

- 2. When  $T_J > T_{JSD}$  OUT is forced OFF, OVT is activated

DS14912 - Rev 2 page 11/29

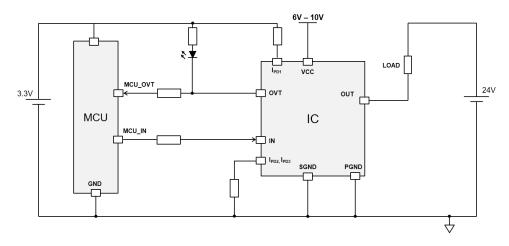

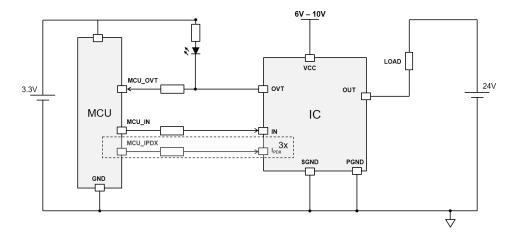

# **Application Schematics Examples**

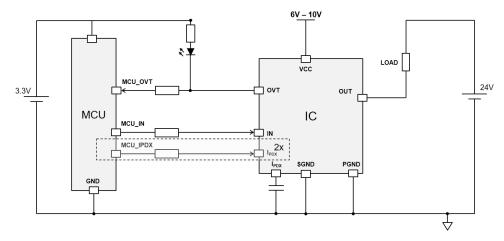

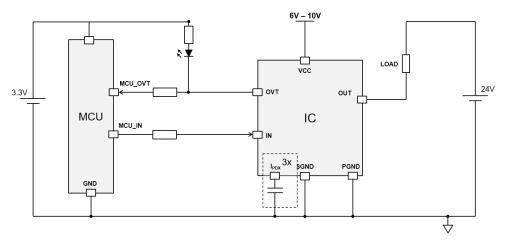

Figure 5. Application schematic: example of static setting of current limitation

Figure 6. Application schematic: example of dynamic control of current limitation by GPIOs

Figure 7. Application schematic: example of dynamic control of current limitation with single capacitor

DS14912 - Rev 2 page 12/29

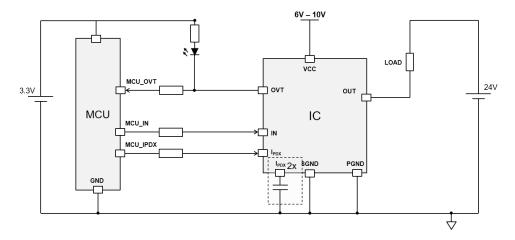

Figure 8. Application schematic: example of dynamic control of current limitation with two capacitors

Figure 9. Application schematic: example of dynamic control of current limitation with three capacitors

DS14912 - Rev 2 page 13/29

## 8 Protections and diagnostic

The IC integrates several protections to help the design of robust applications.

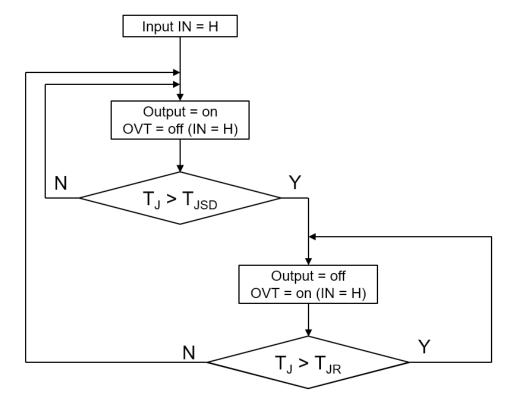

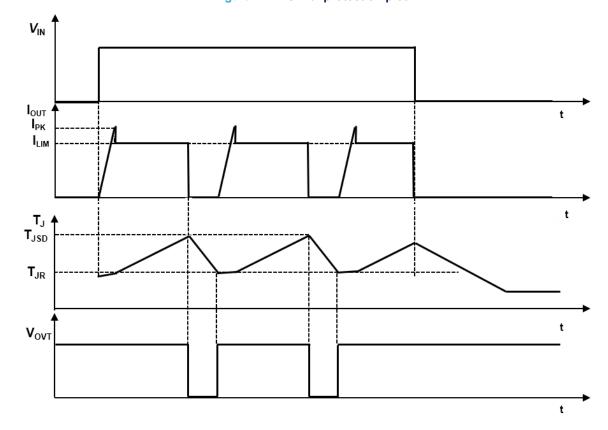

#### 8.1 Over-temperature

The device is protected against overheating in case of overload conditions. During the driving period (by means when the MCU is forcing high the IN pin), if the output is overloaded, then the device suffers huge thermal stress. In thermal stress conditions the junction thermal shutdown protection is activated: the output channel (OUT) is turned off when its junction temperature  $(T_J)$  is higher than the activation threshold  $(T_{JSD})$  and turned back on when it goes below the reset threshold  $(T_{JR})$ .

This behavior continues until the fault on the output is present. When the thermal protection is active for OUT, the OVT pin is activated accordingly.

Figure 10 shows the thermal protection behavior, while Figure 11 reports typical temperature trends and output vs input state.

Figure 10. Thermal protection flowchart

DS14912 - Rev 2 page 14/29

Figure 11. Thermal protection plot

Table 10. Thermal protection temperatures

| Symbol            | Parameter                       | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|------|

| T <sub>JSD</sub>  | Junction temperature shutdown   | 150  | 170  | 190  | °C   |

| T <sub>JR</sub>   | Junction temperature reset      |      | 150  |      | °C   |

| T <sub>JHYS</sub> | Junction temperature hysteresis |      | 20   |      | °C   |

#### 8.2 Overload

The IC integrates an output current control circuitry, activated when the IN pin goes High, guaranteeing the load and IC functionalities in case of overload or short circuit event.

If the sensing part of the control circuitry triggers the overcurrent activation threshold, then the same circuitry activates the output current limitation protection, by means that the current supplied to the load will be limited by a proper regulation of the  $V_{GS}$  on the integrated power switch.

The output current control circuit can work with static and dynamic thresholds, according to the settings of the pins  $I_{PD1}$  and  $I_{PD2}$ .

In the static current limitation, the I<sub>PDX</sub> pins are set "High" or "Low". The activation thresholds and limitation levels are reported in the section "**Static Overload detection and output current limitation:** I<sub>PDX</sub> pins set High or Low" of Section 5.

Note that the I<sub>PDX</sub> pins can be driven by the GPIO ports of an MCU or ASIC: in this case the system can switch between different thresholds and levels.

The dynamic current limitation becomes active if at least one of the  $I_{PDX}$  pins is connected to GND by a  $C_{PDX}$  capacitor. An internal circuitry supplies the  $C_{PDX}$  capacitor so that the related  $I_{PDX}$  pin goes from 0 V to "high level" in  $D_{PK}$  [µs]= 215 ×  $C_{PDX}$  [nF].

Also, the internal circuitry on each  $I_{PDX}$  pin feature the reset of the  $I_{PDX}$  high voltage level so that the system is ready to restart at next transition of the IN pin.

DS14912 - Rev 2 page 15/29

The current limitation activation thresholds and current limitation levels with one  $I_{PDX}$  pin fixed high or low and other  $I_{PDX}$  pin connected to  $C_{PDX}$  are reported in the section "Dynamic Output Overload detection limitation and output current limitation" of Section 5.

If the final application requires same  $C_{PDX}$  capacitor for two or three  $I_{PDX}$  pins, then it is recommended to short the pins to share a single capacitor.

For convenience Table 11 and Table 12 summarize the possible current limitation levels.

Table 11. Static current limitation setting

| I <sub>PD1</sub> | I <sub>PD2</sub> | I <sub>PD3</sub> | I <sub>LIM</sub> [A] |      |      |  |

|------------------|------------------|------------------|----------------------|------|------|--|

| 'PD1             | 1902             | נטקי             | Min.                 | Тур. | Max. |  |

| L                | L                | L                | 21                   | 25   | 39   |  |

| L                | L                | Н                | 15.8                 | 22   | 27.5 |  |

| L                | Н                | L                | 11                   | 16.5 | 22   |  |

| L                | Н                | Н                | 7.9                  | 12   | 16   |  |

| Н                | L                | L                | 4.5                  | 8.2  | 12   |  |

| Н                | L                | Н                | 2.4                  | 4    | 5.6  |  |

| Н                | Н                | L                | 1                    | 2    | 3    |  |

| Н                | Н                | Н                | 0.7                  | 1.2  | 1.8  |  |

Table 12. Mixed mode current limitation setting

| I <sub>PD1</sub> | I <sub>PD2</sub> | I <sub>PD3</sub>                      | I <sub>LIM(I)</sub> [A] | I <sub>LIM(S)</sub> [A] | D <sub>PK(I)</sub> [µs]    |

|------------------|------------------|---------------------------------------|-------------------------|-------------------------|----------------------------|

| L                | L                |                                       | 25                      | 22                      |                            |

| L                | Н                | C <sub>PD</sub>                       | 16.5                    | 12                      |                            |

| Н                | L                | □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ | 8.2                     | 4                       |                            |

| Н                | Н                |                                       | 2                       | 1.2                     |                            |

| L                |                  | L                                     | 25                      | 16.5                    |                            |

| L                | C <sub>PD</sub>  | Н                                     | 22                      | 12                      | 215 × C <sub>PD</sub> [nF] |

| H<br>H           | ОРД              | L                                     | 8.2                     | 2                       | 213 ^ CPD [III ]           |

|                  |                  | Н                                     | 4                       | 1.2                     |                            |

|                  | L                | L                                     | 25                      | 8.2                     |                            |

| C <sub>PD</sub>  | L                | Н                                     | 22                      | 4                       |                            |

|                  | Н                | L                                     | 16.5                    | 2                       |                            |

|                  | Н                | Н                                     | 12                      | 1.2                     |                            |

DS14912 - Rev 2 page 16/29

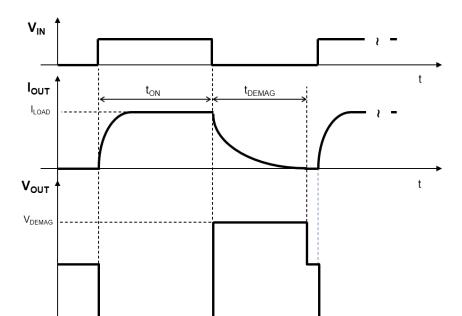

## 9 Active clamp

Active clamp is also known as Fast Demagnetization of inductive loads or Fast Current Decay.

When a high-side driver turns off an inductance, an under-voltage on output is detected.

The OUT pin is pulled-down to  $V_{DEMAG}$ . The conduction state is modulated by an internal circuitry in order to keep the OUT pin voltage at  $\sim V_{DEMAG}$  until the energy in the inductive load has been dissipated.

The energy is dissipated in both IC internal switch and load resistance.

Figure 12. Active clamp behavior

DS14912 - Rev 2 page 17/29

Output current (A)

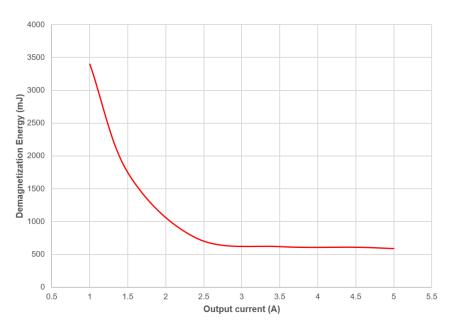

Figure 14. Typical demagnetization: L vs I (single pulse) at  $V_{LOAD}$  = 24 V and  $T_{AMB}$  = 125 °C

DS14912 - Rev 2 page 18/29

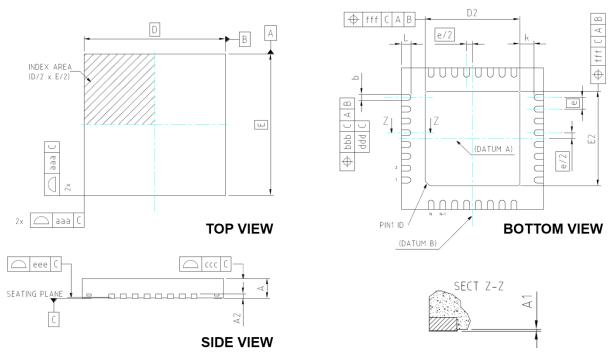

## 10 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com

ECOPACK is an ST trademark.

#### 10.1 Package mechanical data

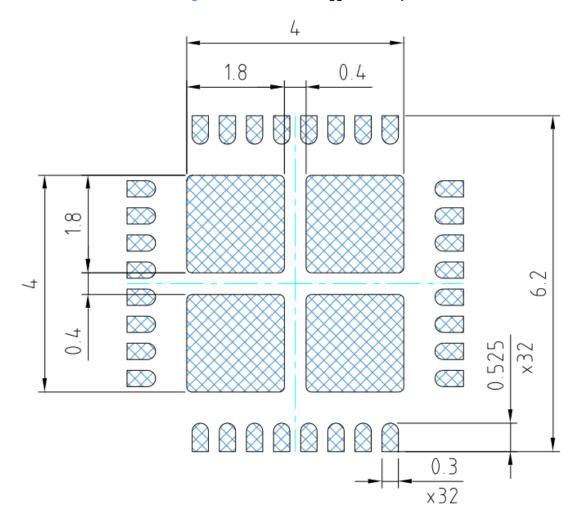

Figure 15. QFN32L 6x6 package dimensions

Table 13. QFN32L 6x6 mechanical data

| Symbol | [mm] |         |      | Notes |

|--------|------|---------|------|-------|

| Symbol | Min. | Nom.    | Max. | Notes |

| А      | 0.80 | 0.90    | 1.00 | 11    |

| A1     | 0.00 | 0.02    | 0.05 | 8, 11 |

| A2     |      | 0.2 REF |      |       |

| L      | 0.35 | 0.40    | 0.45 | 11    |

| b      | 0.20 | 0.25    | 0.30 | 7, 11 |

| D      |      | 6.00    |      | 11    |

| D2     | 3.90 | 4.00    | 4.10 | 11    |

| E      |      | 6.00    |      | 11    |

| E2     | 3.90 | 4.00    | 4.10 | 11    |

| е      | 0.5  |         |      |       |

| k      | 0.55 |         |      |       |

| N      | 32   |         | 9    |       |

DS14912 - Rev 2 page 19/29

| Table 14. | <b>Tolerance</b> | of forms | and | positions |

|-----------|------------------|----------|-----|-----------|

|-----------|------------------|----------|-----|-----------|

| Symbol | Tolerance of forms and position | Notes |

|--------|---------------------------------|-------|

| aaa    | 0.15                            |       |

| bbb    | 0.10                            | 10    |

| ccc    | 0.10                            |       |

| ddd    | 0.05                            | 10    |

| eee    | 0.08                            |       |

| fff    | 0.10                            |       |

- 1. Dimensioning and tolerancing schemes conform to ASME Y14.5M-1994.

- 2. Datum A-B to be determined at datum plane C.

- 3. To be determined at setting datum plane C.

- 4. Detail of pin 1 identifier are optional but must be located within the zone indicated.

- 5. All Dimensions are in millimeters.

- 6. Exact shape of each corner of the exposed die pad is optional.

- 7. These dimensions apply to the flat section of the lead between 0.10 mm and 0.25 mm from the lead tip.

- 8. A1 is defined as the distance from the seating plane to the lowest point on the package body.

- 9. "N" is the max number of terminal positions for the specified body size.

- 10. For Tolerance of Form and Position see Table.

- 11. Critical dimensions:

- \_ A

- A1

- A3

- D&E

- b&L

- D2 & E2

- 12. Component cross reference: OPTIONAL.

- 13. For Symbols, Recommended Values and Tolerances see Table below: (ACCORDING TO JEDEC SPEC IF REGISTERED OR JEDEC DESIGN GUIDE).

DS14912 - Rev 2 page 20/29

**Table 15. Definitions**

| Symbol | Definition                                                                                                                                                                                                                  | Notes                                                                                                                                                                                        |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| aaa    | The bilateral profile tolerance that controls the position of the plastic body sides. The centers of the profile zones are defined by the basic dimensions D and E                                                          | For flange-molded packages, this tolerance also applies for basic dimensions D1 and E1. For packages tooled with intentional terminal tip protusion, aaa does not apply to those protusions. |

| bbb    | The tolerance that controls the position of the entire terminal pattern with respect to Datum's A and B. The center of the tolerance zone for each terminal is defined by basic dimension "e" as related to Datum's A and B |                                                                                                                                                                                              |

| ccc    | The tolerance located parallel to the seating plane in which the top surface of the package must be located                                                                                                                 |                                                                                                                                                                                              |

| ddd    | The tolerance that controls the position of the terminals to each other. The centers of the profile zones are defined by basic dimension "e"                                                                                | This tolerance is normally compounded with tolerance zone defined by bbb                                                                                                                     |

| eee    | The unilateral tolerance located above the seating plane where in the bottom surface of all terminals must be located                                                                                                       | This tolerance is commonly known as the "coplanarity" of the package terminals                                                                                                               |

| fff    | The tolerance that controls the position of the exposed metal heat feature. The center of the tolerance zone is the datum's defined by the center lines of the package body                                                 | This tolerance applies to an optional package feature                                                                                                                                        |

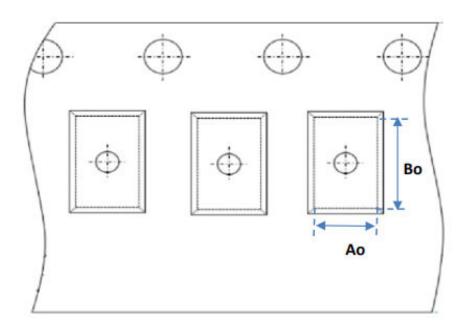

Figure 16. QFN32L 6x6 Suggested footprint

DS14912 - Rev 2 page 21/29

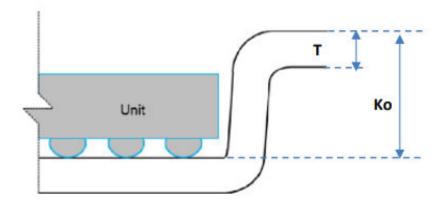

# 11 Packing mechanical data

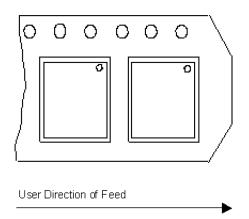

Figure 17. QFN32L 6x6 mm reel shipment

**Table 16. Standard SPC parameters**

| ltem | Description    |

|------|----------------|

| Ao   | Pocket Length  |

| Во   | Pocket Width   |

| Ko   | Pocket Depth   |

| Т    | Tape Thickness |

DS14912 - Rev 2 page 22/29

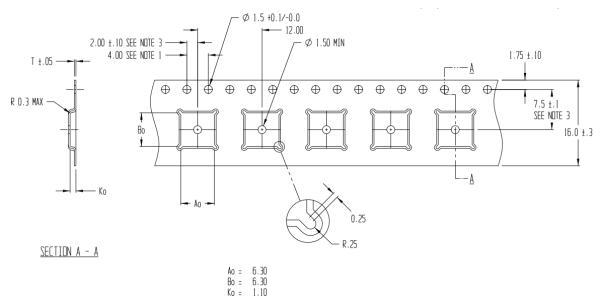

Figure 18. QFN32L 6x6 mm carrier tape dimensions

Figure 19. QFN32L 6x6 mm carrier tape, Pin 1 indication

DS14912 - Rev 2 page 23/29

# 12 Ordering information

### Table 17. Ordering information

| Part number | Package       | Packaging     |

|-------------|---------------|---------------|

| IPS1050LQ   | QFN32L 6x6 mm | Tape and reel |

DS14912 - Rev 2 page 24/29

## **Revision history**

**Table 18. Document revision history**

| Date        | Version | Changes                                                                       |

|-------------|---------|-------------------------------------------------------------------------------|

| 29-Sep-2025 | 1       | Initial release.                                                              |

| 06-Oct-2025 | 2       | Corrected test conditions in the Figure 13 and Figure 14; some minor changes. |

DS14912 - Rev 2 page 25/29

## **Contents**

| 1                | Block diagram                   |    |

|------------------|---------------------------------|----|

| 2                | Pin connection                  |    |

| <b>-</b><br>3    | Absolute maximum ratings        |    |

| 4                | Thermal data                    |    |

| <del></del><br>5 | Electrical characteristics      |    |

|                  |                                 |    |

| 6                | Output Logic                    |    |

| 7                | Application Schematics Examples | 12 |

| 8                | Protections and diagnostic      | 14 |

|                  | 8.1 Over-temperature            | 14 |

|                  | 8.2 Overload                    | 15 |

| 9                | Active clamp                    | 17 |

| 10               | Package information             | 19 |

|                  | 10.1 Package mechanical data    | 19 |

| 11               | Packing mechanical data         | 22 |

| 12               | Ordering information            | 24 |

| Rev              | vision history                  |    |

|                  | t of tables                     |    |

|                  | t of figures                    |    |

|                  |                                 |    |

## **List of tables**

| Table 1.  | Pin descriptions                      | 4  |

|-----------|---------------------------------------|----|

| Table 2.  | Absolute maximum ratings              | 5  |

| Table 3.  | Thermal data                          | 6  |

| Table 4.  | Output stage                          | 7  |

| Table 5.  | Input and I <sub>PDx</sub> pins       | 7  |

| Table 6.  | Switching                             | 8  |

| Table 7.  | Diagnostic pin (OVT)                  | 8  |

| Table 8.  | Protections and Diagnostic            | 9  |

| Table 9.  | Output stage truth table              | 11 |

| Table 10. | Thermal protection temperatures       | 5  |

| Table 11. | Static current limitation setting     | 6  |

| Table 12. | Mixed mode current limitation setting |    |

| Table 13. | QFN32L 6x6 mechanical data            | 9  |

| Table 14. | Tolerance of forms and positions      | 20 |

| Table 15. | Definitions                           |    |

| Table 16. | Standard SPC parameters               |    |

| Table 17. | Ordering information                  | 24 |

| Table 18. | Document revision history             | 25 |

# **List of figures**

| Figure 1.  | Block diagram                                                                                            | . 2 |

|------------|----------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Pin connections (top through view)                                                                       | . 3 |

| Figure 3.  | Timing                                                                                                   | . 8 |

| Figure 4.  | Dynamic current limitation (C <sub>PD1</sub> < C <sub>PD2</sub> < C <sub>PD3</sub> )                     | 10  |

| Figure 5.  | Application schematic: example of static setting of current limitation                                   | 12  |

| Figure 6.  | Application schematic: example of dynamic control of current limitation by GPIOs                         | 12  |

| Figure 7.  | Application schematic: example of dynamic control of current limitation with single capacitor            | 12  |

| Figure 8.  | Application schematic: example of dynamic control of current limitation with two capacitors              | 13  |

| Figure 9.  | Application schematic: example of dynamic control of current limitation with three capacitors            | 13  |

| Figure 10. | Thermal protection flowchart                                                                             | 14  |

| Figure 11. | Thermal protection plot                                                                                  | 15  |

| Figure 12. | Active clamp behavior                                                                                    | 17  |

| Figure 13. | Typical demagnetization: E vs I (single pulse) at $V_{LOAD}$ = 24 V and $T_{AMB}$ = 125 °C               | 17  |

| Figure 14. | Typical demagnetization: L vs I (single pulse) at V <sub>LOAD</sub> = 24 V and T <sub>AMB</sub> = 125 °C | 18  |

| Figure 15. | QFN32L 6x6 package dimensions                                                                            | 19  |

| Figure 16. | QFN32L 6x6 Suggested footprint                                                                           | 21  |

| Figure 17. | QFN32L 6x6 mm reel shipment                                                                              | 22  |

| Figure 18. | QFN32L 6x6 mm carrier tape dimensions                                                                    | 23  |

| Figure 19. | QFN32L 6x6 mm carrier tape, Pin 1 indication                                                             | 23  |

|            |                                                                                                          |     |

DS14912 - Rev 2 page 28/29

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

DS14912 - Rev 2 page 29/29